# BUS AND CACHE MEMORY ORGANIZATIONS FOR MULTIPROCESSORS

By

Donald C. Winsor

CSE-TR-19-89

# THE UNIVERSITY OF MICHIGAN

COMPUTER SCIENCE AND ENGINEERING DIVISION

DEPARTMENT OF ELECTRICAL ENGINEERING AND COMPUTER SCIENCE

Room 3402, EECS Building

Ann Arbor, Michigan 48109-2122

USA

#### **ABSTRACT**

# BUS AND CACHE MEMORY ORGANIZATIONS FOR MULTIPROCESSORS

Donald Charles Winsor

Chairman: Trevor Mudge

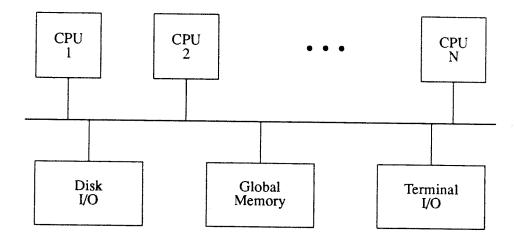

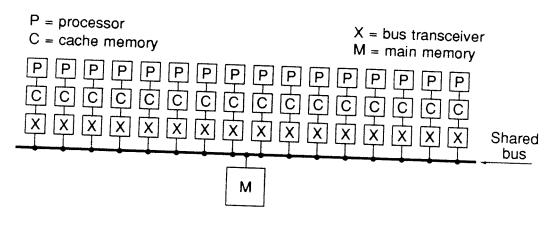

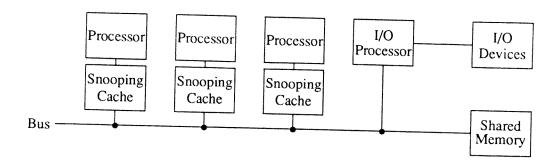

The single shared bus multiprocessor has been the most commercially successful multiprocessor system design up to this time, largely because it permits the implementation of efficient hardware mechanisms to enforce cache consistency. Electrical loading problems and restricted bandwidth of the shared bus have been the most limiting factors in these systems.

This dissertation presents designs for logical buses constructed from a hierarchy of physical buses that will allow snooping cache protocols to be used without the electrical loading problems that result from attaching all processors to a single bus. A new bus bandwidth model is developed that considers the effects of electrical loading of the bus as a function of the number of processors, allowing optimal bus configurations to be determined. Trace driven simulations show that the performance estimates obtained from this bus model agree closely with the performance that can be expected when running a realistic multiprogramming workload in which each processor runs an independent task. The model is also used with a parallel program workload to investigate its accuracy when the processors do not operate independently. This is found to produce large errors in the mean service time estimate, but still gives reasonably accurate estimates for the bus utilization.

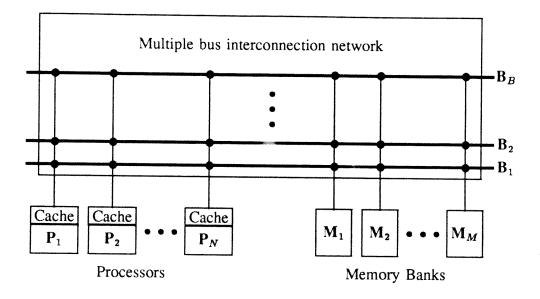

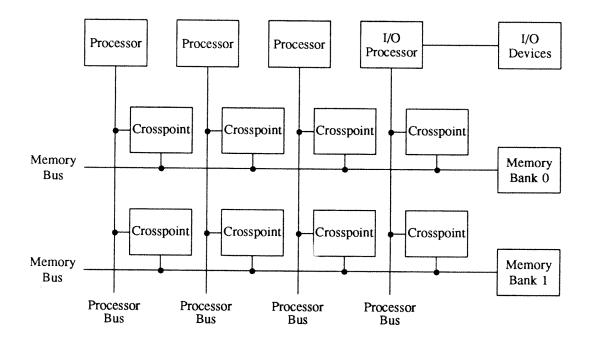

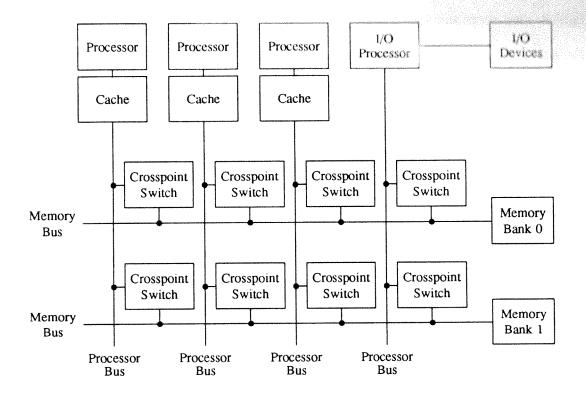

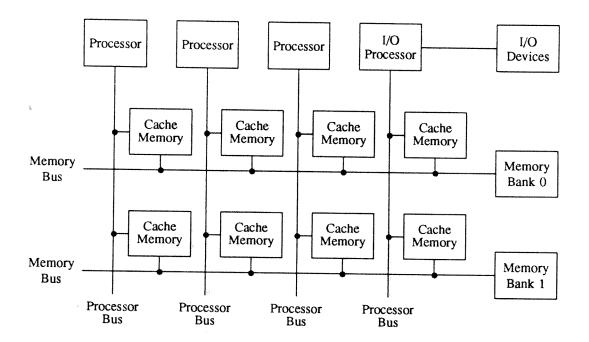

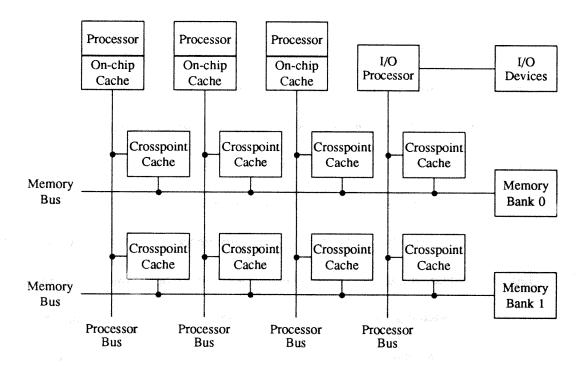

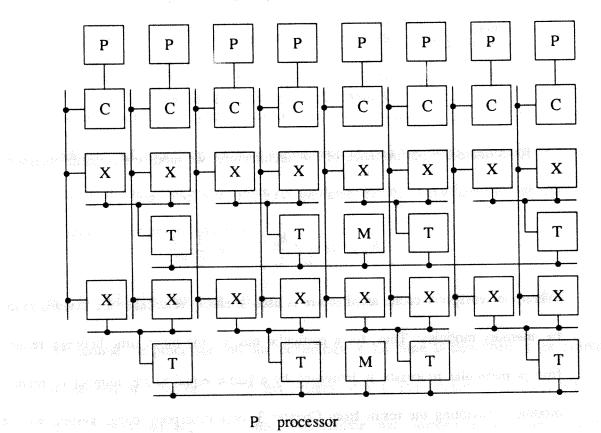

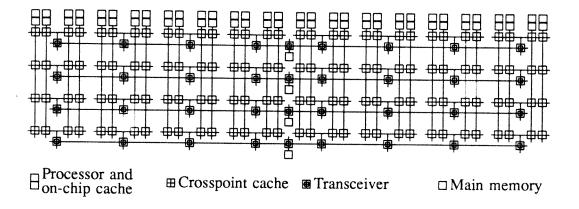

A new system organization consisting essentially of a crossbar network with a cache memory at each crosspoint is proposed to allow systems with more than one memory bus to be constructed. A two-level cache organization is appropriate for this architecture. A small cache may be placed close to each processor, preferably on the CPU chip, to minimize the effective memory access time. A larger cache built from slower, less expensive memory is then placed at each crosspoint to minimize the bus traffic.

By using a combination of the hierarchical bus implementations and the crosspoint cache architecture, it should be feasible to construct shared memory multiprocessor systems with several hundred processors.

© Donald Charles Winsor

All Rights Reserved 1989

To my family and friends

# TABLE OF CONTENTS

| DED | ICAT | TION   |                                             | i    |

|-----|------|--------|---------------------------------------------|------|

| ACK | NOV  | VLEDG  | GEMENTS                                     | ii   |

| TAB | LE O | F CON  | NTENTS                                      | i,   |

|     |      |        | ES                                          | vi   |

|     |      |        | RES                                         |      |

|     | PTEI |        |                                             | V 11 |

| 1   | INT  | RODU   | JCTION                                      | 1    |

|     | 1.1  | Single | e bus systems                               | 2    |

|     | 1.2  | Cache  | e memories                                  | 3    |

|     | 1.3  | Bus e  | electrical limitations                      | 5    |

|     | 1.4  | Trace  | driven simulation                           | 7    |

|     | 1.5  | Cross  | point cache architecture                    | 7    |

|     | 1.6  | Techn  | niques for constructing large systems       | 7    |

|     | 1.7  | Goal   | and scope of this dissertation              | 7    |

|     | 1.8  | Major  | contributions                               | 8    |

| 2   | BAC  | CKGRO  | OUND                                        | 10   |

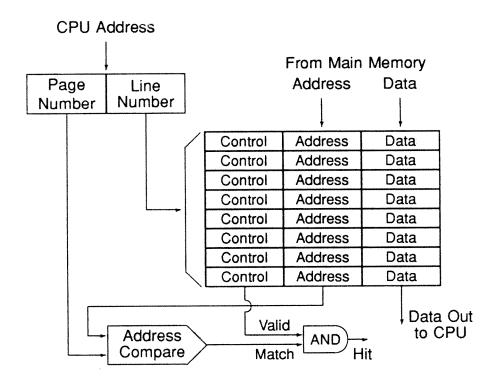

|     | 2.1  | Cache  | e memories                                  | 10   |

|     |      | 2.1.1  | Basic cache memory architecture             | 10   |

|     |      | 2.1.2  | Cache operation                             | 14   |

|     |      | 2.1.3  | Previous cache memory research              | 17   |

|     |      | 2.1.4  | Cache consistency                           | 17   |

|     |      | 2.1.5  | Performance of cache consistency mechanisms | 22   |

|     | 2.2  | Maxin  | nizing single bus bandwidth                 | 27   |

|     |      | 2.2.1  | Minimizing bus cycle time                   | 27   |

|     |      | 2.2.2  | Increasing bus width                        | 28   |

|     |      | 2.2.3  | Improving bus protocol                      | 29   |

|     | 2.3  | Multip | ole bus architecture                        | 30   |

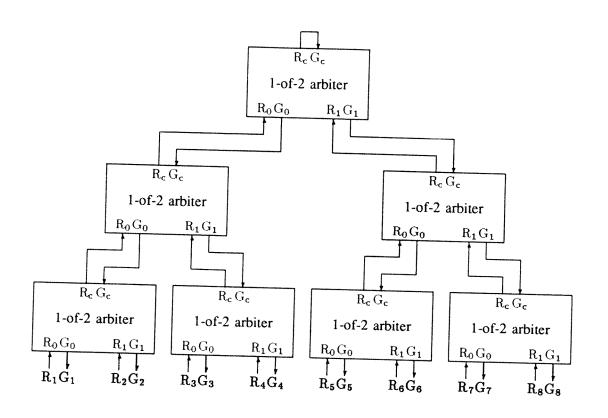

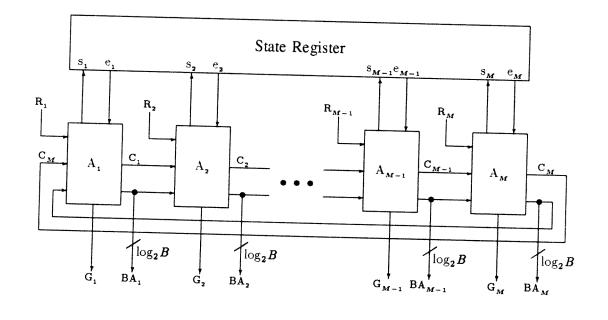

|     |      | 2.3.1  | Multiple bus arbiter design                 | 32   |

|     |      | 2.3.2  | Multiple bus performance models             | 36   |

|     |      | 2.3.3  | Problems with multiple buses                | 36   |

| 3 BUS PERFORMANCE MODELS       38         3.1 Introduction       38         3.2 Implementing a logical single bus       40         3.3 Bus model       42         3.3.1 Delay model       42         3.2 Interference model       44         3.4 Maximum throughput for a linear bus       53         3.5 TTL bus example       60         3.6 Optimization of a two-level bus hierarchy       68         3.8 Maximum throughput for a two-level bus hierarchy       68         3.8 Maximum throughput using a binary tree interconnection       72         3.9 High performance bus example       74         3.9.1 Single bus example       75         3.10 Summary       76         4 TRACE DRIVEN SIMULATIONS       77         4.1 Necessity of simulation techniques       78         4.2 Simulator implementation       79         4.2.1 68020 trace generation and simulation       79         4.2.2 88100 trace generation and simulation       79         4.2.1 Markov chain model results for 68020 example       85         4.3 Simulation workload       86         4.4 Results for 68020 example system       87         4.4.1 Markov chain model results for 68020 example       99         4.5.2 Trace driven simulation results for 88100 e                                                                       |   | 2    | .4 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 37         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 3.1       Introduction       38         3.2       Implementing a logical single bus       40         3.3       Bus model       42         3.3.1       Delay model       42         3.3.2       Interference model       44         3.4       Maximum throughput for a linear bus       53         3.5       TTL bus example       60         3.6       Optimization of a two-level bus hierarchy       68         3.8       Maximum throughput for a two-level bus hierarchy       68         3.8       Maximum throughput using a binary tree interconnection       72         3.9       High performance bus example       75         3.9.1       Single bus example       75         3.9.2       Two-level bus example       75         3.10       Summary       76         4       TRACE DRIVEN SIMULATIONS       77         4.1       Necessity of simulation techniques       78         4.2       Simulation implementation       79         4.2.1       68020 trace generation and simulation       79         4.2.2       88100 trace generation and simulation       79         4.2.1       68020 trace generation and simulation       79         4.2.1       <                                                                                                                                                       |   | 3 B  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . ,        |

| 3.2 Implementing a logical single bus       40         3.3 Bus model       42         3.3.1 Delay model       42         3.3.2 Interference model       44         3.4 Maximum throughput for a linear bus       53         3.5 TTL bus example       60         3.6 Optimization of a two-level bus hierarchy       67         3.7 Maximum throughput for a two-level bus hierarchy       68         3.8 Maximum throughput using a binary tree interconnection       72         3.9 High performance bus example       74         3.9.1 Single bus example       75         3.9.2 Two-level bus example       75         3.10 Summary       76         4 TRACE DRIVEN SIMULATIONS       77         4.1 Necessity of simulation techniques       78         4.2 Simulator implementation       79         4.2.1 68020 trace generation and simulation       79         4.2.2 88100 trace generation and simulation       85         4.3 Simulation workload       86         4.4 Results for 68020 example system       87         4.4.1 Markov chain model results for 68020 example       91         4.4.2 Trace driven simulation results for 68020 example       92         4.5.1 Markov chain model results for 88100 example       90         4.5.2                                                                       |   | 3.   | 1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 38         |

| 3.3.1 Delay model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 38         |

| 3.3.2 Interference model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |      | 3 Bus model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 40         |

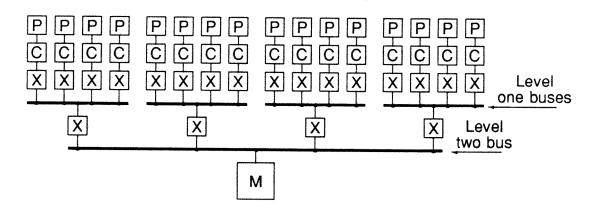

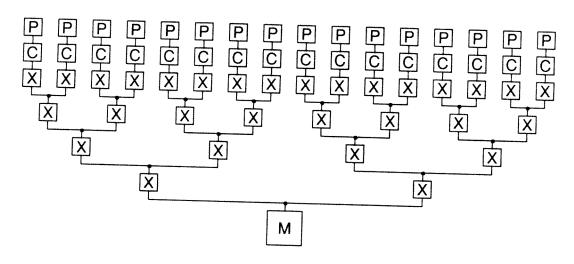

| 3.4 Maximum throughput for a linear bus 3.5 TTL bus example 3.6 Optimization of a two-level bus hierarchy 3.7 Maximum throughput for a two-level bus hierarchy 3.8 Maximum throughput using a binary tree interconnection 3.9 High performance bus example 3.9.1 Single bus example 3.9.2 Two-level bus example 3.9.2 Two-level bus example 3.9.3 Summary 3.9.3 Simulation techniques 4.1 Necessity of simulation techniques 4.2 Simulator implementation 4.2.1 68020 trace generation and simulation 4.2.2 88100 trace generation 4.2.3 Simulation workload 4.4 Results for 68020 example system 4.4.1 Markov chain model results for 68020 example 4.4.2 Trace driven simulation results for 68020 example 4.4.3 Accuracy of model for 68020 example 4.5 Results for 88100 example system 4.5.1 Markov chain model results for 88100 example 4.5.2 Trace driven simulation results for 88100 example 4.5.3 Accuracy of model for 88100 example 4.5.4 Trace driven simulation results for 88100 example 4.5.5 Trace driven simulation results for 88100 example 4.5.1 Single bus architecture 5.1 Single bus architecture 5.3 Crosspoint cache architecture 5.3 Crosspoint cache architecture 5.3 Memory bus activity 5.3.2 Memory bus activity 5.3.3 Memory addressing example                                                 |   | ٥.   | 3.3.1 Delay model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 42         |

| 3.5 STAL multi turbughput for a linear bus 3.5 TTL bus example 3.6 Optimization of a two-level bus hierarchy 3.7 Maximum throughput for a two-level bus hierarchy 3.8 Maximum throughput using a binary tree interconnection 3.9 High performance bus example 3.9.1 Single bus example 3.9.2 Two-level bus example 3.9.2 Two-level bus example 3.9.2 Two-level bus example 3.9.2 Two-level bus example 3.9.3 Simulator implementation 4.1 Necessity of simulation techniques 4.2 Simulator implementation 4.2.1 68020 trace generation and simulation 4.2.2 88100 trace generation 4.3 Simulation workload 4.4 Results for 68020 example system 4.4.1 Markov chain model results for 68020 example 4.4.2 Trace driven simulation results for 68020 example 4.4.3 Accuracy of model for 68020 example 4.5.1 Markov chain model results for 88100 example 4.5.2 Trace driven simulation results for 88100 example 4.5.3 Accuracy of model for 88100 example 4.5.4 Trace driven simulation results for 88100 example 4.5.5 Trace driven simulation results for 88100 example 4.5.1 Single bus architecture 5.1 Single bus architecture 5.3 Crosspoint cache architecture 5.3 Crosspoint cache architecture 5.3 Crosspoint cache architecture 5.3.1 Processor bus activity 5.3.2 Memory bus activity 5.3.3 Memory addressing example |   |      | 3.3.2 Interference model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 42         |

| 3.6 Optimization of a two-level bus hierarchy 67 3.7 Maximum throughput for a two-level bus hierarchy 68 3.8 Maximum throughput using a binary tree interconnection 72 3.9 High performance bus example 74 3.9.1 Single bus example 75 3.0.2 Two-level bus example 75 3.10 Summary 76  4 TRACE DRIVEN SIMULATIONS 77 4.1 Necessity of simulation techniques 78 4.2 Simulator implementation 79 4.2.1 68020 trace generation and simulation 79 4.2.2 88100 trace generation 85 4.3 Simulation workload 86 4.4 Results for 68020 example system 87 4.4.1 Markov chain model results for 68020 example 89 4.4.2 Trace driven simulation results for 68020 example 91 4.4.3 Accuracy of model for 68020 example 92 4.5 Results for 88100 example system 96 4.5.1 Markov chain model results for 88100 example 99 4.5.2 Trace driven simulation results for 88100 example 100 4.5.3 Accuracy of model for 88100 example 100 4.5.4 Summary of results for single logical bus 101  5 CROSSPOINT CACHE ARCHITECTURE 105 5.1 Single bus architecture 105 5.2 Crossbar architecture 106 5.3.1 Processor bus activity 109 5.3.2 Memory bus activity 110 5.3.3 Memory addressing example                                                                                                                                                     |   | 3.   | 4 Maximum throughout family                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 44         |

| 3.7       Maximum throughput for a two-level bus hierarchy       68         3.8       Maximum throughput using a binary tree interconnection       72         3.9       High performance bus example       74         3.9.1       Single bus example       75         3.9.2       Two-level bus example       75         3.10       Summary       76         4       TRACE DRIVEN SIMULATIONS       77         4.1       Necessity of simulation techniques       78         4.2       Simulator implementation       79         4.2.1       68020 trace generation and simulation       79         4.2.2       88100 trace generation and simulation       85         4.3       Simulation workload       86         4.4       Results for 68020 example system       86         4.4.1       Markov chain model results for 68020 example       89         4.4.2       Trace driven simulation results for 68020 example       91         4.5       Results for 88100 example system       96         4.5.1       Markov chain model results for 88100 example       90         4.5.2       Trace driven simulation results for 88100 example       100         4.5.3       Accuracy of model for 88100 example       101                                                                                                       |   |      | 5 TTI bus example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 53         |

| 3.6       Maximum throughput using a binary tree interconnection       72         3.9       High performance bus example       74         3.9.1       Single bus example       75         3.9.2       Two-level bus example       75         3.10       Summary       76         4       TRACE DRIVEN SIMULATIONS       77         4.1       Necessity of simulation techniques       78         4.2       Simulator implementation       79         4.2.1       68020 trace generation and simulation       79         4.2.2       88100 trace generation       85         4.3       Simulation workload       86         4.4       Results for 68020 example system       87         4.4.1       Markov chain model results for 68020 example       89         4.4.2       Trace driven simulation results for 68020 example       91         4.5       Results for 88100 example system       96         4.5.1       Markov chain model results for 88100 example       99         4.5.1       Markov chain model results for 88100 example       100         4.5.3       Accuracy of model for 88100 example       101         4.6       Summary of results for single logical bus       101         5       C                                                                                                               |   |      | 6 Optimization of a total and a second secon | 60         |

| 3.9       High performance bus example       74         3.9.1       Single bus example       75         3.9.2       Two-level bus example       75         3.10       Summary       76         4 TRACE DRIVEN SIMULATIONS       77         4.1       Necessity of simulation techniques       78         4.2       Simulator implementation       79         4.2.1       68020 trace generation and simulation       79         4.2.2       88100 trace generation       85         4.3       Simulation workload       86         4.4       Results for 68020 example system       87         4.4.1       Markov chain model results for 68020 example       89         4.4.2       Trace driven simulation results for 68020 example       91         4.5.3       Accuracy of model for 68020 example       92         4.5.1       Markov chain model results for 88100 example       99         4.5.2       Trace driven simulation results for 88100 example       100         4.5.3       Accuracy of model for 88100 example       101         4.6       Summary of results for single logical bus       101         5       Crossborint cache architecture       105         5.3       Crosspoint cache architecture                                                                                                      |   |      | 7 Maximum throughout 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 67         |

| 3.9.1 Single bus example   75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |      | Maximum throughput for a two-level bus hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 68         |

| 3.9.1 Single bus example   75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |      | High performs the binary tree interconnection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 72         |

| 3.9.2 Two-level bus example 75 3.9.2 Two-level bus example 75 3.10 Summary 76  4 TRACE DRIVEN SIMULATIONS 77 4.1 Necessity of simulation techniques 78 4.2 Simulator implementation 79 4.2.1 68020 trace generation and simulation 79 4.2.2 88100 trace generation 85 4.3 Simulation workload 86 4.4 Results for 68020 example system 87 4.4.1 Markov chain model results for 68020 example 89 4.4.2 Trace driven simulation results for 68020 example 91 4.4.3 Accuracy of model for 68020 example 91 4.5 Results for 88100 example system 96 4.5.1 Markov chain model results for 88100 example 99 4.5.2 Trace driven simulation results for 88100 example 99 4.5.3 Accuracy of model for 88100 example 100 4.5.3 Accuracy of model for 88100 example 100 5.3 Simple bus architecture 105 5.1 Crosspoint cache architecture 105 5.2 Crossbar architecture 105 5.3 Crosspoint cache architecture 106 5.3 Crosspoint cache architecture 108 5.3.1 Processor bus activity 109 5.3.2 Memory bus activity 110 5.3.3 Memory addressing example 111                                                                                                                                                                                                                                                                                   |   | ر. د | 8 Forestmance bus example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 74         |

| 3.10 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |      | 3.9.1 Single bus example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 75         |

| 4 TRACE DRIVEN SIMULATIONS       77         4.1 Necessity of simulation techniques       78         4.2 Simulator implementation       79         4.2.1 68020 trace generation and simulation       79         4.2.2 88100 trace generation       85         4.3 Simulation workload       86         4.4 Results for 68020 example system       87         4.4.1 Markov chain model results for 68020 example       89         4.4.2 Trace driven simulation results for 68020 example       91         4.5 Results for 88100 example system       96         4.5.1 Markov chain model results for 88100 example       99         4.5.2 Trace driven simulation results for 88100 example       100         4.5.3 Accuracy of model for 88100 example       101         4.6 Summary of results for single logical bus       101         5 CROSSPOINT CACHE ARCHITECTURE       105         5.1 Single bus architecture       105         5.2 Crossbar architecture       106         5.3.1 Processor bus activity       109         5.3.2 Memory bus activity       110         5.3.3 Memory addressing example       111                                                                                                                                                                                                        |   | 3 1  | 3.9.2 Two-level bus example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 75         |

| 4 TRACE DRIVEN SIMULATIONS       77         4.1 Necessity of simulation techniques       78         4.2 Simulator implementation       79         4.2.1 68020 trace generation and simulation       79         4.2.2 88100 trace generation       85         4.3 Simulation workload       86         4.4 Results for 68020 example system       87         4.4.1 Markov chain model results for 68020 example       89         4.4.2 Trace driven simulation results for 68020 example       91         4.4.3 Accuracy of model for 68020 example       93         4.5 Results for 88100 example system       96         4.5.1 Markov chain model results for 88100 example       99         4.5.2 Trace driven simulation results for 88100 example       100         4.5.3 Accuracy of model for 88100 example       100         4.6 Summary of results for single logical bus       101         5 CROSSPOINT CACHE ARCHITECTURE       105         5.1 Single bus architecture       105         5.2 Crossbar architecture       106         5.3.1 Processor bus activity       109         5.3.2 Memory bus activity       110         5.3.3 Memory addressing example       111                                                                                                                                             |   | 5.1  | O Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 76         |

| 4.1 Necessity of simulation techniques  4.2 Simulator implementation  4.2.1 68020 trace generation and simulation  4.2.2 88100 trace generation  4.3 Simulation workload  4.4 Results for 68020 example system  4.4.1 Markov chain model results for 68020 example  4.4.2 Trace driven simulation results for 68020 example  4.4.3 Accuracy of model for 68020 example  4.5 Results for 88100 example system  4.5.1 Markov chain model results for 88100 example  4.5.2 Trace driven simulation results for 88100 example  4.5.3 Accuracy of model for 88100 example  4.5.4 Summary of results for single logical bus  5 CROSSPOINT CACHE ARCHITECTURE  5.1 Single bus architecture  5.2 Crossbar architecture  5.3 Crosspoint cache architecture  5.3.1 Processor bus activity  5.3.2 Memory bus activity  109  5.3.3 Memory addressing example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4 | TR   | ACE DRIVEN SIMIL ATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |

| 4.2.1 68020 trace generation and simulation 79 4.2.2 88100 trace generation 85 4.3 Simulation workload 86 4.4 Results for 68020 example system 87 4.4.1 Markov chain model results for 68020 example 91 4.4.2 Trace driven simulation results for 68020 example 91 4.4.3 Accuracy of model for 68020 example 93 4.5 Results for 88100 example system 96 4.5.1 Markov chain model results for 88100 example 99 4.5.2 Trace driven simulation results for 88100 example 99 4.5.3 Accuracy of model for 88100 example 100 4.5.3 Summary of results for single logical bus 101 5 CROSSPOINT CACHE ARCHITECTURE 105 5.1 Single bus architecture 105 5.2 Crosspoint cache architecture 106 5.3 Crosspoint cache architecture 108 5.3.1 Processor bus activity 109 5.3.2 Memory bus activity 110 5.3.3 Memory addressing example 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | 4.1  | Necessity of simulation techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 77         |

| 4.2.2 88100 trace generation and simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   | 4.2  | Simulator implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 78         |

| 4.2.2 88100 trace generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |      | 42.1 68020 trace generation and the second s | 79         |

| 4.4 Results for 68020 example system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |      | 4.2.2 88100 trace generation and simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 79         |