# Realizing Software Defined Radio – A Study in Designing Mobile Supercomputers

by

### Yuan Lin

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 2008

Doctoral Committee:

Associate Professor Scott A. Mahlke, Co-Chair Professor Trevor N. Mudge, Co-Chair Professor Marios C. Papaefthymiou Associate Professor Dennis M. Sylvester Professor Chaitali Chakrabarti, Arizona State University

#### ABSTRACT

#### Realizing Software Defined Radio – A Study in Designing Mobile

Supercomputers

by

Yuan Lin

Co-Chairs: Scott A. Mahlke and Trevor N. Mudge

The physical layer of most wireless protocols is traditionally implemented in custom hardware to satisfy the heavy computational requirements while keeping power consumption to a minimum. These implementations are time consuming to design and difficult to verify. A programmable hardware platform capable of supporting software implementations of the physical layer, or Software Defined Radio (SDR), has a number of advantages. These include support for multiple protocols, faster time-to-market, higher chip volumes, and support for late implementation changes. The challenge is to achieve this under the power budget of a mobile device. Wireless communications belong to an emerging class of applications with the processing requirements of a supercomputer but the power constraints of a mobile device – *mobile supercomputing*.

This thesis presents a set of design proposals for building a programmable wireless communication solution. In order to design a solution that can meet the lofty requirements of SDR, this thesis takes an application-centric design approach – evaluate and optimize all aspects of the design based on the characteristics of wireless communication protocols. This includes a DSP processor architecture optimized for wireless baseband processing, wireless algorithm optimizations, and language and compilation tool support for the algorithm software and the processor hardware. This thesis first analyzes the software characteristics of SDR. Based on the analysis, this thesis proposes the Signal-Processing On-Demand Architecture (SODA), a fully programmable multi-core architecture that can support the computation requirements of third generation wireless protocols, while operating within the power budget of a mobile device. This thesis then presents wireless algorithm implementations and optimizations for the SODA processor architecture. A signal processing language extension (SPEX) is proposed to help the software development efforts of wireless communication protocols on SODA-like multi-core architecture. And finally, the SPIR compiler is proposed to automatically map SPEX code onto the multi-core processor hardware. © <u>Yuan Lin</u> 2008 All Rights Reserved

To my Shepherd, mom, dad, and Jen

#### ACKNOWLEDGEMENTS

First and foremost, I would like to thank God – Father, Son and Spirit. Without His love and guidance, I would be lost. I am grateful that He has led me to complete my graduate study at the University of Michigan. Hindsight is always 20/20. I see now through all the difficulties that He is there with me, guiding me and loving me.

I would like to thank both of my advisors, Prof. Trevor Mudge and Prof. Scott Mahlke, for their guidance and support. Without them, this thesis would not have be possible. Both have been excellent mentors to me. It is a great privilege to have worked with both of them. They have provided me with invaluable guidance, support, and opportunities to succeed. I would like to thank Prof. Chaitali Chakrabarti for being my "unofficial PhD advisor". It has been a pleasure working with you. Your helpful insights have made a great impact on my graduate work. I would also like to thank the other members of my dissertation committee, Prof. Marios Papaefthymiou and Prof. Dennis Sylvester. Thank you both for your time and valuable comments.

The work presented in this thesis is a collaboration between many graduate students. It would not have been possible without the help of my colleagues. I would like to thank Hyunseok Lee for his invaluable expertise on wireless communication protocols. Mark Woh and Yoav Harel both have helped me tremendously with the SODA processor's power analysis. They also have contributed greatly in the design of the SODA processor architecture. Yoonseo Choi was responsible for constructing parts of the compiler system. Without the help of my colleagues, I would have struggled much longer in my PhD journey.

I also had the chance to met many of my fellow graduate students. They made my graduate experiences much more fun and rewarding. I would like to thank Zaher Andraus, Geoff Blake, Jason Blome, Yoonseo Choi, Mike Chu, Nate Clark, Ganesh Dasika, Kevin Fan, Shuguang Feng, Shantanu Gupta, Jeff Hao, Yoav Harel, Amir Hormati, Taeho Kgil, Manjunath Kudlur, Hyunseok Lee, Mojtaba Mehrara, Robert Mullenix, Hyunchul Park, Dave Roberts, Sangwon Seo, Mark Woh, and Hongtao Zhong. I have become good friends with many of them, and I will cherish their friendships for the rest of my life.

Finally, I would like to thank my family. Mom and dad, thank you so much for all of the love and sacrifice that you have done for me. Without you, I won't even get the chance to write this thesis. I am eternally indebted to you. My wife Jennifer Wang, you are a ray of sunshine in my life. I consider myself truly blessed to have married you. You are my best friend and best supporter for the past six years. I can't even begin to imagine my life without you. You are the reason that I am able to finish this PhD thesis. Thank you.

# TABLE OF CONTENTS

| DEDIC  | ATION                        | Iii                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACKN   | OWLE                         | DGEMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| LIST O | F FIG                        | URES                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CHAPT  | ΓERS                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1      | Introdu<br>1.1<br>1.2<br>1.3 | action1Contribution3Organization6Acknowledgements7                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2      | The W<br>2.1<br>2.2<br>2.3   | -CDMA Wireless Communication Protocol9Protocol Overview10Workload Analysis12Summary16                                                                                                                                                                                                                                                                                                                                                                            |

| 3      | 3.1<br>3.2<br>3.3<br>3.4     | A DSP Architecture For SDR17Introduction17W-CDMA Analysis Overview183.2.1System-level Behavior183.2.2Algorithm-level Behavior19Architectural Design Tradeoffs for SDR20SODA Architecture for SDR223.4.1Architecture Overview223.4.2Arithmetic Data Precisions263.4.3Vector Permutation Operations273.4.4Long Vector Arithmetic Operations273.4.5Vector-Scalar Move Operations293.4.7Vector Alignment Through Programmable DMA.313.4.8Embedded Low-power Design31 |

|        | 3.5                          | SIMD Design Tradeoffs                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   | 3.6   | Experimental Evaluation                            | ••• |     |     |   |   | 36       |

|---|-------|----------------------------------------------------|-----|-----|-----|---|---|----------|

|   |       | 3.6.1 Protocol System Implementations              | ••• |     |     |   |   | 37       |

|   |       | 3.6.2 Performance and Power Results                | ••• |     |     |   |   | 39       |

|   |       | 3.6.3 The Cost of Programmability                  | ••• |     |     |   |   | 43       |

|   | 3.7   | Summary                                            |     |     |     |   |   | 44       |

| 4 |       |                                                    |     |     |     |   |   | 45       |

| 4 |       | MA Algorithm Implementations                       |     |     |     |   |   | 45       |

|   | 4.1   | Introduction                                       |     |     |     |   |   | 45       |

|   | 4.2   | FIR Filter                                         |     |     |     |   |   | 46       |

|   | 4.3   | Rake Receiver                                      |     |     |     |   |   | 48       |

|   |       | 4.3.1 Searcher                                     |     |     |     |   |   | 50       |

|   |       | 4.3.2 Rake Fingers and Combiner                    |     |     |     |   |   | 51       |

|   | 4.4   | Convolutional Decoder                              |     |     |     |   |   | 53       |

|   | 4.5   | Turbo Decoder                                      |     |     |     |   |   | 56       |

|   |       | 4.5.1 Performance Results                          |     |     |     |   |   | 59       |

|   |       | 4.5.2 Related Work                                 |     |     |     |   |   | 63       |

|   | 4.6   | Summary                                            |     | ••• |     | • | • | 63       |

| 5 | The A | RM Ardbeg SDR Processor                            |     |     |     |   |   | 64       |

|   | 5.1   | Introduction                                       |     |     |     |   |   | 64       |

|   | 5.2   | Architectural Overview                             |     |     |     |   |   | 66       |

|   | 0.1   | 5.2.1 SODA Architectural Overview                  |     |     |     |   |   | 67       |

|   |       | 5.2.2 Ardbeg Architecture                          |     |     |     |   |   | 69       |

|   | 5.3   | Architectural Evolution From SODA to Ardbeg        |     |     |     |   |   | 70       |

|   | 0.0   | 5.3.1 Optimized Wide SIMD Design                   |     |     |     |   |   | 70       |

|   |       | 5.3.2 LIW SIMD Execution                           |     |     |     |   |   | 75       |

|   |       | 5.3.3 Application Specific Hardware Acceleration . |     |     |     |   |   | 77       |

|   |       | 5.3.4 Hardware Support for Multi-core Scheduling   |     |     |     |   |   | 82       |

|   | 5.4   | Results and Analysis                               |     |     |     |   |   | 83       |

|   | 0.1   | 5.4.1 Wireless Protocols Results                   |     |     |     |   |   | 85       |

|   |       | 5.4.2 Wireless Algorithms Analysis                 |     |     |     |   |   |          |

|   |       | 5.4.3 Wireless Algorithm Power Breakdown           |     |     |     |   |   |          |

|   | 5.5   | DSP Processor Architecture Survey                  |     |     |     |   |   | 91       |

|   | 0.0   | 5.5.1 SIMD-based SDR Processor Architecture        |     |     |     |   |   | 92       |

|   |       | 5.5.2 Reconfigurable SDR Processor Architectures   |     |     |     |   |   | 92<br>93 |

|   |       | 5.5.3 VLIW-based DSP Architectures                 |     |     |     |   |   | 95<br>95 |

|   |       | 5.5.4 Vector/SIMD based Multi-media Solutions .    |     |     |     |   |   | 95<br>95 |

|   | 5.6   | Summary                                            |     |     |     |   |   | 96       |

|   | 0.0   | Sammary                                            |     | ••• | ••• | • | • | 00       |

| 6 |       | age Extensions for Software Defined Radio          |     |     |     |   |   | 97       |

|   | 6.1   | Introduction                                       |     |     |     |   |   | 97       |

|   | 6.2   | Modeling Wireless Protocols                        |     |     |     |   |   | 99       |

|   |       | 6.2.1 Streaming Computation in Wireless Protocols  | •   |     |     |   | • | 100      |

|   |       | 6.2.2 Parameterized Dataflow Model (PDF)           |     |     |     |   | • | 101      |

|   |       | 6.2.3 Modeling Streaming Communications            | ••• |     |     |   | • | 103      |

| 6.3       | SPEX Extensions for Streaming Computation       | 106 |

|-----------|-------------------------------------------------|-----|

|           | 6.3.1 Overview                                  | 107 |

|           | 6.3.2 SPEX Streaming Types                      | 108 |

|           | 6.3.3 SPEX Streaming Functions                  |     |

|           | 6.3.4 SPEX Streaming Constructs                 |     |

|           | 6.3.5 Implementing DSP Algorithm Kernels        |     |

|           | 6.3.6 Implementing Memory Buffers               | 117 |

|           | 6.3.7 Implementing DSP Systems                  | 121 |

| 6.4       | Related Work                                    | 124 |

| 6.5       | Summary                                         | 125 |

| 7 Compi   | lation Support for the Ardbeg processor         | 126 |

| 7.1       | Introduction                                    | 126 |

| 7.2       | The SPIR Compiler                               | 130 |

|           | 7.2.1 Rationales for Function-level Compilation | 130 |

|           | 7.2.2 Overall Compiler Infrastructure           | 131 |

|           | 7.2.3 SPIR Intermediate Representation          | 133 |

|           | 7.2.4 Input and Output Language Formats         | 133 |

|           | 7.2.5 Experimentation Infrastructure            | 136 |

| 7.3       | From SPEX to SPIR: Frontend Compilation         |     |

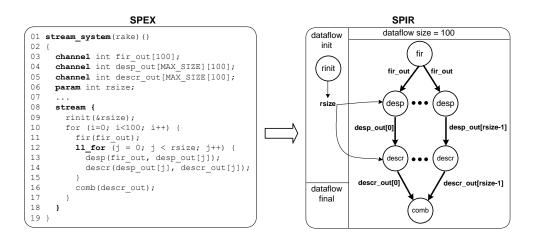

|           | 7.3.1 Basic Dataflow                            | 137 |

|           | 7.3.2 Parameterized Dataflow                    | 139 |

| 7.4       | Function-level Scheduling and Optimizations     | 141 |

|           | 7.4.1 Scheduling Overview                       | 142 |

|           | 7.4.2 Coarse-grained Software Pipelining        |     |

| 7.5       | From SPIR to SocC: Code Generation              |     |

|           | 7.5.1 Predicated Execution                      |     |

|           | 7.5.2 Memory Buffers and DMA Operations         |     |

|           | 7.5.3 SocC Output Example                       |     |

| 7.6       | Related Work                                    |     |

| 7.7       | Summary                                         | 152 |

| 8 Conclu  | usion                                           | 153 |

| 8.1       | Summary                                         |     |

| 8.2       | Future Work                                     | 155 |

| BIBLIOGRA | РНҮ                                             | 157 |

## LIST OF FIGURES

| Figure |

|--------|

|--------|

| 1.1        | Throughput and power requirements of typical 3G wireless protocols. The results are calculated for 16-bit fixed point operations.                                                                                                                                                                                                                                           | 2                                      |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 2.1        | Physical layer operation of W-CDMA wireless protocol. Each block in-<br>cludes the algorithm's name, vector or scalar computation, vector width,<br>and the data precision. The algorithms are also grouped into four cate-<br>gories, shown in shaded boxes: filtering, modulation, channel estimation,                                                                    |                                        |

|            | and error correction.                                                                                                                                                                                                                                                                                                                                                       | 10                                     |

| 2.2        | Workload analysis result of W-CDMA physical layer processing. "Vector<br>comp" indicates whether the algorithm contains vector-based arithmetic<br>operations. "Vector width" lists the native computation vector width. "Bit<br>width" lists the data precision width. "Comp Mcycle/sec" lists the cycle-<br>count of running the algorithm on a general purpose processor | 12                                     |

| 2.3        | Memory requirements for the W-CDMA physical layer algorithms. "KB" is                                                                                                                                                                                                                                                                                                       | 12                                     |

| 2.0        | the memory size requirement in KByte. "MBps" is the memory through re-<br>quirement in KByte-per-second. "Input buffer and output buffer" are the<br>IO memory requirements. "Scratchpad" is the internal memory require-<br>ment. As shown in the figure, the overall memory size and throughput<br>requirements for W-CDMA is not very high. Majority of which come from  |                                        |

| 3.1        | scratchpad memory access of intermediate computation results SODA Architecture for SDR. The system consists of 4 data processing                                                                                                                                                                                                                                            | 15                                     |

| 0.1        | elements (PEs), 1 control processor, and global scratchpad memory, all<br>connected through a shared bus. Each PE consists of a 32-wide 16-bit<br>SIMD pipeline, a 16-bit scalar pipeline, two local scratchpad memories, an<br>Address-Generation-Unit(AGU) for calculating memory addresses, and a                                                                        | 0.0                                    |

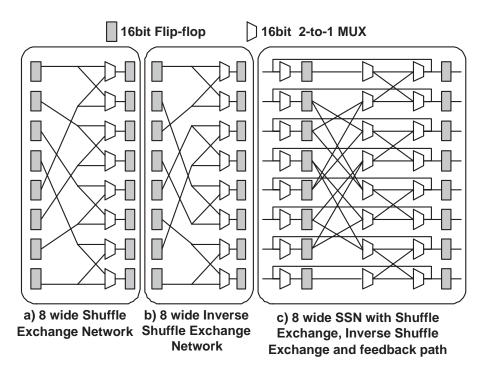

| 3.2        | Direct-Memory-Access (DMA) unit for inter-processor data transfer 8-wide SIMD Shuffle Network(SSN)                                                                                                                                                                                                                                                                          | $\begin{array}{c} 23\\ 24 \end{array}$ |

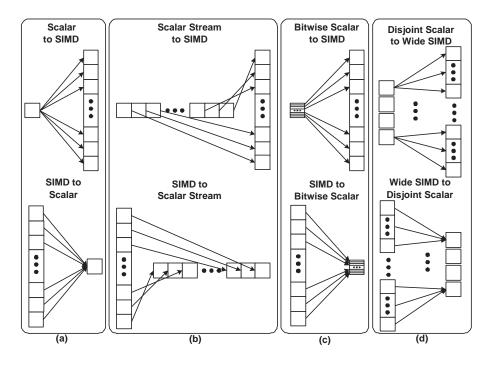

| 3.2<br>3.3 | Scalar-SIMD Operations for Various DSP Algorithms                                                                                                                                                                                                                                                                                                                           | $\frac{24}{28}$                        |

| 3.4        | Special Intrinsic Operations                                                                                                                                                                                                                                                                                                                                                | 30                                     |

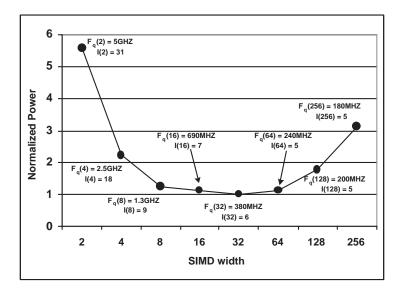

| 3.5        | Average normalized power of a 4-PE configuration for achieving the com-<br>putational requirements of W-CDMA and 802.11a in 180nm technology                                                                                                                                                                                                                                | 33                                     |

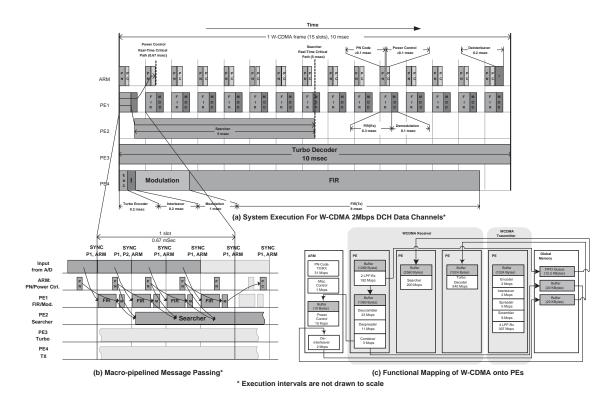

| 3.6        | W-CDMA 2Mbps DCH data channel implementation. The kernel mapping                                                                       |    |

|------------|----------------------------------------------------------------------------------------------------------------------------------------|----|

|            | is shown with the algorithm mapping and memory allocation on the PEs,                                                                  |    |

|            | control processor, and global memory. The execution trace is shown with                                                                |    |

|            | two periodic real-time deadlines: power control and searcher. $\ldots$ .                                                               | 38 |

| 3.7        | Kernel Algorithms in W-CDMA and 802.11a and their performance on a                                                                     |    |

|            | GPP and SODA.                                                                                                                          | 40 |

| 3.8        | System Area and Power Summary                                                                                                          | 41 |

| 3.9        | Power efficiency comparison between SODA-based and ASIC implementa-                                                                    |    |

|            | tions for FIR filter and Turbo decoder. The Turbo decoder ASIC data are                                                                |    |

|            | taken from TI Turbo Coprocessor [26], and FIR filter ASIC data are taken from [77]                                                     | 43 |

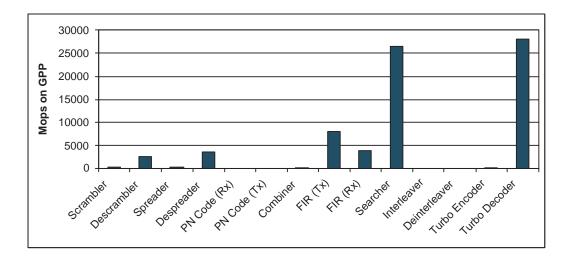

| 4.1        | 2Mbps W-CDMA workload profile in Mops on a general purpose processor                                                                   |    |

|            | $(GPP) \ldots $ | 46 |

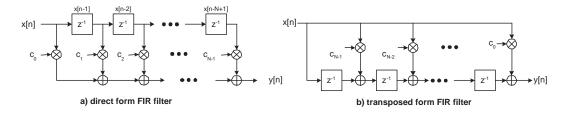

| 4.2        | FIR filters expressed in direct form and transposed form. The two filter forms are mathematically equivalent                           | 47 |

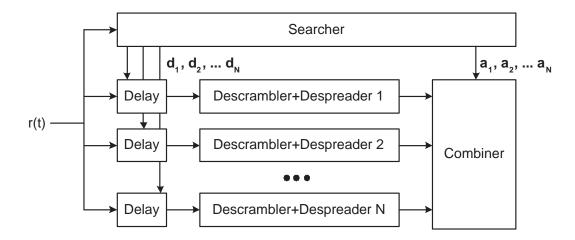

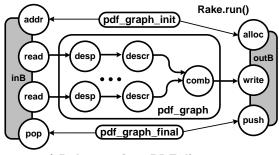

| 4.3        | W-CDMA rake receiver. It consists of a searcher, despreader/descrambler                                                                | 41 |

| 4.3        | pairs, and a combiner. Due to multi-path fading effect, a searcher is used to                                                          |    |

|            | find the synchronization points for each delayed version of the same signal                                                            |    |

|            | stream. Each despread/descrambler pair correspond to one of the delayed                                                                |    |

|            | signal stream. And the combiner combines the different paths together                                                                  | 48 |

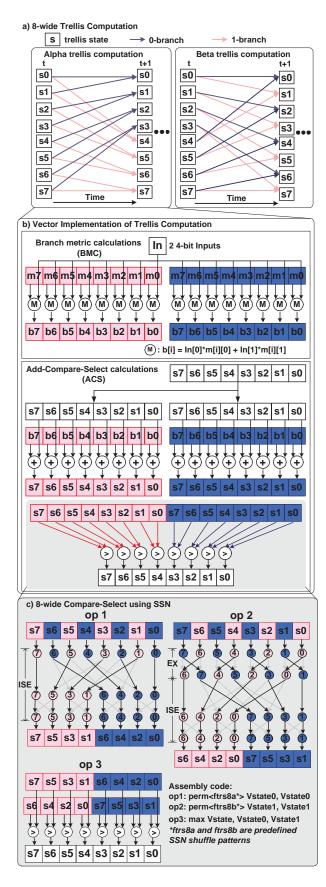

| 4.4        | Trellis state computation, and SIMD implementation using the SSN                                                                       | 55 |

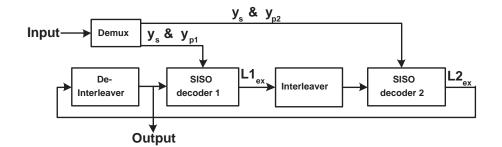

| 4.5        | Block Diagram of a Turbo Decoder                                                                                                       | 56 |

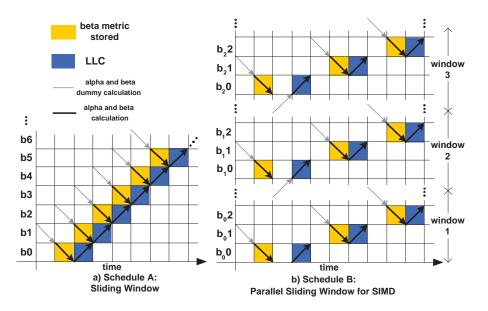

| 4.6        | Parallel MAX-Log-MAP Scheduling                                                                                                        | 57 |

| 4.0<br>4.7 | Computation time of 1 iteration of Turbo decoding for parallel processing                                                              | 51 |

| 4.1        | vs. parallel processing with overlapping interleaving                                                                                  | 59 |

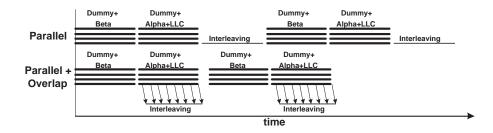

| 5.1        | SODA and Ardbeg architectural diagrams, and a summary of the key ar-                                                                   |    |

| 0.1        | chitectural features of the two designs                                                                                                | 68 |

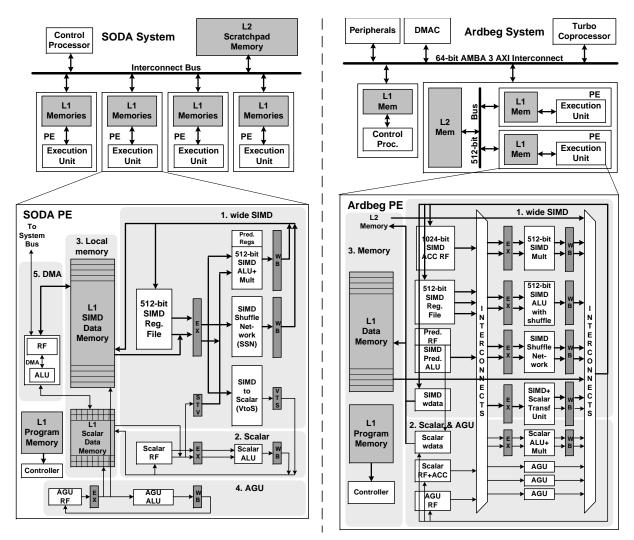

| 5.2        | Plots of normalized energy, delay, and energy-delay product versus area                                                                |    |

|            | plots for different Ardbeg SIMD width configurations running 3G Wireless                                                               |    |

|            | algorithms. The results are normalized to the 8-wide SIMD design                                                                       | 71 |

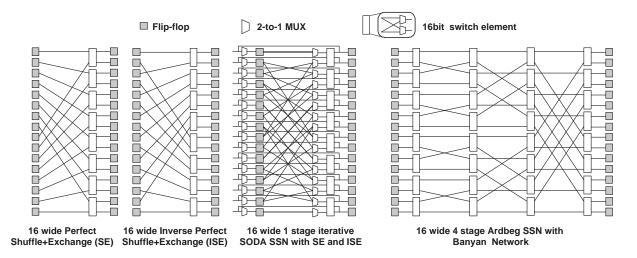

| 5.3        | SIMD shuffle network for the SODA PE and the Ardbeg PE. For illustration                                                               |    |

|            | clarity, these examples show 16-wide shuffle networks. The SODA PE has                                                                 |    |

|            | a 32-wide 16-bit 1-stage iterative shuffle network, and the Ardbeg PE has                                                              |    |

|            | a 128-lane 8-bit 7-stage Banyan shuffle network                                                                                        | 72 |

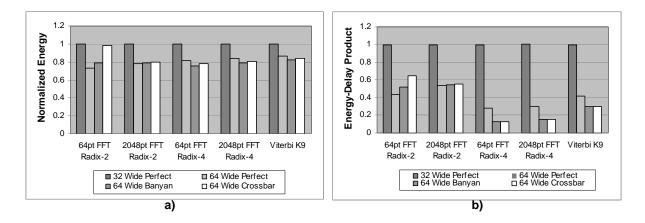

| 5.4        | Normalized energy and energy-delay product for key SDR algorithms run-                                                                 |    |

|            | ning on Ardbeg for different shuffle network topologies                                                                                | 73 |

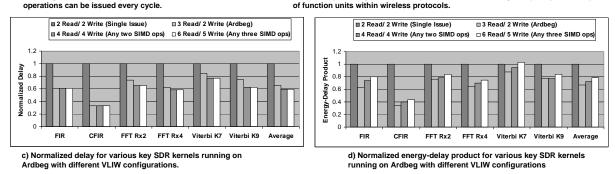

| 5.5        | Ardbeg VLIW support. Ardbeg has 7 different function units, as listed in                                                               |    |

|            | sub-figure a. These seven function units share 3 SIMD register file read                                                               |    |

|            | and 2 write ports. At most two SIMD operations can be issued per cycles,                                                               |    |

|            | and not all combinations of SIMD operations are supported. Different LIW                                                               |    |

|            | configurations are evaluated in terms of delay and energy-delay product, as                                                            |    |

|            | shown in sub-figure c and d. The results are shown for software pipelined                                                              |    |

|            | Ardbeg assembly code                                                                                                                   | 75 |

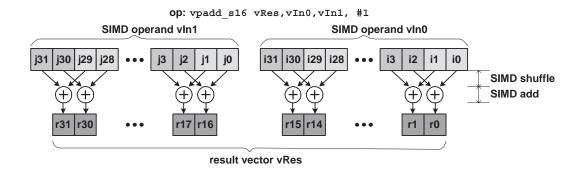

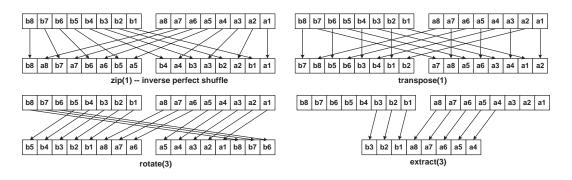

| 5.6        | Ardbeg's pair-wise butterfly SIMD operation implemented using a fused                                                                                    |    |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|            | permute and ALU operation. The figure shows pairs of 2-element butterfly.                                                                                |    |

|            | Ardbeg supports pairs of 1-,2-,4-,8-,and 16-element butterfly of 8- and 16-<br>bits. This butterfly uses the inverse perfect shuffle pattern because the |    |

|            | input to each SIMD ALU lane must come from the 2 inputs of the same                                                                                      |    |

|            |                                                                                                                                                          | 80 |

| 57         |                                                                                                                                                          | 81 |

| 5.7        |                                                                                                                                                          | 01 |

| 5.8        | DSP algorithms that are used in W-CDMA, 802.11a and DVB wireless protocols.                                                                              | 83 |

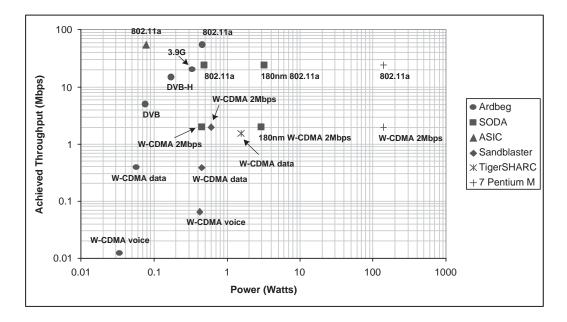

| 5.9        | Throughput and power achieved for SODA and Ardbeg for W-CDMA,                                                                                            |    |

|            | 802.11a and DVB. ASIC 802.11a, Pentium M, Sandblaster, and ADI Tiger-                                                                                    |    |

|            | Sharc results are also included for comparison purposes. Results are shown                                                                               |    |

|            | for processors implemented in 90nm, unless stated otherwise                                                                                              | 85 |

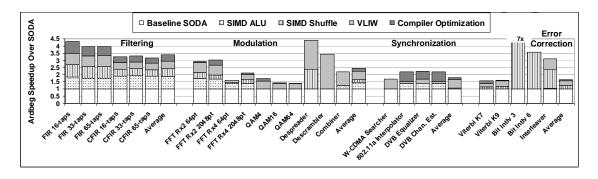

| 5.10       | Ardbeg speedup over SODA for the key DSP algorithms used in our wire-                                                                                    |    |

|            | less protocol benchmarks. The speedup is broken down into the different                                                                                  |    |

|            | architectural optimizations. These include optimized SIMD ALU, wider                                                                                     |    |

|            | 1-cycle SIMD shuffle network, reduced SIMD memory latencies through                                                                                      |    |

|            |                                                                                                                                                          | 86 |

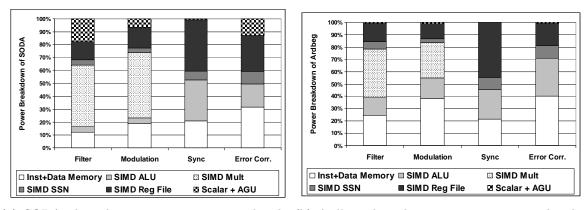

| 5.11       | SODA and Ardbeg power consumption breakdown for the four key kernel                                                                                      |    |

|            | algorithms. The power consumptions are normalized to their respective total.                                                                             | 90 |

| 5.12       | Architectural comparison summary between proposed SIMD-based SDR                                                                                         |    |

|            | processors. *For the Icera DXP and the Phillips EVP, some of the archi-                                                                                  |    |

|            | 1                                                                                                                                                        | 92 |

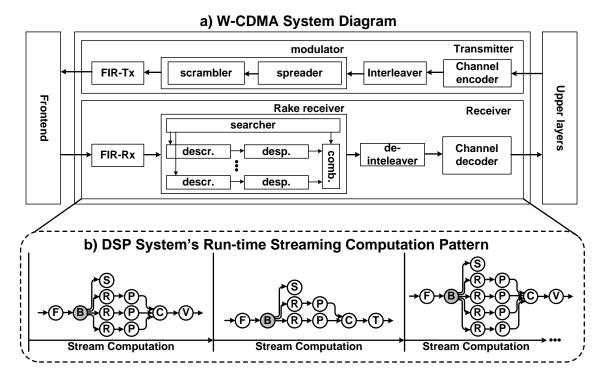

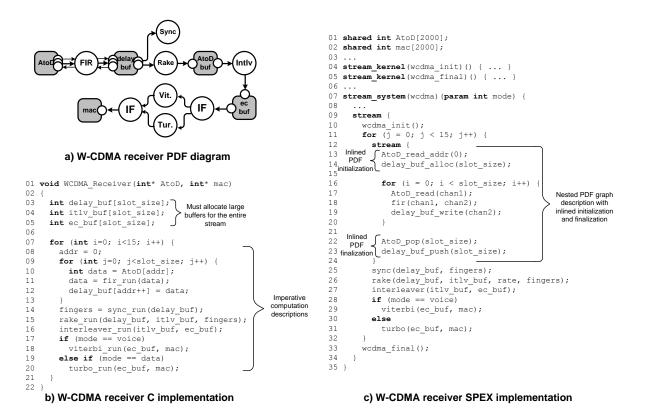

| 6.1        | Part a: W-CDMA System Level Diagram. W-CDMA is used as the on-                                                                                           |    |

|            | going example for SPEX in this study. Part b: DSP system run-time                                                                                        |    |

|            | streaming computation pattern. The receiver may use different number of                                                                                  |    |

|            | rake fingers (denoted by the R and P nodes) and different channel decoding                                                                               |    |

|            | algorithms (denoted by the T and V nodes). Shaded B nodes are memory                                                                                     | 00 |

| <b>C D</b> | buffers                                                                                                                                                  | 00 |

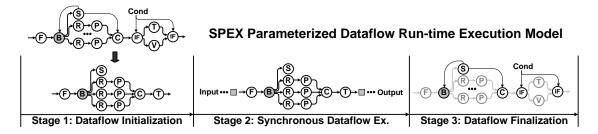

| 6.2        | PDF execution model consists of three steps. Step 1, the parameterized                                                                                   |    |

|            | dataflow graph is constrained into a synchronous dataflow graph. Step 2,<br>the dataflow is executed following a static compile time schedule. Step 2    |    |

|            | the dataflow is executed following a static compile-time schedule. Step 3,<br>PDF graph's data and states are undated with the most recent computed      |    |

|            | PDF graph's data and states are updated with the most recent computed values                                                                             | 02 |

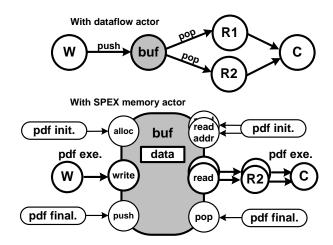

| 6.3        | Example of a vector stream buffer with 1 writer and 2 readers. This buffer's                                                                             | 02 |

| 0.5        | communication pattern has all four streaming properties. This is a vec-                                                                                  |    |

|            | tor buffer, which requires multi-dimensional streaming patterns. Its has                                                                                 |    |

|            | non-sequential streaming patterns because its readers must periodically                                                                                  |    |

|            | reconfigure their streaming addresses. The writer and readers are decou-                                                                                 |    |

|            | pled because they have different real-time deadlines. This is also a shared                                                                              |    |

|            | memory buffer because the readers share the same data, but have different                                                                                |    |

|            | streaming patterns                                                                                                                                       | 05 |

| 6.4        | SPEX language constructs for describing dataflow operations                                                                                              |    |

| 0.1        |                                                                                                                                                          | 10 |

| 6.5 | DSP algorithm kernel example - FIR filter. The keyword stream_kernel                                                                                                                                                                                                                                                                                                                                                            | 110   |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 6.6 | is on line 1 to indicate that this is a PDF actor function                                                                                                                                                                                                                                                                                                                                                                      | 110   |

|     | clared with the keyword <b>spex_memory</b> (on line 2). This example implements                                                                                                                                                                                                                                                                                                                                                 | 110   |

| 6.7 | the same buffer shown in Figure 6.3                                                                                                                                                                                                                                                                                                                                                                                             | 110   |

|     | the PDF graph execution; and pdf_graph_final is used to describe the                                                                                                                                                                                                                                                                                                                                                            | 1.0.0 |

| 6.8 | PDF graph finalization                                                                                                                                                                                                                                                                                                                                                                                                          | 120   |

| 0.0 | implementations of the receiver                                                                                                                                                                                                                                                                                                                                                                                                 | 123   |

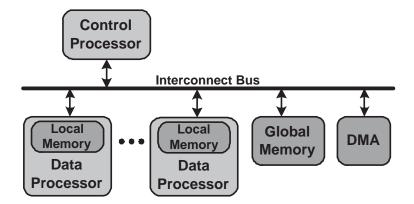

| 7.1 | SDR control-data decoupled MPSoC architecture consisting of one general-<br>purpose control processor, multiple data processors, and a hierarchical<br>scratchpad memory system that are all interconnected with a bus                                                                                                                                                                                                          | 127   |

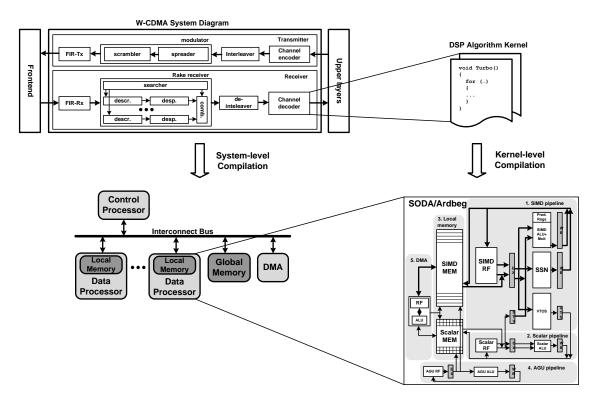

| 7.2 | Two-tier compilation approach for SODA and Ardbeg processors. On the<br>system-level, the compiler deal with coarse-grained compilation challenges,<br>such as function-to-processor assignments and DMA operations. On the<br>kernel-level, the compiler deal with fine-grained compilation challenges,<br>such as VLIW scheduling and vectorization for SIMD processors. The                                                  |       |

|     | SPIR compiler is a system-level compiler that only address the coarse-<br>grained compilation challenges.                                                                                                                                                                                                                                                                                                                       | 128   |

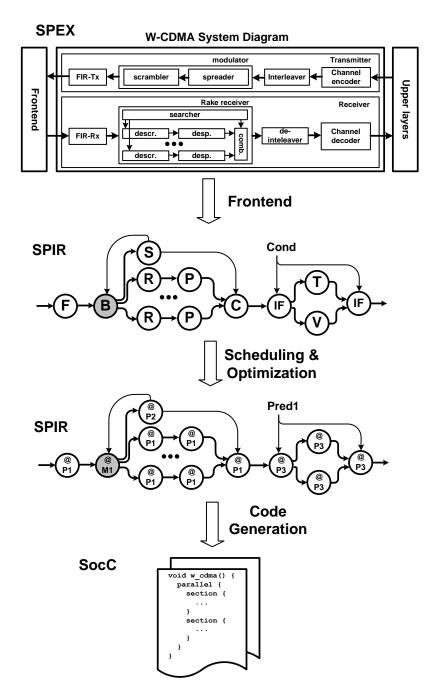

| 7.3 | The overall SPIR compilation flow. The input is written in C with SPEX<br>language extensions. The frontend translates the input into a SPIR dataflow<br>graph. Dataflow scheduling and optimizations are applied to the SPIR<br>dataflow graph by annotating the dataflow actors with processor assign-<br>ments and memory allocations. The code generation then translate the<br>SPIR graph into SocC multi-threading C code | 132   |

| 7.4 | SocC programming example. SocC allows programmers to explicitly par-<br>allelize a program without the complexity of writing the code for explicit<br>thread management. PE0-PE2 refer to the Ardbeg data processors. DMEM0-                                                                                                                                                                                                    |       |

| 7.5 | DMEM2 refer to Ardbeg data processors' local memories                                                                                                                                                                                                                                                                                                                                                                           | 194   |

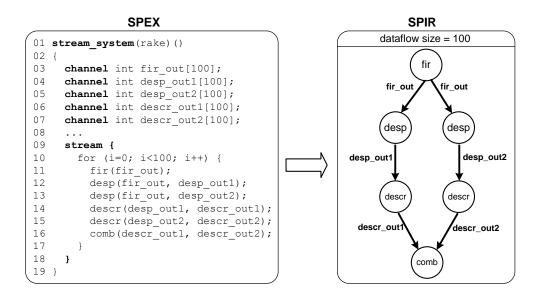

|     | its corresponding SPIR PDF representation.                                                                                                                                                                                                                                                                                                                                                                                      | 137   |

| 7.6 | This diagram describes a stream construct with the if-else construct, and its corresponding SPIR boolean dataflow representation.                                                                                                                                                                                                                                                                                               | 140   |

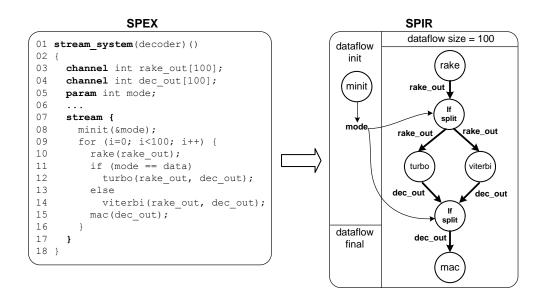

| 7.7 | This diagram describes a stream construct with the ll-for construct, and its corresponding SPIR reconfigurable dataflow representation.                                                                                                                                                                                                                                                                                         |       |

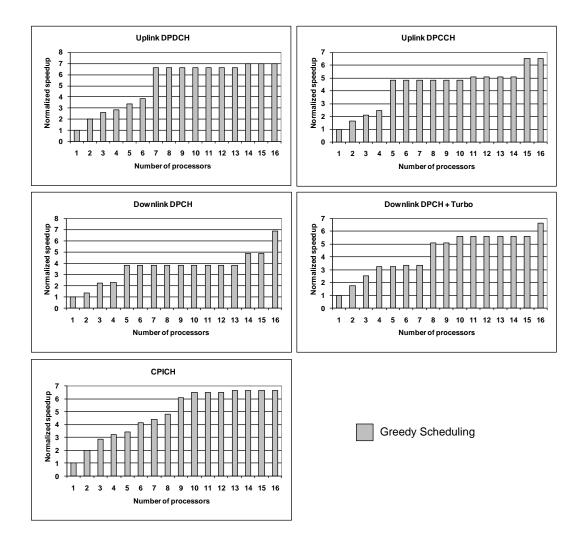

| 7.8 | Execution speedup for W-CDMA benchmarks compiled by greedy modulo scheduler running on 1 to 16 data processors.                                                                                                                                                                                                                                                                                                                 | 146   |

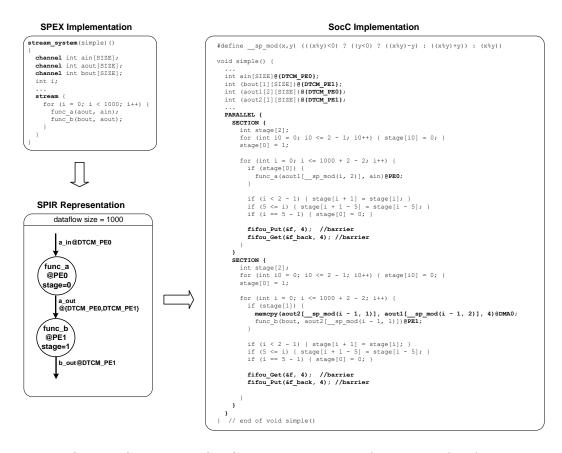

| 7.9 | SPEX, SPIR, and SocC implementation of a simple feedforward dataflow      |

|-----|---------------------------------------------------------------------------|

|     | containing two actors. The SPEX implementation is the input of the SPIR   |

|     | compiler, and the SocC implementation is the output of the SPIR compiler. |

|     | In the SocC implementation, the dataflow is mapped onto two Ardbeg PEs,   |

|     | and is software pipelined into two stages                                 |

## CHAPTER 1

## Introduction

Untethered digital devices are already ubiquitous. The world has over 3.3 billion active cell phones [8], each a sophisticated multiprocessor. With worldwide wireless semiconductor revenue totaled \$24.3 billion in 2005, mobile terminals have arguably become one of the dominant computing platforms. We expect to see both the types and numbers of mobile digital devices increase in the near future. New technologies will improve the mobile phone by incorporating advanced multi-media functionalities. They will also improve the laptop by shrinking the form factor and increasing its battery life. These trends have blurred the line between traditional desktop computing and mobile cellular phones. We are in an era where users are no longer satisfied with computing powers that are confined to their homes or offices. Instead, users want to bring computing powers to wherever they are and whenever they want. To achieve this, we require software applications with the extraordinary computational requirement of a supercomputer running on the power budget of a mobile device – mobile supercomputers [12].

Software Defined Radio (SDR) is one of these mobile supercomputing applications. It promises to deliver a cost effective and flexible mobile communication solution by implementing the wide variety of the wireless protocols in software. The operation throughput

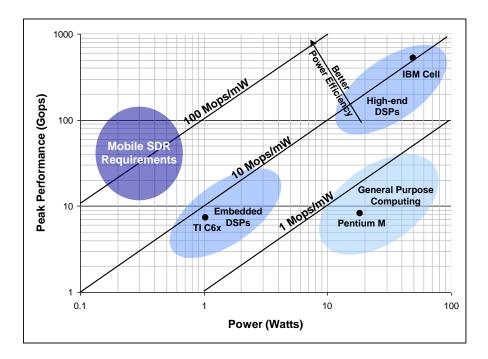

Figure 1.1: Throughput and power requirements of typical 3G wireless protocols. The results are calculated for 16-bit fixed point operations.

requirements of current third-generation (3G) wireless protocols are already an order of magnitude higher than the capabilities of modern DSP processors. This gap is likely to grow in the future. Figure 1 shows the computation and power demands of a typical 3G wireless protocol. Although most DSP processors operate at an efficiency of approximately 10 million operations per second (Mops) per milliwatt (mW), the typical wireless protocol requires 100 Mops/mW. Hence, most wireless protocols to date have been implemented with custom hardware. Although custom hardware can meet the operational requirements, a programmable solution offers many potential advantages:

- A programmable architecture would allow multimode operation, running different protocols depending on the available wireless network-GSM in Europe, CDMA in the USA and some parts of Asia, and 802.11 in coffee shops. This is possible with less hardware than custom implementations require.

- A protocol implementation's time to market would be shorter because it could reuse the hardware. The hardware integration and software development tasks could progress in parallel.

- Prototyping and bug fixes would be possible for next-generation protocols on existing silicon through software changes. The use of a programmable solution would support the specification's continuing evolution; after the chipset's manufacture, developers could deploy algorithmic improvements by changing the software without redesign.

- Chip volumes would be higher because the same chip could support multiple protocols without requiring hardware changes.

#### 1.1 Contribution

In the foreseeable future, it is likely that many mobile communication devices are going to be supported by SDR technology. This thesis presents a set of design proposals for realizing a programmable wireless protocol implementation. In order to design a solution that can meet the lofty requirements of SDR, this thesis takes an application-centric approach – evaluate and optimize all aspects of the design based on the characteristics of wireless communication protocols. Because SDR is an interdisciplinary research topic, this thesis examines multiple research subjects under the overall objective of realizing SDR: computer architecture, DSP algorithm optimizations, programming language design, and compiler construction. We must first understand the workings of wireless protocols and their algorithms. A DSP processor is then designed and optimized for wireless communication algorithms. These wireless algorithms must also be optimized for the DSP architecture. Language and compilation support must be provided to bridge the gap between the programmers and the hardware. This thesis makes the following contributions:

- A programmable multiprocessor architecture, SODA, for supporting third generation wireless protocols within the power budget of a mobile device.

- Design and implementation of wireless protocol's DSP algorithms for SODA.

- A comparison study between the SODA processor and the Ardbeg processor. The Ardbeg DSP processor is a commercial prototype based on the SODA architecture.

- A programming language extension, SPEX, for describing wireless protocols.

- A proposed multiprocessor compiler, SPIR, for the Ardbeg processor.

Wireless Protocol Analysis. Wireless protocols are collections of disparate DSP algorithm kernels working together as one system. It requires both the implementation of each algorithm as well as the construction of the entire system with the algorithms as building blocks. The DSP algorithms consist mostly of long vector arithmetic operations. The system consists of streaming computation where data are processed sequentially through a pipeline of DSP functions.

Software protocol processing provides many advantages over hard-wired solutions. However, the performance requirements for current generation wireless protocols are an order of magnitude higher than the capabilities of modern general purpose and DSP processors. This thesis chooses the W-CDMA wireless protocol as our case study. Workload profiling shows that the 2Mbps W-CDMA baseband processing requires the computational power of approximately seven Pentium 4 processors. In addition, a mobile SDR processor must run on the power budget of a mobile terminal. A typical mobile device allocates around 0.5 Watt for baseband processing, whereas typical general purpose processors consume over 20 Watts.

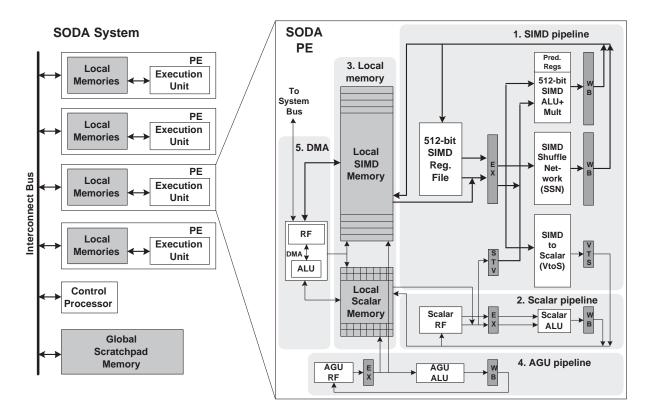

**Processor Design.** This thesis proposes a multi-core DSP architecture, SODA, for supporting SDR. SODA consists of one control processor, four data processors, and a shared global memory. The control processor is an embedded general purpose processor that is capable of handling the control-intensive code that is used to manage the overall baseband processing system. The data processors are specialized DSP processors that can perform data-intensive computations.

Because the biggest challenge is meeting the computation requirements while operating within the embedded power envelope, the focus is on designing a power-efficient data processor. Therefore, we picked an existing low-power embedded processor, ARM Cortex M-3, as SODA's control processor. The design of the SODA data processor is motivated by the observation that the majority of the computation are long vector arithmetic operations. Previous researches have shown that a Single Instruction Multiple Data (SIMD) architecture is a good fit for vector-based computations. However, most existing SIMDbased processors operate on relatively short 4 to 8 element vectors, due to intra-vector data rearrangement difficulties in general purpose computations. Because the SODA data processor is targeted only at the set of DSP algorithms for wireless communication, the data rearrangement issue can be handled efficiently through a specialized vector permutation network. Analysis shows that a wide SIMD datapath that supports 32 element vectors is the most power efficient for wireless baseband processing algorithms.

A commercial SDR processor based on the SODA processor architecture has been developed by ARM Ltd. The Ardbeg processor is also a multi-core DSP processor that consists of 32-lane SIMD data processors. This thesis provides a detailed comparison study between the SODA and Ardbeg processors. This study reconfirms many of the SODA architectural decisions. It also reveals many design shortcomings of SODA, and explains the subsequent design improvements in Ardbeg.

Algorithm Implementations. Each DSP algorithm in W-CDMA is hand coded and optimized for the SODA data processor. The majority of wireless protocols' algorithms operate on large vectors, and are therefore a good fit for a wide-SIMD design. This thesis validates this claim by demonstrating the implementation of key DSP algorithms on SODA. In addition, DSP algorithms usually have multiple different implementations, not all of which can be mapped efficiently onto the wide-SIMD design. This thesis describes a set of DSP algorithm implementations that are suited for the SODA architecture.

Language and Compiler Support. This thesis also proposes a programming lan-

guage and compilation flow for mapping wireless protocols onto SODA-like multi-core DSP architectures. Motivated by the streaming computation of the DSP systems, previous works have proposed using concurrent dataflow models to describe DSP systems. The majority of the compilation research focused on the static dataflow model due to its simplicity and determinism. Although wireless protocols have streaming properties that match the dataflow model, they cannot be described with a static dataflow model. In between long episodes of streaming computation, DSP systems intermittently reconfigure the streaming patterns to account for changes from the users and the environment. This thesis finds that a reconfigurable dataflow model, parameterized dataflow, is better suited for describing wireless protocols.

The SPIR compiler is a function-level compiler, which means that the granularity of an atomic execution unit is a function, not an instruction. Traditional compiler's intermediate representation (IR) is used to model instruction-level interactions. A different IR is needed to model the inter-function behavior. This thesis proposes using the parameterized dataflow model as compiler's intermediate representation. The proposed high-level programming language, SPEX, is a language extension for C. Its purpose is to serve as a guideline for programmers to write stylized C code that can be translated into the parameterized dataflow model. SPIR compiler's backend performs optimization on the dataflow IR and generates multi-threaded C code for the Ardbeg processor.

### **1.2** Organization

The remainder of this dissertation proposal is organized as follows. Chapter 2 provides our analysis on the software characteristics of our SDR case study – the W-CDMA wireless protocol. In Chapter 3, this thesis proposes the Signal-Processing On-Demand Architecture (SODA), a fully programmable architecture that supports SDR. In Chapter 4, this thesis then shows our SDR algorithm implementations on SODA. In Chapter 5, this thesis presents a comparison study between SODA and its subsequent commercial prototype – Ardbeg. In Chapter 6, Signal Processing language EXtensions (SPEX) are proposed . And finally, in Chapter 7, an multiprocessor compiler is described to automatically parallelize SPEX code onto the Ardbeg processor.

Ultimately, we believe that the need to support many increasingly complex wireless protocols will make the use of programmable systems for these protocols inevitable. And the techniques proposed in this thesis are relevant in designing viable solutions for SDR and other mobile supercomputing applications.

## 1.3 Acknowledgements

The work presented in this thesis is a collaboration between three professors and eight graduate students. The author of this thesis has been the student leader on all fronts of this project, but other people have made many key contributions to the projects as well. The wireless protocol analysis was led by Hyunseok Lee. Other contributors included the author of this thesis, Yoav Harel and Mark Woh. The architecture study was led by the author of this thesis, with helps from Hyunseok Lee, Mark Woh, and Yoav Harel. Yoav Harel was involved in the architectural design. Hyunseok Lee helped on the wireless protocol analysis and benchmarking. And Mark Woh was responsible for the SODA power analysis. The comparison study between SODA and Ardbeg is done as a collaboration between Mark Woh, the author of this thesis, and Sangwon Seo. The SPEX language extension is proposed solely by the author of this thesis. There are other contributors to the SPIR compiler. They include Yoonseo Choi and Manjunath Kudlur. Yoonseo Choi was responsible for the Ardbeg code generation. And Manjunath Kudlur developed an optimal software pipelining algorithm as a part of the compiler optimization.

## CHAPTER 2

## The W-CDMA Wireless Communication Protocol

The goal of this study is to design a programmable solution for wireless communication protocols. The first step of this process is to develop a deep understanding of the underlying requirements and computation characteristics of wireless protocols. The majority of the computation occurs at the physical layer of protocols, where the focus is the signal processing. Traditionally, kernels corresponding to the dominant tasks, such as filters and decoding, are identified. Design alternatives are then evaluated on the subset workload. This approach has the advantage of dealing with a small amount of code. However, we have found that the interaction between tasks in SDR has a significant impact on the hardware architecture. This occurs because the physical layer is a combination of algorithms with different complexity and processing time requirements. For example, high computation tasks that run for a long period of time can often be disturbed by small tasks. Further, these small tasks have hard real-time deadlines, thus they must be given high priority. We believe it is necessary to explore the whole physical layer operation with a complete model.

Among many wireless protocols, we select the wideband code division multiple access (W-CDMA) protocol as a representative wireless workload for study. W-CDMA system

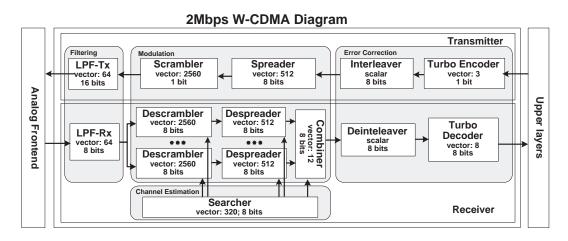

Figure 2.1: Physical layer operation of W-CDMA wireless protocol. Each block includes the algorithm's name, vector or scalar computation, vector width, and the data precision. The algorithms are also grouped into four categories, shown in shaded boxes: filtering, modulation, channel estimation, and error correction.

is one of the dominant third generation wireless communication networks where the goal is multimedia service including video telephony on a wireless link [41]. W-CDMA improves over prior cellular protocols by increasing the data rate from 64 Kbps to 2 Mbps. Additionally, W-CDMA unifies a single service link for both voice and packet data, compared with supporting only one service in previous generations. We have developed a full C implementation of the W-CDMA physical layer to serve as the basis for our study. The implementation can be executed on a Linux workstation and thus studied with conventional architectural tools. In this chapter, Section 2.1 provides a summary of the computing characteristics of the W-CDMA physical layer.

#### 2.1 Protocol Overview

The protocol stack of the W-CDMA system consists of several layers. Each protocol layer provides a specific function in the system. For example the physical layer placed at the bottom of protocol stack is responsible for overcoming errors induced by an unreliable wireless link, and the medium access control (MAC) layer resolves contention on the shared radio resources. In this section we discuss the computation model of the W-CDMA physical layer.

Due to the high computation demand and tight power budget, the physical layer in most wireless protocols is implemented in ASICs. Although SDR encompasses all protocols layers, this thesis only focuses on the physical layer due to its computation and power importance. The operation of physical layer utilizes both digital and analog circuits. Because the operation frequency of analog circuits such as low noise amplifier and mixers is over GHz level, it is infeasible to achieve programmability with current digital circuit technology. Thus, this thesis narrows down our focus on the physical layer operation performed by digital circuits. Figure 1 shows a high level block diagram of W-CDMA physical layer implemented by digital circuits. It is placed between upper layer protocols and the front-end circuit. The upper layer protocols are implemented on a general purpose processor due to their relatively low computation requirements. The front-end circuit is realized by analog circuit technology.

The operation flow of the W-CDMA physical layer is shown in Figure 2.1. It contains a set of disparate DSP algorithm kernels that work together as one system. There are four major components: filtering, modulation, channel estimation, and error correction. Filtering algorithms are used to suppress signals transmitted outside of the allowed frequency band so that interference with other frequency bands are minimized. Modulation algorithms map source information onto the signal waveforms of the transmitter, and receivers demodulate the signal waveforms back into source information. Channel estimation algorithms calculate the channel conditions to synchronize the two communicating terminals to ensure lock-step communication between the sender and the receiver. Error correction algorithms are used to combat noisy channel conditions. The sender encodes

| Algorithms                                                                                     | Configurations                  | Vector<br>Comp. | Vector<br>Length | Bit<br>Width | Comp.<br>Mcycles/sec |  |  |  |

|------------------------------------------------------------------------------------------------|---------------------------------|-----------------|------------------|--------------|----------------------|--|--|--|

|                                                                                                | W-CDMA                          | (2Mbps)         |                  |              |                      |  |  |  |

| Scrambler                                                                                      | Defined in W-CDMA standard      | yes             | 2560             | 1,1          | 240                  |  |  |  |

| Descrambler*                                                                                   | 12 fingers, 3 base stations     | yes             | 2560             | 1,8          | 2,600                |  |  |  |

| Spreader                                                                                       | Spreading factor = 4            | yes             | 512              | 8            | 300                  |  |  |  |

| Despreader*                                                                                    | 12 fingers, 3 base stations     | yes             | 512              | 8            | 3,600                |  |  |  |

| PN Code (Rx)                                                                                   | 3 base stations                 | no              | 1                | 8            | 30                   |  |  |  |

| PN Code (Tx)                                                                                   | Defined in W-CDMA standard      | no              | 1                | 8            | 10                   |  |  |  |

| Combiner*                                                                                      | 2Mbps data rate                 | partial         | 12               | 8            | 100                  |  |  |  |

| FIR (Tx)                                                                                       | 4 filters x 65 coeff x 3.84Msps | yes             | 64               | 1,16         | 7,900                |  |  |  |

| FIR (Rx)                                                                                       | 2 filters x 65 coeff x 7.68Msps | yes             | 64               | 8,8          | 3,900                |  |  |  |

| Searcher*                                                                                      | 3 base stations, 320 windows    | no              | 320              | 1,8          | 26,500               |  |  |  |

| Interleaver                                                                                    | 1 frame                         | no              | 1                | 8            | 10                   |  |  |  |

| Deinterleaver                                                                                  | 1 frame                         | partial         | 1                | 8            | 10                   |  |  |  |

| Turbo Enc.                                                                                     | K=4                             | yes             | 3                | 1,1          | 100                  |  |  |  |

| Turbo Dec.*                                                                                    | K=4, 5 iterations               | yes             | 8                | 8,8          | 17,500               |  |  |  |

| *These algorithms have dynamically changing workloads that are dependent on channel conditions |                                 |                 |                  |              |                      |  |  |  |

Figure 2.2: Workload analysis result of W-CDMA physical layer processing. "Vector comp" indicates whether the algorithm contains vector-based arithmetic operations. "Vector width" lists the native computation vector width. "Bit width" lists the data precision width. "Comp Mcycle/sec" lists the cycle-count of running the algorithm on a general purpose processor.

the original data sequence with a coding scheme that inserts systematic redundancies into the output, which is decoded by the receiver to find the most likely original data sequence.

## 2.2 Workload Analysis

Workload Profiling. Figure 4.1 shows the result of our profiling. The first column lists the W-CDMA algorithms that have been implemented as a part of this study. The second column lists the corresponding configurations for each of the algorithms. The third and fourth column lists the vector computation information for the algorithms. The fifth column lists the data precision width. The last column shows peak workload of the algorithms. The peak workload is the minimum performance needed to sustain 2Mbps throughput, under the worst wireless channel condition. For example we need a processor with approximately 8 GOPS in order to finish the transmitter FIR task within 0.67 msec. For peak workload analysis, we compiled our W-CDMA model with an Alpha gcc compiler, and executed on M5 architectural simulator [16]. We measure the instruction count that is required to finish each algorithm. Results are calculated by dividing the instruction count by the maximum processing time of each algorithm. The workloads of Viterbi and Turbo decoder requires further verification because their processing times are not fixed. The data are calculated under the assumption that the processing time of Viterbi decoder is 40 msec and that of Turbo is 25 msec.

The results show that there are a set of key DSP algorithms that are responsible for the majority of the computation. These algorithms include the FIR filter, searcher, Turbo decoder, descrambler and despreader. Therefore, a SDR processor must process these algorithms efficiently.

**Parallelism in the Protocol.** To meet the real-time W-CDMA performance requirement in software, we must exploit inherent algorithmic parallelism. Figure 4.1 columns 3 and 4 show the potential parallelism that can be exploited either through Data Level Parallelism (DLP) or Thread Level Parallelism (TLP). We define DLP as the maximum SIMD variable vector width. The first column represents maximum possible DLP through the maximum number of elements in a vector. The width of element in a vector is shown at the second column. Because a vector operation needs two operands, we represent the element width of each vector separately. We define TLP as the maximum number of different threads that can be executed in parallel.

From this result, we can see that searcher, filter, scrambler, and descrambler contain

a lot of vector parallelism due to intensive vector operation. In addition, we can expect tasks level parallelism from them. For searcher operation we can issue 5120 tasks concurrently. For the case of scrambler and descrambler we can expect tasks level parallelism by bisecting a wide vector into smaller ones. Although sliced vectors are not perfectly uncorrelated, we can execute the smaller vector operations with negligible dependency. At the practical view point, too wide vector is implausible. However turbo decoder, which is one of dominant workloads, contains limited vector and task level parallelism. The vector width of turbo decoder is 8.

Intrinsic Computations. Many DSP algorithms have a large number of multiplication operations. Because multiplication is a power consuming operation, it is advantageous to convert this into other operations. First, the multiplications in the spreader and scrambler can be simplified to an exclusive OR, because both operands are either 1 or -1. Second, the multiplication operations in the searcher, descrambler, despreader, and FIR(Tx) can be simplified into conditional complement operations, because one operand of the multiplications in these algorithms is either 1 or -1, and the other operand is a fixed point number. However, the multiplication of the FIR(Rx) cannot be simplified because both operands are fixed point numbers.

Vector permutations are required for the Turbo decoder, FIR, and searcher, because either output or operand vector needs to be permuted. In Turbo decoder, the core computation operation is the Add-Compare-Select operation, which consists of one vector addition, one vector comparison, one vector permutation, and one vector move operation.

Memory Requirements. Figure 2.3 lists the memory size and throughput requirements for W-CDMA algorithms. Memory usage is divided into data and instruction memory access. Data memory access is further divided into input buffer, output buffer, and scratchpad memories. Input and output buffers are used for IO memory accesses, and

|                   |                                        | Data Memory                                                                                   |       |               |       |            |         |               |  |  |  |

|-------------------|----------------------------------------|-----------------------------------------------------------------------------------------------|-------|---------------|-------|------------|---------|---------------|--|--|--|

| Algorithms        | Configurations                         | Input Buffer                                                                                  |       | Output Buffer |       | Scratchpad |         | Inst.<br>Mem. |  |  |  |

|                   |                                        | KB                                                                                            | MBps  | KB            | MBps  | KB         | MBps    | menn.         |  |  |  |

|                   | W-(                                    | CDMA (2                                                                                       | Mbps) |               |       |            |         |               |  |  |  |

| Scrambler         | Defined in W-CDMA standard             | 0.7                                                                                           | 15.4  | 0.7           | 15.4  | 0.7        | 15.4    | 0.5           |  |  |  |

| Descrambler*      | 12 fingers, 3 base stations            | 5.6                                                                                           | 123.2 | 5.6           | 123.2 | 0.7        | 15.4    | 0.5           |  |  |  |

| Spreader          | Spreading factor = 4                   | 0.1                                                                                           | 1.9   | 0.4           | 7.6   | 0.1        | 3.9     | 0.4           |  |  |  |

| Despreader*       | 12 fingers, 3 base stations            | 0.4                                                                                           | 7.6   | 0.1           | 1.9   | 0.1        | 3.9     | 0.3           |  |  |  |

| Combiner*         | 2Mbps data rate                        | 0.1                                                                                           | 0.1   | 0.1           | 0.1   | 0.1        | 0.1     | 0.1           |  |  |  |

| FIR (Tx)          | 4 filters x 65 coeff x 3.84Msps        | 0.3                                                                                           | 7.6   | 10.3          | 245.8 | 0.1        | 1996.8  | 0.2           |  |  |  |

| FIR (Rx)          | 2 filters x 65 coeff x 7.68Msps        | 10.5                                                                                          | 245.8 | 2.5           | 61.4  | 0.1        | 1996.8  | 0.2           |  |  |  |

| Searcher*         | 3 base stations, 320 windows           | 20.8                                                                                          | 2.1   | 0.1           | 0.1   | 32.0       | 2654.3  | 3.1           |  |  |  |

| Interleaver       | 1 frame                                | 1.2                                                                                           | 1.1   | 1.2           | 1.1   | 9.5        | 1.9     | 0.1           |  |  |  |

| Deinterleaver     | 1 frame                                | 26.1                                                                                          | 5.2   | 26.1          | 5.2   | 8.7        | 5.2     | 0.1           |  |  |  |

| Turbo Enc.        | K=4                                    | 2.6                                                                                           | 4.0   | 7.8           | 12.0  | 0.1        | 2.0     | 1.6           |  |  |  |

| Turbo Dec.*       | K=4, 5 iterations                      | 61.5                                                                                          | 96.0  | 2.6           | 4.0   | 6.4        | 25600.0 | 3.4           |  |  |  |

| *These algorithms | have dynamically changing workloads th | These algorithms have dynamically changing workloads that are dependent on channel conditions |       |               |       |            |         |               |  |  |  |

Figure 2.3: Memory requirements for the W-CDMA physical layer algorithms. "KB" is the memory size requirement in KByte. "MBps" is the memory through requirement in KByte-per-second. "Input buffer and output buffer" are the IO memory requirements. "Scratchpad" is the internal memory requirement. As shown in the figure, the overall memory size and throughput requirements for W-CDMA is not very high. Majority of which come from scratchpad memory access of intermediate computation results.

the scratchpad memory is used for storing intermediate computation results. As shown in the figure, the overall memory size and throughput requirements for W-CDMA are not very high. Majority of which come from scratchpad memory access. Most algorithms are streaming DSP algorithms, where each input data is consumed once in a sequential order, and each corresponding output data is produced in the same sequential order. Streaming DSP algorithms do not need to buffer data, which result in smaller memory requirements. The exceptions are the Turbo decoder, searcher, interleaver and deinterleaver – all require their input data to be buffered. Interleaver and deinterleaver do not process their input data in a sequential order. Turbo decoder and searcher process input data multiple times. This is the reason behind the relatively high memory requirements for these algorithms.

**Power Budget.** [62] has presented an overall evaluation of cellular phones as embed-

ded systems. It has outlined the power budget for the various components in a cellular phone. For W-CDMA physical layer processing, the power budget is typically around 300mW. This varies for difference wireless protocols and mobile devices.

#### 2.3 Summary