## PARALLEL PROCESSING OF BEST-FIRST BRANCH AND BOUND ALGORITHMS ON DISTRIBUTED MEMORY MULTIPROCESSORS

$\label{eq:by} \begin{tabular}{ll} \begin{tab$

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 1989

**Doctoral Committee:**

Associate Professor Trevor N. Mudge, Chairman Assistant Professor Chaitanya K. Baru Professor John P. Hayes Professor William R. Martin  $\bigcirc \ \, \frac{ \text{Tarek S. Abdel-Rahman}}{ \text{All Rights Reserved}}$

1989

To my family

## ACKNOWLEDGEMENTS

I would like to thank my committee members for their useful comments and suggestions, and their careful review of this manuscript. I would like to specially thank my advisor Trevor N. Mudge for his help during the many stages of my studies at the University of Michigan.

I would like to extent my deepest gratitude to my family, whom without their help and support it would not have been possible to complete this work. I wish to thank my wife Suad for her love, care, support and patience during the years of our marriage.

Financial support has been partially provided by the Robot Systems Division (RSD), Center for Research on Integrated Manufacturing (CRIM) at the University of Michigan; by the Materials Laboratory, Air Force Wright Aeronautical Laboratories, Aeronautical Systems Division (AFSC), United States Air Force, Wright-Patterson AFB, Ohio 45433-6503; by the Army Research Office under Contract DAAG29-84-K-0070; and by a pre-doctoral Fellowship from the Hoarce H. Rackham School of Graduate Studies at the University of Michigan.

The computing facilities of the Advanced Computer Architecture Laboratory and the Robot Systems Division were instrumental in the completion of this work.

## TABLE OF CONTENTS

| D  | EDIC  | CATIO  | $\mathbf{N}$                                  | ii   |  |

|----|-------|--------|-----------------------------------------------|------|--|

| A  | CKN   | OWLI   | EDGEMENTS                                     | iii  |  |

| LI | ST (  | OF FIG | GURES                                         | vi   |  |

| LJ | IST ( | OF TA  | BLES                                          | viii |  |

| LI | ST (  | OF AP  | PENDICES                                      | ix   |  |

| 1  | INT   | RODI   | UCTION                                        | 1    |  |

|    | 1.1   | Motiva | ations and Objectives                         | . 2  |  |

|    | 1.2   | Resear | rch Overview                                  | . 4  |  |

|    | 1.3   | Thesis | organization                                  | . 6  |  |

| 2  | DIS   | TRIB   | UTED MEMORY MULTIPROCESSORS                   | 8    |  |

|    | 2.1   | The A  | architecture of DMMs                          | . 8  |  |

|    |       | 2.1.1  | Multiplicity of Instructions and Data Streams | . 11 |  |

|    |       | 2.1.2  | Interconnection Topology                      | . 12 |  |

|    |       | 2.1.3  | Granularity of Processing Elements            | . 18 |  |

|    | 2.2   | Exam   | ples of DMMs                                  | . 19 |  |

|    |       | 2.2.1  | The Connection Machine                        | . 19 |  |

|    |       | 2.2.2  | The Massively Parallel Processor (MPP)        | . 20 |  |

|    |       | 2.2.3  | The Mark III                                  | . 20 |  |

| 3  |       |        |                                               |      |  |

|    | 3.1   | Formu  | ılation of the BB Algorithm                   | . 25 |  |

|    |       | 3.1.1  | The BB Tree                                   | . 26 |  |

|    |       | 3.1.2  | The Selection Procedure                       | . 28 |  |

|    |       | 3.1.3  | The Branching Procedure                       | . 32 |  |

|    |       | 3.1.4  | The Elimination Procedure                     | . 33 |  |

|    |       | 3.1.5  | The Termination Procedure                     | . 36 |  |

# TABLE OF CONTENTS

| DEDICATION |                                |        |                                               | ii   |  |

|------------|--------------------------------|--------|-----------------------------------------------|------|--|

| A          | ACKNOWLEDGEMENTS               |        |                                               |      |  |

| L          | IST (                          | OF FIG | GURES                                         | vi   |  |

| LI         | ST (                           | OF TA  | BLES                                          | viii |  |

| L          | IST (                          | OF AP  | PPENDICES                                     | ix   |  |

| 1          | INT                            | rod    | UCTION                                        | 1    |  |

|            | 1.1                            | Motiv  | rations and Objectives                        | . 2  |  |

|            | 1.2                            | Resear | rch Overview                                  | . 4  |  |

|            | 1.3                            | Thesis | s Organization                                | . 6  |  |

| 2          | DIS                            | TRIB   | UTED MEMORY MULTIPROCESSORS                   | 8    |  |

|            | 2.1                            | The A  | Architecture of DMMs                          | . 8  |  |

|            |                                | 2.1.1  | Multiplicity of Instructions and Data Streams | . 11 |  |

|            |                                | 2.1.2  | Interconnection Topology                      | . 12 |  |

|            |                                | 2.1.3  | Granularity of Processing Elements            | . 18 |  |

|            | 2.2                            | Exam   | ples of DMMs                                  | . 19 |  |

|            |                                | 2.2.1  | The Connection Machine                        | . 19 |  |

|            |                                | 2.2.2  | The Massively Parallel Processor (MPP)        | . 20 |  |

|            |                                | 2.2.3  | The Mark III                                  | . 20 |  |

| 3          | THE BRANCH AND BOUND ALGORITHM |        |                                               |      |  |

|            | 3.1                            | Formu  | ulation of the BB Algorithm                   | . 25 |  |

|            |                                | 3.1.1  | The BB Tree                                   | . 26 |  |

|            |                                | 3.1.2  | The Selection Procedure                       | . 28 |  |

|            |                                | 3.1.3  | The Branching Procedure                       | . 32 |  |

|            |                                | 3.1.4  | The Elimination Procedure                     | . 33 |  |

|            |                                | 3.1.5  | The Termination Procedure                     | . 36 |  |

|                                  |                | 3.1.6                      | Outline of the BB Algorithm                      | 36  |  |  |

|----------------------------------|----------------|----------------------------|--------------------------------------------------|-----|--|--|

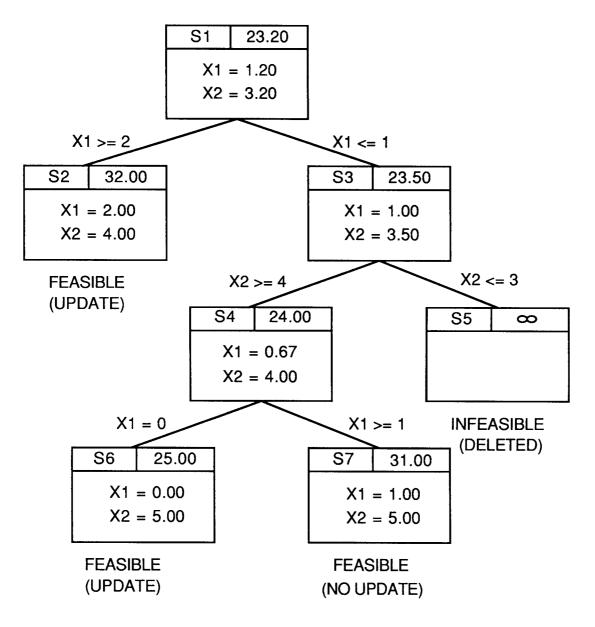

| 3.2                              |                | Examp                      | oles of the BB Algorithm                         | 39  |  |  |

|                                  |                | 3.2.1                      | The 0-1 Integer Linear Programming (ILP) Problem | 40  |  |  |

|                                  |                | 3.2.2                      | The Integer Linear Programming (ILP) Problem     | 43  |  |  |

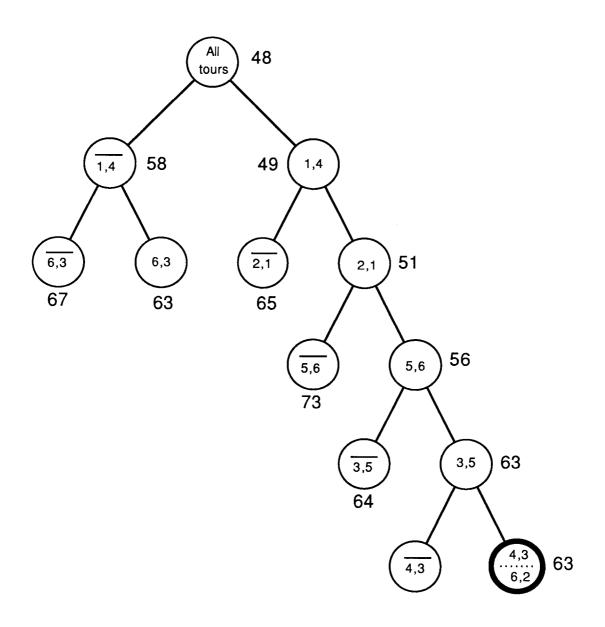

|                                  |                | 3.2.3                      | The Traveling Salesman Problem (TSP)             | 45  |  |  |

|                                  |                | 3.2.4                      | The $A^*$ Algorithm                              | 51  |  |  |

| 4                                | MA             | PPIN                       | G THE BB ALGORITHM ONTO DMMs                     | 57  |  |  |

| 4.1 Parallelism in BB Algorithms |                |                            | elism in BB Algorithms                           | 57  |  |  |

|                                  | 4.2            | The L                      | ogical Model Algorithm                           | 59  |  |  |

|                                  | 4.3            | The D                      | istributed Model Algorithm                       | 66  |  |  |

|                                  |                | 4.3.1                      | Computation-Overhead                             |     |  |  |

|                                  |                | 4.3.2                      | Communication-Overhead                           | 74  |  |  |

|                                  |                | 4.3.3                      | Imbalance-Overhead                               | 74  |  |  |

|                                  |                | 4.3.4                      | Computation-Communication Tradeoff               | 75  |  |  |

|                                  |                | 4.3.5                      | The Model                                        |     |  |  |

|                                  | 4.4            | Releva                     | ant Work on Parallel BB                          | 81  |  |  |

| 5                                | TH             | THE PARALLEL ALGORITHMS 96 |                                                  |     |  |  |

|                                  | 5.1            | The C                      | L Algorithm                                      | 97  |  |  |

|                                  | 5.2            | The S                      | HIFT Algorithm                                   | 104 |  |  |

|                                  | 5.3            | The D                      | L Algorithm                                      | 116 |  |  |

| 6                                | EX             |                            | VIDIVITIE TELESCETS                              | 128 |  |  |

|                                  | 6.1            | The L                      | M Algorithm                                      | 133 |  |  |

|                                  | 6.2            | The C                      | L Algorithm                                      | 135 |  |  |

|                                  | 6.3            | The S                      | HIFT Algorithm                                   | 141 |  |  |

|                                  | 6.4            | The D                      | OL Algorithm                                     | 150 |  |  |

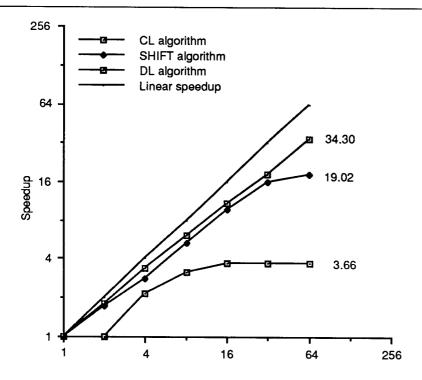

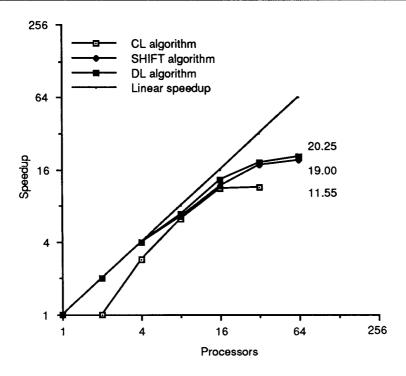

|                                  | 6.5            |                            | arison of Performance                            |     |  |  |

|                                  | 6.6            | Summ                       | nary of Results                                  | 159 |  |  |

| 7                                | $\mathbf{AC}$  | CELE                       | RATION ANOMALIES                                 | 163 |  |  |

| 8                                | CO             | CONCLUSIONS 1              |                                                  |     |  |  |

|                                  | 8.1            | Summ                       | nary and Contributions                           | 173 |  |  |

|                                  | 8.2            | Futur                      | e Research                                       | 175 |  |  |

| A                                | $\mathbf{PPE}$ | NDIC                       | ES                                               | 177 |  |  |

| $\mathbf{B}_{i}$                 | IBLI           | ogr <i>A</i>               | АРНҮ                                             | 191 |  |  |

## LIST OF FIGURES

| 2.1 | A distributed memory multiprocessor system                                 |

|-----|----------------------------------------------------------------------------|

| 2.2 | The architecture of a node                                                 |

| 2.3 | The Message Transfer System                                                |

| 2.4 | The 2-D grid topology                                                      |

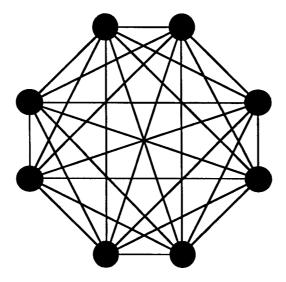

| 2.5 | The completely connected topology                                          |

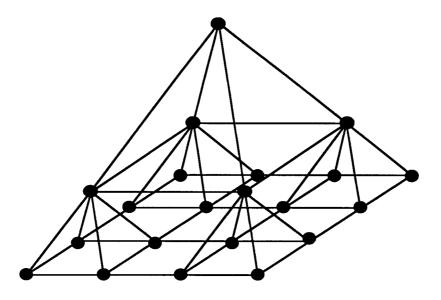

| 2.6 | The pyramid topology                                                       |

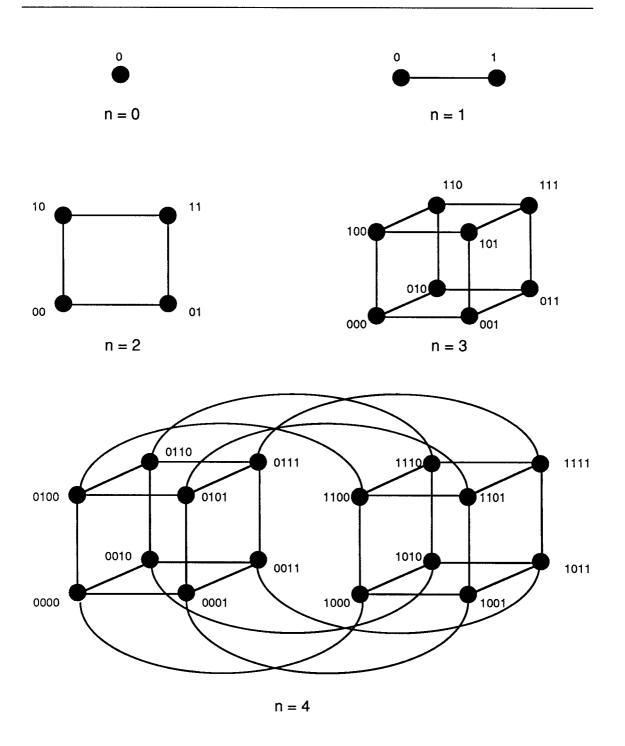

| 2.7 | The hypercube topology                                                     |

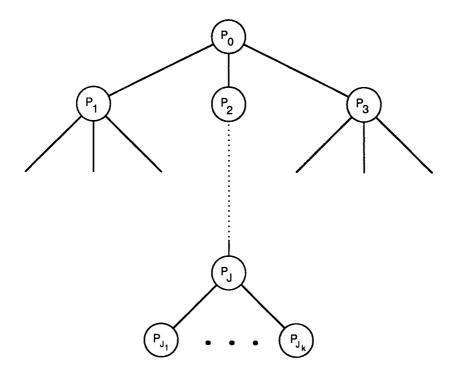

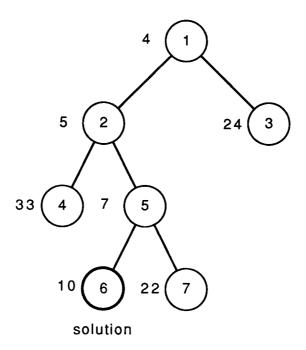

| 3.1 | BB tree of a simple example                                                |

| 3.2 | A BB tree                                                                  |

| 3.3 | A BB tree with path numbers                                                |

| 3.4 | BB tree for the ILP example                                                |

| 3.5 | The BB tree for the TSP example                                            |

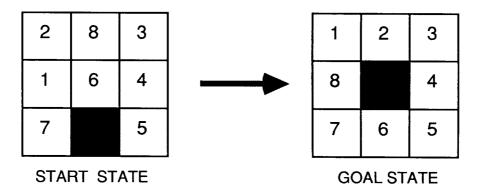

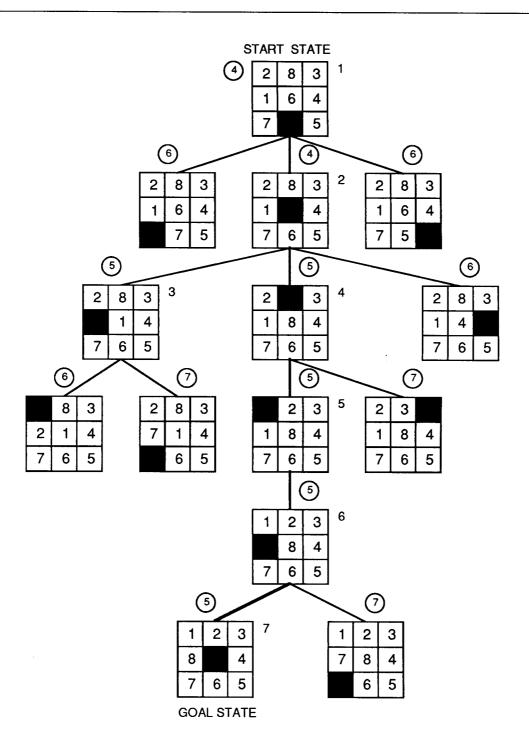

| 3.6 | An 8-puzzle example                                                        |

| 3.7 | The BB tree for the 8-puzzle example                                       |

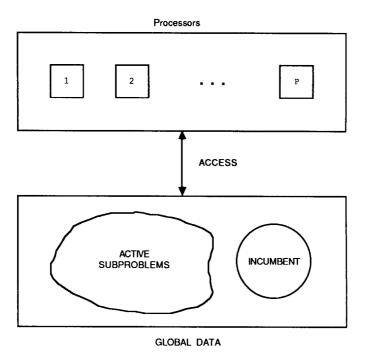

| 4.1 | The Logical Model                                                          |

| 4.2 | The BB tree generated by the sequential BB algorithm 65                    |

| 4.3 | The BB tree generated by the LM algorithm using two processors 66          |

| 4.4 | The Distributed Model                                                      |

| 4.5 | Example of computation-overhead caused by lack of selection information 71 |

| 4.6 | Example of computation-overhead caused by lack of pruning information 73   |

| 4.7 | Example illustrating possible load imbalance                               |

| 4.8 | The computation-communication tradeoff                                     |

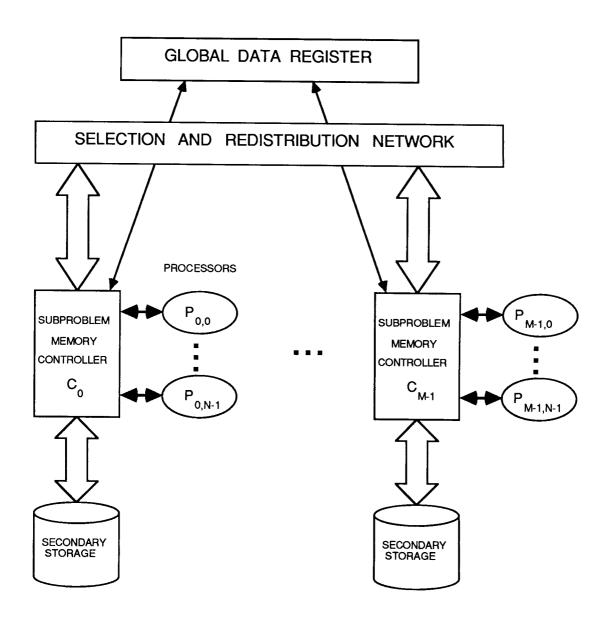

| 4.9 | The architecture of MANIP                                                  |

| 5.1 | Outline of the CL algorithm                                                |

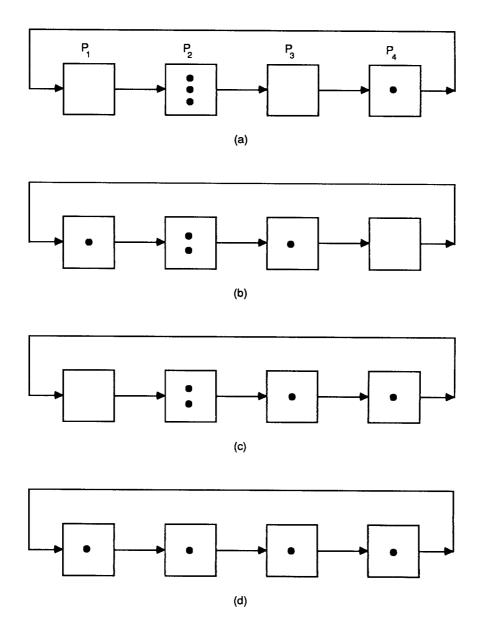

| 5.2 | The process of shifting subproblems to achieve complete distribution 10'   |

| 5.3 | Outline of the SHIFT algorithm                                             |

| 5.4 | Outline of the DL algorithm                                                |

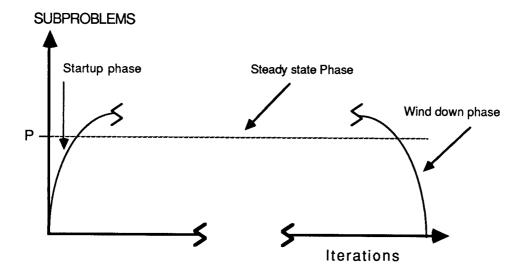

| 5.5 | The phases of execution of a BB algorithm                                  |

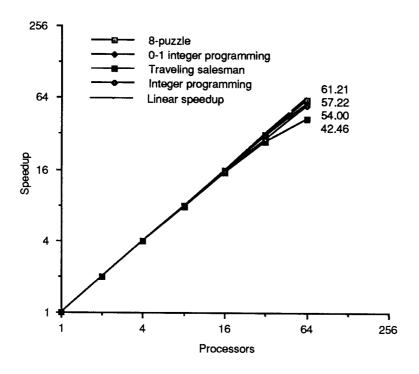

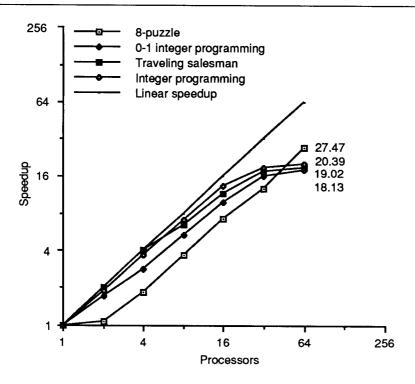

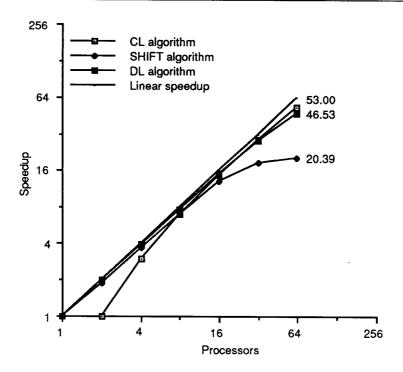

| 6.1  | The speedup of the logical model algorithm                 |

|------|------------------------------------------------------------|

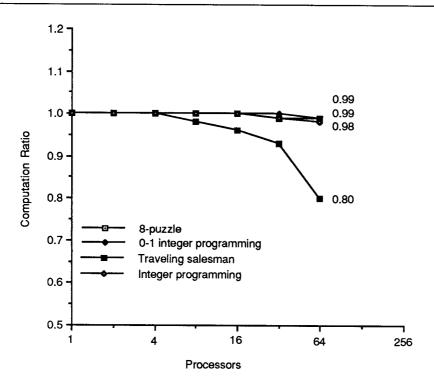

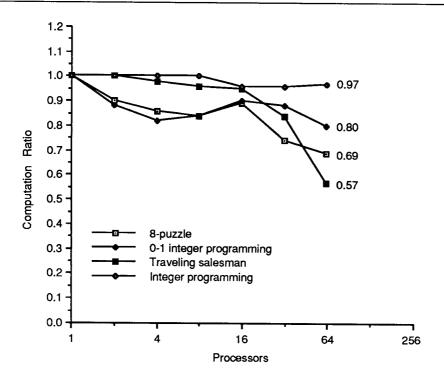

| 6.2  | Computation ratio of the CL algorithm                      |

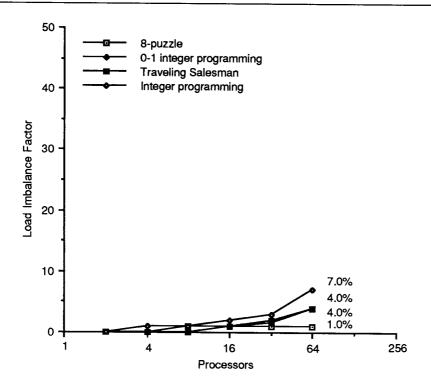

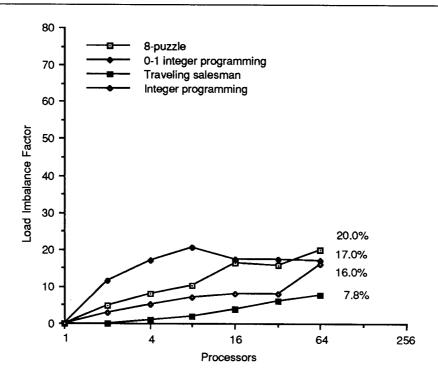

| 6.3  | Load imbalance factor of the CL algorithm                  |

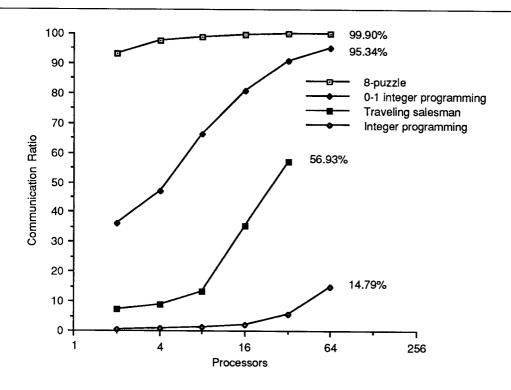

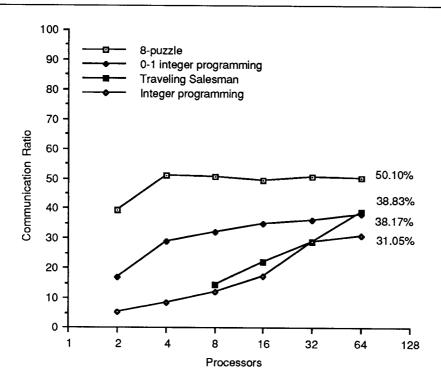

| 6.4  | Communication ratio of the CL algorithm                    |

| 6.5  | Speedup of the CL algorithm                                |

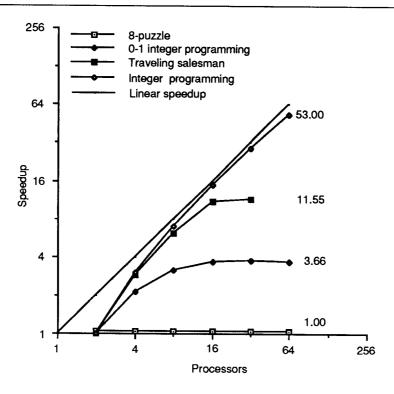

| 6.6  | The effect of communication distance on load balance       |

| 6.7  | The speedup of the SHIFT algorithm versus $s$              |

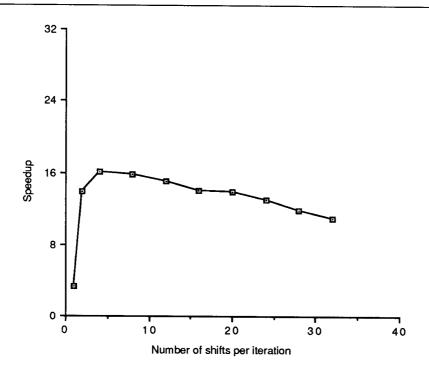

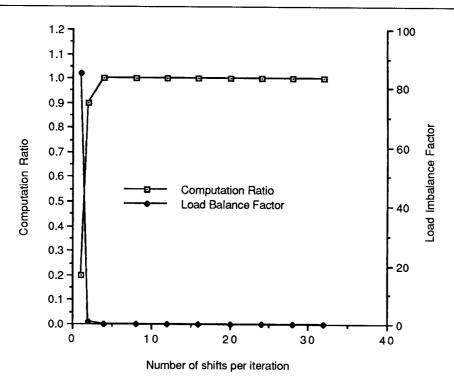

| 6.8  | $C_r$ and $\ell$ of the SHIFT algorithm versus $s$         |

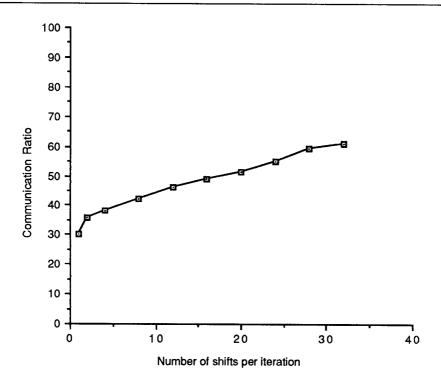

| 6.9  | The communication ratio of the SHIFT algorithm versus s    |

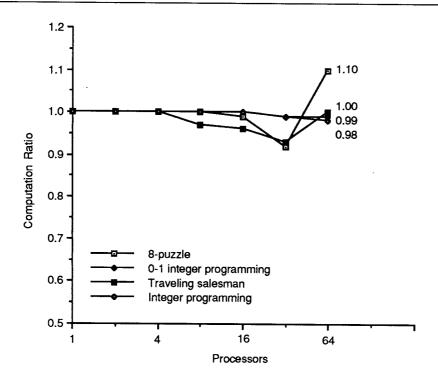

| 6.10 | The computation ratio of the SHIFT algorithm               |

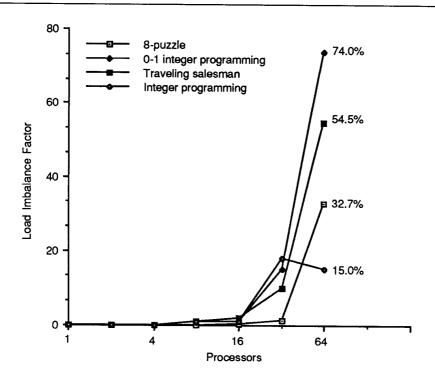

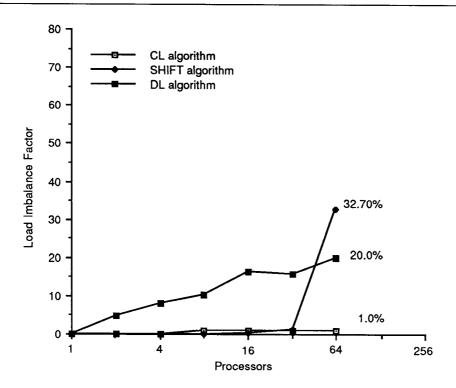

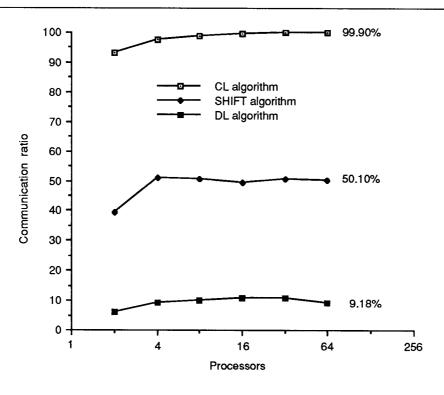

| 6.11 | The load imbalance factor of the SHIFT algorithm           |

| 6.12 | The communication ratio of the SHIFT algorithm             |

| 6.13 | The speedup of the SHIFT algorithm                         |

| 6.14 | The computation ratio of the DL algorithm                  |

| 6.15 | The load imbalance factor of the DL algorithm              |

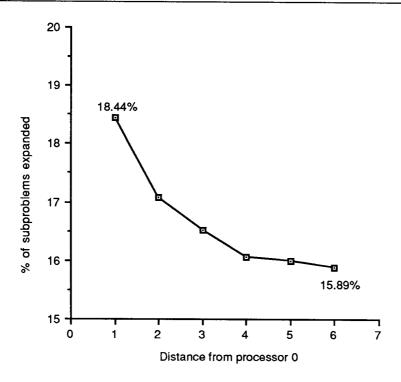

| 6.16 | The communication ratio of the DL algorithm                |

| 6.17 | The speedup of the DL algorithm                            |

| 6.18 | The speedups for the 8-puzzle problem                      |

| 6.19 | The computation ratio for the 8-puzzle problem             |

| 6.20 | The load imbalance factor for the 8-puzzle problem         |

| 6.21 | The communication ratio for 8-puzzle problem               |

| 6.22 | The speedups for the 0-1 integer programming problem       |

| 6.23 | The speedup of the traveling salesman problem              |

| 6.24 | The speedup of the integer programming problem             |

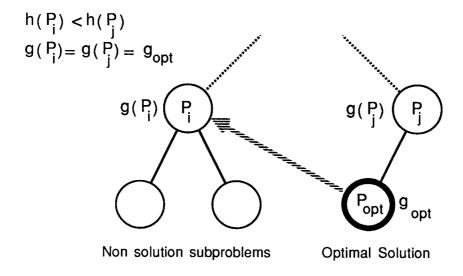

| 7.1  | Example showing the possible inconsistency of $h$ with $g$ |

| 7.2  | The occurrence of an anomaly                               |

| 7.3  | Example illustrating an acceleration anomaly               |

| 1.0  |                                                            |

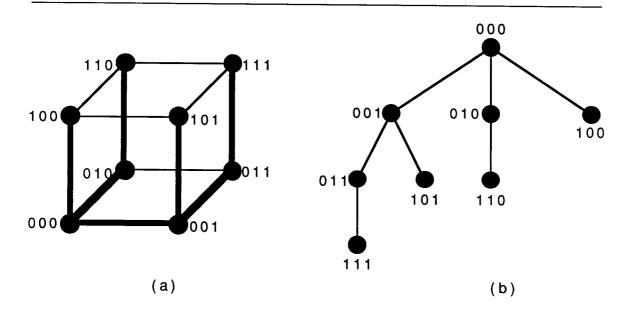

| A.1  | Embedding of a ring in a 3-dimensional hypercube           |

| A.2  | Embedding of a spanning tree in a 3-dimensional hypercube  |

| Δ 3  | The implementation of broadcast using a spanning tree 184  |

## LIST OF TABLES

| 6.1         | The average time to expand a subproblem in the four applications 132  |

|-------------|-----------------------------------------------------------------------|

| 6.2         | Observed optimal number of shifts                                     |

| 6.3         | The improvement in the speedup of the DL algorithm due to slicing 154 |

| 7.1         | The ratio of $ S_e $ to the total number of subproblems               |

| <b>A</b> .1 | A Gray code for three bit integers                                    |

## LIST OF APPENDICES

| A            | The NCUBE/ten          | 178 |

|--------------|------------------------|-----|

| В            | The Test Problems      | 185 |

| $\mathbf{C}$ | IMPLEMENTATION DETAILS | 188 |

## CHAPTER 1

### INTRODUCTION

The continuing advances in VLSI technology are making possible the construction of highly parallel multiprocessor systems that are capable of delivering high performance computing at relatively low costs. These systems are based on a large ensemble of relatively simple and relatively inexpensive processors connected together by a message passing network. There is no globally shared memory in these systems; rather, each processor has its own private memory. The processors communicate to share data and/or synchronize by passing messages to one another over the network. Consequently, these multiprocessors are known as Distributed Memory Multiprocessors (DMMs), or Message Passing Multiprocessors (MPMs). Examples include the hypercubes of Intel [Inte85], Ametek [Amet85], and NCUBE [NCUB85], and the mesh-connected systems of Ametek [Amet88] and Goodyear [Pott85].

In contrast to more conventional high-performance supercomputers, which rely on pipelined and vectored processing, DMMs achieve their high performance potential through the use of a large number of processors cooperating in parallel to perform a particular computation. This approach is referred to as parallel processing and is becoming an increasingly attractive alternative to achieving high performance computing. The effective use of a large number of processors, however, relies on the extent to which a computation can be mapped onto the multiprocessor, i.e., divided into smaller components which can be assigned to, and independently executed by, individual processors. There are no

general techniques for mapping applications onto multiprocessors; rather, the mapping of applications is studied on a case by case basis. This study deals with the mapping of a class of heuristic search problems that can be described by the Branch and Bound (BB) algorithm onto DMMs.

## 1.1 Motivations and Objectives

DMMs have been successfully applied to a large number of problems from many application areas of science and engineering (see [FJLO88] for a survey). Examples include: image processing, computer vision, matrix computations, simulation of particle transport, and computer-aided design. The results obtained often reflect substantial improvements over the performance of a single processor. A notable example is the use of a 1024-processor hypercube at Sandia National Labs to solve large scale problems in fluid dynamics and structural analysis [GuMB88]. Experimentally obtained results indicate an impressive gain in performance, not only over a single processor, but also over supercomputers of higher cost.

However, the success of a DMM in improving the performance of a particular computation depends to a large extent on the nature of that computation. In many cases a computation lends itself to parallelism and substantial performance improvements are possible. In some other computations, however, this is not the case, and special care must be taken with the mapping of that computation onto the DMM if any improvements in performance are to be obtained. Therefore, it is safe to say that the performance gains obtained by applying a DMM to a computation depends not only on the performance potential of the DMM, but also on the nature of that computation. Hence, to obtain a valid view of the true potential of DMMs as high performance computers, applications of diverse computational nature must be studied. The majority of applications to which DMMs have been applied to date tend to have common properties which lend them to

parallel processors in general, and to DMMs in particular. The applications tend to have regular and homogeneous data sets, typically consisting of arrays of data elements of the same type. Operations are usually applied to the elements of the data sets almost independently of each other, implying large degrees of inherent parallelism. The computations are also structured in such a way that a static load-balancing strategy can be employed to generate uniform workloads across the processors. This is usually accomplished by dividing the data sets equally among the processors. Therefore, it seems that only a restricted set of computation have been considered to reflect performance gains that can be obtained from DMMs. A key motivation behind this study was to extend the scope of the computations to which DMMs have been applied by considering the parallel processing of the BB algorithm on this class of multiprocessors.

The BB algorithm generates a data set that is highly irregular and dynamic. This data set, referred to as the BB tree, will be described later in Chapter 3. The structure of this data set cannot be predicted in advance and hence, dynamic balancing of workloads must be employed. Furthermore, the BB algorithm, as will be seen later, requires global knowledge of some attributes of this data set in order to maintain its computational efficiency. This global knowledge requirement can pose problems in a distributed memory environment and presents a challenge for DMMs. Therefore, an objective of this study is to investigate the suitability of a distributed memory architecture when both global knowledge and dynamic load balancing are required.

There are other factors that motivate us to study the parallel processing of BB algorithms on DMMs and make this study significant. The BB algorithm is an interesting algorithm in its own right. It is used to solve a large number of fundamental problems in science and engineering that otherwise would have no efficient solution methods [LaWo66, Nils80]. Examples of such problems include the well-known traveling salesman problem, the integer programming problem, and state-space search. BB techniques have also been used in

heuristic search algorithms [KuKa83], floor planning of VLSI integrated circuits [WiKC88], placement of electronic components [BrKa88] and robot path planning [KaNa85]. The use of BB to solve many of the above problems generally results in intensive computations that can benefit from the high performance potential of DMMs. One objective of this research is to find out the extent to which BB can benefit from these multiprocessors.

In most scientific and engineering applications that have been successfully parallelized to date, the amount of computations performed by the parallel algorithm to complete the solution of a particular problem instance has not been influenced by the introduction of parallelism. That is, the number of computational steps needed to obtain a solution to a given problem instance is independent of, and hence, is not affected by the parallelism introduced through the use of parallel processors. Parallelism affects the performance of the application only through overheads incurred by the processors in communicating data and/or synchronizing. This is not actual in the case of parallel BB algorithms. The introduction of parallelism to BB can, and indeed often does, change the amount of computations needed to obtain a solution to a given problems instance. This can have considerable effects on the performance of the parallel BB algorithm when compared to the performance of the sequential one. One objective of this study is to investigate the effect of this change in the computational characteristics introduced by parallelism on the performance of the parallel BB algorithm. This will, in effect, lead to the design of a more efficient mapping of BB onto DMMs.

#### 1.2 Research Overview

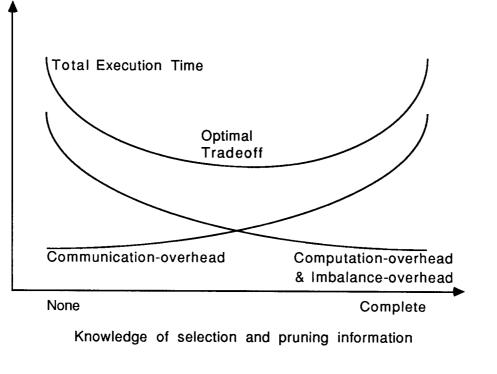

The mapping of BB algorithms on DMMs will be investigated in this study. This will be done by identifying the factors that affect the performance of this class of algorithms on DMMs. These factors will be shown to give rise to three types of overhead that degrade the performance of the algorithm. The first is communication-overhead that

results from the need to exchange information about the search among the processors. The second is computation-overhead that results as a consequence of the expansion of non-essential subproblems; i.e, subproblems not expanded by the sequential algorithm. The third is imbalance-overhead that results as processors idle due to load imbalance. A computation-communication tradeoff exists between the first type of overhead on one hand and the other two types of overhead on the other. In order to reduce the expansion of non-essential subproblems and obtain a more balanced workload, more exchange of information is needed, which gives rise to more communication-overhead. On the other hand, communication-overhead can be minimized by eliminating communications among the processors, which can be done only at the expense of expanding non-essential subproblems and an imbalanced workload, giving rise to more computation-overhead.

Analytical modeling and algorithm analysis techniques are limited in predicting the extent to which these types of overhead affect performance, and in further characterizing the tradeoff among them. While these techniques are successful in predicting the performance of sequential BB algorithms [Smit84, WaYu85], their applicability to parallel BB algorithms is limited by the change in computational characteristics of BB algorithms which caused by the introduction of parallelism. This change is dependent not only on the problem instance to be solved, but also on the nature of the parallel algorithm and the characteristics of the DMM, making it difficult to model without unrealistic simplifying assumptions.

Consequently, the extent to which the factors described above, the three types of overhead, and the computation-communication tradeoff affect the performance of parallel BB algorithms will be demonstrated for actual applications using three parallel algorithms that map the sequential BB algorithm on a hypercube multiprocessor. The third algorithm also demonstrates the performance of a new load balancing strategy that utilizes the computation-communication tradeoff to obtain good performance.

### 1.3 Thesis Organization

This remainder of this thesis is organized as follows:

- In Chapter 2 the key features of DMMs are reviewed.

- In Chapter 3 a formulation of the BB algorithm outlining its main components is presented. Examples illustrating the application of the algorithm to mathematical programming and artificial intelligence are given.

- In Chapter 4 the mapping of the BB algorithm on DMMs is examined. The factors that affect the performance of a parallel BB algorithm on this class of multiprocessors are presented. The tradeoff among the three types of overhead these factors give rise to is described, and a simple model that captures how this tradeoff affects performance is presented. A review of past work on parallel BB algorithms is also given in this chapter.

- In Chapter 5 the three parallel algorithms used to illustrate the effect of the factors identified in Chapter 4 are described. The third algorithm uses the new load balancing strategy.

- In Chapter 6 experimental results obtained by implementing the algorithms on a commercial hypercube multiprocessor are presented and discussed.

- In Chapter 7 acceleration anomalies that can occur in the execution of parallel BB algorithms are described.

- In Chapter 8 concluding remarks and future research are presented.

- In Appendix A the NCUBE/ten hypercube multiprocessor used to obtain experimental results is described.

- In Appendix B the test problems used in the experimental runs are described.

• In Appendix C implementation details of the experiments are described.

## CHAPTER 2

## DISTRIBUTED MEMORY MULTIPROCESSORS

In this chapter an overview is presented of distributed memory multiprocessors (DMMs). In section 2.1 the general organization of this class of multiprocessors is reviewed and the key elements of their architecture are discussed. In section 2.2 examples of DMMs are presented.

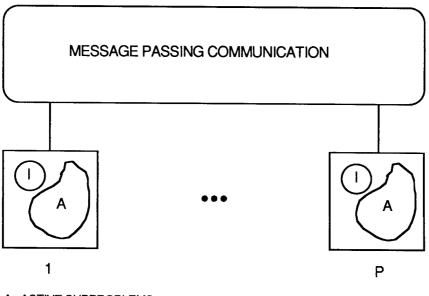

#### 2.1 The Architecture of DMMs

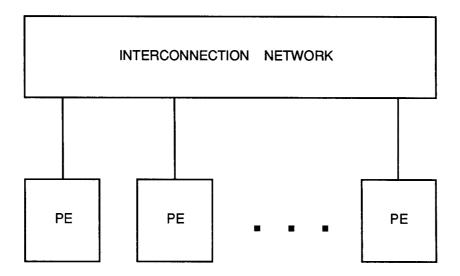

A DMM consists of N processing elements or nodes that are interconnected together using an interconnection network. There exists no globally shared memory in a DMM; instead, each node contains its own local memory. The nodes communicate to each other through the interconnection network. A block diagram of a DMM is shown in figure 2.1.

The interconnection network consists of a set of dedicated communication links. Each communication link is used to connect a pair of processing elements to each other. In general, the communication links interconnect the nodes so that each node is directly connected to only a subset, referred to as its *neighbors*, of the other nodes in the system.

The nodes and the communication links interconnecting them can be represented by a graph G = (N, E) that consists of a set of vertices N and a set of edges E. The vertices of the graph represent the processing elements in the system, and the edges of the graph represent the communication links. The overall configuration in which the processors and

Figure 2.1. A distributed memory multiprocessor system.

the communication links are interconnected is referred to as the interconnection topology.

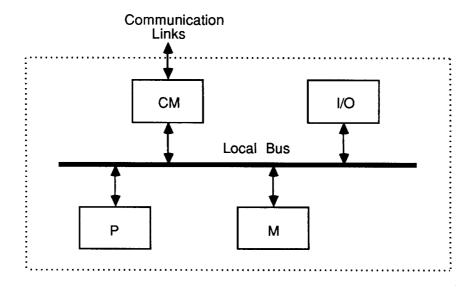

A processing element or node consists of four major components: a processor P, a local memory M, an I/O module, and a communication module CM. These components interface to a local bus as shown in figure 2.2. P is a general purpose instruction set processor, and the local memory is used to store both programs and data for P. The I/O module provides an interface to external devices and peripherals. The communication module connects the node to the communication links, which in turn connects the node to its neighbors in the DMM.

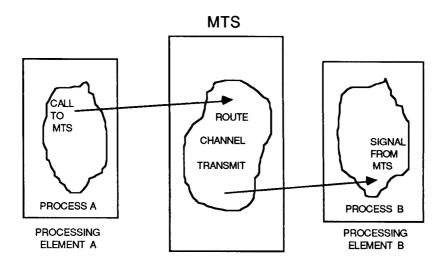

The processing elements communicate by passing messages to one another over the communication links. This is facilitated by a Message Transfer System (MTS) which operates in each node [HwBr84]; this is depicted in figure 2.3. A process in node A makes a call to the MTS when it wants to send a message to another process in node B. The MTS receives the request, determines the destination, computes the route if needed, and initiates the transmission of the message. When the message arrives at B, the MTS

Figure 2.2. The architecture of a node.

interrupts the process on B to inform it that the message has arrived. Such communication protocol also is referred to as the mail box communication protocol [PTLP85].

DMMs generally support the *loosely coupled* model of computation. In this model, concurrent processes in the computation are assumed to be independent of one another. The degree of interaction among the processes is small. Each process executes its own code operating on its own data set. Processes communicate by passing messages to each other. Hence, DMMs are also referred to as *loosely coupled* multiprocessors.

The architecture of DMMs offers a number of advantages over other architectures for interconnecting processors to processors as well as processors to memory. First, the contention for memory as a shared resource is avoided by distributing the memory resources across the nodes. Second, since there is no contention for memory, the latency in memory access is reduced to a minimum. This is an important factor since memory access is a significant part of any computation. Finally, with a properly designed interconnection network, the number of nodes can be increased to several times that which is possible in

Figure 2.3. The Message Transfer System.

alternative architectures based on shared-buses or multistage interconnection networks.

This provides the potential for massive parallelism and very high performance computing.

The architecture of DMMs can be characterized by three main elements: the multiplicity of instruction and data streams, the interconnection topology, and the granularity of the node.

#### 2.1.1 Multiplicity of Instructions and Data Streams

Following Flynn's classification scheme [Flyn66], DMM systems can be split into two groups with respect to the multiplicity of instruction and data streams: Single Instruction Multiple Data streams, or SIMD multiprocessors and Multiple Instruction Multiple Data streams, or MIMD multiprocessors.

In SIMD multiprocessors, there is a single instruction stream to all the processing elements, or nodes, in the system. A global control unit broadcasts the instructions to all nodes, and each node executes the instructions using the data in its local memory. The

nodes are synchronized and execute in lock-step, and each node can be optionally activated or deactivated. Only activated nodes execute the broadcasted instructions allowing the conditional execution of instructions.

In MIMD multiprocessors, there is a separate instruction stream in each node of the system. Each node has a control unit which issues instructions allowing the node to execute asynchronously with respect to other nodes on the data in its local memory. In general, MIMD multiprocessors offer the potential for more flexibility and performance over SIMD multiprocessors for a wide range of applications. Furthermore, MIMD multiprocessors can efficiently emulate SIMD multiprocessors by executing the same instructions in each node. This mode of operation is referred to as Single Code Multiple Data execution (SCMD) [Buzz88], or sometimes as Single Program Multiple Data (SPMD) [Karp87].

### 2.1.2 Interconnection Topology

The interconnection network is used to transfer messages from one node in the system to another. The topology of the interconnection network plays an important role in the efficiency with which the network can achieve that goal. Topologies for interconnecting processors in a DMM system can be characterized by a number of properties [AgJa86].

Diameter. The diameter D of an interconnection topology is defined as the maximum

of the minimum distances between any two nodes in the topology. The distance is

measured by the number of links. That is,

$$D = \max\{d_{min}(i,j) \mid \forall i, j \in V\},\$$

where  $d_{min}(i,j)$  is the minimum distance between any two nodes i and j. The diameter can be used as a measure of the communication distance between pairs of nodes in a given interconnection topology. The smaller the diameter, the shorter the communication distance and, consequently, the closer the nodes are to each other.

Hence, it is desirable to interconnect the nodes in a topology that has as small a diameter as possible.

- 2. Degree. The degree δ of a node in a topology is defined as the number of edges that are connected to that node. A topology in which all nodes have the same degree δ is referred to as a regular topology of degree δ. The degree of the node can be used as a measure of the number of wires that fanout from a node. The smaller the degree, the smaller the fanout of the node, simplifying its design and increasing its fault tolerance. Furthermore, a regular topology implies that all the nodes can be identical. Hence, it is desirable to interconnect the nodes in a regular topology that has as small a degree as possible. However, it is important to realize that minimizing the degree of the topology is typically in conflict with minimizing the diameter of the topology. In order to get the nodes closer together by minimizing the diameter, the number of connections from each node must be increased. Therefore, it is not possible to minimize both the degree and the diameter independently.

- 3. Expandability. The expandability of a topology is a measure of the ability of that topology to accommodate more nodes and links. A distributed memory multiprocessor system with an expandable topology requires little or no modification to the topology to add new nodes to the system. Topologies that have borders are generally hard to expand since border processors are usually connected to I/O. It is often desirable to have a system with an expandable topology.

- 4. Scalability. The scalability of a topology refers to the extent to which it is possible to scale the topology to systems containing a large number of nodes without serious performance degradation. It is desirable to have a topology that is scalable. Topologies that have small node degrees can normally be expanded more easily than those with large degrees. However, since topologies with small degrees typically tend to

have larger diameters, the data communication time becomes large and the topology becomes unusable.

5. Fault tolerance. The fault tolerance of a topology refers to its ability to tolerate faulty nodes or links. Some topologies can map out faulty nodes and/or links without affecting the basic operation of the topology. These topologies are fault tolerant and are also desirable for a DMM system.

Examples of topologies that have been, or are being used in DMM systems include: rings, multi-dimensional grids or meshes, trees, completely connected arrays, pyramids and hypercubes. The more common ones are reviewed briefly below.

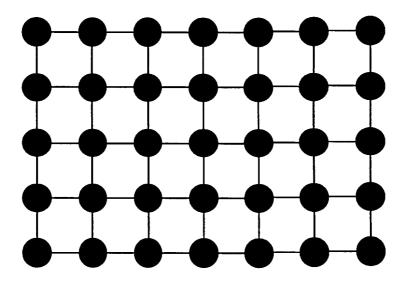

**2-D Grids.** In this topology, the nodes are interconnected together to form a two-dimensional grid. Each node is directly connected to only four neighbors in the grid; this is depicted in figure 2.4. This topology has a small degree, 4, which is constant and independent of the number of PEs in the system. This results in simple and regular interconnections. However, the diameter of the topology is relatively large,  $O(\sqrt{N})$ . Data movements beyond the four neighbors can become time consuming.

Completely Connected Arrays. In this topology, every node is connected to every other node. An example is shown in figure 2.5. Each node is exactly one edge away from any other node. The advantage of this topology is the high connectivity of its nodes. The diameter of the topology is the minimum possible diameter. The major disadvantages of this topology are the large degree of the topology and the fact that the number of links grows quadratically with respect to the number of the nodes.

**Pyramids.** In this topology the nodes are interconnected together to form a pyramid, as shown in figure 2.6. Each node is connected to four neighbors, a parent and four children nodes (some boundary nodes have fewer connections). The advantage of this topology is that the degree of each node is small ( $\leq 9$ ) and that no two nodes are more than  $O(\log_2 N)$

Figure 2.4. The 2-D grid topology.

steps apart. The disadvantage is congestion in the upper levels during system wide data transfers.

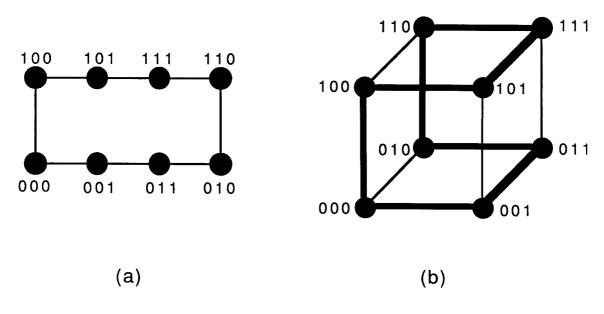

Hypercubes. In this topology,  $N=2^n$ , identical processing elements are interconnected together using  $n2^{n-1}$  communication links to form an n-dimensional hypercube graph. An n-dimensional hypercube array of nodes, or an n-cube, can be constructed and its nodes uniquely labeled using the following recursive procedure. First, a 1-cube is formed by connecting two nodes with a single communication link. One of the nodes is labeled with a 0 and the other is labeled with a 1. This is the basis step of the procedure. An n-cube is formed from two (n-1)-cubes using the general step of the procedure as follows: node labels in one of the (n-1)-cubes are prefixed with a 0 so they are of the form  $0xx \dots xx$ . Similarly, node labels in the other (n-1)-cubes are prefixed with a 1 so they are of the form  $1xx \dots xx$ . Finally, the two (n-1)-cubes are connected with communication links between nodes that have labels differing only in their most significant bit. This labeling scheme results in a unique n-bit binary address for each node in the resulting hypercube array. The address for each node differs in exactly one bit position from that of any of its

Figure 2.5. The completely connected topology.

neighbors. Since there are n such neighbors, each bit in the address can be thought of as corresponding to one dimension in the hypercube array. The hypercube array topology is illustrated in figure 2.7 for  $n \le 4$ . The zero-dimensional hypercube is the conventional single processor computer.

The hypercube topology for interconnecting nodes has a number of features that makes it an attractive topology for DMMs.

1. The hypercube topology offers a unique balance between the diameter and the degree of the topology. The nodes of the hypercube topology are no more than log<sub>2</sub> N steps apart. Consequently, any two nodes in the hypercube array can communicate efficiently even if they are not directly connected to each other. At the same time, the degree of each node in the graph is relatively small—log<sub>2</sub> N. This balance makes the hypercube topology compare favorably with other topologies such as grids and completely connected arrays. It also allows the topology to be scalable to a large number of processors.

Figure 2.6. The pyramid topology.

- 2. The hypercube topology results in a regular and homogeneous array of nodes. All of the processors are identical and have the same view of the array. There are no special nodes that must be designated as the "borders" of the topology, as is the case in most other topologies (two-dimensional grids for example). Homogeneity makes it natural to attach an I/O channel to each node, providing the potential for high I/O bandwidth.

- 3. A large dimension hypercube array can be divided into smaller dimension hypercube arrays, or subcubes. Each subcube is completely independent of the other subcubes. This feature of the hypercube topology facilitates multiprogramming in which each user can be assigned a dedicated subcube [NCUB85]. It also increases the fault tolerance of the hypercube array since a faulty node can be mapped out by mapping out a subcube that contains it. Furthermore, a user program can be developed and debugged on a small size hypercube while production runs can be made on larger dimension hypercubes.

4. Finally, the hypercube topology can efficiently embed other regular topologies such that neighboring processors in those topologies are also neighboring, or at least close, in the hypercube topology. Examples include: multi-dimensional grids [ChSa86], trees [BCLR86] and pyramids [Stou86]. Since many of these regular topologies are used in a variety of applications, this feature makes the hypercube topology a good candidate for a general purpose parallel architecture.

#### 2.1.3 Granularity of Processing Elements

The granularity of a DMM refers to the number of nodes it contains and the characteristics of their main features. It is generally difficult to quantify granularity, so the concept will be described qualitatively here.

At one end of the spectrum there are fine-grained DMMs which are characterized by a very large number of nodes. Each node is a relatively simple processor consisting of a CPU and a limited size local memory. The ratio of communication to computation tends to be large in fine-grained multiprocessors. Therefore, this granularity of multiprocessors is generally suitable for *data parallel* applications, in which sequences of simple operations are applied across very large sets of data (SIMD). Examples of fine-grained multiprocessors include the MPP [Batc80] and the Connection Machine [Hill85].

At the other end of the spectrum there are coarse-grained multiprocessors which are characterized by a small number of very powerful nodes. Each node contains a large memory and a sophisticated CPU that may even support vector operations. The ratio of communication to computation in coarse-grained multiprocessors is generally low. Coarse-grained multiprocessors are usually suitable for *control parallel* applications, in which different segments of the code execute simultaneously (MIMD). Such applications appear frequently in many areas of science and engineering. Examples of coarse-grained multiprocessors include the Mark III hypercube [PTLP85] and the Intel iPSC-VX hyper-

cube multiprocessor which incorporates vector co-processors with each node [Inte86].

In the middle of the spectrum lie medium-grained multiprocessors, which offer a compromise between the two extremes. Medium-grained multiprocessors are characterized by a moderate number of nodes, in the range 100–1000, each a reasonably sized CPU and memory. This configuration has the potential of efficiently handling applications that are either data or control parallel. Furthermore, with the current technology, such granularity provides the maximum possible performance. Applications for medium-grained multiprocessors range from AI to scientific applications. Examples of this granularity include the Intel iPSC [Inte85] and the NCUBE/ten [NCUB85], both hypercube DMMs.

### 2.2 Examples of DMMs

In this section three examples of DMM systems are presented. The examples represent existing multiprocessor systems, and an overview of each system is given emphasizing the key architectural features described above.

#### 2.2.1 The Connection Machine

The Connection Machine is a very-fine-grained DMM [Hill85]. It consists of up to 65,536 nodes that contain a bit-serial processor with 4096 bits of memory. The nodes are interconnected using a dual network topology. Groups of 16 nodes are interconnected in a two-dimensional grid topology. These groups are then connected by a 12-cube interconnection topology. The bit-serial processors execute instructions that are broadcast from a set of four control processors. Each control processor is connected to a subset of 16,384 processors in the system. The control processors are asynchronous, and each can broadcast a different set of instruction streams. The system is hence an MSIMD (Multiple SIMD) system.

The connection machine is designed for AI applications and is particularly well-suited

for low-level vision applications, and for searching databases in parallel [HiSt86].

#### 2.2.2 The Massively Parallel Processor (MPP)

The MPP is a fine-grained DMM that consists of 16,384 bit serial processors that are interconnected in a two dimensional grid topology. Each processor has 4096 bits of local memory. The processors execute instructions that are broadcast from a single control unit. A global 320 Mbytes/sec I/O channel is used to transfer programs and data to and from the MPP. The MPP is designed for real-time, low-level image processing and scene analysis. These and other applications are discussed in [Pott85].

#### 2.2.3 The Mark III

The Mark III is a coarse-grained distributed memory multiprocessor. It consists of up to 1024 nodes that are interconnected in a 10-dimensional hypercube topology. The nodes operate asynchronously, making the Mark III an MIMD system. Each node consists of a 16 MHz Motorola 68020 microprocessor with an associated 68881 floating point coprocessor. A separate 68020 is used for inter-node communication support. Each node can include up to 4 Mbytes of memory and can use special function units such as vector processors.

Two types of message transfer systems are available for the Mark III. The first is the Crystalline Operating System (CrOS-III), which provides synchronous communication between the nodes; the second is the Mercury operating system, which supports asynchronous communication between nodes.

Figure 2.7. The hypercube topology.

## CHAPTER 3

## THE BRANCH AND BOUND ALGORITHM

There is a large class of problems in the fields of Operations Research (OR) and Artificial Intelligence (AI) for which there exist no "direct" methods of solution or only inefficient ones. Techniques for solving such problems generally involve the search for solutions in a large problem space. Examples include the traveling salesman problem [LMSK63] and heuristic search problems [Nils80].

Unguided search through the problem space is usually inefficient and impractical. This is particularly true since many of these problems are NP-hard, and the size of the problem space increases exponentially with the size of the problem. Several techniques have been developed to improve the average efficiency of the search. The most general of these techniques is the Branch and Bound (BB) algorithm [LaWo66].

The BB algorithm, as its name suggests, consists of two processes: a branching process and a bounding process. The branching process partitions the problem space, or subspaces of it, into smaller subspaces until the subspaces are small enough to be searched exhaustively for the desired solution. The bounding process of the algorithm acts to reduce the number of subspaces partitioned by the branching process. A subspace is examined by the bounding process before it is partitioned. If it can be proved that the subspace does not contain the desired solution, the subspace is *pruned* or eliminated from further consideration from the branching process.

The combined action of the branching and bounding processes reduces the extent of the search and improves the average efficiency of the BB algorithm. The branching process guides the search towards a solution by partitioning subspaces that are a more likely to contain a solution before subspaces that are less likely to contain it. The bounding process assists the search by eliminating subspaces that cannot lead to a solution before they are actually partitioned.

The branching process applied to the problem space of a given problem is performed by building a search tree, called the *BB tree*, over the problem space. The root of the tree represents the complete problem space. The nodes of the tree represent subspaces of the problem space. The branching process proceeds from the root of the tree to its leaves, partitioning subspaces into smaller and smaller subspaces. The leaf nodes represent subspaces that are small enough to be completely searched for solutions.

Subspaces of the problem space represent partial solutions to the problem. Consequently, a node of the BB tree represents a partial solution to the original problem. The branching process proceeds from the root of the tree to its leaves extending partial solutions towards more complete solutions. Each child node represents one possible way of extending its parent's partial solution towards a more complete one.

In most problems, it is impractical, if not impossible, to explicitly represent the problem space or its subspaces. A more practical representation is to use a problem specific data structure that implicitly represents the problem space. This data structure representation is referred to as a *subproblem*. Hence, a subproblem is a representation of a problem subspace or equivalently, a partial solution to the problem. The BB algorithm is generally expressed and formulated in terms of subproblems rather than in terms of problem subspaces.

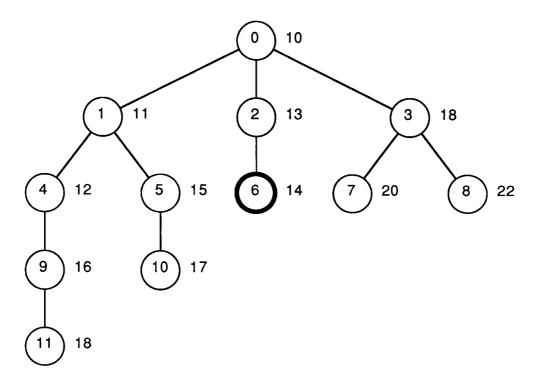

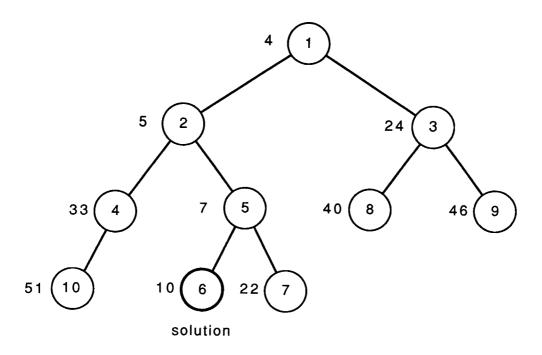

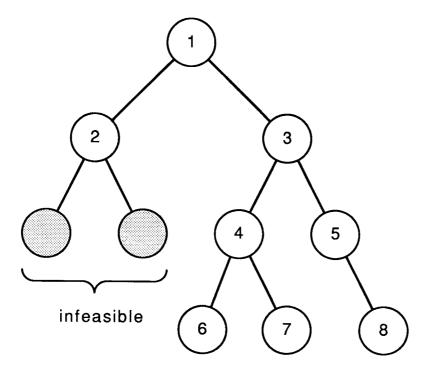

The above process of building a BB tree is illustrated in figure 3.1. The figure shows the BB tree for a simple example. The original problem  $P_0$  is at the root of the tree.

Figure 3.1. BB tree of a simple example.

$P_0$  is then partitioned into three smaller subproblems  $P_1$ ,  $P_2$  and  $P_3$ . These subproblems are represented as the three children of  $P_0$ . Each one of the three subproblems is further partitioned into yet smaller subproblems, as shown in the figure. In general, a subproblem  $P_j$  is partitioned into k smaller subproblems  $P_{j_1}, \ldots, P_{j_k}$  which are represented as the k children of  $P_j$ . The process of partitioning a subproblem into smaller subproblems and adding the new subproblems to the BB tree is referred to as *expanding* that subproblem.

The remainder of this chapter is devoted to the formulation of the BB algorithm and its use in a number of application problems. In the next section a more formal description of the BB algorithm is presented, and in section 3.2 the use of the BB to solve four application problems is given.

#### 3.1 Formulation of the BB Algorithm

The general class of problems that are solved by the BB algorithm can be divided into two subclasses: decision problems and optimization problems. In decision problems the objective is to determine the existence of one solution that satisfies a set of constraints. Examples of decision problems include: theorem proving, game playing and rule-based expert systems. In optimization problems, on the other hand, it is desired to optimize an objective function subject to a number of given constraints. Examples of optimization problems include: the traveling salesman problem, integer programming and job-shop scheduling.

A problem instance can be equivalently represented in the form of a decision problem or an optimization problem [GaJo79]. Hence, we represent our problem instances in the generic form of constrained optimization problems without any loss of generality. Furthermore, for the consistency of presentation, the minimization form of the problem is assumed. Hence, the constrained optimization problem takes the form:

Minimize

$$C_o(\mathbf{x})$$

subject to  $G_i(\mathbf{x}) \geq 0$   $i = 1, 2, ..., m$

where  $\mathbf{X}$  is the permissible domain of optimization, often the Euclidean n-space, and  $\mathbf{x}$  denotes a vector  $(x_1, x_2, \ldots, x_n)$ . A solution vector  $\mathbf{x}$  that satisfies the constraints and lies within the domain of optimization  $\mathbf{X}$  is called a *feasible solution*. A feasible solution for which the objective function  $C_o(\mathbf{x})$  is a minimum is called an *optimal solution*. In general, there may be more than one optimal solution.

The formulation of the BB algorithm consists of five major components: the BB tree, which is the basic data structure used by the algorithm, and four procedures that are used to implement the branching and bounding processes of the algorithm: the *selection* procedure, the *branching* procedure, the *elimination* procedure, and the *termination* procedure.

The first two procedures implement the branching process while the last two implement the bounding process.

#### 3.1.1 The BB Tree

The branching process in a BB algorithm can be represented by a rooted tree  $\mathcal{B} = (\mathcal{P}, \mathcal{E})$ . The tree consists of a set of nodes  $\mathcal{P}$  and a set of edges  $\mathcal{E}$ . The nodes represent partitioned subproblems that are generated by the branching process. The edges represent the action of the branching process on the subproblems. The original problem, denoted by  $P_0$ , is at the root of the tree  $\mathcal{B}$ . For any two subproblems  $P_i$  and  $P_j \in \mathcal{P}$ , the directed arc  $(P_i, P_j) \in \mathcal{E}$  if and only if  $P_j$  is directly generated from  $P_i$  by the branching process.  $P_i$  is called the parent of  $P_j$ , and  $P_j$  is, hence, called a child of  $P_i$ . A subproblem  $P_j$  is said to be a descendant of a subproblem  $P_i$  (or equivalently,  $P_i$  is said to be the ancestor of  $P_j$ ) if there exists a sequence of S subproblems  $P_{i_1}, P_{i_2}, \ldots, P_{i_S}$  such that  $(P_i, P_{i_1}) \in \mathcal{E}$ ,  $(P_{i_1}, P_{i_2}) \in \mathcal{E}$ , ..., and  $(P_{i_S}, P_j) \in \mathcal{E}$ . A set of subproblems is said to be independent if no subproblem is a descendant of any other subproblems in the set.

The level of a subproblem  $P_i$ , denoted by  $L(P_i)$ , is defined as the length of the path, measured by the number of arcs, from the root  $P_0$  to  $P_i$  in  $\mathcal{B}$ .  $P_0$  is defined to be at level 1. The set of leaf nodes in the BB tree is denoted by  $\mathcal{T}$ .

The set of subproblems that has been generated by the branching process but not yet examined by that process nor deleted by the bounding process is referred to as the set of active subproblems and is denoted by  $\mathcal{A}$ . The branching process examines that set, removes a subproblem and expands it, adding new subproblems back to the set. The set of active subproblems is, therefore, an independent set of subproblems.

The real valued cost function  $f: \mathcal{P} \to \mathbf{E} \cup \{\infty\}$ , where  $\mathbf{E}$  is the set of non-negative real numbers, denotes the value of the best solution that can be obtained from any subproblem

$P_i \in \mathcal{P}$ . The function f can be defined recursively as follows:

$$f(P_i) = \min\{f(P_{i_j}), j = 1, ..., k\},\$$

where  $P_{i_j}$  denotes the  $j^{th}$  subproblem partitioned directly from  $P_i$ , and k is the total number of these subproblems. That is,

$$k = |\{(P_i, x) \mid (P_i, x) \in \mathcal{E} \quad \forall x\}|.$$

The value of f is computed at the leaf subproblems by directly evaluating the solutions represented by these subproblems. Consequently, the value of the function f for any subproblem  $P_i$  is not known until all leaf subproblems in the subtree rooted at  $P_i$  have been evaluated. The value of f at the root node in the BB tree, therefore, denotes the value of the objective function at the optimal solution vector. That is,  $f(P_0) = C_o(\mathbf{x})$ . The function  $f(P_i)$  takes the value  $\infty$  when there are no feasible solutions from  $P_i$ .

Each subproblem  $P_i$  is also characterized by a value that is computed from a lower bound function  $g: \mathcal{P} \to \mathbf{E} \cup \{\infty\}$ . The lower bound function must have the following properties:

1.

$$g(P_i) \le f(P_i)$$

for all  $P_i \in \mathcal{P}$ ,

2.

$$g(P_i) = f(P_i)$$

for  $P_i \in \mathcal{T}$ , and

3.

$$g(P_j) \ge g(P_i)$$

for  $(P_i, P_j) \in \mathcal{E}$

In other words, the function g is a lower bound estimate of the cost function f, is exact when a subproblem is terminal (i.e., the subproblem represents a feasible solution or the subproblem can never lead to one), and never decreases for descendant subproblems.

The function g can be used to guide the search of the BB algorithm by providing an estimate of f, as will be described in the following section. Hence, it is desired to make g as close an estimate to f as possible so as to guide the search to a solution as quickly

as possible; the more accurate g is, the smaller is the number of subproblems expanded by the BB algorithm [Pear84]. However, making g more accurate usually implies that it becomes more difficult to evaluate. Clearly the evaluation of g should not amount to the complete evaluation of f, or even be close to it. However, g should provide a good estimate of f to guide the search effectively. There is a tradeoff between the accuracy of g and its evaluation difficulty [Pear84].

#### 3.1.2 The Selection Procedure

The selection procedure examines the set of active subproblems  $\mathcal{A}$  and selects one subproblem from that set for expansion. The procedure selects the subproblem that is most likely to lead to the optimal solution among those that belong to the set of active subproblems.

The selection procedure is defined in terms of a selection function  $s_h : \pi \to \mathcal{P}$  such that  $s_h(\mathcal{A}) \in \mathcal{A}$ , where  $\pi$  denotes the family of all independent sets in  $\mathcal{P}$ . The selection function is based on the heuristic function  $h : \mathcal{P} \to \mathbf{E} \cup \{\infty\}$  which assigns a figure of merit to each subproblem in  $\mathcal{P}$ . The selection function  $s_h$  always selects the subproblem with the smallest value of h. That is,

$$h(s_h(\mathcal{A})) = \min\{h(P_i) \mid P_i \in \mathcal{A}\}.$$

The heuristic function h is assumed to be monotone. That is,

$$h(P_j) \ge h(P_i)$$

if  $P_j$  is a descendant of  $P_i$ . (3.1)

The heuristic function is also assumed to be unambiguous. That is,

$$h(P_i) \neq h(P_j)$$

for  $P_i \neq P_j$  and  $P_i, P_j \in \mathcal{A}$ . (3.2)

The selection function determines the order in which the subproblems are selected for expansion from the set of active subproblems. In other words, it determines the order in which the nodes of the BB tree are expanded. Therefore, the selection function is in effect a search strategy for the BB algorithm. Three search strategies are generally used in BB algorithms: best-first search, depth-first search and breadth-first search.

In best-first search, the heuristic function h is the same as the lower bound function g. That is,

$$s_g(\mathcal{A}) = \{ P_i \in \mathcal{A} \mid g(P_i) = \min\{g(P_i) \mid P_i \in \mathcal{A} \} \}.$$

Therefore, in this search strategy, subproblems with smaller lower bounds are selected before subproblems with larger lower bounds. In depth-first search, the selection function is defined such that

$$s_d(\mathcal{A}) = \{ P_i \in \mathcal{A} \mid L(P_i) = \max\{L(P_j) \mid P_j \in \mathcal{A} \} \}.$$

That is, subproblems that are deeper in the tree are selected before subproblems that are closer to the root of the tree. Finally, in breadth-first search, the selection function is defined such that

$$s_b(A) = \{ P_i \in A \mid L(P_i) = \min\{L(P_j) \mid P_j \in A\} \}.$$

That is, subproblems with smaller level numbers (subproblems that are closer to the root) are selected before subproblems that are deeper in the tree.

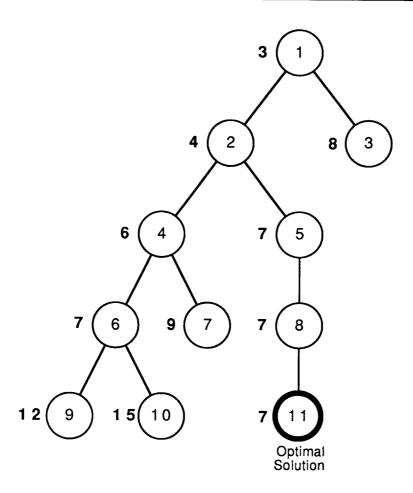

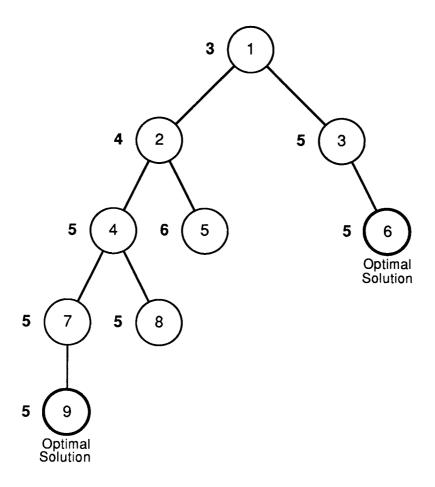

The above three strategies are illustrated using the BB tree shown in figure 3.2. The number inside each subproblem in the tree designates the number of that subproblem. The number to the right of each subproblem denotes the value of the lower bound function for that subproblem. The optimal solution is obtained at subproblem 6. If depth-first strategy is used, then the order of subproblems expanded is  $0 \to 1 \to 4 \to 9 \to 11 \to 5 \to 10 \to 2$ . If breadth-first strategy is used, then the order of subproblems expanded is  $0 \to 1 \to 2 \to 4$ . Finally, if best-first strategy is used, then the order becomes  $0 \to 1 \to 4 \to 2$ .

It is generally the case that equation 3.2 does not hold for the above search strategies, and more than one active subproblem may have the same lower bound or the same level

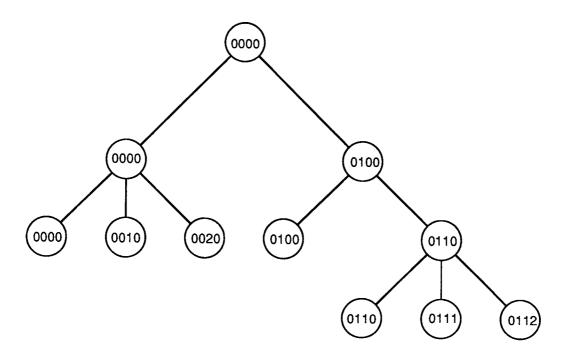

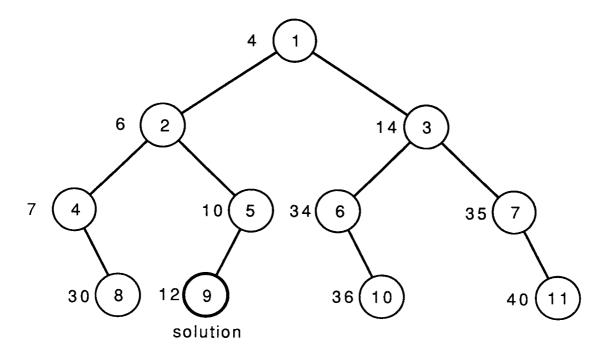

Figure 3.2. A BB tree.

number. Therefore, a tie-breaking mechanism must be be employed. A path number is defined to uniquely identify each subproblem in the set of active subproblems [Li85]. The path number,  $e_1e_2 \ldots e_d$ , of a subproblem  $P_i$ , denoted by  $p(P_i)$ , is a sequence of d integers representing the path from the root to  $P_i$ , where d is the maximum level in the BB tree. The path number for a subproblem in the BB tree is defined recursively as follows:

- 1. The root  $P_0$ , which is at level 1, has a path number  $p(P_0) = 00...0$ .

- 2. If a subproblem  $P_i$  at level l has a path number  $p(P_i) = e_1 e_2 \dots e_l 0 \dots 0$ , then  $P_{i_j}$ , the  $j^{th}$  child of  $P_i$  counting from the left, has a path number  $p(P_{i_j}) = e_1 e_2 \dots e_l (j-1)0 \dots 0$ .

A path number  $p(P_1) = e_1^1 e_2^1 \dots e_d^1$  can be compared to a path number  $p(P_2) = e_1^2 e_2^2 \dots e_d^2$  using the relations '<' and '=' as follows:

Figure 3.3. A BB tree with path numbers.

- 1.  $p(P_1) = p(P_2)$  if  $e_i^1 = e_i^2$  for  $1 \le i \le d$ .

- 2.  $p(P_1) < p(P_2)$  if there exits  $j, 1 \le j \le d$  such that  $e_i^1 = e_i^2, 1 \le i < j$  and  $e_j^1 < e_j^2$ .

An example showing a BB tree with its nodes labeled by path numbers is depicted in figure 3.3. Subproblems can have equal path numbers only if they have ancestor-descendant relationship. Since these subproblems cannot coexist in the set of active subproblems, each active subproblem will have its own unique path number.

The path number can be included in the definition of the heuristic function h in order for h to become unambiguous. In the case of depth-first, the heuristic function h becomes

$$h(P_i) = p(P_i).$$

In the case of breadth-first,

$$h(P_i) = (L(P_i), p(P_i)).$$

In this case, subproblems that are at the same level in the tree will be searched left to right. Finally, in the case of best-first,

$$h(P_i) = (g(P_i), L(P_i), p(P_i)).$$

(3.3)

In this case, subproblems that have the same lower bound are searched in a breadth-first fashion. Alternatively, the heuristic function for the case of best-first can be defined as

$$h(P_i) = (g(P_i), p(P_i)),$$

(3.4)

in which case subproblems that have the same lower bound are searched in a depth-first fashion.

It is often convenient to view the set of active subproblems as being arranged in a list  $\mathcal{L}$  referred to as the *list of active subproblems*. Different search strategies of the BB algorithm can then be viewed as different ways of maintaining that list. For breadth-first search, the list is maintained in a first-in-first-out order. For depth-first search, the list is maintained in increasing order of lower bounds. In the general heuristic search, the list can be viewed as being maintained in increasing order of the heuristic function h. Therefore, the subproblem that is selected by the selection procedure is always the first subproblem on the list of active subproblems.

## 3.1.3 The Branching Procedure

The branching procedure is used by the BB algorithm to decompose problem subspaces into smaller subspaces. The branching procedure examines the subproblem selected for expansion by the selection procedure and creates new subproblems from it. The procedure performs this function by heuristically selecting some unassigned parameters in the subproblem representation and then assigning alternative values for these parameters. In general, the branching procedure is highly problem dependent and is critical to the performance of the BB algorithm.

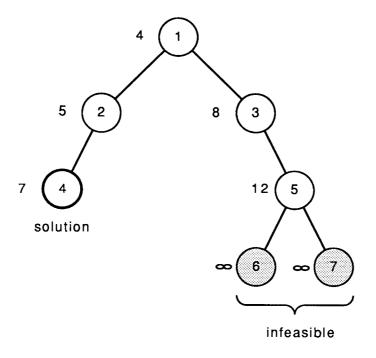

## 3.1.4 The Elimination Procedure

The elimination procedure is used by the BB algorithm to bound the number of subproblems examined by the branching process of the algorithm. It achieves this goal by eliminating subproblems that cannot lead to better optimal solutions than ones already known. This is accomplished by employing one or more bounding tests. These tests generally can be divided into three types: *lower bound* tests, *dominance* tests, and *equivalence* tests.

# Lower Bound Tests

A lower bound test employs a special subproblem which is referred to as the incumbent, and which will be denoted by z. The incumbent is used to store the best feasible solution discovered during the search process at any point in time.

The lower bound test examines the lower bound of a new subproblem generated by the branching procedure, and compares it to the value of the best solution of the incumbent. If the lower bound of that subproblem exceeds that of the incumbent, this subproblem can be eliminated from further consideration, as it can never lead to a better solution than the one already found. That is, a subproblem  $P_i$  is eliminated if

$$g(P_i) \ge g(z), \qquad P_i \in \mathcal{A}.$$

When a new subproblem represents a feasible solution, the value of that feasible solution is compared to that of the incumbent. If the new subproblem represents a better solution, then the incumbent is replaced by the new subproblem.

It is possible to obtain a suboptimal solution with some guaranteed accuracy by

relaxing the above lower bound test [Ibar76a]. BB algorithms with such relaxed lower bound tests are referred to as approximate BB algorithms. The lower bound test is relaxed as follows: a subproblem  $P_i$  is eliminated from further consideration if

$$g(P_i) \ge g(z) - \epsilon(z),$$

where  $\epsilon(z): \mathbf{R} \to \mathbf{R}$  (**R** is the set of real numbers) is referred to as the *allowance function*, and it must satisfy the following conditions,

- 1.  $\epsilon(z) \geq 0$ .

- 2.  $g(z_1) \le g(z_2) \Longrightarrow g(z_1) \epsilon(z_1) \le g(z_2) \epsilon(z_2)$ .

The allowance function specifies the allowable deviation of the suboptimal solution value from the optimal solution value. In fact, the suboptimal solution  $z_A$  obtained using approximate BB algorithms can be shown to deviate from the exact optimal solution  $z_o$  by:

$$g(z_A) - \epsilon(z_A) \le g(z_o) \le g(z_A).$$

Examples of allowance functions include:

- 1. Absolute error deviation allowance function:  $\epsilon(z) = \epsilon$ ,  $\epsilon \geq 0$ . The suboptimal solution is guaranteed to deviate at most by  $\epsilon$  from the exact one.

- 2. Relative error deviation allowance function:  $\epsilon(z) = \frac{\epsilon g(z)}{1+\epsilon}$ ,  $\epsilon \geq 0$ ,  $z \geq 0$ . This guarantees a relative deviation of  $\frac{\epsilon}{1+\epsilon}$ .

## **Dominance Tests**

A dominance test is performed to eliminate subproblems that cannot lead to better optimal solutions compared to other subproblems already examined. More formally, a subproblem  $P_i$  is said to dominate a subproblem  $P_j$  if  $P_j$  is known not to provide a better

feasible solution than the one that can be obtained from  $P_i$ . This binary relation between  $P_i$  and  $P_j$  is called a *dominance* relation and is denoted by  $P_i\mathbf{D}P_j$ . A test based on the dominance relation eliminates a subproblem  $P_j$  from further consideration from the selection process if there exists a subproblem  $P_i$  such that  $P_i\mathbf{D}P_j$ . A dominance relation must satisfy the following conditions [Ibar77]:

- 1.  $P_i\mathbf{D}P_j$  implies that  $f(P_i) \leq f(P_j)$  and that  $P_i$  is not a proper descendant of  $P_j$ .

- 2. D is a partial ordering. (i.e., reflexive, antisymmetric, and transitive).

- 3.  $P_i\mathbf{D}P_j$  and  $P_i \neq P_j$  imply that there exists a descendant  $P_i'$  (including  $P_i$ ) of  $P_i$  such that  $P_i'\mathbf{D}P_j'$  for any proper descendant  $P_j'$  of  $P_j$ . That is, if  $P_i\mathbf{D}P_j$ , then there exists a subproblem in the subtree rooted at  $P_i$  that dominates all subproblems in the subtree rooted at  $P_j$ .

Since a dominance relation is only a partial ordering, it is possible that neither the  $P_i \mathbf{D} P_j$  nor the  $P_j \mathbf{D} P_i$  holds. In this case  $P_i$  and  $P_j$  are said to be incomparable. A subproblem  $P_i$  is said to be a current dominating subproblem if it has been generated but has not been dominated so far. It then follows that all current dominating subproblems are incomparable to each other. In order to apply dominance tests, a set of current dominating subproblems (denoted by  $\mathcal{D}$ ) has to be maintained. When a subproblem  $P_j$  is generated, it is compared against the subproblems in  $\mathcal{D}$ . If it is incomparable to each one of them, then it is added to  $\mathcal{D}$ . If it is dominated by  $P_i \in \mathcal{D}$ , then it is deleted. Finally, if it dominates  $P_i \in \mathcal{D}$ , then  $P_i$  is deleted from  $\mathcal{D}$  and  $P_j$  is added to  $\mathcal{D}$ .

Dominance tests can greatly reduce the number of subproblems expanded, and hence the execution time of a BB algorithm. This is accomplished by storing more information, the set  $\mathcal{D}$ , and represents a typical time-space tradeoff. This tradeoff must be taken into consideration when dominance tests are employed, particularly if the dominance relation is weak and, hence, most of the subproblems are incomparable. Furthermore, in NP-hard

problems, the size of  $\mathcal{D}$  can be exponentially large [Li85]. In this study, dominance tests are assumed to be inactive.

## **Equivalence Tests**

Equivalence tests are special cases of dominance tests that are frequently used in AI applications [Ibar78a]. An equivalence test eliminates a subproblem  $P_j$  from further consideration of the branching process if there exists a subproblem  $P_i$  that is equivalent to  $P_j$  and has already been examined by the branching process. That is,  $P_j$  is deleted if it is equivalent to  $P_i$  which has already been expanded by the BB algorithm. The equivalence of two subproblems is determined by the equivalence of their representation.

# 3.1.5 The Termination Procedure

The termination procedure is used by the BB algorithm to eliminate subproblems that will not eventually lead to any feasible solutions. The termination procedure employs techniques that are highly problem dependent and require considerable knowledge about the problem domain. This knowledge is used to determine if a subproblem represents a partial solution that can be extended to a complete feasible solution.

# 3.1.6 Outline of the BB Algorithm

The following is an outline of how the algorithm uses the selection, branching, elimination and termination procedures to obtain the optimal solution to a problem.

### 1. Initialization.

- (a) The set of active subproblems is initialized to contain the original problem.

- (b) The lower bound of the incumbent is initialized to  $\infty$ . The subproblem defined by the incumbent is initially undefined.

#### 2. Selection.

- (a) The subproblem with the smallest value of the heuristic function h is selected from the set of active subproblems.

- (b) The subproblem is removed from the set.

## 3. Branching.

The branching procedure is used to generate new smaller subproblems from the one selected in (2). The lower bounds of the new subproblems are calculated.

Steps 4 to 7 are repeated for each of the new subproblems generated by the branching procedure above.

#### 4. Termination test.

The subproblem is evaluated to determine if it can lead to a feasible solution. If not, it is deleted.

#### 5. Feasibility.

- (a) The subproblem is evaluated to determine if it is a feasible solution. If it is, and its lower bound is smaller than that of the incumbent, it replaces the incumbent. Otherwise, it is deleted.

- (b) If the incumbent is updated in 5(a), then all the subproblems in the set of active subproblems A whose lower bounds are greater than that of the new incumbent are deleted from the set of active subproblems.

# 6. Lower bound test.

If the lower bound of a new subproblem is greater than the lower bound of the incumbent, the subproblem is deleted. Otherwise it is added to A if dominance tests are not being employed.

# THE UNITED

#### 7. Dominance test.

- (a) If a new subproblem is dominated by a subproblem in  $\mathcal{D}$ , then the subproblem is deleted.

- (b) If a new subproblem dominates a subproblem  $P_j \in \mathcal{D}$ , then  $P_j$  is deleted. The subproblem is added to  $\mathcal{D}$  and  $\mathcal{A}$ .

- (c) If a new subproblem is incomparable, it is added to  $\mathcal{D}$  and  $\mathcal{A}$ .

## 8. Algorithm termination.

If the set of active subproblems is not empty, steps (2)-(7) are repeated. Otherwise the algorithm terminates. The optimal solution is stored in the incumbent.

A number of researchers have examined BB algorithms and their properties. Theoretical comparisons of search strategies in BB algorithms and their effects on the average performance of BB algorithms are developed in [Ibar76b]. Various search strategies are shown to be special cases of the general heuristic search. It is also shown that when the value of the lower bound function of a subproblem is unique (i.e., the lower bound function is one-to-one), then the performance of a BB algorithm under a best-first search strategy is better than the performance of the same algorithm under breadth-first or depth-first strategies.

The effect of the accuracy of the lower bound function on the average performance of some BB algorithms for decision problems was conducted by Pearl in [Pear84]. The analysis shows that linear errors in the lower bound function cause the number of nodes generated by the BB algorithm to grow exponentially.

The computational efficiency of approximate BB algorithms is studied in [Ibar76a]. It is shown that under proper conditions the number of subproblems examined using the approximate algorithm is smaller than the number of nodes examined using the exact

one. In [WaYu85] it is shown that a linear reduction in the accuracy of the solution can result in an exponential reduction in the total number of subproblems examined by the BB algorithm. This result seems to be consistent with Pearl's result in [Pear84], since changes in the accuracy of the solution can be modeled as changes in the accuracy of the lower bound function and vice versa.

Dominance tests in BB algorithms and their effect on the performance of the BB algorithm are discussed in [Ibar77]. It is shown that under certain conditions dominance tests can enhance the performance of BB algorithms. In fact, a stronger dominance relation implies improved performance.

The above formulation of BB algorithms is also recognized as a general formulation for many heuristic procedures for searching AND/OR graphs, game trees and state-space representations in the area of AI [KuKa83].

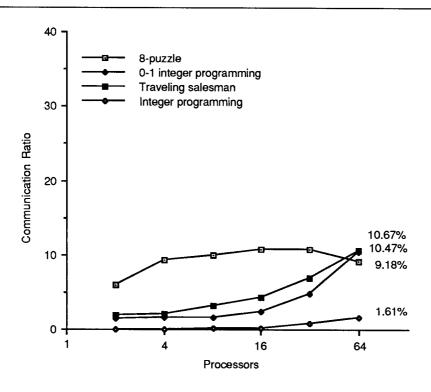

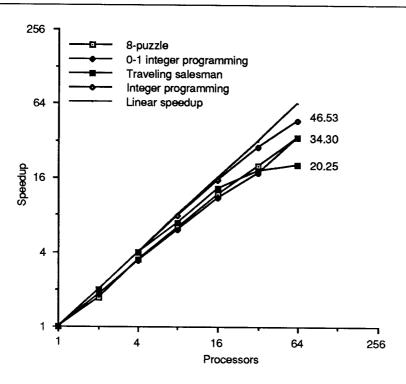

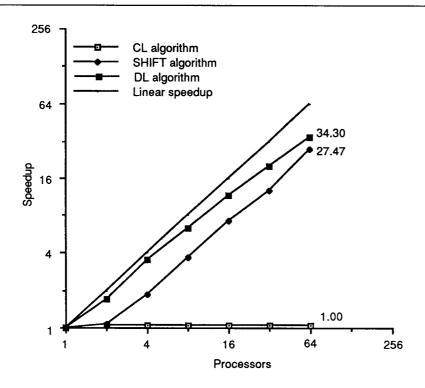

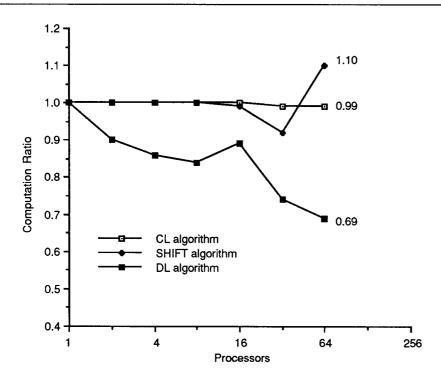

A PARE RABBER A STAR