# Near Threshold Computing: From Single Core to Many-Core Energy Efficient Architectures

by

Ronald Dreslinski, Jr.

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctorate of Philosophy (Computer Science and Engineering) in The University of Michigan 2011

#### **Doctoral Committee:**

Professor Trevor N. Mudge, Chair Professor David Blaauw Professor Dennis Michael Sylvester Assistant Professor Thomas F. Wenisch © Ronald Dreslinski, Jr. 2012

All Rights Reserved

#### ACKNOWLEDGEMENTS

I would like to start by thanking Steve Reinhardt, who in his wisdom took a chance on me as in incoming graduate student. As my advisor for my first several years here his advice was invaluable. When Steve left the University, it was Trevor Mudge who adopted Steve's students. I am thankful for the advice he gave me as I switched major research areas and began to focus on what would eventually become my thesis. His career and research advice were important to my development as a student and researcher. In addition I would like to thank Trevor for allowing me the opportunity to build my skill set by including me in countless research proposal writing sessions and allowing me a glimpse behind the curtain of being a faculty member.

In addition, I was closely advised by several other faculty members throughout my long career at the University of Michigan. I would like to acknowledge the outside advice from Chaitali Chakrabarti at Arizona State University as well as Krisztian Flautner from ARM for their thoughtful advice. Within the University of Michigan I also received weekly advice from intergroup meetings with David Blaauw, Dennis Sylvester, Thomas Wenisch, and Scott Mahlke. It was these collaborative relationships that yielded such a broad dissertation topic.

In my early years as a graduate student I was lucky to have several senior students as mentors. I would like to particularly thank Nate Binkert for my early experiences at preparing a research paper. In addition both Steve Raasch and Eric Hallnor provided useful guidance. In my early years as a graduate student I got involved designing a simulator (not something you should do if you want to graduate quickly). Through this experience I gained several important colleagues. For that reason I would like to thank those other M5 simulator developers that helped me understand how software should be written. Particularly I would like to thank Ali Saidi, Lisa Hsu, Kevin Lim, Gabe Black, and Korey Sewell in addition to those I have already mentioned earlier.

When I joined Trevor's research group I gained another set of colleagues. I wold like to particularly thank Geoff Blake for putting up with my demanding requests for perfection in every plot he made. Also I would like to thank Tae Ho Kgil, Sangwon Seo, Mark Woh, and Dave Roberts. The newer students who have worked tirelessly to help me run simulations

also deserve an acknowledgment, so thank you Joe Pusdesris, Tony Gutierrez, and Mike Cieslak.

I received a great deal of help from the circuits students working with David Blaauw and Dennis Sylvester. My closest and most rewarding work was done with Bo Zhai, Sudhir Satpathay, Dave Fick, Greg Chen, Michael Wieckowski, and Bharan Girdihar. In addition there were a whole host of other students who assisted in designing and taping out a massive 7-layer 3D stacked chip with 128 commercial cores on it (taping out a chip is the second thing I got involved with that you should not do if you want to graduate quickly), and for there help I am grateful.

Of course I needed some people to help keep my mind off of research every waking minute and for that I would like to thank my friends at the Blue Leprechaun, Brown Jug, and Good Time Charley's. In particular several friends helped me keep one foot in reality during all these years and those are Jeff Wegehaupt, Nenad Milosavljevic, Mike Gradillas, Jose Orozco, Matt Petry, and Thomas M. Dziuszko.

Lastly I would like to thank my family for helping me make it through all these years. In particular my parents Ronald and Margaret for there patience and monetary help. And my sisters Kathy and Laurie for being everything a brother needed and more.

# TABLE OF CONTENTS

| ACKNOWLED    | GEMENTS                                                   |

|--------------|-----------------------------------------------------------|

| LIST OF FIGU | RES viii                                                  |

| LIST OF TABL | ES xii                                                    |

| ABSTRACT     |                                                           |

| CHAPTER      |                                                           |

| 1. Introd    | uction                                                    |

| 2. Near T    | Threshold Operation                                       |

| 2.1          | Defining Operating Regions                                |

| 2.2          | NTC Analysis                                              |

| 2.3          | NTC in Different Computing Segments                       |

|              | 2.3.1 NTC Integration in Ultra Energy-Efficient Servers 8 |

|              | 2.3.2 NTC Integration in Personal Computing 9             |

|              | 2.3.3 NTC Integration in Sensor Networks                  |

| 2.4          | NTC Barriers                                              |

|              | 2.4.1 Performance Loss                                    |

|              | 2.4.2 Increased Performance Variation                     |

|              | 2.4.3 Increased Functional Failure                        |

| 2.5          | Addressing NTC Barriers                                   |

|              | 2.5.1 Addressing Performance Loss                         |

|              | 2.5.2 Addressing Performance Variation                    |

|              | 2.5.3 Addressing Functional Failure                       |

| 2.6          | Conclusions                                               |

| 3. Single    | Core Architectures                                        |

| 3.1          | Introduction                                              |

| 3.2          | Low Voltage Tolerant SRAM cell design                     |

| 3.3       | Energy Efficient Cache Architectures          | 25 |

|-----------|-----------------------------------------------|----|

|           | 3.3.1 Near Threshold Filter Cache             |    |

|           | 3.3.2 RENT Caches                             | 27 |

|           | 3.3.3 Alternative RENT Caches                 | 30 |

| 3.4       | Methodology                                   | 31 |

|           | 3.4.1 Simulation Environment                  | 31 |

|           | 3.4.2 Benchmarks                              | 32 |

|           | 3.4.3 Energy Models                           | 32 |

| 3.5       | Results                                       | 33 |

|           | 3.5.1 Filter Cache                            | 33 |

|           | 3.5.2 RENT Cache                              | 37 |

|           | 3.5.3 Alternative RENT Cache                  | 39 |

|           | 3.5.4 Spec2000 Analysis                       | 40 |

|           | 3.5.5 Power Savings Mode                      | 40 |

|           | 3.5.6 Technology Node Comparison              | 40 |

|           | 3.5.7 Additional Analysis                     | 42 |

| 3.6       | Related Work                                  | 42 |

| 3.7       | Conclusion                                    | 44 |

| 3.7       | Conclusion                                    |    |

| 4. Multi- | -Core Architectures                           | 45 |

| 4.1       | Introduction                                  | 45 |

| 4.2       | Proposed Near Threshold Architecture          | 47 |

| 1.2       | 4.2.1 New Memory Architecture                 | 47 |

|           | 4.2.2 Architectural Trade-offs                | 48 |

| 4.3       | Benchmarks for Evaluating the Design          | 51 |

| 4.4       | Simulation Methodology                        | 51 |

|           | 4.4.1 Power Models                            | 51 |

|           |                                               | 53 |

|           | 4.4.3 Simulation Configurations               |    |

| 4.5       | Results                                       | 54 |

| 7.5       | 4.5.1 Optimal L1 Size                         | 54 |

|           | 4.5.2 Optimal Cluster Size                    | 55 |

|           | 4.5.3 Various Energy Savings Modes            | 57 |

|           | 4.5.4 Multi-Dimensional Analysis              | 58 |

|           | 4.5.5 Global Optimal Solutions                | 63 |

|           | 4.5.6 Optimality under Different Performances | 63 |

| 4.6       | Split L1 Cache                                | 65 |

| 4.0       | 4.6.1 Architectural Trade-offs                | 66 |

|           |                                               | 67 |

|           | 2,7                                           |    |

| 4.7       |                                               | 67 |

|           | Related Work                                  | 68 |

| 4.8       | Conclusions                                   | 69 |

| 5. Signal | Processing Architectures                      | 70 |

| 5.1        | Motivation                                       |   |   |       | <br>70  |

|------------|--------------------------------------------------|---|---|-------|---------|

| 5.2        | DSC Algorithm Analysis                           |   |   |       | <br>72  |

|            | 5.2.1 DSC Signal Processing Pipeline             |   |   |       | <br>72  |

|            | 5.2.2 Characteristics of DSC Algorithms          |   |   |       |         |

| 5.3        | Diet SODA Architecture                           |   |   |       | <br>74  |

|            | 5.3.1 Diet SODA PE Design                        |   |   |       | <br>74  |

|            | 5.3.2 SIMD Pipeline Width                        |   |   |       |         |

|            | 5.3.3 Scatter-Gather Data Prefetcher             |   |   |       | <br>77  |

|            | 5.3.4 Operating Modes                            |   |   |       | <br>78  |

|            | 5.3.5 Mapping Example: CFA Interpolation         |   |   |       | <br>79  |

| 5.4        | Results and Analysis                             |   |   |       | <br>81  |

|            | 5.4.1 Methodology                                |   |   |       | <br>81  |

|            | 5.4.2 Area and Power                             |   |   |       | <br>82  |

|            | 5.4.3 Performance                                |   |   |       | <br>83  |

|            | 5.4.4 Comparison With Other Solutions            |   |   |       | <br>84  |

| 5.5        | Conclusion                                       |   |   |       | <br>85  |

|            |                                                  |   |   |       |         |

| 6. Voltage | e Boosting                                       | • | • | <br>• | <br>87  |

| 6.1        | Introduction                                     |   |   |       | <br>87  |

| 6.2        | NTC Impact on Single Thread Performance          |   |   |       |         |

|            | 6.2.1 Parallelization Complications              |   |   |       |         |

| 6.3        | Circuit Techniques                               |   |   |       |         |

|            | 6.3.1 Boosting via Dual- $V_{dd}$                |   |   |       |         |

|            | 6.3.2 Boosting Degree via DVFS                   |   |   |       |         |

| 6.4        | Boosting Architectures                           |   |   |       | <br>95  |

|            | 6.4.1 Designs and Tradeoffs                      |   |   |       | <br>95  |

|            | 6.4.2 Tradeoff Analysis                          |   |   |       | <br>97  |

|            | 6.4.3 Methodology                                |   |   |       | <br>98  |

|            | 6.4.4 Simulator and Benchmarks                   |   |   |       | <br>98  |

|            | 6.4.5 Results                                    |   |   |       | <br>98  |

| 6.5        | Transactional Bottlenecks                        |   |   |       | <br>100 |

|            | 6.5.1 Methodology                                |   |   |       | <br>100 |

|            | 6.5.2 Simulator and Benchmarks                   |   |   |       | <br>101 |

|            | 6.5.3 Results                                    |   |   |       | <br>101 |

| 6.6        | Web Server Latency                               |   |   |       | <br>103 |

|            | 6.6.1 Improving Server Response Time             |   |   |       | <br>103 |

|            | 6.6.2 Methodology                                |   |   |       | <br>104 |

|            | 6.6.3 Results                                    |   |   |       |         |

| 6.7        | Related Work                                     |   |   |       | <br>107 |

|            | 6.7.1 Dynamic Voltage Scaling                    |   |   |       |         |

|            | 6.7.2 Heterogenous Architectures for Bottlenecks |   |   |       | <br>108 |

| 6.8        | Conclusions                                      |   |   |       | <br>108 |

| 7. Many-  | Core Architectures                       | 10 |

|-----------|------------------------------------------|----|

| 7.1       | Introduction                             | 10 |

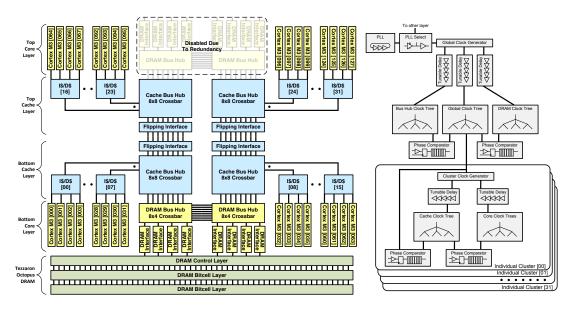

| 7.2       | Top Level Architecture                   | 13 |

|           | 7.2.1 Variable Cache Access Architecture |    |

|           | 7.2.2 Clock Network                      | 15 |

| 7.3       | Final Layout                             | 18 |

| 7.4       | Evaluation                               | 20 |

| 8. Relate | d Work                                   | 21 |

| 8.1       | Subthreshold Circuits and Architectures  | 21 |

| 8.2       | Energy-Performance Tradeoff Analysis     | 21 |

| 9. Conclu | <b>usions</b>                            | 22 |

| (OGRAPI   | I <b>V</b> 1                             | 23 |

# LIST OF FIGURES

| <b>Figure</b> |                                                                                     |    |

|---------------|-------------------------------------------------------------------------------------|----|

| 1.1           | Technology scaling trends of supply voltage and energy                              | 2  |

| 2.1           | Energy and delay in different supply voltage operating regions                      | 6  |

| 2.2           | Subliminal processor frequency and energy breakdowns at various supply              |    |

|               | voltages.                                                                           | 7  |

| 2.3           | Phoenix frequency and energy breakdowns at various supply voltages                  | 8  |

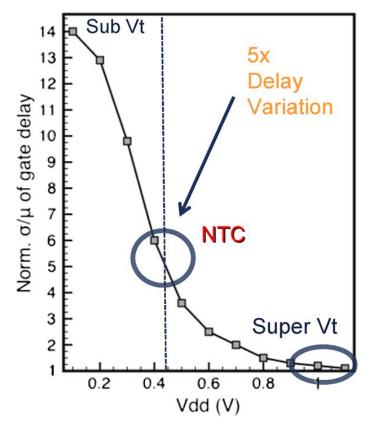

| 2.4           | Impact of voltage scaling on gate delay variation                                   | 11 |

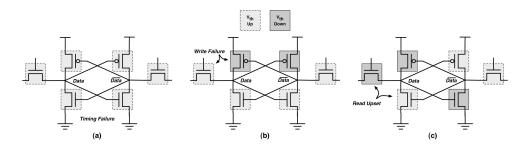

| 2.5           | Effects of global and local variation on a standard 6T SRAM cell. (a)               |    |

|               | Global $V_{th}$ reduction resulting in timing failure. (b) Global $V_{th}$ P-N skew |    |

|               | resulting in write failure. (c) Local $V_{th}$ mismatch resulting in read upset.    | 12 |

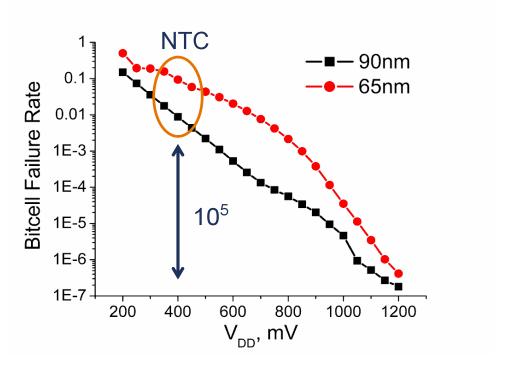

| 2.6           | Impact of voltage scaling on SRAM failure rates                                     | 13 |

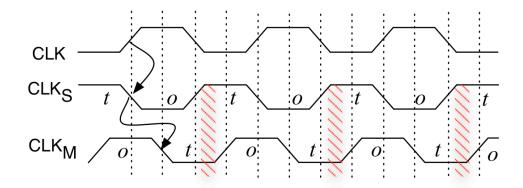

| 2.7           | Delaying the master clock creates a window of transparency                          | 15 |

| 2.8           | FIR filter with soft edge clocking compared to standard flip-flops (SFF);           |    |

|               | presented with and without useful skew                                              | 15 |

| 2.9           | Body biasing techniques for three target frequencies                                | 17 |

| 2.10          | Alternative 8T SRAM cell, decoupling the read and write [18]                        | 18 |

| 2.11          | Alternative 10T SRAM cell [16]                                                      | 19 |

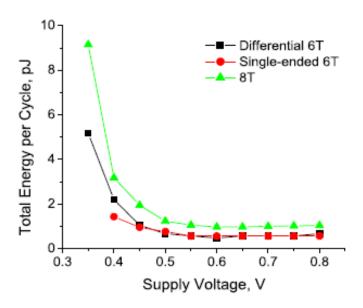

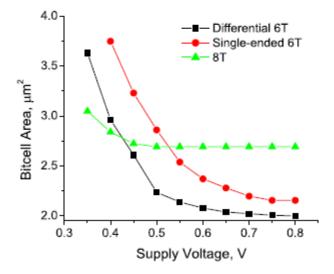

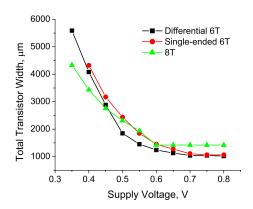

| 2.12          | Energy of SRAM topologies for 20-cycle L2 cache across voltages                     | 20 |

| 2.13          | Size of SRAM topologies for 20-cycle L2 cache across voltages with iso-             |    |

|               | robustness                                                                          | 20 |

| 3.1           | SRAM Cell area (measured in total transistor width) at different supply             |    |

|               | voltages to maintain ISO-Robustness.                                                | 24 |

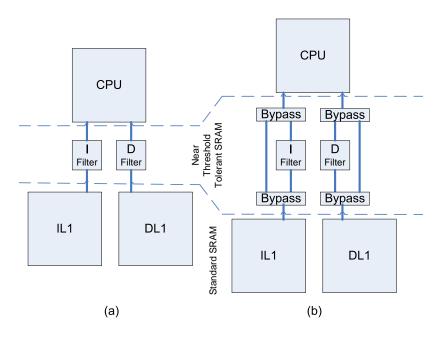

| 3.2           | Near threshold filter cache architectures (a) with and (b) without bypass           |    |

|               | networks                                                                            | 26 |

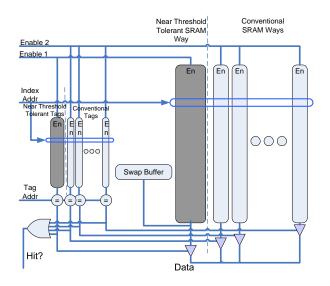

| 3.3           | Cache architecture of the RENT cache                                                | 28 |

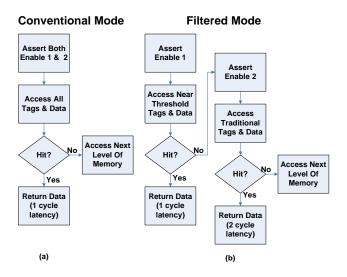

| 3.4           | RENT cache access policy flow charts for (a) conventional mode and (b)              | •  |

| 2.5           | filtered mode                                                                       | 29 |

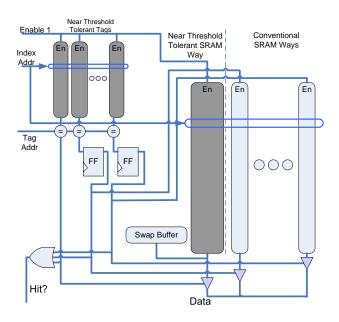

| 3.5           | Architecture of the alternative RENT cache                                          | 30 |

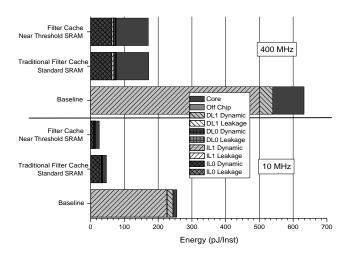

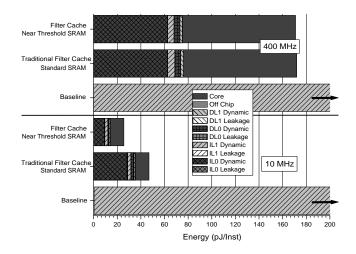

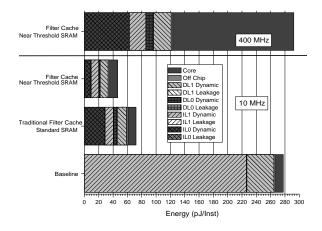

| 3.6           | Filter cache energy breakdown for BitCount benchmark                                | 34 |

| 3.7           | Filter cache energy for BitCount benchmark (Zoomed In).                             | 35 |

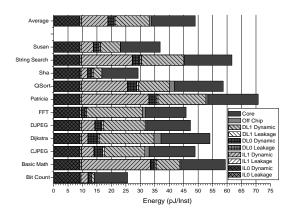

| 3.8           | NT filter cache energy breakdowns for all Benchmarks at 10MHz                       | 36 |

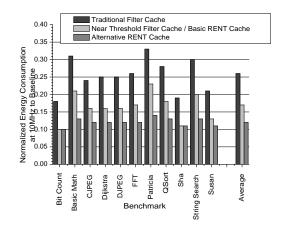

| 3.9           | Cache energy comparisons for all benchmarks normalized to the baseline              | 20 |

| 2.10          | at 10MHz.                                                                           |    |

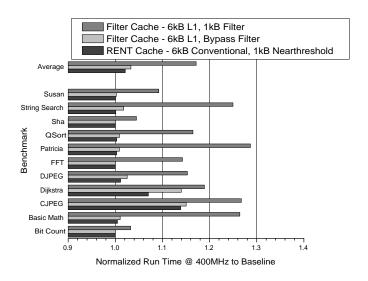

| 3.10          | Normalized runtimes at full voltage to baseline machine                             | 37 |

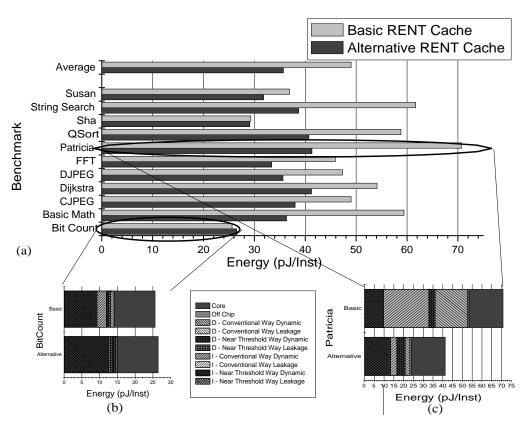

| 3.11        | Comparison of energy breakdowns for RENT cache policies (a) for all benchmarks at 10MHz. With a breakdown of energy for (b) Bitcount and |          |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------|----------|

|             | (c) Patricia                                                                                                                             | 38       |

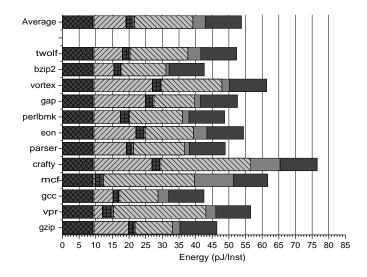

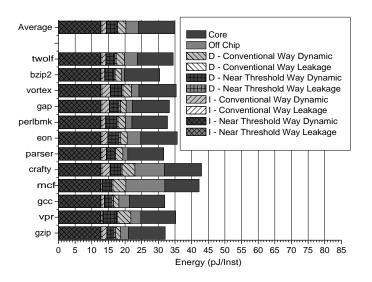

| 3.12        | Energy breakdowns for the GZIP benchmark                                                                                                 |          |

| 3.13        | Energy breakdown for SpecInt 2000 benchmarks with the basic RENT                                                                         |          |

| 2.12        | cache at 10MHz.                                                                                                                          | 41       |

| 3.14        | Alternative RENT.                                                                                                                        |          |

| 3.15        | Normalized Cache Energy for Average MIBench Performance at Differ-                                                                       |          |

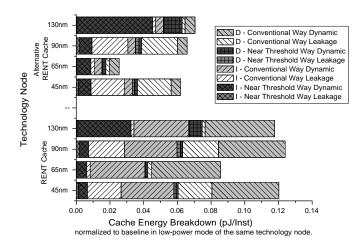

| 0,10        | ent Technology Nodes.                                                                                                                    | 42       |

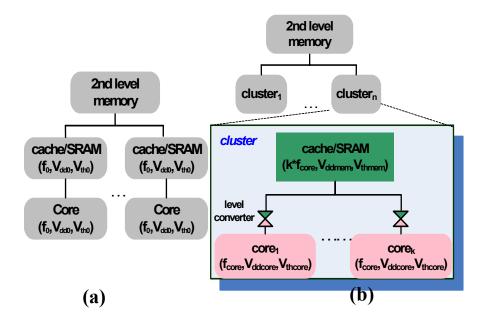

| 4.1         | Conventional (a) and proposed (b) multi-processor architectures                                                                          |          |

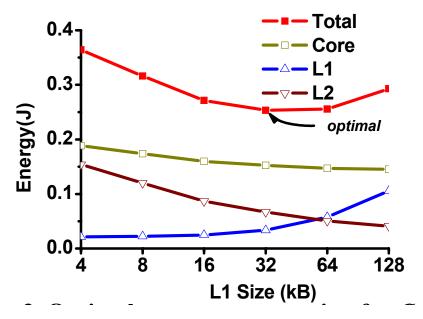

| 4.2         | Optimal energy consumption for <i>Cholesky</i> when using one core and one                                                               |          |

|             | L1                                                                                                                                       | 55       |

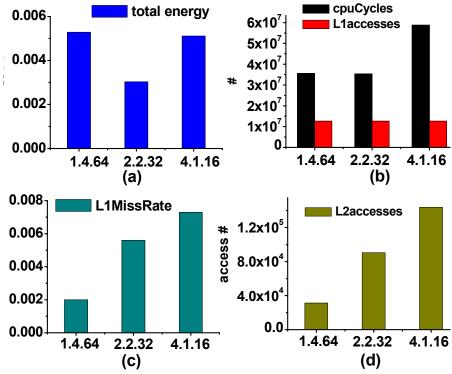

| 4.3         | Three configuration comparison                                                                                                           |          |

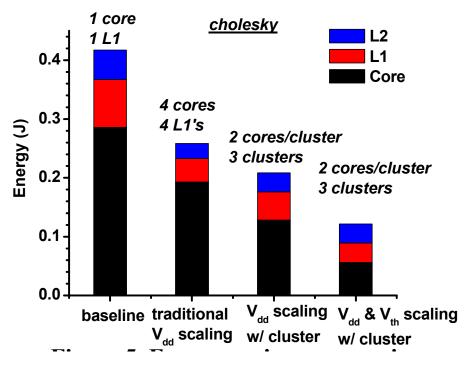

| 4.4         | Energy savings comparison using various scaling methods                                                                                  |          |

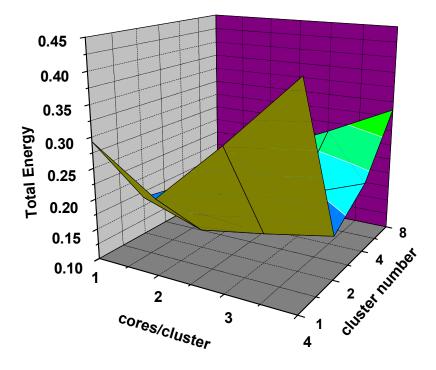

| 4.5         | Total Energy for <i>Cholesky</i>                                                                                                         |          |

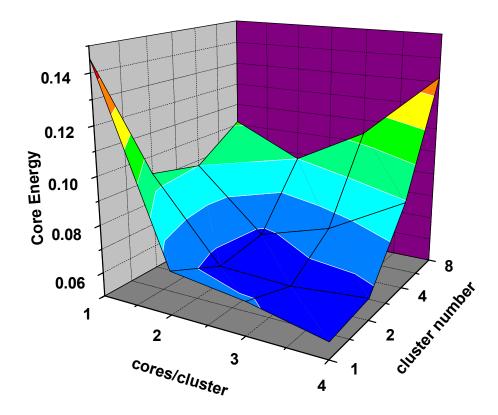

| 4.6         | Core Energy for <i>Cholesky</i>                                                                                                          |          |

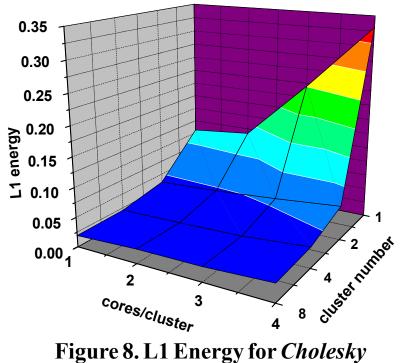

| 4.7         | L1 Energy for <i>Cholesky</i>                                                                                                            | 61       |

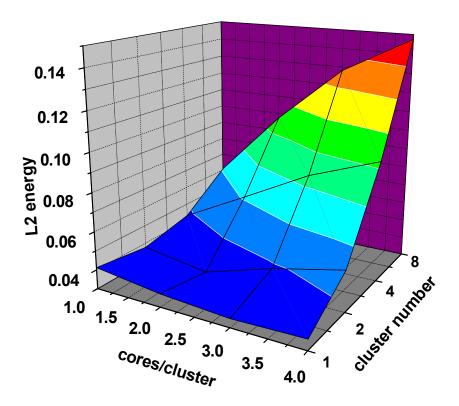

| 4.8         | L2 Energy for <i>Cholesky</i>                                                                                                            | 62       |

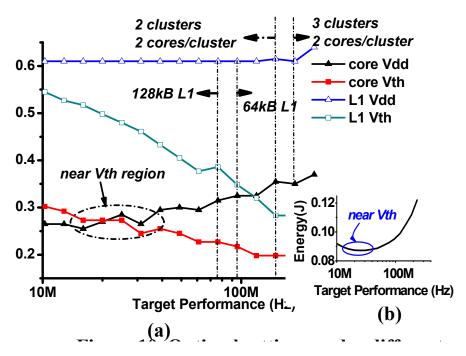

| 4.9         | Optimal settings under different target performances                                                                                     | 64       |

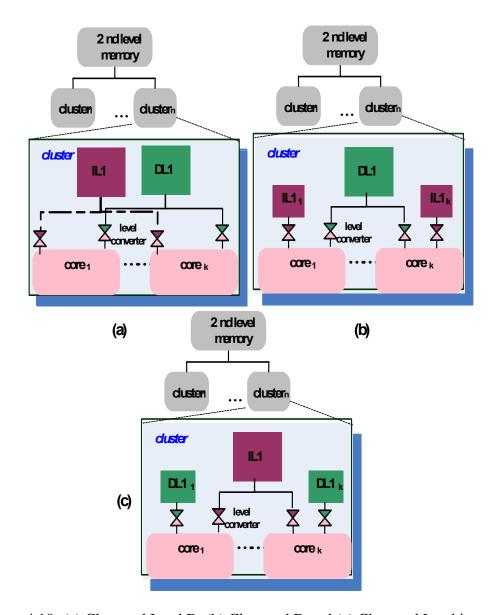

| 4.10        | (a) Clustered I and D, (b) Clustered D and (c) Clustered I architectures                                                                 | 65       |

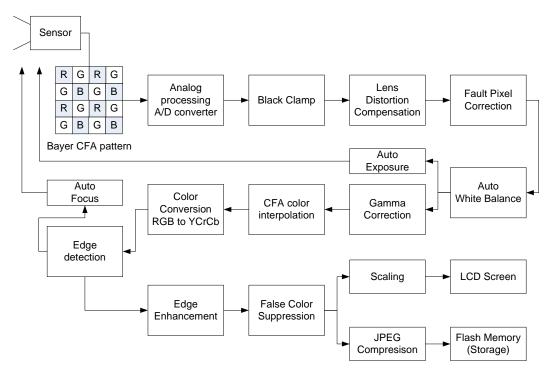

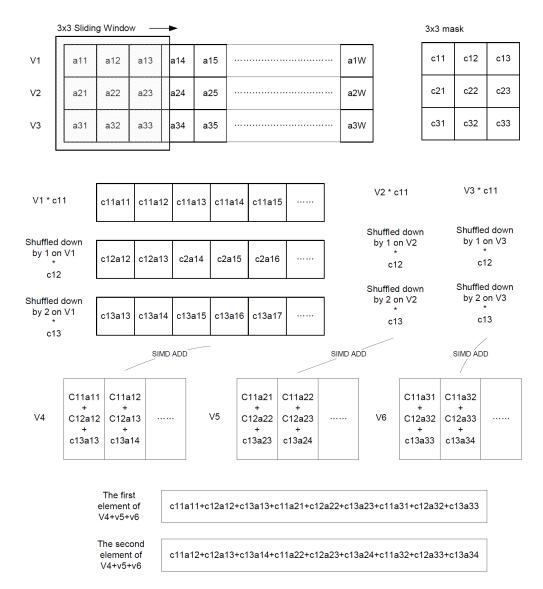

| 5.1         | A typical DSC image signal processing pipeline [21], [41]                                                                                | 72       |

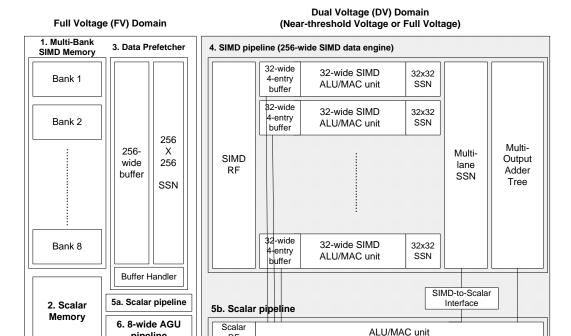

| 5.2         | Diet SODA processing element (PE) for DSCs. The PE contains two                                                                          |          |

|             | different voltage domains: full voltage (FV) and dual voltage (DV). DV                                                                   |          |

|             | domain operates at either full or near-threshold supply voltage. The PE                                                                  |          |

|             | consists of: 1) multi-banked SIMD memory; 2) scalar memory; 3) SIMD                                                                      |          |

|             | data prefetcher; 4) SIMD pipeline; 5a) scalar pipeline in full voltage do-                                                               |          |

|             | main; 5b) scalar pipeline in dual voltage domain; and 6) 8-wide address                                                                  |          |

|             | generation unit (AGU) pipeline                                                                                                           | 75       |

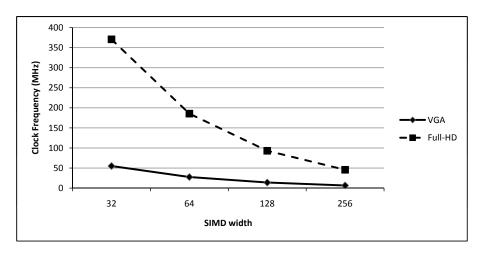

| 5.3         | Minimum clock frequencies based on different SIMD width configura-                                                                       |          |

|             | tions to run the preview mode of DSC signal processing pipeline shown                                                                    |          |

| ~ ·         | in Figure 5.1.                                                                                                                           | 76       |

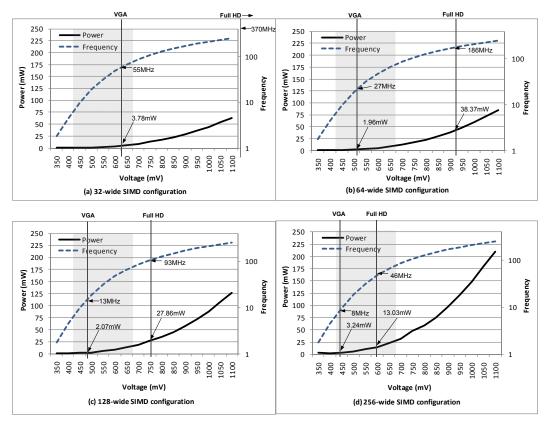

| 5.4         | Near-threshold operation is applied to four different SIMD width config-                                                                 |          |

|             | urations: 32, 64, 128, and 256. Solid vertical lines provide guidelines                                                                  |          |

|             | for the minimum supply voltage necessary to meet VGA and full-HD                                                                         | 77       |

| <i>5 5</i>  | processing demands. Gray boxes represent the near-threshold regions                                                                      | 77       |

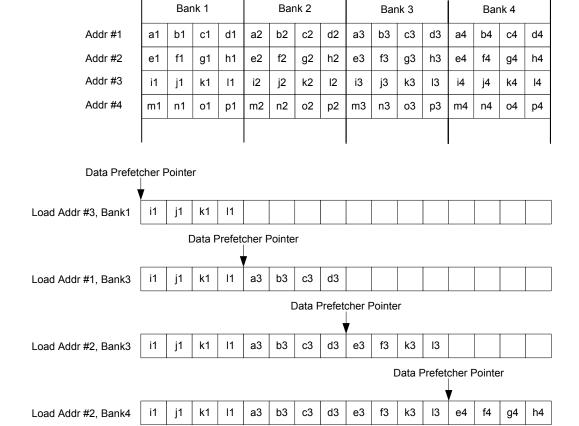

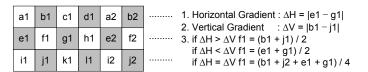

| 5.5         | Example of complex data shuffling with 4-bank 4-wide SIMD memory,                                                                        | 70       |

| 5.6         | SIMD data prefetcher, and 16-wide buffer                                                                                                 | 78<br>81 |

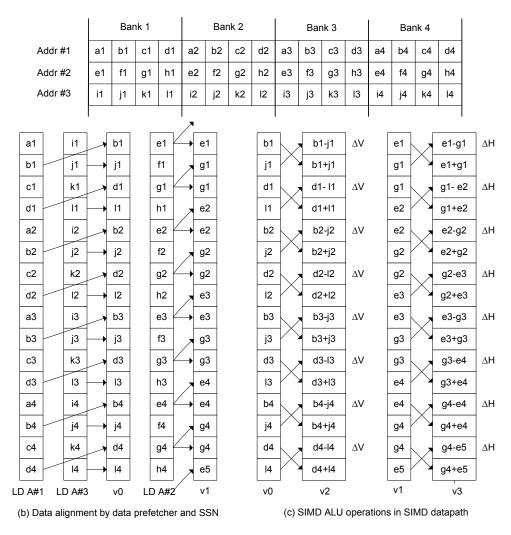

| 5.7         | An Edge-directed CFA interpolation mapped on Diet SODA                                                                                   | 01       |

| 3.7         | mask is applied to 3x3 pixels                                                                                                            | 82       |

| 5.8         | A Test DSC image signal pipeline [21]                                                                                                    |          |

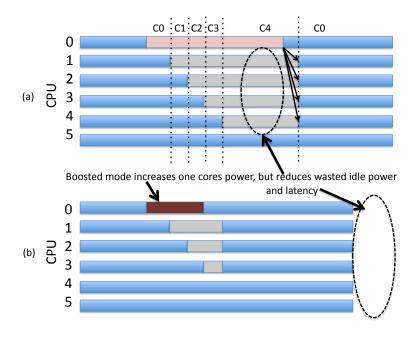

| 6.1         | (a) Amdahl bottleneck in a system and how boosting (b) can be used to                                                                    | 04       |

| 0.1         | improve the system.                                                                                                                      | 90       |

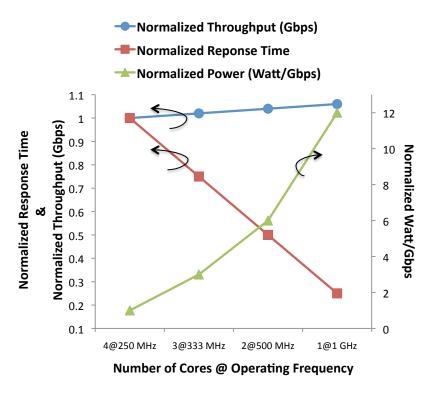

| 6.2         | SpecWeb99 latency, throughput, and power for various parallel operating                                                                  | 70       |

| J. <u>_</u> | points                                                                                                                                   | 91       |

|             |                                                                                                                                          |          |

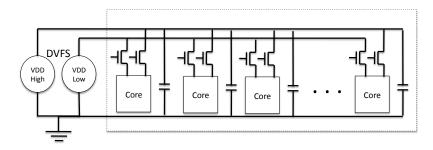

| 6.3        | Dual- $V_{dd}$ chip. Each core provides decap on high voltage rail to allow a single core to boost in 10's of cycles. DVFS can be used on external power supplies to adjust degree of boosting over longer time frames. Area overhead of decap and power transistors is 5-10% for 16 cores. Either |     |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|            | an additional metal layer is needed to route the second power grid, or an additional 10% area overhead[10,22]                                                                                                                                                                                      | 92  |

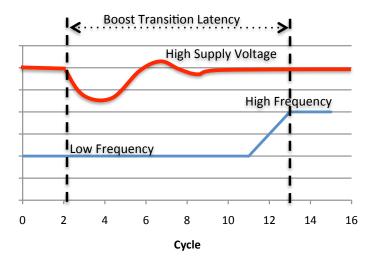

| 6.4        | Boost transition. When boosting occurs, voltage droops on the high sup-                                                                                                                                                                                                                            |     |

|            | ply, core remains at low frequency. Once stable the frequency changes                                                                                                                                                                                                                              | 93  |

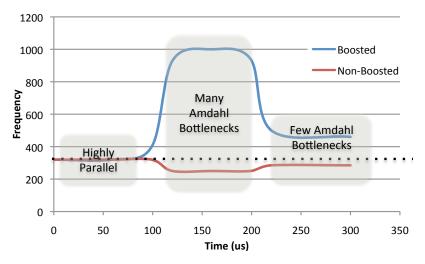

| 6.5        | DVFS Techniques to adjust boosting degree. DVFS operates over 10's of microseconds and responds to changes in workload characteristics. The more bottlenecks in the system, the greater the boosting difference                                                                                    | 94  |

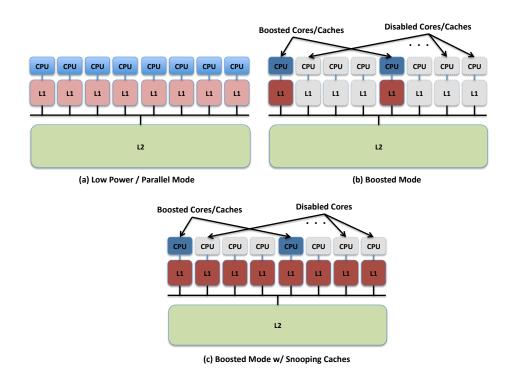

| 6.6        | Traditional CMP Architectures and Boosting Options (a) Non-Boosted,                                                                                                                                                                                                                                | 94  |

| 0.0        | (b) Boosted, (c) Boosted w/ Snooping                                                                                                                                                                                                                                                               | 96  |

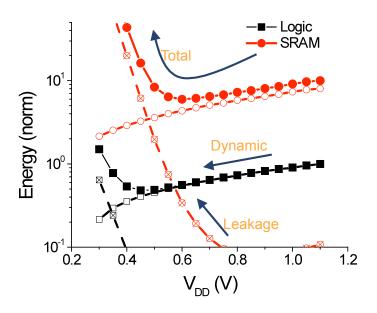

| 6.7        | Difference in energy optimal SRAM and Logic. Note SRAM has an op-                                                                                                                                                                                                                                  |     |

|            | timal at higher voltages, enabling NTC architectures                                                                                                                                                                                                                                               | 96  |

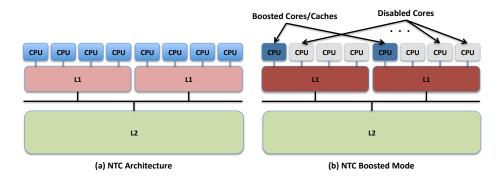

| 6.8        | NTC Architecture (a) Non-Boosted, (b) Boosted                                                                                                                                                                                                                                                      | 97  |

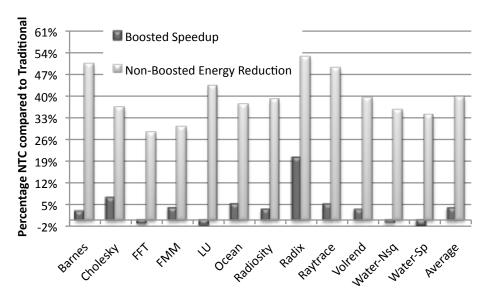

| 6.9        | Comparison of NTC against Traditional Architectures. NTC is 40% more                                                                                                                                                                                                                               |     |

|            | energy efficient in non-boosted mode, and runs 4% faster in boosted mode                                                                                                                                                                                                                           | 00  |

| 6.10       | on average                                                                                                                                                                                                                                                                                         | 99  |

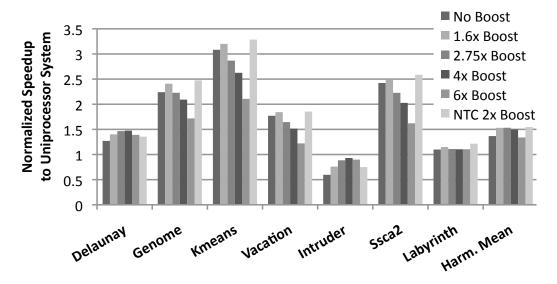

| 0.10       | cases where parallel low voltage systems do not perform as well as a                                                                                                                                                                                                                               |     |

|            | uniprocessor system, boosting techniques help to regain some of the lost                                                                                                                                                                                                                           |     |

|            | performance. All configurations are under same TDP                                                                                                                                                                                                                                                 | 102 |

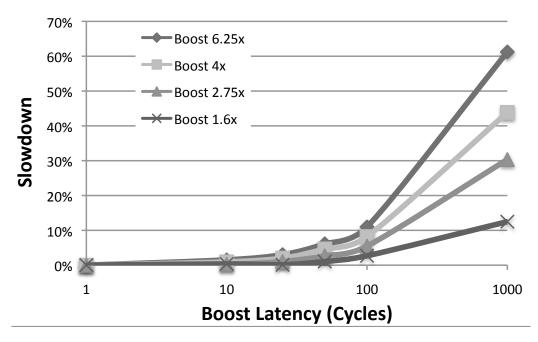

| 6.11       | Impact of boost latency on system for the Intruder benchmark. For laten-                                                                                                                                                                                                                           |     |

|            | cies under 100 cycles, the overhead is less than 10%                                                                                                                                                                                                                                               |     |

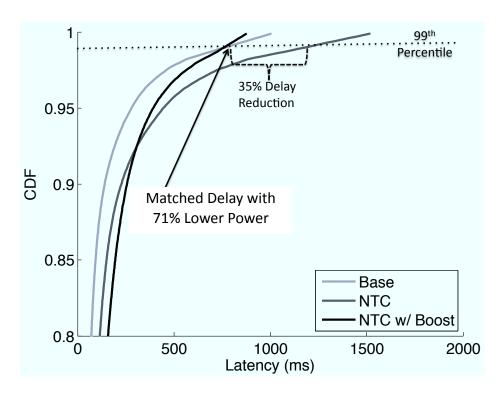

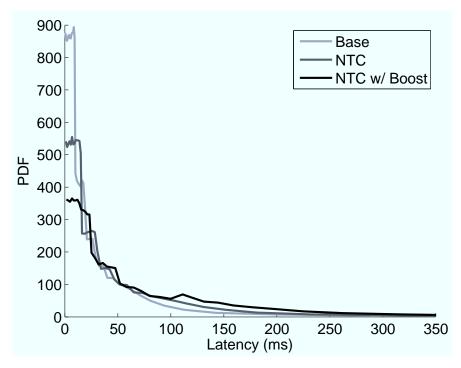

| 6.12       | Response Time CDF                                                                                                                                                                                                                                                                                  |     |

| 6.13       | Response Time PDF                                                                                                                                                                                                                                                                                  | 105 |

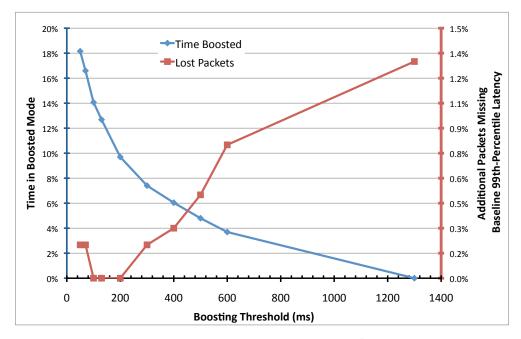

| 6.14       | Breakdown of Baseline, NTC without boosting, and several boosting                                                                                                                                                                                                                                  |     |

|            | thresholds. Showing the impact of boosting threshold on latency, power, and boosting percentages. 16-core system. Power normalized to 100W                                                                                                                                                         |     |

|            | Baseline                                                                                                                                                                                                                                                                                           | 106 |

| 6.15       | Impact of boosting threshold on the $99^{th}$ -Percentile latencies                                                                                                                                                                                                                                |     |

| 7.1        | Cross section of the 3D stacked Centip3De chip                                                                                                                                                                                                                                                     |     |

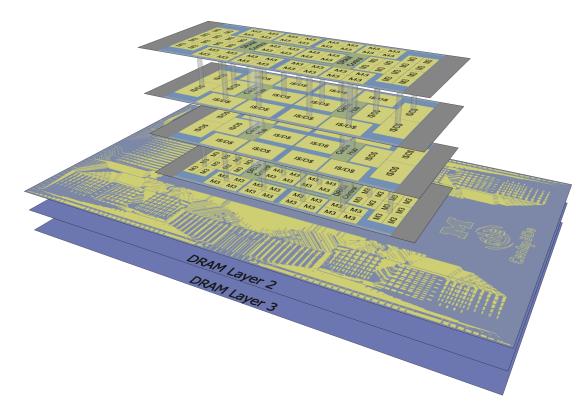

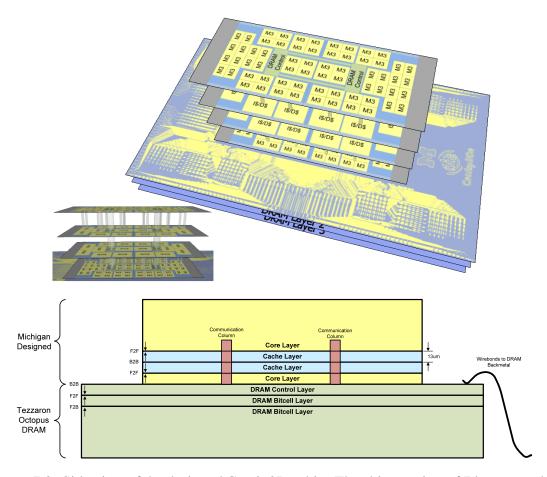

| 7.2        | Side view of the designed Centip3De chip. The chip consists of 7 layers                                                                                                                                                                                                                            |     |

|            | stacked and connected with through-silicon-vias. There are 4 logic lay-                                                                                                                                                                                                                            |     |

|            | ers consisting of cores and caches, 2 layers of DRAM cells, and 1 layer                                                                                                                                                                                                                            |     |

|            | of DRAM controller and bond routing. There are 128 ARM M3 cores                                                                                                                                                                                                                                    |     |

| <b>5</b> 2 | clustered in groups of 4 sharing a cache                                                                                                                                                                                                                                                           | 112 |

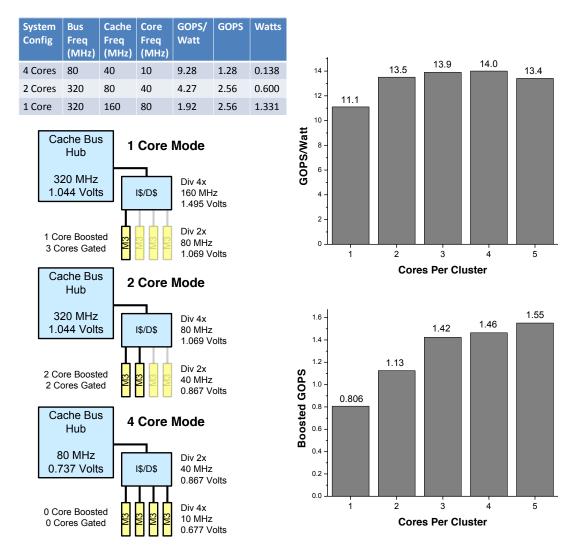

| 7.3        | Diagram showing how 1, 2, and 4 core mode works in the Centip3De                                                                                                                                                                                                                                   |     |

|            | system as well as analysis that shows the impact of clustering cores on Performance per Watt                                                                                                                                                                                                       | 112 |

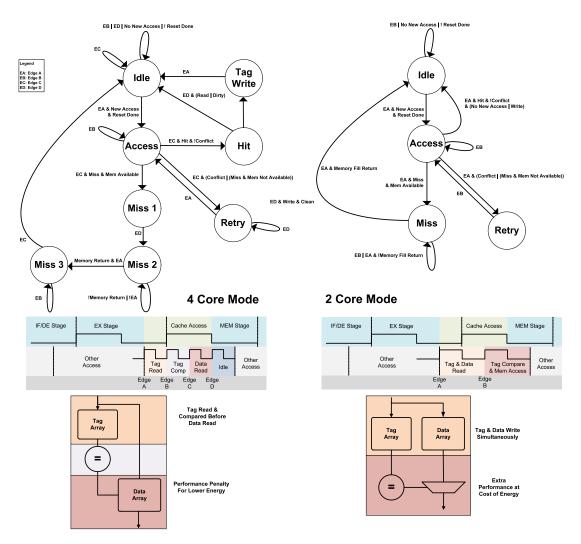

| 7.4        | State diagram for cache accesses in 4 and 2 core mode. Note the access                                                                                                                                                                                                                             | 113 |

| ,          | pattern is the same for 1 core mode                                                                                                                                                                                                                                                                | 116 |

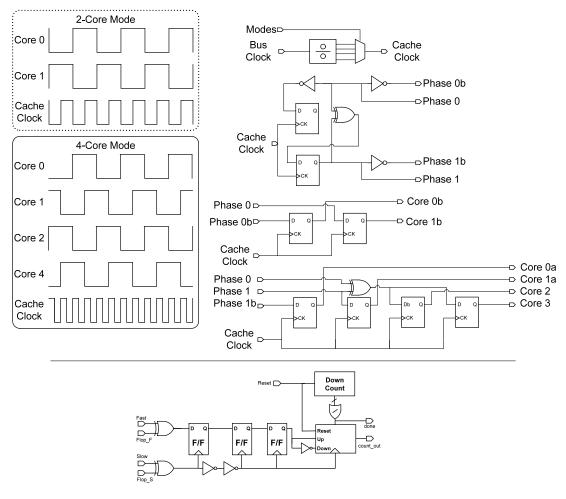

| 7.5        | Circuit diagrams for level convertors and clock dividers in the Centip3De                                                                                                                                                                                                                          | 0   |

|            | chip                                                                                                                                                                                                                                                                                               | 117 |

| 7.6  | Diagram of the clock tree design for the 128 cores, 32 caches, and mem- |

|------|-------------------------------------------------------------------------|

|      | ory controllers                                                         |

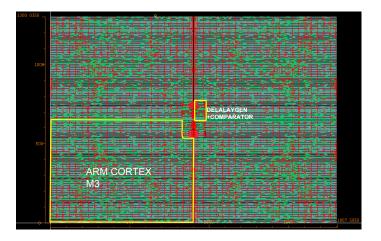

| 7.7  | Final layout of the 4 core tile used in Centip3De                       |

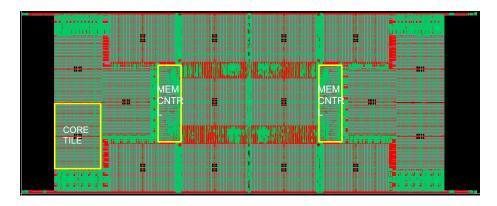

| 7.8  | Final layout of the entire core layer in Centip3De                      |

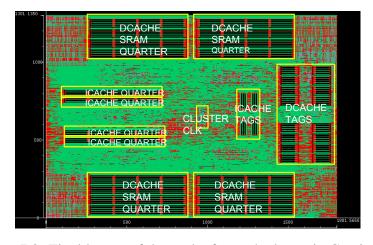

| 7.9  | Final layout of the cache for each cluster in Centip3De                 |

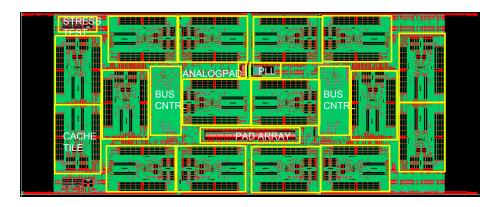

| 7.10 | Final layout of the entire cache layer in Centip3De                     |

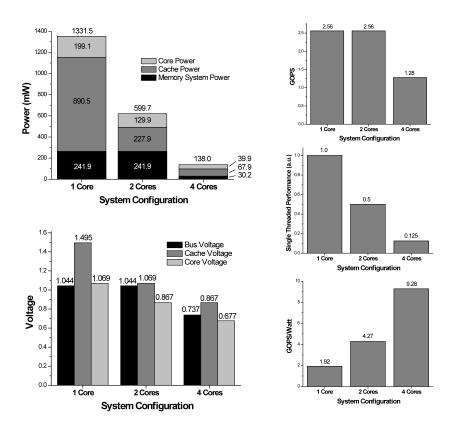

| 7.11 | Power breakdown, operating voltages, and system analysis for the Cen-   |

|      | tip3De chip in 1, 2, and 4 core mode                                    |

# LIST OF TABLES

| <u>Table</u> |                                                                                                                                                                                                                                                                               |     |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1          | Simulated System Parameters. *Body-Biasing used to meet timing con-                                                                                                                                                                                                           | 2.5 |

|              | straints.                                                                                                                                                                                                                                                                     | 32  |

| 3.2          | Simulated System Parameters for RENT Cache                                                                                                                                                                                                                                    | 38  |

| 4.1          | Baseline Architecture                                                                                                                                                                                                                                                         | 52  |

| 4.2          | Each Benchmarks Optimal Configuration. $k$ : number of cores per cluster; $n_c$ : number of clusters; *L1 size is per cluster. Energy Savings is relative to baseline uniprocessor machine                                                                                    | 63  |

| 4.3          | Each Benchmarks Optimal Configuration for split L1. $k$ : number of cores per cluster; $n_c$ : number of clusters; *L1 size is per cluster. Energy Savings is relative to baseline uniprocessor machine                                                                       | 67  |

| 5.1          | Data level parallelism analysis for DSC image signal processing algorithms. Instructions are categorized into three groups: SIMD, scalar, and overhead instructions                                                                                                           | 73  |

| 5.2          | Architectural modules that are turned on and off for dual voltage (DV) and full voltage (FV) modes                                                                                                                                                                            | 79  |

| 5.3          | Area and Power Summary of Diet SODA for Preview Mode of Full-HD Images at 30 fps. For comparison, the results of both DV mode and FV mode are presented. The eDRAM proposed in [74] are used for SIMD local memory                                                            | 83  |

| 5.4          | The Latencies of DSC signal processing pipeline algorithms for the preview mode of a VGA image and a Full-HD image                                                                                                                                                            | 84  |

| 5.5          | Execution Time Comparison with TI TMS320C64x, CRISP, and Diet SODA. Task Group 1 - White Balance, Gamma Correction, CFA Interpolation; Task Group 2 - Noise Reduction, Smooth Filter; Task Group 3 - Color Space Conversion, Edge Enhancement. *Diet SODA operates in DV mode | 85  |

| 5.6          | Chip Statistics and Energy Comparison with TI TMS320C64x, CRISP and Diet SODA. *Area and energy are normalized to 90nm technology. **Diet SODA operates in DV mode - 1V and 600mV                                                                                             | 85  |

| 6.1          | Summary of the tradeoffs of each boosting architecture. + Good, - Bad, 0 Neutral                                                                                                                                                                                              | 98  |

| 6.2          | Simulation Parameters for Transactional Memory Analysis                                                                                                                                                                                                                       | 100 |

#### **ABSTRACT**

Near Threshold Computing: From Single Core to Many-Core Energy Efficient Architectures

by

Ronald Dreslinski, Jr

Chair: Trevor N. Mudge

Over the past four decades, the number of transistors on a chip has increased exponentially in accordance with Moore's law. This has led to progress in diversified computing applications, such as health care, education, security, and communications. A number of societal projections and industrial roadmaps are driven by the expectation that these rates of improvement will continue, but the impediments to growth are more formidable today than ever before. The largest of these barriers is related to energy and power dissipation, and it is not an exaggeration to state that developing energy-efficient solutions is critical to the survival of the semiconductor industry. Extensions of today's solutions can only go so far, and without improvements in energy efficiency they are in danger of running out of steam.

When examining the history of computers, a pattern emerges: successive generations of technologies, ranging from vacuum tubes to bipolar to NMOS-based technologies, were replaced when their energy overheads became prohibitive. However, there is no clear successor to todays technology, CMOS. The available alternatives are far from being commercially viable, and none has gained sufficient traction, or provided the economic justification for overthrowing the large investments made in today's CMOS-based infrastructure. Therefore, there is a strong case supporting the position that solutions to the power conundrum must come from enhanced devices, design styles and architectures, rather than a reliance on the promise of radically new technologies becoming commercially viable. This dissertation proposes that the solution to this energy crisis is the universal application of aggressive low voltage operation across all computation platforms. This can be accomplished by targeting so-called "near-threshold computing" (NTC) and by proposing novel methods to

overcome the barriers that have historically relegated ultra-low voltage operation to niche markets. In particular, this dissertation explores the performance barrier that prevents the widespread adoption of NTC and provides architectures for single-core, multi-core, many-core, and digital signal processing systems. As a final proof of concept a 3D integrated prototype of 128 ARM Cortex-M3 cores and 256MB of DRAM is presented that shows a 6.4X improvement in energy-efficiency over the Intel Atom processor.

### **CHAPTER 1**

## Introduction

Over the past four decades, the number of transistors on a chip has increased exponentially in accordance with Moore's law [63]. Moore's seemingly innocuous observation made in 1965, characterized in precise technical terms by Dennard [24] in 1974, has continued to hold until the present day. This has fueled the computing growth that we have come to expect—improved performance, increased density, and reduced energy per device. The ramifications have been widespread for all segments of society, improving health care, education, security, communications, etc. Indeed devices almost unimaginable a generation ago are common place in todays society, such as cell phones, navigation systems, and cloud computing. If Moore's law continues to hold we can expect further exciting developments for all segments of society. For example it may enable handheld medical devices, such as diagnostic imaging devices, that presently are limited in use by their immense cost and size. Thus turning machines like ultrasound scanners into common day devices like the thermometer found in everyones medicine cabinet.

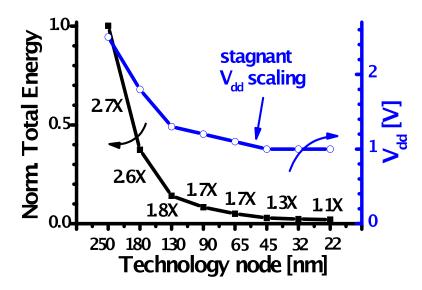

Todays current technology, complementary metal oxide semiconductors (CMOS), has continued to march in the direction of miniaturization per Moore's law [63]. New silicon-based technologies such as FinFET devices [37] and 3D integration [87] provide a path to increasing transistor counts in a given footprint. However, using device size as the metric of progress has become misleading since improvements in packing densities no longer translate into proportionate increases in performance or energy efficiency. Starting around the 65nm node, device scaling no longer delivers the energy gains that drove the semiconductor growth of the past several decades, as shown in Figure 1.1. The supply voltage has remained essentially constant since then and dynamic energy efficiency improvements have stagnated, while leakage currents continue to increase. Heat removal limits at the package level have further restricted more advanced integration. Together, such factors have created a curious design dilemma: more gates can now fit on a die, but a growing fraction cannot actually be used due to strict power limits.

Figure 1.1: Technology scaling trends of supply voltage and energy.

At the same time, we are moving to a "more than Moore" world, with a wider diversity of applications than the microprocessor or ASICs of ten years ago. Tomorrow's design paradigm must enable designs catering to application spanning from high-performance processors and portable wireless applications, to sensor nodes and medical implants. Energy considerations are vital over this entire spectrum, including:

- 1) High-performance computers, targeted for use in data centers. These create large amounts of heat and require major investments in power and cooling infrastructure, resulting in major environmental and societal impact. In 2006 data centers consumed 1.5% of total US electricity, equal to the entire US transportation manufacturing industry [68], and alarmingly, data center power is projected to double every  $\sim$ 5 years. These systems are the backbone of cloud computing.

- 2) Personal computers are becoming increasingly wireless and miniaturized, and are limited by tradeoffs between battery lifetimes (days) and computational requirements (e.g., high-definition video). Wireless applications increasingly rely on digital signal processing. While Moore's law enables greater transistor density, only a fraction may be used at a time due to power limitations and application performance is therefore muzzled by power limits, often in the 500mW-5W range.

- 3) Sensor-based computer systems critically depend on ultra-low power ( $\leq \mu$ W in standby) and reduced form-factor (mm<sup>3</sup>). These promise to unlock new semiconductor applications, such as implanted monitoring and actuation of medical devices, as well as ubiquitous environmental monitoring, e.g., structural sensing within critical infrastructure elements such as bridges.

The aim of the designer in this era is to overcome the challenge of energy efficient computing and unleash performance from the reins of power to re-enable Moores law in the semiconductor industry. The proposed strategy is to provide 10 times (10X) or more improvements in energy efficiency at constant performance through widespread application of near-threshold computing (NTC), where devices are operated at or near their threshold voltage ( $V_{th}$ ). By reducing supply voltage ( $V_{dd}$ ) from a nominal 1.1V to 400-500mV, NTC obtains as much as 10X energy efficiency gains and represents the re-establishment of voltage scaling and its associated energy efficiency gains.

The use of ultra-low voltage operation, and in particular subthreshold operation ( $V_{dd}$  <  $V_{th}$ ), was first proposed over three decades ago when the theoretical lower limit of  $V_{dd}$  was found to be 36mV [84]. However, the challenges that arise from operating in this regime have kept subthreshold operation confined to a handful of minor markets, such as wristwatches and hearing aids. To the mainstream designer, ultra-low voltage design has remained little more than a fascinating concept with no practical relevance. However, given the current energy crisis in the semiconductor industry and stagnated voltage scaling some foresee the need for a radical paradigm shift where ultra-low voltage operation is applied across application platforms and forms the basis for renewed energy efficiency.

NTC does not come without some barriers to widespread acceptance. In this dissertation three key challenges are identified that have been poorly addressed to date with respect to low voltage operation, specifically: 1) 10X or greater loss in performance, 2) 5X increase in performance variation, and 3) 5 orders of magnitude increase in functional failure rate of memory as well as increased logic failures. Overcoming these barriers is a formidable challenge requiring a synergistic approach combining methods from the algorithm and architecture levels to circuit and technology levels. Chapter 2 presents a top level view of these barriers and current research being conducted to overcome them. The next chapter, Chapter 3, presents a cache architecture that uses NTC to lower the power of single core systems where area is a major constraint. The remaining chapters will pick up the main theme of "Overcoming Performance Loss", which is the primary focus of this dissertation.

Solving the performance loss associated with NTC is critical in order to meet the stringent demands of the broad range of future applications, from tiny sensors to warehouse scale servers (such as Google and Facebook). There are a variety of code and architectures for this broad application space. For many, the use of parallelism—splitting the code up onto multiple cores—can be accompanied with running each core slower to consume less total power. The result can be used to improve the performance of the system while still retaining the energy gains of NTC operation. In Chapter 4 this dissertation explores the use of parallelism in multi-core processors for small scale systems, targeting handheld, laptop,

and desktop computing. In such systems NTC operation creates different optimal operating points for logic and memory devices, as such, NTC offers a unique design tradeoff where several cores can be clustered together to connect to a single cache, reducing power. In Chapter 5, this work is expanded to cover digital signal processing (DSP) chips, where there are unique architectural constraints due to the highly parallel replication of logic, and more stringent memory constraints.

While parallelism can help overcome performance bottlenecks, not every piece of code or architectural design space allows for parallelism. For example, in small sensor processors, where form factor is essential, replicating a design requires to much overhead. Even for systems that can exploit parallelism, inherently sequential pieces of code/work can still form bottlenecks to scalability. To address this, in Chapter 6 the work on multi-core and many-core architectures is augmented by the use of voltage boosting—increasing the voltage for short periods of time to overcome serial bottlenecks in parallel applications.

Finally, Chapter 7 expands the multi-core research into systems with 100's of cores, currently referred to as many-core architectures. In particular the design of a 3D integrated chip—one where multiple silicon wafers are stacked together and connected with tiny through-silicon-via's—is explored. This type of 3D design provides an interesting synergy with NTC, particularly because the energy-efficiency of NTC designs reduces the thermal management constraints associated with large 3D stacks of silicon. In this Chapter a prototype design, Centip3De, is developed for fabrication and the energy savings of the design are analyzed. The Centip3De system connects 128 ARM Cortex-M3 processors and 256 MB of DRAM in a 7-layer 3D stack, and was sent for fabrication in a 130nm process. This design achieves an energy efficiency improvement of 6.4X compared to an Intel Atom processor implemented in 45nm technology.

Ultimately this dissertation shows through detailed architectural simulation and chip design/fabrication that Near Threshold Computing is a viable way to extend the lifetime of Moore's law. By extending its life we will enable the continued growth in computational power that designers and users have come to expect.

### **CHAPTER 2**

# **Near Threshold Operation**

Power has become the primary design constraint for chip designers today. While Moores law continues to provide additional transistors, power budgets have begun to prohibit those devices from actually being used. To reduce energy consumption, voltage scaling techniques have proved a popular technique with subthreshold design representing the extreme endpoint of voltage scaling. Although it is extremely energy efficient, subthreshold design has been relegated to niche markets due to its major performance penalties. This chapter defines and explores Near Threshold Computing (NTC), a design space where the supply voltage is approximately equal to the threshold voltage of the transistors. This region retains much of the energy savings of subthreshold operation with more favorable performance and variability characteristics. This makes it applicable to a broad range of power-constrained computing segments from sensors to high performance servers.

NTC does not come without some barriers to widespread acceptance. In this chapter the focus is on three key challenges that have been poorly addressed to date with respect to low voltage operation, specifically: 1) 10X or greater loss in performance, 2) 5X increase in performance variation, and 3) 5 orders of magnitude increase in functional failure rate of memory as well as increased logic failures. Overcoming these barriers is a formidable challenge requiring a synergistic approach combining methods from the algorithm and architecture levels to circuit and technology levels. The focus of this dissertation is on overcoming the performance loss. Other research is also being conducted to cover the remaining two barriers, which will be discussed briefly in this chapter. Much of the Introduction and this chapter was conducted with the collaboration of my colleague Michael Wieckowski. This work appears as a part of a journal article in The Proceedings of the IEEE [25].

## 2.1 Defining Operating Regions

Energy consumption in modern CMOS circuits largely results from the charging and discharging of internal node capacitances and can be reduced quadratically by lowering supply voltage ( $V_{dd}$ ). As such, voltage scaling has become one of the more effective methods to reduce power consumption in commercial parts. It is well known that CMOS circuits function at very low voltages and remain functional even when  $V_{dd}$  drops below the threshold voltage ( $V_{th}$ ). In 1972, Meindl et al. derived a theoretical lower limit on  $V_{dd}$  for functional operation, which has been approached in very simple test circuits [84, 33]. Since this time, there has been interest in subthreshold operation, initially for analog circuits [92, 60, 61] and more recently for digital processors [81, 69, 48, 93, 16, 102], demonstrating operation at  $V_{dd}$  below 200mV. However, the lower bound on  $V_{dd}$  in commercial applications is typically set to 70% of the nominal  $V_{dd}$  due to concerns about robustness and performance loss [88, 44, 39].

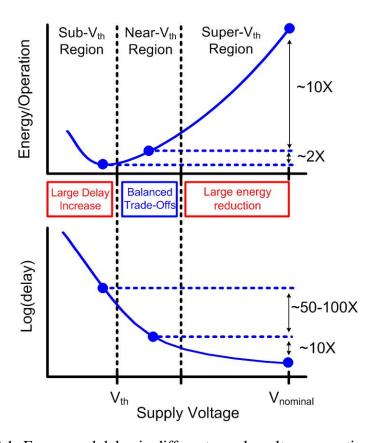

Figure 2.1: Energy and delay in different supply voltage operating regions.

Given such wide voltage scaling potential, it is important to determine the  $V_{dd}$  at which the energy per operation (or instruction) is optimal. In the superthreshold regime ( $V_{dd} > V_{th}$ ), energy is highly sensitive to  $V_{dd}$  due to the quadratic scaling of switching energy

with  $V_{dd}$ . Hence voltage scaling down to the near-threshold regime ( $V_{dd} \sim V_{th}$ ) yields an energy reduction on the order of 10X at the expense of approximately 10X performance degradation, as seen in Figure 2.1 [98]. However, the dependence of energy on  $V_{dd}$  becomes more complex as voltage is scaled below  $V_{th}$ . In subthreshold ( $V_{dd} < V_{th}$ ), circuit delay increases exponentially with  $V_{dd}$ , causing leakage energy (the product of leakage current,  $V_{dd}$ , and delay) to increase in a near-exponential fashion. This rise in leakage energy eventually dominates any reduction in switching energy, creating an energy minimum seen in Figure 2.1. The near threshold operating point is meant to be near the threshold voltage but the optimal location may vary depending on application and technology node.

The identification of an energy minimum led to interest in processors that operate at this energy optimal supply voltage [93, 102, 34] (referred to as  $V_{min}$  and typically 250mV-350mV). However, the energy minimum is relatively shallow. Energy typically reduces by only  $\sim$ 2X when  $V_{dd}$  is scaled from the near-threshold regime (400-500mV) to the subthreshold regime, though delay rises by 50-100X over the same region. While acceptable in ultra-low energy sensor-based systems, this delay penalty is not tolerable for a broader set of applications. Hence, although introduced roughly 30 years ago, ultra-low voltage design remains confined to a small set of markets with little or no impact on mainstream semiconductor products.

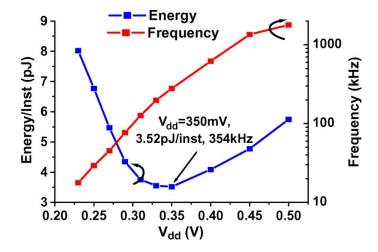

Figure 2.2: Subliminal processor frequency and energy breakdowns at various supply voltages.

## 2.2 NTC Analysis

Recent work at many leading institutions has produced working processors that operate at subthreshold voltages. For instance, the Subliminal [34] and Phoenix processors [80]

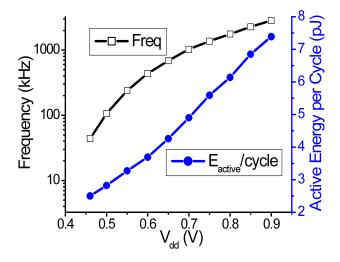

Figure 2.3: Phoenix frequency and energy breakdowns at various supply voltages.

designed by Hanson et al. provide the opportunity to experimentally quantify the NTC region and how it compares to the subthreshold region. Figure 2.2 and 2.3 present the energy breakdown of the two different designs as well as the clock frequency achieved across a range of voltages. As discussed in Section 2.1, there is a V<sub>min</sub> operating point that occurs in the subthreshold region where energy usage is optimized, but clock frequencies are limited to sub-1MHz values (not pictured for Phoenix as testing was not conducted in subthreshold). On the other hand, only a modest increase in energy is seen operating at the NTC region (around 0.5V), while frequency characteristics at that point are significantly improved. For example, at nominal voltages, the Subliminal processor runs at 20.5 MHz and 33.1 pJ/inst, while at NTC voltages, a 6.6X reduction in energy and an 11.4X reduction in frequency are observed. For the Phoenix processor a nominal 9.13 MHz and 29.6 pJ/inst translate to a 9.8X reduction in energy and a 9.1X reduction in frequency. These tradeoffs are much more attractive than those seen in the subthreshold design space and open up a wide variety of new applications for NTC systems.

## 2.3 NTC in Different Computing Segments

#### 2.3.1 NTC Integration in Ultra Energy-Efficient Servers

The exponential growth of the web has yielded a dramatic increase in the demand for server style computers with the installed base of servers expected to exceed 40 million by 2010 [40]. Server growth is accompanied by an equally rapid growth in the energy demand to power them. For example, it is estimated that the five largest internet sites consume at least 5MW each [47].

The tier 1 of a data center that serves web pages provides a perfect opportunity for NTC. The requests in these servers represent the bulk of requests to these data centers [82], consuming 75% of the overall energy. The workload is a stream of independent requests to render web pages that can be naturally executed in parallel. HTML is fetched from memory, subjected to relatively simple operations, and returned to memory without requiring extensive shared data. To achieve this, 10-100s of NTC cores on a single die can be used to obtain very high throughput with unprecedented energy efficiency.

### 2.3.2 NTC Integration in Personal Computing

The personal computing platform continues to evolve rapidly. WiFi is a standard on laptops but other mobile wireless communications are also starting to be supported. Future devices must be able to move seamlessly among communication alternatives. Such systems will combine a high level of processing power along with signal processing capabilities integrated into a much smaller form factor than todays laptops. Battery life is expected on the order of days, while functionality requirements are extreme and may include high-definition video, voice recognition, along with a range of wireless standards. The features of PC platforms that distinguish them from the two other systems are the dual needs to cope with variable workloads and energy efficient wireless communication.

In the PC platform space, cores may run at widely varying performance/energy points. The voltage and frequency of the cores and their supporting peripherals can be dynamically altered in real time to meet the constraints of performance and power consumption. This dynamic voltage and frequency scaling technique (DVFS) can be leveraged to enable adaptive NTC circuits in the personal computing space [71]. The scaling method may be driven by operating system commands and/or distributed sensors. Exploiting phase variations in workloads [11], efficient phase detection techniques need to be established for multicore multithreaded processors to enable power management schemes in achieving savings without significantly compromising performance.

#### 2.3.3 NTC Integration in Sensor Networks

With advances in circuit and sensor design, pervasive sensor-based systems, from single to thousands of nodes, are quickly becoming a possibility. A single sensor node typically consists of a data processing and storage unit, off-chip communication, sensing elements, and a power source. They are often wirelessly networked and have potential applications in a wide range of industrial domains, from building automation to homeland security to biomedical implants. The versatility of a sensor is directly linked to its form factor—for a

sensor to be truly useful in many new application areas, a form factor on the order of 1mm<sup>3</sup> is desirable while maintaining a lifetime of months or years.

To meet the above requirements, the key limiting constraint is energy. Both sensors and electronics are readily shrunk to  $<1 \text{mm}^3$  in modern technologies. However, current processors and communication systems require batteries that are many orders of magnitude larger than the electronics themselves (e.g.,  $50 \text{mm}^3$  processor die in a laptop vs.  $167 \text{cm}^3$  4-cell lithium-ion battery). Hence, whether a sensor node is powered through batteries, harvesting, or both, power consumption will limit overall system size. To integrate a sensor node in  $<1 \text{mm}^3$ , energy levels must be reduced by 4-7 orders of magnitude. Processing speed is not a major constraint in most sensor applications [67], easing the integration of NTC. Initial investigations showed simple sensor architectures coupled with NTC can obtain an active energy reduction of  $\ge 100 \text{X}$  [102].

### 2.4 NTC Barriers

Although NTC provides excellent energy-frequency tradeoffs, it brings its own set of complications. NTC faces three key barriers that must be overcome for widespread use; performance loss, performance variation, and functional failure. The following subsections discuss why each of these issues arises and why they pose problems to the widespread adoption of NTC. Section 2.5 then addresses the recent work related to each of these barriers. The focus of this dissertation will be on overcoming the performance loss, although brief discussions of the other barriers is addressed for completeness.

#### 2.4.1 Performance Loss

The performance loss observed in NTC, while not as severe as that in subthreshold operation, poses one of the most formidable challenges for NTC viability. In an industrial 45nm technology the fanout-of-four inverter delay (FO4, a commonly used metric for the intrinsic speed of a semiconductor process technology) at an NTC supply of 400mV is 10X slower than at the nominal 1.1V. There have been several recent advances in architectural and circuit techniques that can regain some of this loss in performance. These techniques, described in detail in Section 2.5.1, center around aggressive parallelism with a novel NTC oriented memory/computation hierarchy. The increased communication needs in these architectures is supported by the application of 3D chip integration, as made feasible by the low power density of NTC circuits. In addition, new technology optimizations that opportunistically leverage the significantly improved silicon wearout characteristics (e.g., oxide

breakdown) observed in low voltage NTC can be used to regain a substantial portion of the lost performance.

Figure 2.4: Impact of voltage scaling on gate delay variation.

#### 2.4.2 Increased Performance Variation

In the near-threshold regime, the dependencies of MOSFET drive current on  $V_{th}$ ,  $V_{dd}$ , and temperature approach exponential. As a result, NTC designs display a dramatic increase in performance uncertainty. Figure 2.4 shows that performance variation due to global process variation alone increases by approximately 5X from  $\sim$ 30% (1.3X) [13] at nominal operating voltage to as much as 400%, (5X) at 400mV. Operating at this voltage also heightens sensitivity to temperature and supply ripple, each of which can add another factor of 2X to the performance variation resulting in a total performance uncertainty of 20X. Compared to a total performance uncertainty of  $\sim$ 1.5X at nominal voltage, the increased performance uncertainty of NTC circuits looms as a daunting challenge that has caused most designers to pass over low voltage design entirely. Simply adding margin so that all chips will meet the needed performance specification in the worst-case is effective in nominal voltage design. In NTC design this approach results in some chips running at

1/10th their potential performance, which is wasteful both in performance and in energy due to leakage currents. Section 2.5.2 presents a new architectural approach to dynamically adapt the performance of a design to the intrinsic and environmental conditions of process, voltage, and temperature that is capable of tracking over the wide performance range observed in NTC operation. This method is complemented by circuit-level techniques for diminishing the variation of NTC circuits and for efficient adaptation of performance.

#### 2.4.3 Increased Functional Failure

The increased sensitivity of NTC circuits to variations in process, temperature and voltage not only impacts performance but also circuit functionality. In particular, the mismatch in device strength due to local process variations from such phenomena as random dopant fluctuations (RDF) and line edge roughness (LER) can compromise state holding elements based on positive feedback loops. Mismatch in the loops elements will cause it to develop a natural inclination for one state over the other, a characteristic that can lead to hard functional failure or soft timing failure. This issue has been most pronounced in SRAM where high yield requirements and the use of aggressively sized devices result in prohibitive sensitivity to local variation.

Figure 2.5: Effects of global and local variation on a standard 6T SRAM cell. (a) Global  $V_{th}$  reduction resulting in timing failure. (b) Global  $V_{th}$  P-N skew resulting in write failure. (c) Local  $V_{th}$  mismatch resulting in read upset.

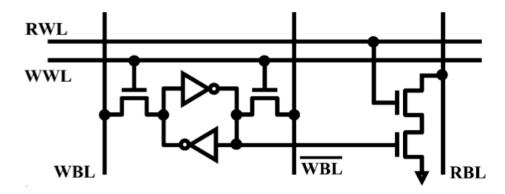

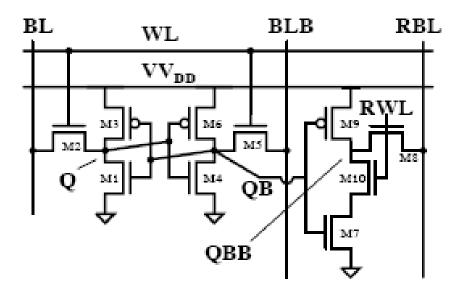

Several variation scenarios for a standard 6T SRAM cell are shown in Figure 2.5. In (a), global process variation has resulted in both P and N devices being weakened by a  $V_{th}$  increase resulting in a potential timing failure during both reads and writes. In (b), a similar global effect has introduced skew between the P and N device strengths. This is particularly detrimental when the P is skewed stronger relative to the N resulting in a potential inability to write data into the cell. In (c), random local mismatch is considered and the worst case is shown for a read upset condition. The cell is effectively skewed to favor one state over another, and the weak pull-down on the left side cannot properly combat the strong access device at its drain. As such, the Data node is likely to flip to the

"1" state during normal read operations. While these examples are shown in isolation, a fabricated circuit will certainly experience all of them simultaneously to varying degrees across a die and with different sensitivities to changes in supply voltage and temperature. The resulting likelihood of failure is potentially very high, especially as supply voltage is reduced and feature sizes are shrunk.

Figure 2.6: Impact of voltage scaling on SRAM failure rates.

For instance, a typical 65nm SRAM cell has a failure probability of  $\sim 10^{-7}$  at nominal voltage, as shown in Figure 2.6. This low failure rate allows failing cells to be corrected for using parity checks or even swapped using redundant columns after fabrication. However, at an NTC voltage of 500mV, this failure rate increases by  $\sim 5$  orders of magnitude to approximately 4%. In this case, nearly every row and column will have at least one failing cell, and possibly multiple failures, rendering simple redundancy methods completely ineffective. Section 2.5.3 therefore presents novel approaches to robustness ranging from the architectural to circuit levels that address both memory failures and functional failure of flip-flops (FFs) and latches.

# 2.5 Addressing NTC Barriers

The following subsections will address some of the research being done to overcome each of the barriers presented in Section 2.4.

#### 2.5.1 Addressing Performance Loss

Performance loss, as discussed in Section 2.4.1, can significantly hinder the adoption of NTC. The main focus of this dissertation is architectural techniques to overcome performance loss. The rest of the dissertation will present the parallel architectures to address this bottleneck, in addition to techniques for systems that can not employ parallelism because of either area or algorithmic concerns. These architectures span single-, multi-, and many-core architectures and include techniques for DSP and voltage boosting for serial bottlenecks.

#### 2.5.2 Addressing Performance Variation

As noted in Section 2.4.2, the combined impact of intrinsic process variations and extrinsic variations, such as fluctuations in temperature and supply voltage, results in a spread in the statistical distribution of NTC circuit performance of  $\sim 10 \mathrm{X}$  compared to designs at nominal supplies. Traditional methods to cope with this issue, which are largely centered on adding design margin, are inadequate and hugely wasteful when voltage is scaled, resulting in a substantial portion of the energy efficiency gain from NTC operation being lost. Hence, in this section architectural and circuit solutions to provide variation tolerance and adaptivity are discussed.

#### 2.5.2.1 Soft Edge Clocking

The device variation inherent to semiconductor manufacturing continues to increase from such causes as dopant fluctuation and other random sources, limiting the performance and yield of ASIC designs. Traditionally, variation tolerant, two-phase, latch-based designs have been used as a solution to this issue. Alternatively, hard-edge data flip-flops (DFF) with intentional or useful skew can be used. Both of these techniques incur a significant penalty in design complexity and clocking overhead.

One potential solution to address timing variation while minimizing overhead is a type of soft-edge flip-flop (SFF) that maintains synchronization at a clock edge, but has a small transparency window, or softness. In one particular approach to soft-edge clocking, tunable inverters are used in a master-slave flip-flop to delay the incoming master clock edge with respect to the slave edge as shown in Figure 2.7.

As a result of this delay, a small window of transparency is generated in the edgetriggered register that accommodates paths in the preceding logic that were too slow for the nominal cycle time—in essence allowing time borrowing within an edge-triggered register environment. Hence, soft edge clocking results in a trade-off between short and long

Figure 2.7: Delaying the master clock creates a window of transparency.

Figure 2.8: FIR filter with soft edge clocking compared to standard flip-flops (SFF); presented with and without useful skew.

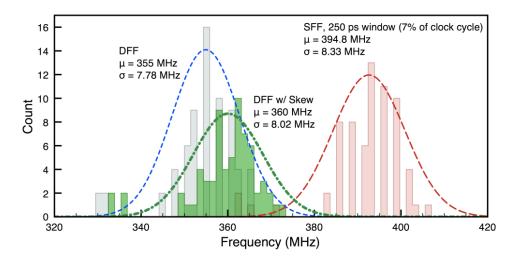

paths and is effective at mitigating random, uncorrelated variations in delay, which are significant in NTC. In theoretical explorations at a nominal super-threshold supply voltage, it was shown that soft-edge clocking reduced the mean (standard deviation) clock period in benchmark circuits by up to 22% (25%). Joshi et al. [46] furthered this work by developing a library based on these soft flip-flops and providing a statistical algorithm for their assignment. In the work by Wieckowski et al. [95], this technique was employed in silicon to show that small amounts of softness in a FIR filter achieved improvements in performance of 11.7% over a standard DFF design and improvement of 9.2% compared to a DFF with useful skew. These increases in performance, shown in Figure 2.8, demonstrate a greater tolerance to intra-die variation that becomes even more important in the NTC operating region.

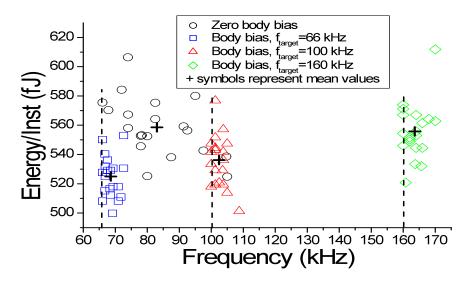

#### 2.5.2.2 Body Biasing

At superthreshold supply voltages, body biasing (BB) is a well known technique for adapting performance and leakage to global variation of process, voltage, and temperature. Its use is becoming more widespread and was recently demonstrated in silicon within a communication processor application [30]. While effective in the superthreshold domain, the influence of body-biasing becomes particularly effectual in the NTC domain where device sensitivity to the threshold voltage increases exponentially. Body-biasing is therefore a strong lever for modulating the frequency and performance in NTC, and is ideally suited as a technique for addressing the increased detriments of process variation in NTC. Further, because P and N regions can be adapted separately using body biasing, and because the relative drive strength of P and N transistors can change dramatically from superthreshold to NTC, body biasing has the added advantage of allowing the P to N ratio of a design to be optimally adjusted.