## **Trap-driven Memory Simulation**

by

**Richard Albert Uhlig**

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 1995

Doctoral Committee:

Professor Trevor Mudge, Chair Associate Professor Richard Brown Assistant Professor Peter Chen Assistant Professor Stuart Sechrest Peter Bird, Computer Architect, ACRI, Lyon, France Associate Research Scientist Peter Honeyman

Diese Doktorarbeit ist ohne Dreckfehler

© <u>Richard Albert Uhlig</u>

All Rights Reserved

1995

# Dedication

To my parents, Albert and Trudy Uhlig

## Acknowledgments

My parents created me. As my father has often said, they had fun doing it.

Peter Bird encouraged me to start along this path and taught me strategies for finishing before I even started. He saved me at least a year or two with his advice.

Trevor Mudge gave me all the resources and guidance that I needed without ever constraining the direction of this research. His sense of humor helped to break up the monotony.

Stuart Sechrest taught me most of what I know about operating systems. Of all the courses in graduate school, I enjoyed his the most.

Richard Brown, Peter Chen and Peter Honeyman rounded out my committee. I am grateful for their time and interest.

Tim Stanley ported Tapeworm to OSF/1, Chih-Chieh Lee ported Tapeworm to the 486, and Mike Smith of Harvard reviewed Chapter 2 on trace-driven simulation. Their help was much appreciated.

NSF paid for three years of my graduate education and (D)ARPA paid for the rest. This makes paying taxes a little easier.

All the students of Room 2001 and 3003, past and present, and too numerous to mention individually, provided the densest collection of bright people that I've ever been surrounded by. My conversations with Mike Upton, Tom Huff, Tim Stanley and Ajay Chandna were particularly enjoyable.

Hilary DeKraai offered emotional support and proofreading when it was most needed, especially during the final days. I look forward to our upcoming adventures.

I am most indebted to David Nagle. Every aspect of our research, from establishing the direction of study, to writing the initial proposals for funding, to carrying out the work and writing up the results has been a joint effort. Our partnership has taught me how powerful good collaboration can be. He is my dearest friend and I look forward to our continued partnership on future ventures.

# **Table of Contents**

| Dedicationii                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Acknowledgmentsiii                                                                                                                                                                                                                                                                                                                                                                                                               |

| Table of Contents iv                                                                                                                                                                                                                                                                                                                                                                                                             |

| List of Tables                                                                                                                                                                                                                                                                                                                                                                                                                   |

| List of Figuresx                                                                                                                                                                                                                                                                                                                                                                                                                 |

| List of Appendicesxii                                                                                                                                                                                                                                                                                                                                                                                                            |

| Chapter 1                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Introduction1                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Chapter 2                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Trace-driven Simulation9                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.1 Ideal Trace-driven Memory Simulation102.2 An Analysis of the State-of-the-art in Trace-driven Simulation132.2.1 Trace Collection13External Hardware Probes16Microcode Modification20Instruction-set Emulation22Code Instrumentation26Single-step Execution31Summary of Trace-collection Methods322.2.2 Trace Reduction332.2.3 Trace Processing392.2.4 Trace Interfaces43Files44Pipes44Same-task Communication452.3 Summary49 |

| Chapter 3                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Trap-driven Simulation                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.1 Beyond Trace-driven Simulation                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.1.1 Hit Bypassing                                  |    |

|------------------------------------------------------|----|

| 3.1.2 Customized Instrumentation                     | 53 |

| 3.1.3 Active Memory                                  | 54 |

| 3.1.4 Summary of New Memory Simulation Methods       | 54 |

| 3.1.5 Performance Bounds on Software-only Methods    | 55 |

| 3.2 Enter Trap-driven Simulation                     | 56 |

| 3.2.1 Trap-driven TLB Simulation                     | 56 |

| 3.2.2 Trap-driven Cache Simulation                   | 58 |

| 3.2.3 Open Questions about Trap-driven Simulation    | 59 |

| 3.3 Tapeworm II                                      | 59 |

| 3.3.1 Design Goals                                   | 60 |

| 3.3.2 Tapeworm Organization                          | 61 |

| System-independent Code                              |    |

| OS-dependent Code                                    | 63 |

| Hardware-dependent Code                              | 65 |

| 3.4 Chapter Summary                                  | 68 |

| Character 4                                          |    |

| Chapter 4                                            |    |

| Flexibility                                          |    |

|                                                      |    |

| 4.1 Simulation Range                                 |    |

| 4.1.1 Basic Cache Structures                         |    |

| Simulating Direct-mapped Caches                      |    |

| Simulating Different Cache Sizes and Line Sizes      |    |

| Simulating Set Associativity                         |    |

| Simulating Full Associativity                        |    |

| 4.1.2 Basic Caching Policies                         |    |

| Simulating Random Replacement                        |    |

| Simulating FIFO Replacement                          |    |

| Simulating LRU Replacement                           |    |

| Simulating NMRU Replacement                          |    |

|                                                      |    |

| Simulating a Write-back Write Policy                 |    |

| · ·                                                  |    |

| 4.1.3 Complex Memory Systems                         |    |

| Simulating Caches in Parallel                        |    |

| 4.1.4 Metrics                                        |    |

| Miss Ratios                                          |    |

| Traffic Ratios                                       |    |

| Misses per Instruction                               |    |

| Cycles per Instruction                               |    |

| 4.2 Adapting Methods of Trace-driven Simulation      |    |

| 4.2.1 Set Sampling                                   |    |

| 4.2.1 Set Samping                                    |    |

| 4.2.3 Multi-configuration Simulation                 |    |

| A Basic Stack Algorithm                              |    |

| A Trace-driven Implementation of the Stack Algorithm |    |

| A Trap-driven Implementation of the Stack Algorithm  |    |

| Other Multi-configuration Algorithms                 |    |

|                                                      |    |

| 4.2.4 Real-time Filtered Trace Generation                                     | 109 |

|-------------------------------------------------------------------------------|-----|

| 4.4 Flexibility Summary                                                       |     |

| Portability                                                                   |     |

| 5.1 Porting to Existing Hardware                                              | 114 |

| 5.1.1 Implementing Access Control                                             |     |

| TLB Miss Redirection                                                          |     |

| Page Table Shadowing                                                          |     |

| Instruction Shadowing                                                         |     |

| Instruction Recoding                                                          |     |

| Tagged Memory Trap Redirection                                                |     |

| Memory Parity Recoding                                                        |     |

| 5.1.2 Implementing Traps                                                      |     |

| 5.1.3 Implementing Event Counting                                             |     |

| 5.1.4 Summary of General Implementation Methods                               |     |

| 5.2 Portability and Tapeworm II                                               |     |

| 5.2.1 Implementation of Access Control                                        |     |

| 5.2.2 Implementation of Traps5.2.3 Implementation of Event Counts             |     |

| 5.2.4 Summary of Tapeworm II Portability                                      |     |

| 5.3 Trap-driven Simulation on Next-generation Hardware                        |     |

| 5.3.1 Support for Access Control                                              |     |

| Memory Management Unit Modifications                                          |     |

| Memory Access Tags                                                            |     |

| Trap on Cache Miss                                                            |     |

| 5.3.2 Support for Traps                                                       |     |

| 5.3.3 Support for Event Counting                                              |     |

| 5.4 Portability Summary                                                       | 128 |

| Chapter 6                                                                     |     |

| Speed                                                                         |     |

| 6.1 Trap-driven versus Trace-driven Simulation Speed                          |     |

| 6.2 Speed and Tapeworm II                                                     |     |

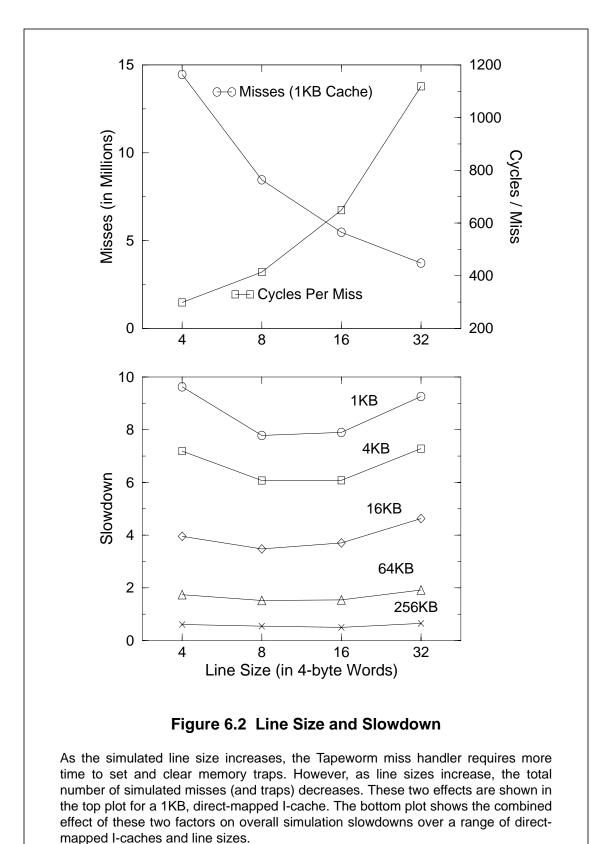

| 6.2.1 Line Size and Slowdown                                                  |     |

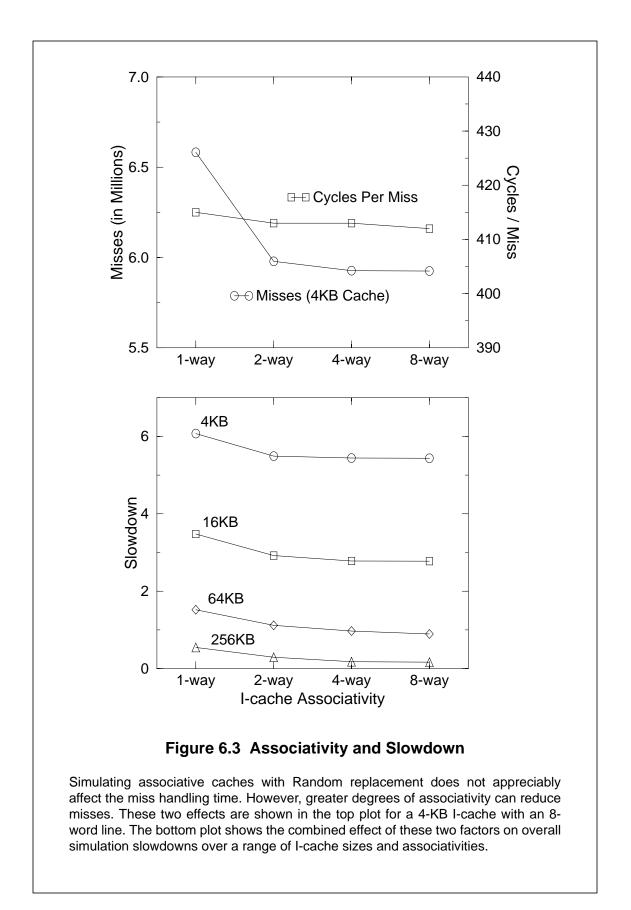

| 6.2.2 Associativity and Slowdown                                              |     |

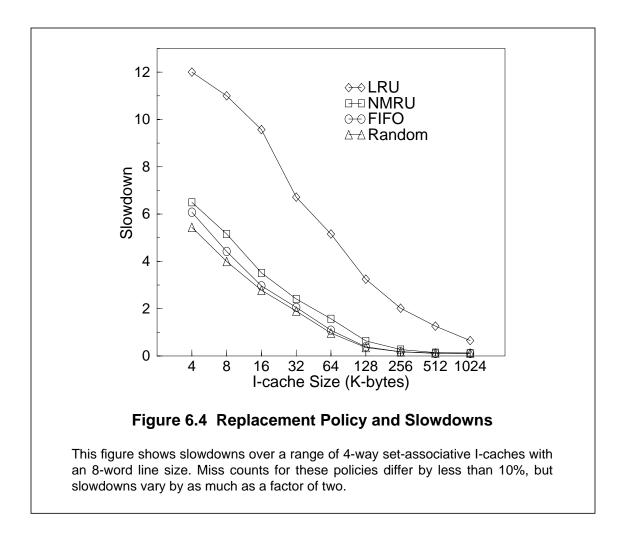

| 6.2.3 Replacement Policy and Slowdown6.2.4 Cache Indexing Policy and Slowdown |     |

| 6.2.5 Data-cache Simulation and Slowdown                                      |     |

| 6.2.6 TLB Simulation and Slowdown                                             |     |

| 6.2.7 Set Sampling and Slowdown                                               |     |

| 6.3 Speed Summary                                                             |     |

| Chapter 7                                                                     |     |

| Accuracy                                                                      | 1// |

| 7.1 Accuracy and Tapeworm II                                                  |     |

|                                                                               | 147 |

| 7.1.1 Sources of Measurement Variation    |     |

|-------------------------------------------|-----|

| Variation due to Set Sampling             |     |

| Variation due to Page Allocation          |     |

| Variation due to Memory Fragmentation     |     |

| Summary of Measurement Variation          |     |

| 7.1.2 Sources of Measurement Bias         |     |

| Bias due to Omitted Workload Components   |     |

| Bias due to Memory Dilation               |     |

| Bias due to Time Dilation                 |     |

| Bias due to Non-trapping Memory Locations |     |

| Summary of Measurement Bias               |     |

| 7.2 Accuracy Summary                      |     |

| Chapter 8                                 |     |

| Conclusions and Future Work               |     |

| 8.1 Future Work                           | 161 |

| 8.        | I Futu | re w    | ork  |     | • • • |       | • • • | • • • | • • • | • • • | • • • | • • • | • • • |     | • • • | •••     | <br>        | • • • • | 161 |

|-----------|--------|---------|------|-----|-------|-------|-------|-------|-------|-------|-------|-------|-------|-----|-------|---------|-------------|---------|-----|

| Appendi   | ces .  | • • • • | •••• | ••• | •••   | •••   | •••   | •••   | •••   | •••   | •••   | •••   | •••   | ••• | • • • | • • • • | <br>•••     | ••••    | 164 |

| Bibliogra | aphy . | • • • • | •••• | ••• | •••   | • • • | •••   | •••   | •••   | •••   | •••   | • • • | •••   | ••• | • • • | • • • • | <br>• • • • | • • • • | 169 |

# List of Tables

| Table 1.1 | The Effect of Operating Systems on CPU Stall Behavior     |

|-----------|-----------------------------------------------------------|

| Table 2.1 | Summary of Trace-collection Methods 15                    |

| Table 2.2 | Probe-based Trace Collectors                              |

| Table 2.3 | Trace Collection through Instruction-set Emulation        |

| Table 2.4 | Code-instrumentation Tools                                |

| Table 2.5 | Address Trace Reduction Methods 35                        |

| Table 2.6 | Multi-configuration Memory Simulators 40                  |

| Table 2.7 | Some Trace Interfacing Methods                            |

| Table 2.8 | Overall Trace-driven Simulation Times                     |

| Table 3.1 | Beyond Traces: Some Recent Fast Simulators                |

| Table 3.2 | Trap-driven Simulators 57                                 |

| Table 3.3 | Tapeworm Code Distribution    61                          |

| Table 3.4 | OS-dependent Tapeworm Routines                            |

| Table 3.5 | Hardware-dependent Tapeworm Primitives                    |

| Table 4.1 | Simulation Range: Cache Structures, Policies, and Metrics |

| Table 5.1 | Methods for Implementing Access-control Primitives        |

| Table 5.2 | Privileged Operations on Modern Microprocessors 120       |

| Table 5.3 | Suggested Hardware Support for Trap-driven Primitives     |

| Table 6.1 | Tapeworm Miss Handling Time    133                        |

| Table 7.1 | Workload Summary                                          |

| Table 7.2 | Variation in Measured Memory System Performance           |

| Table 7.3 | Measurement Variation Removed                             |

Table 7.4Miss Contributions of Different Workload Components156

# List of Figures

| Figure 1.1  | The MPEG Decoder Workload                                                 |

|-------------|---------------------------------------------------------------------------|

| Figure 1.2  | Trace-driven and Trap-driven Simulation Algorithms                        |

| Figure 2.1  | The Three Steps of Trace-driven Simulation                                |

| Figure 2.2  | Levels of System Abstraction and Trace Collection Methods 14              |

| Figure 2.3  | The Components of Trace-driven Slowdowns                                  |

| Figure 3.1  | The MPEG Decoder Workload                                                 |

| Figure 3.2  | The Tapeworm Simulation System                                            |

| Figure 3.3  | Basic Tapeworm Simulation Parameters                                      |

| Figure 3.4  | Tapeworm and the Host VM System    66                                     |

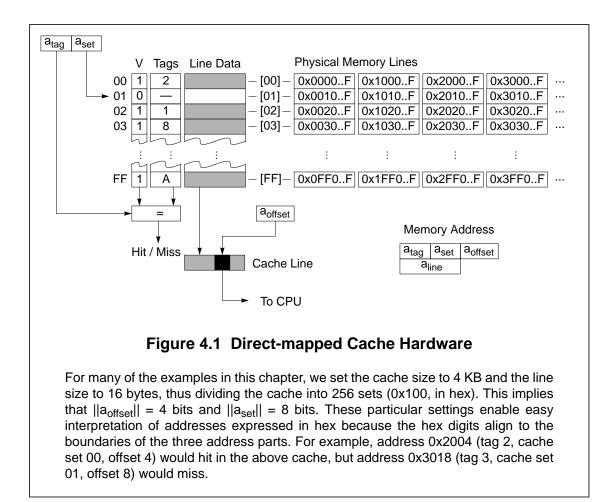

| Figure 4.1  | Direct-mapped Cache Hardware                                              |

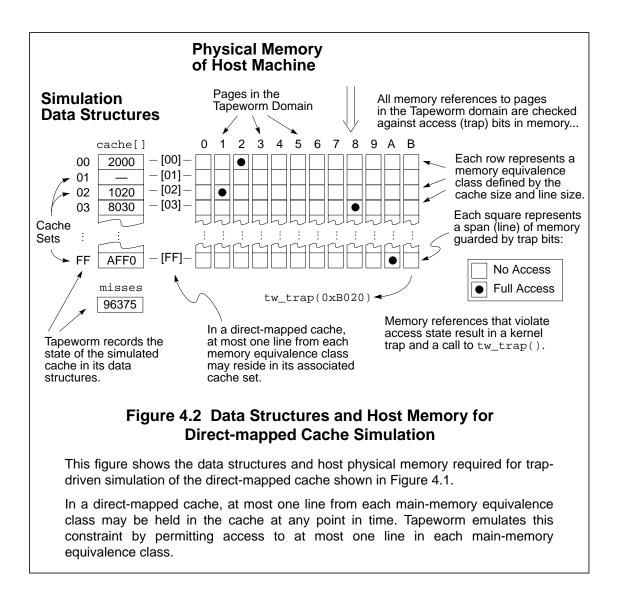

| Figure 4.2  | Data Structures and Host Memory for Direct-mapped Cache Simulation 75     |

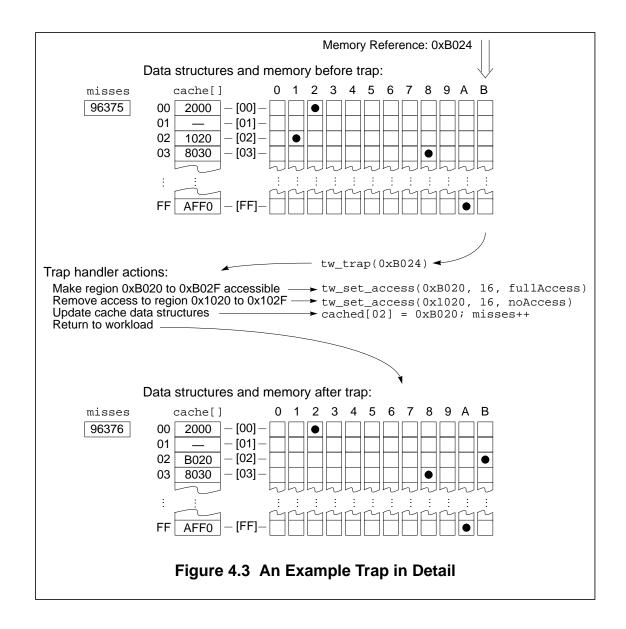

| Figure 4.3  | An Example Trap in Detail                                                 |

| Figure 4.4  | A Trap Handler for Direct-mapped Cache Simulation                         |

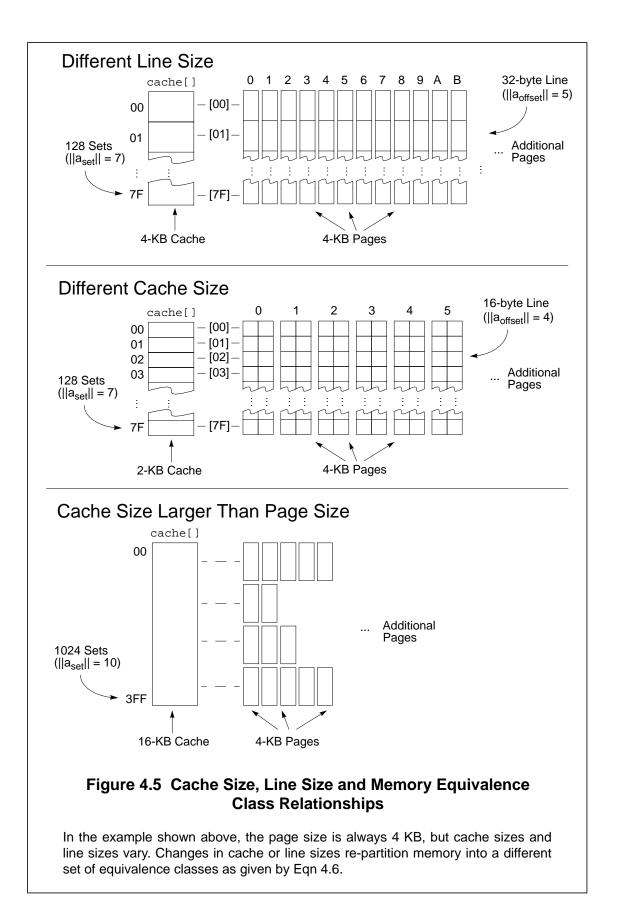

| Figure 4.5  | Cache Size, Line Size and Memory Equivalence Class Relationships 80       |

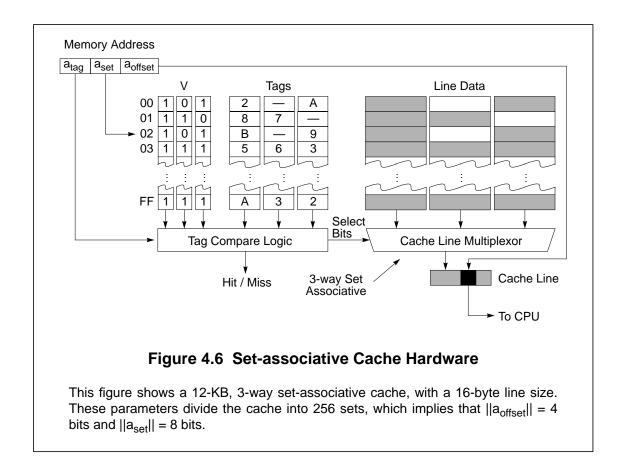

| Figure 4.6  | Set-associative Cache Hardware                                            |

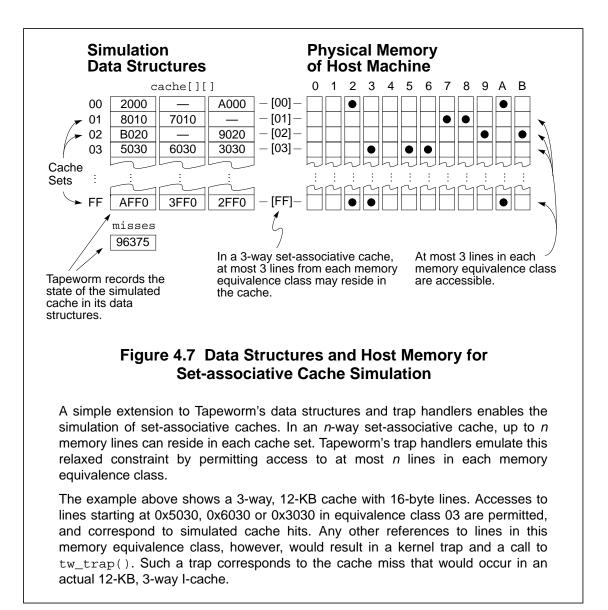

| Figure 4.7  | Data Structures and Host Memory for Set-associative Cache Simulation 83   |

| Figure 4.8  | A Trap Handler for Set-Associative Cache Simulation                       |

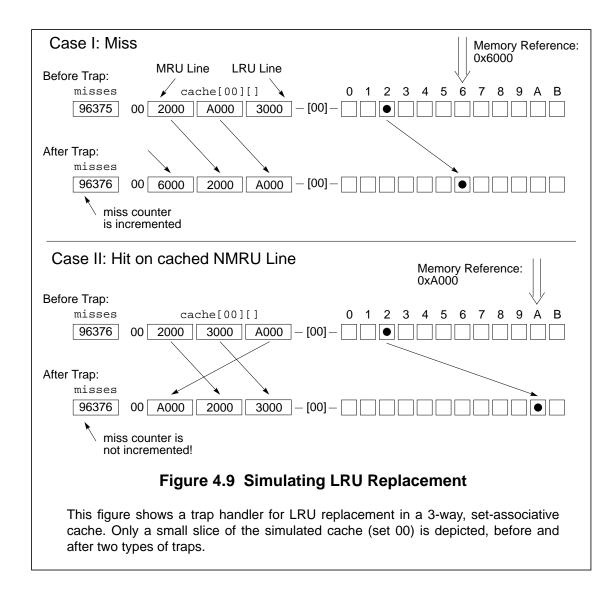

| Figure 4.9  | Simulating LRU Replacement                                                |

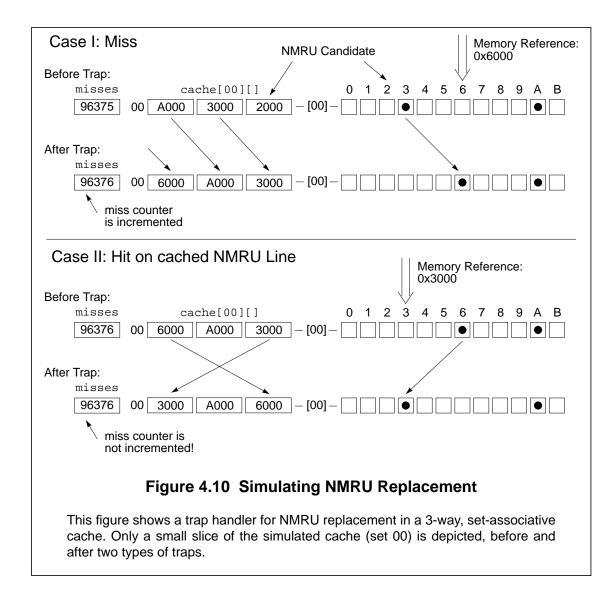

| Figure 4.10 | Simulating NMRU Replacement                                               |

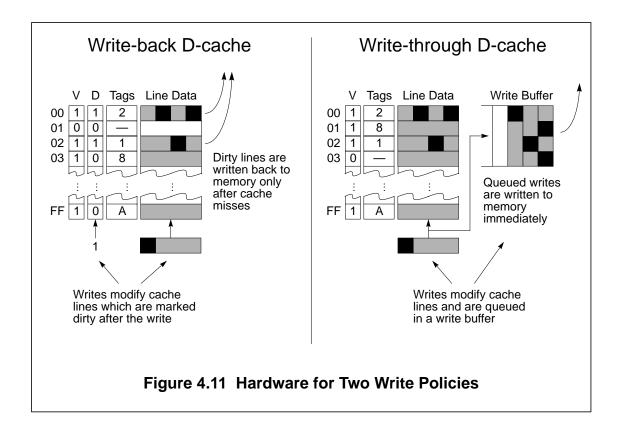

| Figure 4.11 | Hardware for Two Write Policies                                           |

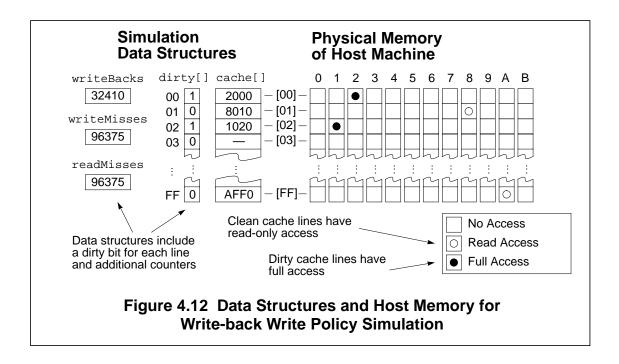

| Figure 4.12 | Data Structures and Host Memory for Write-back Write Policy Simulation 93 |

| Figure 4.13 | A Trap Handler for Write-back Write Policy Simulation                     |

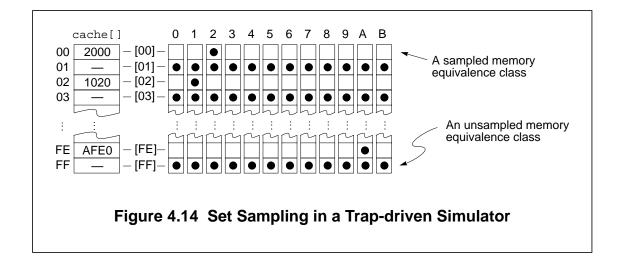

| Figure 4.14 | Set Sampling in a Trap-driven Simulator 103                          |

|-------------|----------------------------------------------------------------------|

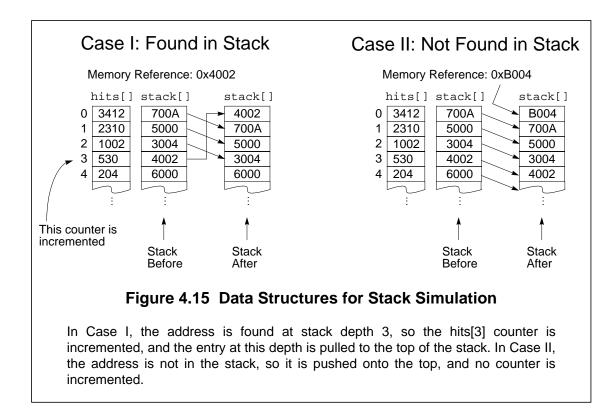

| Figure 4.15 | Data Structures for Stack Simulation 105                             |

| Figure 4.16 | A Trace-driven Implementation of the Stack Algorithm 106             |

| Figure 4.17 | A Trap-driven Implementation of the Stack Algorithm 107              |

| Figure 4.18 | Some Tapeworm Cache and TLB Simulation Parameters 110                |

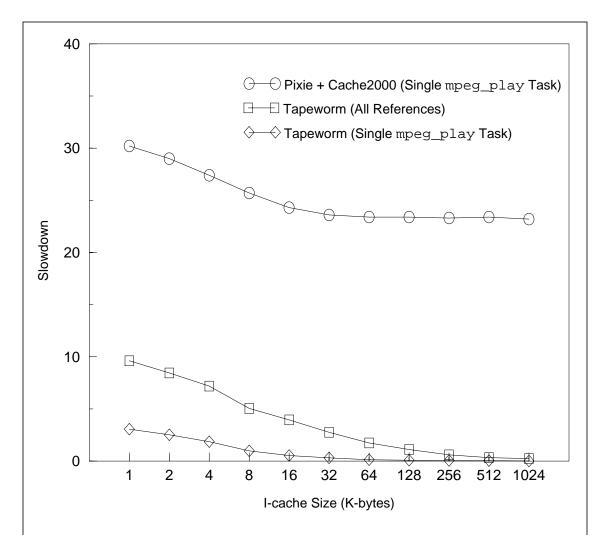

| Figure 6.1  | Comparison of Trace-driven and Tapeworm Slowdowns 132                |

| Figure 6.2  | Line Size and Slowdown 135                                           |

| Figure 6.3  | Associativity and Slowdown                                           |

| Figure 6.4  | Replacement Policy and Slowdowns 138                                 |

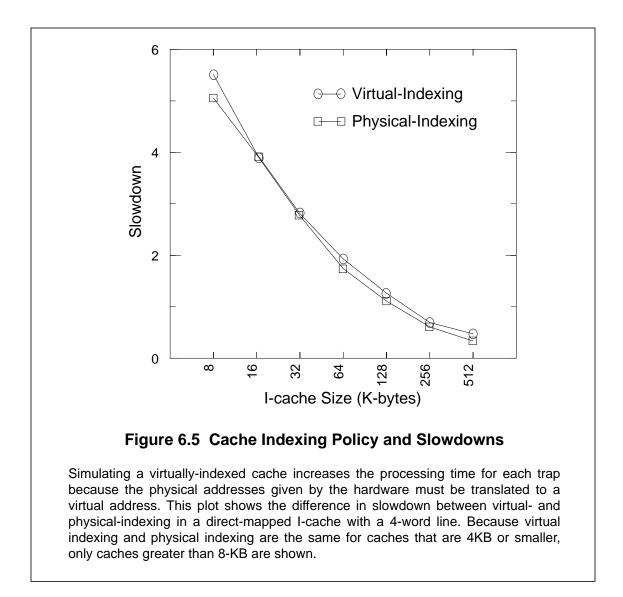

| Figure 6.5  | Cache Indexing Policy and Slowdowns 140                              |

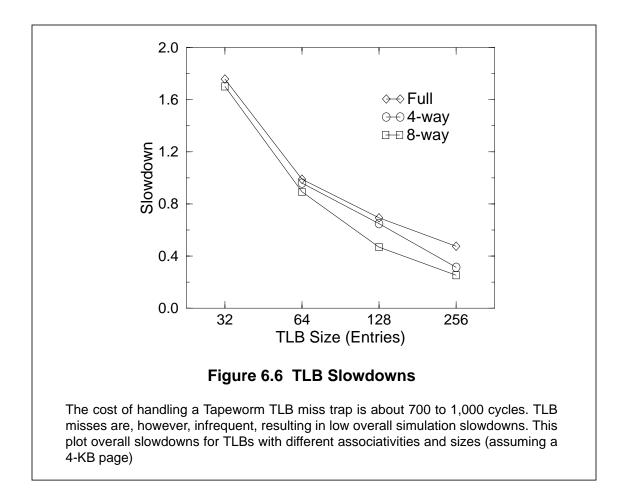

| Figure 6.6  | TLB Slowdowns 141                                                    |

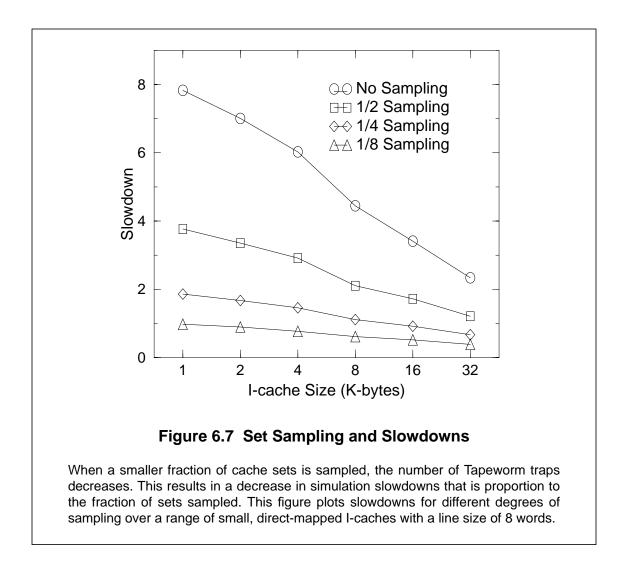

| Figure 6.7  | Set Sampling and Slowdowns 142                                       |

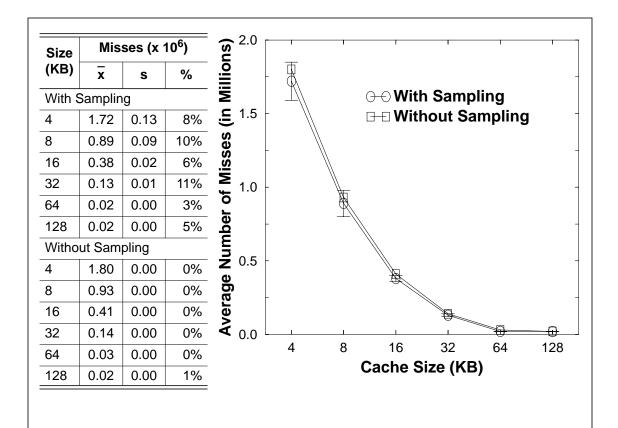

| Figure 7.1  | Variation due to Set Sampling 148                                    |

| Figure 7.2  | Variation Due to Page Allocation                                     |

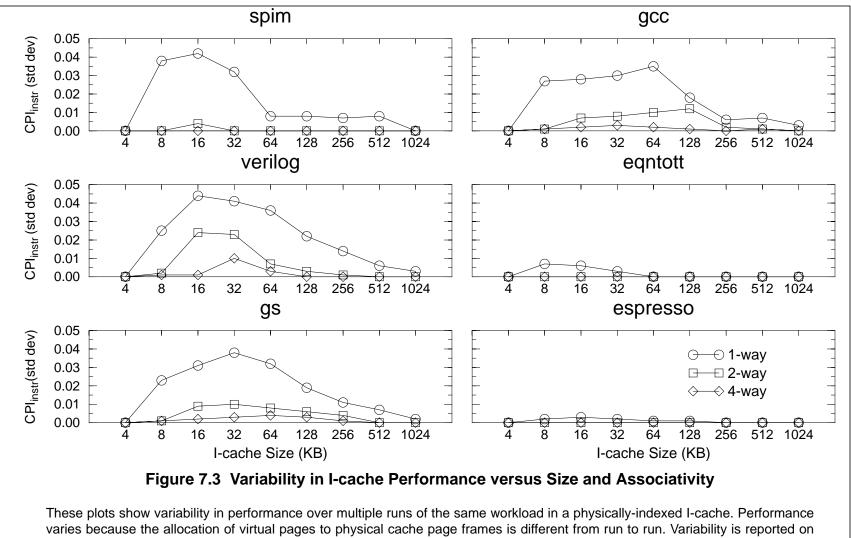

| Figure 7.3  | Variability in I-cache Performance versus Size and Associativity 150 |

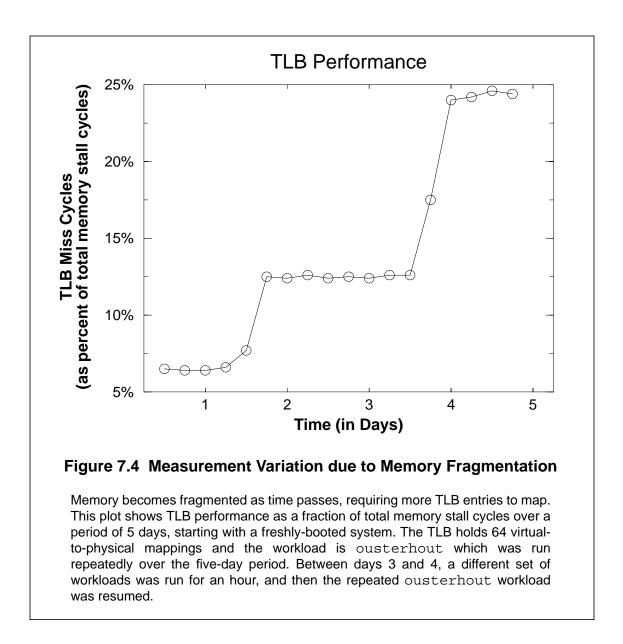

| Figure 7.4  | Measurement Variation due to Memory Fragmentation                    |

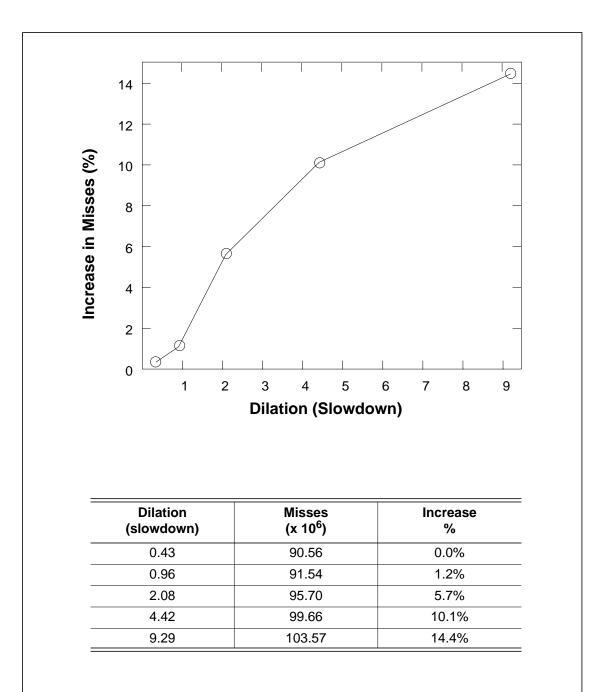

| Figure 7.5  | Error Due to Time Dilation                                           |

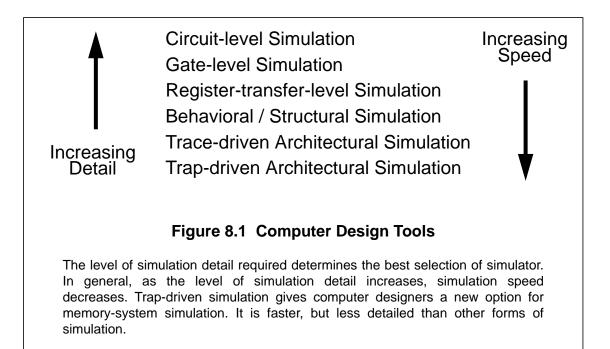

| Figure 8.1  | Computer Design Tools                                                |

# List of Appendices

| Appendix A | ISCA Paper Abstracts | 165 |

|------------|----------------------|-----|

|------------|----------------------|-----|

# Chapter 1 Introduction

Many researchers feel that uniprocessor cache design is a well-understood process that warrants no further investigation. While caches are among the most thoroughly-studied components of computer architectures, the current level of understanding has not helped industry to consistently produce microprocessors with balanced memory systems. A few recent examples support this point:

- The performance of the Macintosh 680x0 emulator running on a PowerPC 603 is roughly 60% that of the earlier PowerPC 601 running the same emulator at the same clock rate (80 MHz) [MacWeek94; MPReport94]. A more optimized version of the 680x0 emulator that is twice as fast on the 601 delivers only a 5% improvement on the 603. These performance problems have been attributed to the 603 cache structure, which implements split, 2-way, 8-KB instruction and data caches, compared with the unified, 8-way, 32-KB cache of the 601. The disappointing performance of the 603 has delayed the introduction of PowerPC-based Apple Powerbooks, which are awaiting a re-design of the chip, called the 603+, with larger on-chip caches.

- Disappointing performance of Windows NT on the MIPS R4000 processor led to a redesign of the memory system in its successor chip, the R4200. The new design doubles the size of the direct-mapped instruction cache to 16KB, but leaves the direct-mapped data cache at 8KB. Fortunately, simulations prevented designers from making the mistake of allocating die area to the data cache, rather than the instruction cache. The reverse configuration (8-KB I-cache, 16-KB D-cache) yields 7% less performance under Windows NT [MPReport93].

- Although the peak cycles per instruction (CPI) of the first-generation DEC Alpha chip (21064) is 0.5, hardware-monitor measurements reveal that the actual CPI of the chip

is typically in the range of 2 to 3 on the SPEC92 benchmarks and over 4 on the data transaction processing TPC benchmarks [Cventanovic94]. This 200-MHz chip implements relatively meager, direct-mapped, 8-KB, primary instruction and data caches, resulting in memory stalls that account for more than 60% to 70% of lost performance. Later versions of the Alpha architecture (e.g., the 21164) have implemented much more substantial on-chip caches, enabling the processor to come closer to its potential peak performance.

The belief that cache design is a solved problem is not consistent with the reality that several recent microprocessors exhibit memory-system problems that either prevent them from achieving the true potential of their high clock rates, or that require costly chip redesigns to reach their performance goals.

If caches are so well understood, why do memory-system problems persist? One reason is that hardware technologies are constantly changing, upsetting previous system designs that achieved a balance between the processor and the memory system. In particular, memories are generally getting larger and cheaper, but not faster [Touma92; Jouppi94]. At the same time, the move towards higher clock rates and multi-issue machines are making processors more memory hungry. In his dissertation, Upton shows that microprocessor clock rates have increased at a rate of 40% per year during the past decade, while DRAM speeds have only increased at a rate of 11% per year during the same period [Upton94]. These trends are increasing the sensitivity of overall performance to cache designs. Jouppi notes that disabling the cache of the VAX 11/780, a machine introduced in the late 1970's, would only increase run times by a factor of 1.6 [Jouppi90]. Disabling the cache of a more recent machine, the HP 9000/735 introduced in the early 1990's, would increase its run times by a factor of 15 [Upton94].

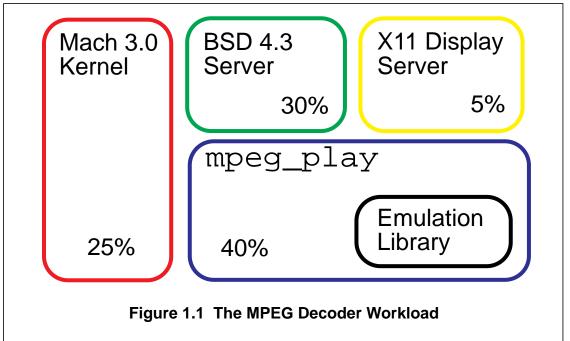

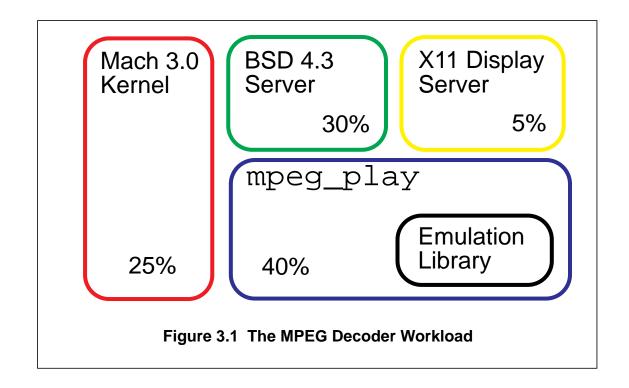

A more subtle reason behind unbalanced memory-system designs is a shift in the utilization of memory resources caused by changes in operating system and application software. A memory system that has been optimized for a given workload, consisting of certain versions of applications and an operating system, is not necessarily optimal for later versions of the same software. An example of this is shown in Table 1.1 which gives the contribution to processor stall cycles of different memory-system components (TLB, I-cache, D-cache and Write Buffer) in an engineering workstation. The last two rows of the table give the performance of the same application (an MPEG decoder, see Figure 1.1) on the same machine (a MIPS-based DECstation) under two

| Operating<br>System | Measurement<br>Method | СРІ  | TLB       | l-cache   | D-cache   | Write Buffer | Other     |

|---------------------|-----------------------|------|-----------|-----------|-----------|--------------|-----------|

| None                | pixie + cache2000     | 1.43 | 0.01(1%)  | 0.06(14%) | 0.05(13%) | 0.18(41%)    | 0.14(32%) |

| Ultrix              | Monster               | 1.66 | 0.01(2%)  | 0.10(15%) | 0.26(39%) | 0.14(21%)    | 0.15(23%) |

| Mach                | Monster               | 2.06 | 0.15(14%) | 0.32(30%) | 0.30(28%) | 0.21(20%)    | 0.08(8%)  |

#### Table 1.1 The Effect of Operating Systems on CPU Stall Behavior

This table shows three collections of CPU stall measurements for the mpeg\_play workload (see Figure 1.1) running on a DECstation 3100. The DECstation 3100 has 64-KB, off-chip, direct-mapped instruction and data caches and a 64-entry, fully-associative TLB. The cache line size is one word. The different columns show the total CPI and the contributions of different system components to CPI increases above 1.0 (this is a single-instruction issue machine). Numbers in parenthesis give the relative contribution of each stall type to CPI increases above 1.0. *Other* stands for non-memory related stalls, such as integer and floating-point interlock cycles.

In the first row, CPI was determined by a cache2000 simulation driven by pixie-generated traces [MIPS88]. cache2000 was configured to simulate a memory system with the same parameters as the DECstation 3100. Because pixie generates single-task, user-only references, this measurement only includes references made by the mpeg\_play task itself (40% of total execution activity). The last two rows give CPI under both Ultrix and Mach as measured by direct monitoring of the DECstation hardware, using the Monster hardware monitoring system [Nagle92]. These last two measurements include 100% of system activity.

$mpeg_play$  decodes an MPEG-compressed video stream and displays the resulting sequence of frames in an X window [Patel92]. We will frequently use  $mpeg_play$  throughout this dissertation as an example of an application that presents a several difficulties to accurate memory-system simulation.

The components of <code>mpeg\_play</code>, depicted in this figure, include a dynamically-linked emulation library, an X11 display server, a user-level BSD server, the Mach 3.0 micro-kernel and the <code>mpeg\_play</code> process itself. The relative importance of each workload component is given as a percentage of total execution time.

The memory-referencing behavior of this application is difficult to analyze because most trace-driven simulators are unable to account for the activity of multiple user-level tasks, dynamically-linked code, or operating system servers and kernels.

different operating systems, Ultrix and Mach. Note that although the workload and machine are the same, the overall CPI under the two operating systems differs by 25%. More importantly, when compared against Ultrix, there is a shift toward greater utilization of the TLB and I-cache under Mach. This shift in memory utilization leads to a different optimal allocation of chip die area for on-chip TLBs and caches [Nagle94].

The increasing sensitivity of overall system performance to cache design, combined with a shift in how memory-system components are utilized by modern applications and operating systems, presents a challenging design problem to computer architects. Before architects commit a

### **Trace-driven Simulation**

```

while (address = next_address(trace)){

if (search(address))

hit++;

else {

miss++;

replace(address);

}

}

```

### **Trap-driven Simulation**

```

traps invoke trap_handler(address):

```

```

trap_handler(address){

miss++;

clear_trap(address);

displaced_address = replace(address);

set_trap(displaced_address);

}

```

### Figure 1.2 Trace-driven and Trap-driven Simulation Algorithms

The core execution loops of trace-driven and trap-driven simulators. This code omits many details of actual simulation, such as the treatment of writes and assigning penalties for different types of misses (e.g., in a critical-word-first cache). Single-pass simulators that evaluate multiple memory configurations in a single trace pass also have a more complex structure [Mattson70; Hill87; Thompson89; Sugumar93].

particular design to silicon, they need a way to evaluate the performance of design alternatives more quickly, accurately and cheaply.

*Trace-driven memory simulation* is probably the most popular method for dealing with this problem [Smith82, Holliday91]. Trace-driven simulation begins by collecting a long sequence of memory references made by some workload of interest. A trace-driven simulator then executes a loop similar to that shown at the top of Figure 1.2. The processing steps include obtaining an

address from a trace, searching for this address in a simulated cache, and then invoking a replacement policy in the event of a miss. The trace addresses can come from a file created by a trace-extraction tool, or they might be generated "on the fly" by an annotated workload. The search procedure involves indexing a data structure that represents the cache and then, depending on the associativity of the cache, performing one or more comparisons to test for a hit. Though a simple operation, the search and test must be performed for every address in the trace.

Over a period of at least 30 years, this basic approach to memory simulation has been continually improved with respect to flexibility, portability, speed, and accuracy. Despite this progress, trace-driven simulators still suffer from an inherent speed bottleneck that is a direct consequence of their basic operation: (1) read *each* address, (2) search and (3) replace on a miss. The result is that the very fastest trace-driven simulators are still from one to two orders of magnitude slower than actual hardware.

This dissertation is about a different method for memory-system analysis, called *trap-driven memory simulation*. This method is based on the observation that most memory references, such as cache hits, do not change a cache's state. Those references that *do* change cache state, such as cache misses resulting in cache-line refills, are far less-frequent events. A trap-driven simulator is designed to only be invoked (trapped to) when the state of a simulated memory structure changes.

Trap-driven simulation is best explained by contrasting its essential features against those of traditional trace-driven cache simulation (see Figure 1.2). As discussed previously, the processing steps in trace-driven simulation include reading each address from a trace, searching for each address in a simulated cache, and then invoking a replacement policy whenever an address misses the simulated cache. A trap-driven simulator operates on a different principle. It is driven not by address traces, but by traps into an operating system kernel where it resides. A trap-driven simulation begins by setting traps on all memory locations in a workload's address space.<sup>1</sup> Locations with traps set represent memory that is not currently resident in a simulated cache structure. As the workload executes, the first reference to each such location causes a trap into the kernel, which is directed to the trap-driven simulator. Because all such traps represent simulated cache. The

<sup>1.</sup> Setting a trap on a memory location means that any reference to it results in a kernel trap that invokes the trap-driven simulator. We discuss a variety of methods for achieving this effect in later chapters of this dissertation.

simulator simply counts the miss and then clears the trap on the required memory location. Clearing the trap effectively caches the memory location in the simulated cache structure because subsequent references to the location will proceed uninterrupted. As a simulated cache begins to fill, incoming traps may collide with previously cached memory locations that map to the same cache line. To mimic the displacement of such lines from an actual cache, the simulator sets a new trap on a previously-cached memory location in accordance with some replacement policy.

The most important aspect of this form of simulation is that it offers the potential for increased simulation speed. Because simulated cache hits do not trap to the simulator, they are processed at the full speed of the underlying hardware. Overall simulation slowdowns are therefore determined by the cost to process cache misses, which are a far less frequent event than cache hits. Trapdriven simulation is, in principle, a promising approach to memory simulation because it overcomes bottlenecks inherent in trace-driven simulation speed. However, a number of practical questions must be answered to determine if trap-driven simulation is actually a viable alternative to trace-driven simulation:

- (1) Flexibility: What is the range of memory configurations, policies, and performance metrics that can be simulated by a trap-driven simulator? Are there any inherent limitations in the flexibility of the method?

- (2) *Portability:* How difficult is it to implement a trap-driven simulator, and what hardware support is required? How could future hardware be designed to better support trap-driven simulation?

- (3) *Speed:* How much overhead is incurred by a simulator trap? Is it so large that overall simulation slowdowns are worse than traditional trace-driven simulation?

- (4) Accuracy: What forms of simulation error are exhibited by a trap-driven simulator and how do these errors compare with trace-driven simulation? Is it possible to take into account references made by all workload components, including multiple user tasks, operating system servers and the kernel?

The purpose of this dissertation is to answer these questions. We begin in Chapter 2 by establishing the current state-of-the-art in trace-driven simulation with a survey of over 50 recent trace-driven simulation tools. The conclusions drawn from this survey will serve as a basis for comparison in our study of trap-driven simulation, which begins in Chapter 3. We introduce the

design of a prototype trap-driven simulator, named *Tapeworm*, which we then use in the remaining chapters to examine the four issues of *flexibility*, *portability*, *speed* and *accuracy*.

We will show that although first-generation trap-driven simulators have exhibited some problems with flexibility and portability, many of these limitations can be overcome through careful simulator design, and with the help of minor and inexpensive modifications to future host hardware. More importantly, we show that trap-driven simulation delivers on its potential to break past bottlenecks in trace-driven simulation speeds. The high speed of trap-driven simulation, combined with its ability to accurately account for multi-task and operating system effects, makes it an attractive alternative to trace-driven simulation in future memory-system designs.

# Chapter 2 Trace-driven Simulation

Trace-driven simulation has been used in the evaluation of memory systems for decades. In his 1982 survey of cache memories, A. J. Smith gives examples of trace-driven memory-system studies that date as far back as 1966 [Smith82]. This chapter is a survey of developments in trace-driven memory simulation during the past 10 years. It plays an important role in this dissertation because it helps to define the classic problems associated with memory-system simulation and the motivating factors behind the vast body of published works on trace-driven techniques. Because the trap-driven approach is an alternative method for memory-system simulation, any arguments for its use must include a comparison against more established techniques. Therefore, a second objective for this chapter is to evaluate the current state-of-the-art in trace-driven simulation in preparation for a comparison with trap-driven simulation. In later chapters, we will see that many of the advances in trace-driven memory evaluation, such as multi-configuration simulation algorithms and set sampling, can also be applied to trap-driven simulation. Thus, a final justification for this survey is that it also benefits the further development of trap-driven simulation.

This is not the first survey of trace-driven simulation techniques. Holliday examined the topic for uniprocessor and multiprocessor memory-system design [Holliday91] and Stunkel et al. studied trace-driven simulation in the specific context of multiprocessor design [Stunkel91]. However, developments in the field during the past three to four years, together with the need to elaborate issues of importance in this dissertation warrant a new examination of these methods.

Although trace-driven methods have been successfully applied to other domains of computer architecture, such as the simulation of instruction microarchitectures, this survey will focus on trace-driven *memory-system* simulation. In particular, we are primarily interested in uniprocessor memory-system design that takes into account operating-system activity. Throughout this chapter, we will comment on the strengths and weaknesses of various trace-driven approaches in terms of

desirable features for any memory simulation technique, such as *flexibility*, *portability*, *speed*, and *accuracy*.

This study will begin by defining the characteristics of an ideal trace-driven simulation environment. This is followed by an analysis of over 50 actual implementations of trace-driven simulation tools, noting how they compare against the ideal. This chapter has been organized so that it can be read at two different levels of detail. A good sense of the overall goals and strategies of trace-driven simulation, along with the capabilities of existing tools can be obtained by reading just the first and last sections (Section 2.1 and Section 2.3) and then scanning the summary tables that accompany each subsection in Section 2.2. An in-depth reading of the text in Section 2.2 offers additional information and insights that are not captured by the summary tables alone.

#### 2.1 Ideal Trace-driven Memory Simulation

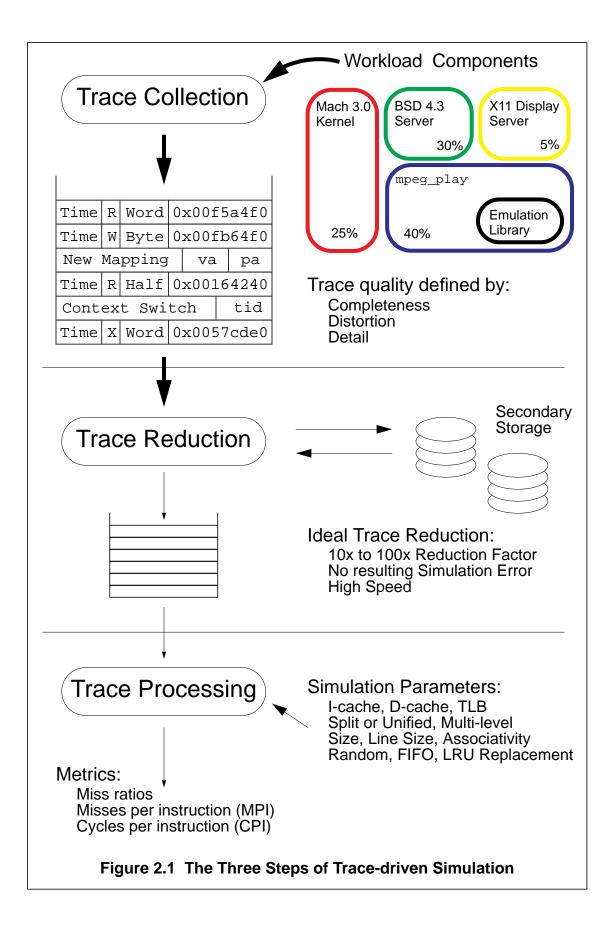

An ideal trace-driven memory simulation environment supports three main activities: *trace collection*, *trace reduction* and *trace processing* (See Figure 2.1).

*Trace collection* is the process of determining the exact sequence of memory references made by some workload of interest. To ensure accurate simulations, the collected address trace should be as close as possible to the stream of memory references made by the workload when running on an actual system. In particular, an ideal trace should be *complete*, *detailed*, and free of any *distortions*.

A *complete* trace includes all memory references made by each component of the system, including all user-level tasks and the operating system kernel. User-level tasks include not only applications, but also OS server and daemon tasks that provide services such as a file system or network access. Because dynamically compiled and linked code is becoming increasingly important in applications such as multiple API and ABI emulation [Nagle94; Cmelik94], a complete trace should also include references made by this form of code.

An ideal *detailed* trace is one that is annotated with information beyond simple raw addresses. Useful annotations include changes in VM *page-table state* for translating between physical and virtual addresses, *context switch points* with identifiers specifying newly activated tasks, and tags that mark each address with a *reference type* (read, write, execute), *size* (word, half word, byte) and a *timestamp*.

Ideal traces should be *undistorted* so that they do not include any additional memory references, or references that appear out of order. Though this is usually not a problem with single-task traces, various forms of distortion can affect the quality of more complete traces that include multi-task and operating-system references. These distortions, which will be discussed in greater detail later, include *trace discontinuities, time dilation* and *memory dilation*.

Although the three aspects of trace quality described above are the most important considerations, ideal trace collectors should have other characteristics as well. In particular, *portability*, both in moving to other machines of the same type and to machines that are architecturally different is important. Finally, an ideal trace collector should be *fast*, *inexpensive* and *easy to operate*.

Address traces can be very large, consuming both storage space and processing time. An ideal trace-driven simulation environment should include *trace-reduction* techniques that help to reduce these space and time requirements by removing unneeded or redundant data from full address traces. Ideal trace reduction should achieve very high levels of data compression without affecting the accuracy of simulations performed by the reduced traces. It may be acceptable to relax the constraint of exact trace reduction if higher levels of compression can be attained and if the resulting degree of simulation error is low. As with ideal trace collection, ideal trace reduction should be fast, inexpensive and easy to use.

The final stage of trace-driven simulation is *trace processing*. An ideal address-trace processor would be able to simulate a wide range of memory system hierarchies consisting of caches, TLBs, and primary- and secondary-storage devices. Ideally, these simulations would produce a range of performance metrics, such as miss ratios, misses per instruction (MPI) and memory cycles per instruction (CPI) for each component of the memory system.<sup>1</sup> An ideal trace processor would be able to simulate all memory system configurations of interest in a single pass over the trace data, quickly and cheaply, producing error-free performance metrics, even from reduced trace data.

The individual stages of trace-driven simulation must be connected through *trace interfaces* so that trace data can flow from one stage to the next. In the ideal case, the overhead of these interfaces would be negligible, adding little to the overall simulation time. Ideal trace interfaces

<sup>1.</sup> These performance metrics, along with others, are defined in greater detail in Chapter 4.

would also offer unlimited buffering so that different stages of trace-driven simulation can be performed at different times and so that trace data can be reused without having to be recollected.

#### 2.2 An Analysis of the State-of-the-art in Trace-driven Simulation

Achieving all of the characteristics of ideal trace-driven simulation as defined above is difficult to do in practice. Nevertheless, considerable progress has been made during the past decade to develop good trace-driven simulation environments. In this section we study the techniques, the algorithms and several example implementations of actual trace-collection, trace-reduction and trace-processing tools to determine how close they come to the ideal.

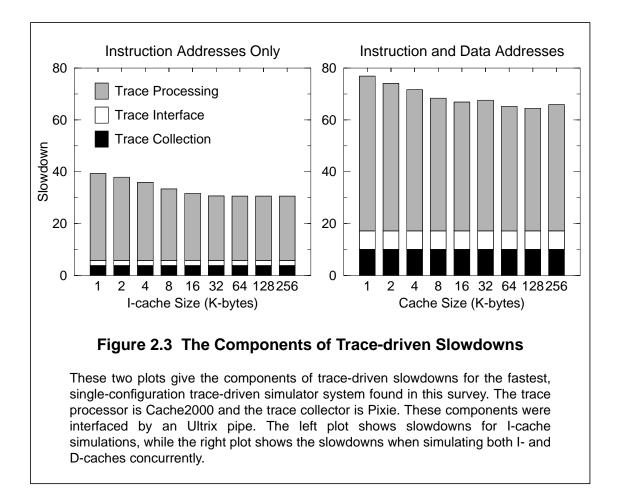

Before we begin our analysis, we must define an important metric that we use to compare the speed of different trace-driven simulation tools. The rate at which addresses are collected, reduced or processed is one natural way to measure speed, but this metric makes it difficult to compare trace collectors or processors that have been implemented on dissimilar hardware. Because the number of addresses processed per second by a particular trace processor is a function of the speed of the host hardware on which it is implemented, it is not meaningful to compare this rate against a different trace-processing method implemented on slower host hardware. To overcome this difficulty, we report all speeds in terms of *slowdown* relative to the host hardware from which traces are collected from or processed on. Depending on the context, slowdowns are computed in a variety of ways:

Slowdown = (Address Collection Rate) / (Host Address Generation Rate) (Eqn 2.1)

Slowdown = (Address Processing Rate) / (Host Address Generation Rate) (Eqn 2.2)

Note that each of these definitions divides by the speed of the host hardware and thus allows a rough comparison of two methods implemented on different hosts.

#### 2.2.1 Trace Collection

Of the three basic stages of trace-driven simulation, the problem of trace collection is probably the most difficult and has certainly received the most attention in terms of published work.

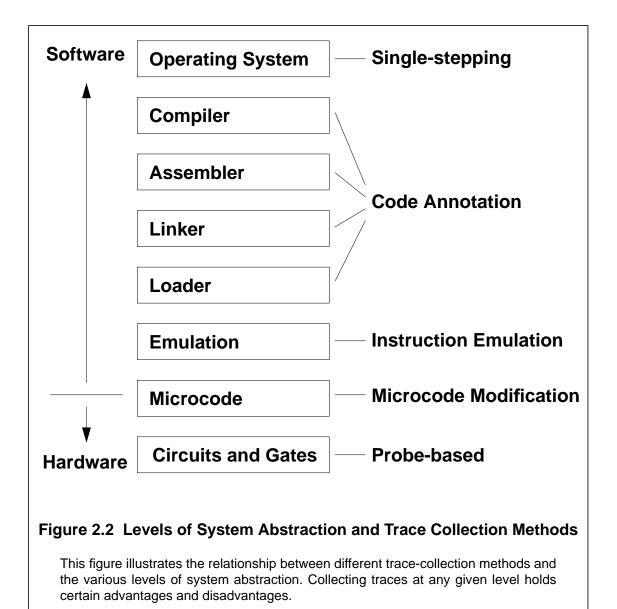

Address traces have been extracted at virtually every system level, starting at the circuit and microcode levels all the way up to the compiler and operating system levels (see Figure 2.2). Table 2.1 arranges approaches to trace collection into five basic categories, along with a summary of their defining characteristics. After examining each of these different methods in greater detail, we will return to this table to draw general conclusions about the state-of-the-art in trace collection techniques.

| С            | haracteristics          | Probe-based | Microcode<br>Modification | Instruction-set<br>Emulation | Static Code<br>Instrumentation | Single-step<br>Execution |  |

|--------------|-------------------------|-------------|---------------------------|------------------------------|--------------------------------|--------------------------|--|

| Completeness | Multi-task              | Yes         | Yes                       | Maybe                        | Maybe                          | No                       |  |

|              | Kernel                  | Yes         | Yes                       | Maybe                        | Maybe                          | No                       |  |

|              | Dynamically-compiled    | Yes         | Yes                       | Yes                          | No                             | No                       |  |

|              | Dynamically-linked      | Yes         | Yes                       | Yes                          | Maybe                          | No                       |  |

| Detail       | Tags (R / W / X / Size) | Yes         | Yes                       | Yes                          | Yes                            | Yes                      |  |

|              | Virtual Addresses       | Maybe       | Yes                       | Yes                          | Yes                            | Yes                      |  |

|              | Physical Addresses      | Yes         | Yes                       | Emulated                     | No                             | Yes                      |  |

|              | Task Identifiers        | Maybe       | Yes                       | Emulated                     | Maybe                          | N/A                      |  |

|              | Time Stamps             | Yes         | No                        | Maybe                        | No                             | No                       |  |

| Distortions  | Discontinuities         | Yes         | Yes                       | No                           | Maybe                          | N/A                      |  |

|              | Time Dilation           | No          | 10 - 20                   | No                           | 2 - 30                         | N/A                      |  |

|              | Memory Dilation         | No          | No                        | No                           | 4 - 10                         | N/A                      |  |

| Slowdown     |                         | 1,000 +     | 10 - 20                   | 15 - 75                      | 10 - 30                        | 50 - 100                 |  |

| Memory       |                         | Ext. Buffer | Host Buffer               | 4 - 40                       | 10 - 30 + Buffer               | Host Buffer              |  |

| Expense      |                         | High        | Medium                    | Medium-Low                   | Medium-Low                     | Low                      |  |

| Portability  |                         | Low         | Very Low                  | High-Medium                  | Medium                         | High                     |  |

| Ease-of-Use  |                         | Low         | High                      | High                         | High-Low                       | High                     |  |

## Table 2.1 Summary of Trace-collection Methods

This table summarizes the characteristics of five common methods for collecting address traces. For the descriptions of trace quality (*completeness, detail* and *distortions*) a *Maybe* entry means that the method has inherent difficulty providing data with the given characteristics, but there are examples of tools in the given category that overcome these limitations. The ranges given in the *slowdown* row exclude times for excessively bad implementations.

#### **External Hardware Probes**

A straightforward method for collecting address traces is to record signals from electrical probes physically connected to the address bus of a computer while it runs a workload. These address and control signals are fed into a high-speed memory buffer at the full speed of the monitored system. Some mechanism is required to move the contents of the hardware trace buffer to a standard storage device, such as tape or disk, so that it can be processed at a later time. If a long, continuous address trace is desired, then the buffer must either be very large or there must be some way to stall the monitored system. If there is no way to stall the system, then several discontinuous address-trace samples can be acquired and concatenated together. The resulting trace exhibits a form of distortion that we will call *trace discontinuity*. Under certain circumstances (see the discussion on time sampling in Section 2.2.2), traces with discontinuities can be used to perform the same sort of memory simulations enabled by longer, continuous traces, but with some sampling error. Table 2.2 summarizes several probe-based trace collectors recently described in the literature. We discuss each in greater detail below.

Most commercial logic analyzers provide the necessary hardware to construct a tracecollection system [Tektronix94; HP91]. Alexander et al. used this approach by connecting a logic analyzer to a National Semiconductor 32016-based workstation running Genix to collect address traces for TLB and cache simulation [Alexander85; Alexander86]. The small size of the trace buffer (4096 entries of 32 bits each) required the design of some circuitry to place the processor in a stalled state while the buffer was unloaded to a secondary-storage device. A similar approach was used by a team including the author who connected a DAS 9200 logic analyzer to an R2000based DECstation 3100 to obtain traces in a system called *Monster* [Nagle92]. In this system, the operating system kernel was modified to stall the machine in a software loop, avoiding the need to design any additional hardware. Some logic analyzers provide interchangeable probes to more easily support multiple architectures. For example, in addition to support for MIPS processors, the DAS 9200 also has probe modules for most other popular microprocessors. Fuentes has demonstrated this portability by using a DAS 9200 to collect addresses from both Alpha-based and Pentium-based workstations [Fuentes93].

When a probe-based trace collector stalls a processor, subsequent activity by that processor may be different from the activity that would have ensued had the stall not occurred. In other words, the traces become distorted. The resulting traces still capture all activity, but they still exhibit *trace discontinuities* because of gaps in real time. For example, if only the processor is

| Reference                    | Nomo    | Draaaaar              | Buff    | er Size    | Stall Method               |                  | Download<br>Channel   |

|------------------------------|---------|-----------------------|---------|------------|----------------------------|------------------|-----------------------|

|                              | Name    | Processor             | Entries | Entry Size | Stall Method               | Completeness     |                       |

| [Alexander85]                | _       | NS 32016              | 4 K     | 32 bits    | HOLD Logic                 | All References   | Serial                |

| [Nagle92]                    | Monster | R2000                 | 512 K   | 96 bits    | Kernel Idle Loop           | All References   | Ethernet              |

| [Fuentes93]                  | _       | Alpha, Pentium        | 512 K   | 156 bits   | None                       | Cache Misses     | Ethernet              |

| [Happel92]                   | _       | R2000                 | 8 M     | 40 bits    | _                          | All References   |                       |

| [Fuentes93]                  | MTM     | i486                  | 33 M    | 80 bits    | None                       | Bus Transactions | Ethernet              |

| [Flanagan92]<br>[Flanagan94] | BACH    | i486, 68030,<br>SPARC | 80 M    | 96 bits    | High-priority<br>Interrupt | All References   | Parallel DIC<br>Board |

| [Torellas92]                 | DASH    | R3000                 | 2 M     | 72 bits    | Master Process             | Bus Transactions | Ethernet              |

| [Biomation91]                | K450M   | —                     | 80 M    | 64 bits    | _                          | _                | 12 Mbits/se<br>DMA    |

### Table 2.2 Probe-based Trace Collectors

All of the probe-based trace collectors in this table collect complete address traces with multi-task and operating system references. Buffer size determines the maximum sample size of uninterrupted memory references that can be captured. Most collectors can stall the monitored system when the trace buffer becomes full, but some cannot (see *Stall Method*). The speed with which the trace buffer can be unloaded is determined by the *Download Channel* which typically moves data at much lower bandwidths than the rate at which traces are acquired. Some probe-based trace collectors are only able to collect cache misses or bus transactions, not complete address traces (see *Completeness*).

stalled, external I/O devices, such as disks or network controllers, will continue to operate and will appear to the stalled processor to respond faster than they normally would. Stalling too long or too frequently may result in distorted traces that do not accurately reflect true system operation.

A problem with hardware monitors based on logic analyzers is that their trace buffer sizes are often relatively small (4 K-entries to 128 K-entries), resulting in frequent processor stalls, and thus greater distortion in the trace due to discontinuities. Special-purpose hardware with very large, high-speed memories has been built to reduce the extent of this problem. Biomation Corporation builds a trace-collection system with 80 million trace buffer entries [Biomation91]. The trace collector described in [Happel92] has a 40 M-byte trace buffer, large enough to hold 8 million memory references at a time. The *Magellan Trace Machine (MTM)* has buffer that can hold 33 million bus transactions [Fuentes93], and recent versions of the *Bach* system use similarly large buffers [Flanagan94].

The trend towards higher levels of chip integration creates a problem for probe-based trace collection. Most recent microprocessors implement at least their primary caches and TLBs onchip, making many of their important address and control signals inaccessible to external probes [MPReport93; MPReport94]. Examples of probe-based trace collectors that are limited in this way are described in [Torrellas92] and [Fuentes93]. One solution to this problem is to deactivate onchip caches to force all load and store operations off chip where they can be detected by external probes. However, this action can perturb the behavior of the system. Even if the resulting trace distortion is considered acceptable, some processors do not support disabling of on-chip caches in a general way [Digital92; Fuentes92]. Although full address traces are desirable, a trace of just cache misses is by no means worthless. As we will see in Section 2.2.2 on trace reduction, a trace of cache misses can still be used to simulate other cache configurations, subject to certain restrictions.

There are numerous other examples of hardware-based monitors that give performance information specific to the particular memory system implemented by the host hardware. These monitors, which usually consist of collections of event counters [Nagle92; Digital92; Cvetanovic94; IBM90] or address histograms [Emer84; Clark85b], do not collect address traces and therefore cannot be used to determine the performance of memory systems that are different from the monitored system.

The main advantage of all of the probe-based trace collectors described above is their ability to capture trace sequences complete with both user and kernel memory references, and free of most forms of trace distortion, provided the trace buffer is deep enough. Although the traces are complete, this does not necessarily mean that they are easy to interpret. Hardware events such as cache misses, integer- and floating-point-unit stalls, exceptions and interrupts all must be separated from run cycles to determine the actual type (read, write, execute) and size (word, half word, byte) of the memory references made by a monitored processor. This essentially amounts to implementing the inverse function of the processor sequencer, either in the trace-collecting hardware, or in a trace post-processing tool [Nagle92]. Because the addresses captured by a probebased monitor are usually physical addresses, special methods that require cooperation from the host OS must be used to reverse translate these physical addresses to their matching virtual addresses [Grimsrud93]. For similar reasons, it is often difficult to relate a given memory reference to the task that made it without assistance from a modified OS kernel that emits trace markers or other annotations as clues [Torellas92; Nagle92; Fuentes93]. These problems all follow from the fact that probe-based trace collectors are external to the monitored system and therefore do not have easy access to operating system data structures held inside the system.

A common misconception regarding trace collection using hardware probes is that the technique is very fast. While it is true that acquisition of the trace proceeds at the full speed of the monitored system, it is important to include the overhead of managing trace-buffer overflow and unloading the trace-buffer memory. This overhead is typically not reported in published papers, but because most systems can only unload these buffers through some form of relatively low-bandwidth channel (see Table 2.2), this overhead is necessarily high. For a system where overhead data is available (Monster), approximately 12 hours are required to obtain 11 seconds of real-time system activity in a fully-automated system. Fuentes has reported that a similar delay of 45 minutes is required to download about one second of real-time activity captured by the MTM system [Fuentes93]. These delays represent effective slowdowns of more than a thousand times the speed of unmonitored hardware. The overhead from both these systems comes from moving trace-buffer data over an Ethernet to a machine with SCSI-connected disks. Most of the other systems listed in Table 2.2 use similar or even lower-bandwidth interconnect to the trace buffer, so their overheads should be comparable or higher.

Hardware probe-based methods share other common disadvantages. The first is expense. Logic analyzers with deep trace memories cost in the range of \$50,000 to \$200,000 [Tektronix94;

HP91]. These amounts are probably low compared to the engineering costs associated with designing custom hardware as in [Flanagan92] or [Torellas92]. A second problem is portability. Although logic analyzers like the DAS 9200 support most popular microprocessors with custom probes, making it easier to move to other architectures, it is often necessary to physically modify the motherboard or chassis of the monitored system to enable probe access to the signals of interest [Nagle92; Fuentes94]. Finally, these systems are generally not very user friendly, often requiring a long start-up period to learn to operate.

As noted above, the advent of on-chip caches is making it increasingly difficult to build trace collection hardware as an afterthought. The future of probe-based trace collection will therefore be determined mainly by the level of support *designed* into systems for this activity. A small, on-chip trace buffer that traps to the kernel whenever it becomes full is an example of the sort of support that could be provided. However, even a very small buffer of 2048 entries with 32-bits per entry (8 K-bytes) is about the size of on-chip caches in current microprocessors [Nagle94] and thus would be relatively costly in terms of chip area. We are not aware of any existing microprocessor that includes such hardware.

#### **Microcode Modification**

The high cost circuit-level probing has motivated many researchers to develop methods for collecting traces at higher levels of system abstraction. In this section we examine a form of trace collection that takes place at the microcode level, which is on the borderline between the hardware and software levels of a system (see Figure 2.2).

From the beginnings of the IBM 360 series (1964) until the DEC VAX machines, the most common method for implementing control logic was microcode. When implemented off-chip, a microcode memory is often writable or can be modified through replacement, making it possible to change the behavior of instructions, or to support multiple instruction sets. Agarwal realized that this mechanism makes it possible to collect address traces [Agarwal86; Agarwal88]. He modified the microcode on a VAX 8200 to cause all instructions to deposit the addresses of their memory references into a reserved area of main memory as a side effect of their execution.

This method, which Agarwal calls *address tracing using microcode (ATUM)*, offers a number of advantages. The first is completeness. Because the microcode runs "beneath" the operating system, all user and kernel references are captured, as well as those from dynamically-compiled

and dynamically-linked code. Because ATUM has access to internal system state, it is easily able to annotate traces with access-type tags, context switch points, and page-map information. Another advantage is speed. ATUM acquires address traces with a slowdown of only about 10 to 20, and because the addresses can be processed directly out of the trace buffer in main memory, there is not the same overhead for buffer unloading as with external probe-based trace collection. Finally, because no additional hardware is required, the only cost associated with ATUM is the engineering effort required to modify microcode to produce the desired results.

The ATUM method suffers from a few minor disadvantages and one major one. First, ATUM traces exhibit some discontinuity distortion because the processor is not stalled when the trace buffer becomes full. Buffer size can only be increased to a certain point because it takes away from the usable memory of the host system.<sup>2</sup> Agarwal has developed a method, called *trace stitching*, to treat this problem [Agarwal89]. Microcode modification also introduces another form of trace distortion, commonly called *time dilation*. Because instructions take 10 to 20 times as long to execute as they normally would, external events such as clock interrupts will occur more frequently. This causes more frequent invocations of the code that handles clock interrupts, disturbing TLB and cache state. More frequent clock interrupts can also cause scheduling quanta to expire more rapidly, resulting in changes in the behavior of the CPU scheduler. Another disadvantage is that the method captures only microcode-controlled activities, meaning that I/O activity and other memory transactions controlled by hardwired logic are not captured. The primary disadvantage of the microcode-modification technique is that it suffers from poor portability. Because most modern processors have a hardwired control, rather than being microprogrammed, this technique is no longer generally applicable [Hennessey90]. In such systems, trace collection is more conveniently performed at higher levels in the system. For example, RISC processors are typically implemented with hardwired control and are therefore not amenable to microcode modification. However, the relatively simple and uniform coding of RISC instruction sets has lead to the development of fast instruction-set emulators and binary-rewriting tools that instrument executables to produce traces as a side effect of their normal execution (see the following sections on *instruction-set emulation* and *code annotation*).

<sup>2.</sup> In Agarwal's implementation, the size was limited to 2 MB, which holds 400,000 memory references.

While most RISC machines no longer use microcode, some CISC machines as the x86 series from Intel still do. However, this microcode resides in an unmodifiable, on-chip ROM. This suggests that microcode modification may still be a viable method,<sup>3</sup> but as with probe-based monitoring, it can no longer be added to a processor as an afterthought; if future processors wish to take advantage of this technique, it must be *designed* in from the start.

#### **Instruction-set Emulation**

An instruction-set architecture (ISA) is the set of instructions that defines the interface between hardware and software for a particular machine. A microcode engine is an ISA interpreter that is implemented in hardware. It is also possible to interpret an instruction set in software through the use of an *instruction-set emulator*. Emulators typically execute one instruction set (the *target* ISA) in terms of another instruction set (the *host* ISA) and are usually used to enable software development for a machine that has not yet been built, or to ease the transition from an older ISA to a newer one [Sites92]. As with microcode, an instruction-set emulator can be modified to cause an emulated program to generate address traces as a side-effect of its execution.

Conventional wisdom holds that instruction-set emulation is very inefficient, with slowdowns estimated to be in the range of 1,000 to 10,000 [Agarwal89; Wall89; Borg89; Stunkel91; Flanagan92]. Clearly, the degree of slowdown is related to the level of emulation detail. For some applications, such as the verification of a processor logic design, the level of detail required is very high and the corresponding slowdowns may agree with those cited above. However, in the context of this review, we consider an instruction-set emulator to be sufficiently detailed for the purposes of address-trace collection if it produces an accessible stream of instruction and data references as part of its emulation. Given this minimal requirement, there are several recent examples of instruction-set emulators that have achieved slowdowns much lower than 1,000 (see Table 2.3).

*Tracer* [Henry83] and *Spa* [Cmelik93] are examples of slow instruction-set emulators. They work by reading, interpreting and dispatching instructions one at a time. Instructions are reinterpreted each time they are encountered. Reported slowdowns for these iterative emulators range from 500 to about 1,500.

<sup>3.</sup> Not all Pentium instructions come out of the microcode store, so such modifications could be challenging.

| Reference     | Name   |                                |                                   | Method                   | Multi-<br>task | Kernel | Slowdown           |  |

|---------------|--------|--------------------------------|-----------------------------------|--------------------------|----------------|--------|--------------------|--|

| [Henry83]     | Tracer | VAX 11/780                     | VAX 11/780                        | Iterative Interpretation | No             | No     | 1,500              |  |

| [Cmelik93]    | Spa    | SPARC                          | SPARC                             | Iterative Interpretation | No             | No     | 600                |  |

| [Larus91]     | SPIM   | MIPS-I                         | SPARC, 680x0, MIPS,<br>x86, HP-PA | Predecode to IR          | No             | Some   | 25                 |  |

| [Cmelik93]    | Shadow | SPARC                          | SPARC                             | Dynamic Compilation      | No             | No     | 64                 |  |

| [Magnusson93] | gsim   | 88100                          | HP-PA, SPARC                      | Block Compilation        | Yes            | Some   | 35 - 45<br>50 - 74 |  |

| [Veenstra94]  | MINT   | R3000                          | R3000                             | Block Compilation        | Yes            | No     | 18 - 65            |  |

| [Bedicheck94] | mg88   | 88100                          | SPARC, 680x0, 88100               | Threaded Code            | Yes            | Some   | 54 - 74            |  |

| [Cmelik94]    | Shade  | SPARC-V8,<br>SPARC-V9,<br>MIPS | SPARC-V8                          | Dynamic Compilation      | No             | No     | 9 - 14             |  |

## Table 2.3 Trace Collection through Instruction-set Emulation

We define an instruction-set emulator to be a program that directly reads executable images written in one ISA (the target) and that emulates it using another ISA (the host). In general, the target and host ISAs do not need to be the same, although they may be. We only consider instruction-set emulators that also generate address traces. For a more complete survey of instruction-set emulators in general, see [Cmelik94]. Some of these tools support multi-processor simulation. In these cases, slowdowns are given for a single process, but may include some un-removable overhead due to the multi-processor support. The faster emulators use a variety of techniques to achieve their speed. In *SPIM*, a MIPS-I executable is read and translated, in its entirety, to an intermediate representation understood by the emulation engine [Larus91]. After translation, emulation slowdown relative to the host hardware is a factor of approximately 25. *Shadow* dynamically compiles only target instructions that are actually executed into a form that can be run directly by the host [Cmelik93].

A later generation of Shadow, named *Shade*, also uses dynamic compilation to host instructions, but translations are cached so that each instruction is compiled only once. In this system, as each instruction is referenced for the first time it is compiled into an efficient sequence of native instructions that runs directly on the host machine. Compiled sequences of native code are recorded in a lookup table, which is checked by a core emulation loop each time it dispatches a new instruction. If a compiled translation already exists, is it found through the lookup mechanism and the code sequence need not be recompiled. Both Shadow and Shade support address-trace processing by calling user-supplied "analyzer" code after each instruction is emulated. The analyzer code is given access to the emulation state, such addresses generated by the previous instruction, so that memory simulations are possible. The slowdowns reported in Table 2.3 are for Shadow and Shade emulations with a null analyzer.

Like Shadow and Shade, *MINT* [Veenstra94] and *gsim* [Magnusson93] also dynamically compile code into the sequences of host instructions that are then saved for future re-execution. But unlike Shade, which compiles one instruction at a time, these simulators compile clusters of several source instructions together. This strategy makes it possible to construct more efficient sequences of equivalent host instructions because less emulator state must be saved and restored between each translated instruction.

Each of the emulators described up to this point rely on a core emulation loop that is executed after each emulated instruction or block of instructions executes. The *mg88* emulator avoids this overhead by combining dynamic compilation with a technique called *threaded-code execution* that directly links multiple translations together. These links, from one translation to the next, avoid the need to return to the core execution loop until a new, untranslated instruction is encountered [Bedichek94].

These last three emulators (MINT, gsim and mg88) exhibit slowdowns as high as 65 to 75. However, this reflects the additional overhead required to generate multi-processor address traces. The reported slowdowns are in some cases higher than they need to be for address-trace collection because they include additional emulation detail. For example, the mg88 emulator models instruction-execution times and includes full simulation of caches, a memory management unit and I/O devices [Bedichek94]. The gsim slowdowns reflect a similar overhead for more complete system simulation, but the MINT slowdowns are for emulation with address generation only.