## **Of Limits and Myths in Branch Prediction**

by

Avinoam Nomik Eden

A dissertation submitted in partial fulfillment of the requirement for the degree of Doctor of Philosophy (Computer Science and Engineering) in the University of Michigan 2001

Doctoral Committee: Professor Trevor N. Mudge, Chair Professor Richard B. Brown Associate Professor Marious Papaefthymiou Assistant Professor Steven Reinhardt Assistant Professor Gary Tyson

#### **Of Limits and Myths in Branch Prediction**

by

#### Avinoam Nomik Eden

#### **Chair: Trevor N. Mudge**

The need to flush pipelines when miss-predicting branches occur can throttle the performance of a pipelined super-scalar microprocessor. It is argued that by the year 2010 branch prediction will become the most limiting factor in processor performance [1]. A plethora of research has been done on the subject of branch prediction. While many branch prediction structures have been proposed, their performance is usually demonstrated empirically through simulations that provide little insight into the underlying principle that enables their behavior.

Since the introduction of the two-level dynamic branch prediction scheme, research into branch prediction has followed four different paths. The first attempts to improve prediction by reducing aliasing in the second level table, which was shown to adversely affect prediction accuracy. The second attempts to improve prediction accuracy by combining two or more different components in the branch prediction structure. The third attempts to improve prediction by changing the configuration of a particular predictor. Lastly, the fourth, tries to find new schemes to improve branch prediction. Most papers on research along one path ignored comparisons with other paths on the basis that the different paths are orthogonal. A set of studies is presented that consolidate the different research paths by showing that the advantage gained by most of them is to reduce aliasing. After showing that reducing aliasing is the prevailing factor in prediction gain regardless of which path of research is followed, we highlight a set of criteria that a predictor should embrace, to have a good prediction. The criteria emerge from the studies we performed and previous work on the subject.

The set of criteria, a predictor should follow to achieve good prediction accuracy, is used to build a new predictor – YAGS. YAGS outperforms the leading branch predictor structures from the different paths of research. It provides the micro-architect with a set of parameters that can be used to meet different restrictions, such as size and latency.

This work highlights misconceptions that resulted from the work done on the topic. It especially stresses the importance of a relevant limit study for understanding a new branch prediction scheme and structure.

## ACKNOWLEDGEMENTS

I would like to thank my parents, which provided a worry free environment for pursuing my higher education, and in the process turned me into an over-educated spoiled brat. Thank you.

Thanks to my advisor, professor Trevor Mudge, for deciding I should pursue my Ph.D. Thank you for the pets on the back and kicks in the butt you provided as necessary, and, of course, for translating my papers into English. Thank you.

Thanks to my boss and my friend Vik Kheterpal for providing a flexible work environment and support that allowed me to pursue my PhD while holding a job.

Special thank you to Professor Kevin Compton and Robin Rennie for providing mental support and concrete advice during my early stages of education. Thank you.

Thank you to Jeff Ringenberg and Adam Freund. It was a pleasure working with you.

Moreover O, thanks to Amy Claire Harfeld for editing this dissertation and coping with the bore.

## **TABLE OF CONTENTS**

|       | NOWLEDGEMENTii                                      |  |  |  |

|-------|-----------------------------------------------------|--|--|--|

|       | OF TABLESvi<br>OF FIGURESvi                         |  |  |  |

|       | er 1 - Introduction 9                               |  |  |  |

| onupt |                                                     |  |  |  |

| 1.1   | The Branch Irony 9                                  |  |  |  |

| 1.2   | Solutions to the Branch Problem 11                  |  |  |  |

| 1.3   | <b>3</b> Directions in Dynamic Branch Prediction 12 |  |  |  |

| 1.4   | 4 Thesis Statement 14                               |  |  |  |

| 1.5   | 5 Contributions of This Dissertation 15             |  |  |  |

| 1.6   | Organization 16                                     |  |  |  |

| Chapt | er 2 - Previous Work 18                             |  |  |  |

| 2.1   | Prediction Schemes 18                               |  |  |  |

| 2.    | 1.1 Bimodal<br>                                     |  |  |  |

| 2.1   | .2 History Only Branch Predictor                    |  |  |  |

| 2.1   | .3 Two-level Adaptive Branch Predictors             |  |  |  |

| 2.1   | .4 Global Two-level Branch Predictors               |  |  |  |

| 2.1   | .5 Local Two-level Branch Predictors                |  |  |  |

| 2.1   | .6 Path-Based Branch Predictors                     |  |  |  |

| 2.1   | .7 Other Schemes                                    |  |  |  |

| 2.1   | .8 Summary                                          |  |  |  |

| 2.2   | Aliasing in Global Predictors 23                    |  |  |  |

| 2.2   | 2.1 The Problem                                     |  |  |  |

| 2.2   | Aliasing Reducing Branch Prediction Structures      |  |  |  |

|       | 2.2.2.1 Gshare                                      |  |  |  |

|       | iii                                                 |  |  |  |

| 2.    | 2.2.2 Agree Predictor 25                                                  |    |

|-------|---------------------------------------------------------------------------|----|

|       | 2.2.2.3 Skew Predictor                                                    | 6  |

|       | 2.2.2.4 Bi-Mode Predictor                                                 |    |

|       | 2.2.2.5 Filter Mechanisms                                                 | 9  |

| 2.2   | 2.3 Summary                                                               | 0  |

| 2.3   | Hybrid Predictors 31                                                      |    |

| 2.3   | 3.1 Hybrid Branch Predictors                                              | 1  |

| 2.3   | 3.2 Selection Mechanisms                                                  | 4  |

| 2.4   | Third-level of Adaptivity 34                                              |    |

| 2.4   | 1.1 Third-level of Adaptivity Structures                                  | 4  |

| 2.4   | 4.2 Selection Mechanisms                                                  | 6  |

| Chapt | er 3 - Experimental Methodology and Benchmark Description 37              |    |

| 3.1   | Experimental Methodology 37                                               |    |

| 3.2   | Benchmarks' Description 38                                                |    |

| 3.3   | Performance Metrics 41                                                    |    |

| 3.4   | <b>Results Presentation 41</b>                                            |    |

|       |                                                                           |    |

| Chapt | er 4 - The Scheme of Schemes Error! Bookmark not defined.                 |    |

| 4.1   | The Difference Between Schemes and Structures Error! Bookmark not defined | 1. |

|       |                                                                           |    |

- **4.2 Limits on Branch Prediction Scheme** Error! Bookmark not defined.

- 4.3 Global Branch Prediction Schemes Error! Bookmark not defined.

- **4.4 The Effect of Aliasing** Error! Bookmark not defined.

- 4.5 Correlation vs. Aliasing Tradeoff Error! Bookmark not defined.

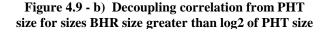

- **4.6 Decoupling Correlation from PHT size** Error! Bookmark not defined.

- Chapter 5 Myths of Hybrid Predictors Error! Bookmark not defined.

- 5.1 Issues in Hybrid Predictors Error! Bookmark not defined.

| 5.2 | Simulation Methodology | Error! Bookmark not defined. |

|-----|------------------------|------------------------------|

|-----|------------------------|------------------------------|

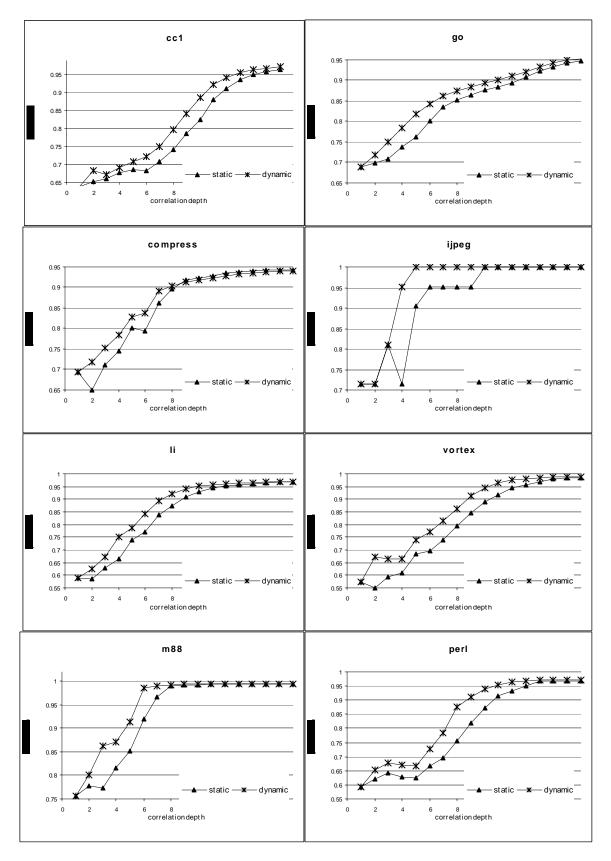

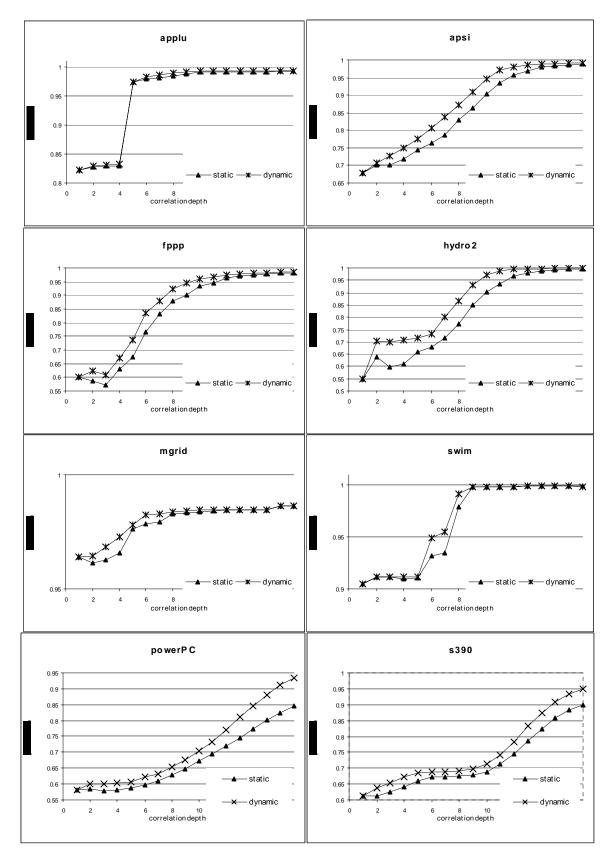

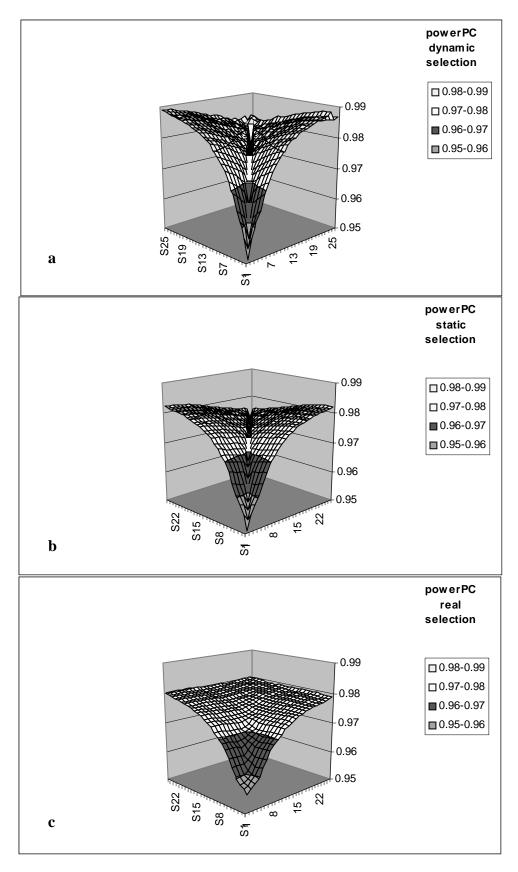

**5.3 Selection Mechanism** Error! Bookmark not defined.

**5.3.1 The Merit of Dynamic Selection Mechanism ..**Error! Bookmark not defined.

**5.3.2** .....**Dynamic vs. Static Selection Mechanism** .....Error! Bookmark not defined.

**5.3.4** Static Aliasing Aware vs. Dynamic Selection Mechanism .....Error! Bookmark not defined.

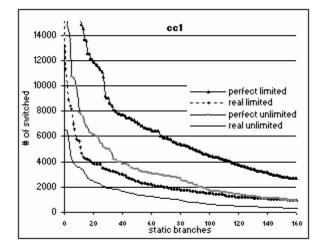

- **5.3.5 Shortcomings of Static Selection**.....Error! Bookmark not defined.

- **5.3.6** In Depth Analysis.....Error! Bookmark not defined.

- **5.4 The Notion of Hybrid Predictors** Error! Bookmark not defined.

**5.5 Updating Policies and Aliasing** Error! Bookmark not defined.

- **5.6 Combining Aliasing and Hybrid Paths** Error! Bookmark not defined.

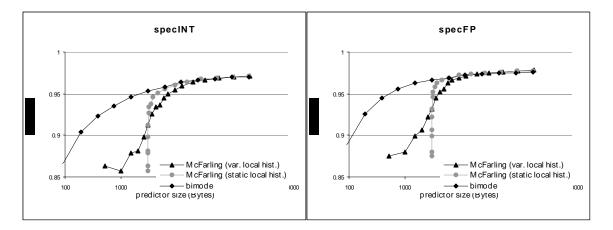

- 5.7 McFarling vs Bi-Mode Predictor Error! Bookmark not defined.

- **5.8 Summary** Error! Bookmark not defined.

**Chapter 6 -Filtering Characteristic of the Third-Level of Adaptivity** Error! Bookmark not defined.

- **6.1 Branch Classification** Error! Bookmark not defined.

- 6.2 Dynamic History Length Fitting Error! Bookmark not defined.

- **6.3 Paths Comparison** Error! Bookmark not defined.

- **6.4 Summary** Error! Bookmark not defined.

**Chapter 7 - The Do's and Don'ts of Branch Predictor Structures** Error! Bookmark not defined.

- 7.1 Micro-architectural Trends Error! Bookmark not defined.

- 7.1.1 Wire Delay .....Error! Bookmark not defined.

| 7.1.2 Software Development | Error! | Bookmark | not defined. |

|----------------------------|--------|----------|--------------|

|----------------------------|--------|----------|--------------|

7.2 Observing Past Work Error! Bookmark not defined.

- 7.2.1 Good Practices.....Error! Bookmark not defined.

- 7.2.2 Bad Practices .....Error! Bookmark not defined.

7.3 Studies Done in This Dissertation Error! Bookmark not defined.

**7.3.1 The Omniscient Dynamic Selection Mechanism...**Error! Bookmark not defined.

7.3.2 Compile Time Information .....Error! Bookmark not defined.

**7.3.3 The Dependence of Correlation on Structure Size**Error! Bookmark not defined.

Chapter 8 -Solutions Error! Bookmark not defined.

8.1 Yet Another Global Structure (YAGS) Error! Bookmark not defined.

| 8.1.1                  |                                                      | Motivatio                     | <b>n</b> Error! Bookmark not defined.                                                                                                              |  |  |

|------------------------|------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 8.1.2                  |                                                      | YAGS                          | Error! Bookmark not defined.                                                                                                                       |  |  |

|                        | 8.1.2.2<br>Bookma                                    | Amount of Ir<br>rk not define | ccuracyError! Bookmark not defined.<br>Information Stored in Prediction StructuresError!<br>d.<br>er Context SwitchingError! Bookmark not defined. |  |  |

| 8.2                    | In-Deptl                                             | h Analysis I                  | Error! Bookmark not defined.                                                                                                                       |  |  |

| 8.3                    | And Yet                                              | More Aliasin                  | g Error! Bookmark not defined.                                                                                                                     |  |  |

| 8.4                    | 8.4 <b>Profile YAGS</b> Error! Bookmark not defined. |                               |                                                                                                                                                    |  |  |

| 8.5                    | The Fut                                              | ure of Profilir               | ng Error! Bookmark not defined.                                                                                                                    |  |  |

| 8.5.1 Profiling        |                                                      | <b>Profiling</b>              | PitfallsError! Bookmark not defined.                                                                                                               |  |  |

| 8.5.2 Dynamic          |                                                      | <b>Dynamic</b>                | ProfilingError! Bookmark not defined.                                                                                                              |  |  |

| Chapter 9 - Conclusion |                                                      | nclusion                      | Error! Bookmark not defined.                                                                                                                       |  |  |

| 9.1                    | Contrib                                              | utions                        | Error! Bookmark not defined.                                                                                                                       |  |  |

## 9.2 Future Work Error! Bookmark not defined.

**Bibliography** Error! Bookmark not defined.

## LIST OF TABLES

**TABLE 3.1 – BRANCH PREDICTION SCHEMES AND THEIR ATTRIBUTES**37

**TABLE 3.2 - BENCHMARK CHARACTERISTICS**39

**TABLE 3.3 – BENCHMARK DESCRIPTION AND DATASETS**40

#### TABLE 8.1. – THE RELATIONSHIP BETWEEN CORRELATION DEPTH AND PREDICTOR SIZE

**INCREMENT** ERROR! BOOKMARK NOT DEFINED.

## LIST OF FIGURES

## **Chapter 1 - Introduction**

As VLSI technology continues to improve, more resources become available for the branch prediction module. Concurrently, newer high-performance machines are implementing deeper pipelines and greater issue-widths. This, in turn, increases the number of branches predicted and not yet retired, and increases the branch misprediction penalty. Code size is expected to increase [2], and the memory state reached in one cycle to decrease [63][65]. Although more resources are available to computer architects, the decreasing state reached in one cycle dictates the usage of smaller branch predictors, if the prediction is going to happen in one cycle. Thus the need to predict more branches with higher accuracy employing a smaller amount of resources continues to grow.

### **1.1 The Branch Irony**

The branch instruction is thing that separates a computer from a calculator. It facilitated the leap from simple sequential calculations performed by a calculator to complex calculations and tasks performed by computers today.

At first, computers executed programs sequentially – one instruction was executed before the next instruction started. By the time the instruction following the branch was fetched, the outcome of the branch instruction was known and it was clear which instruction was to follow. Micro-architectural mechanisms to speed execution led to pipelining and super-scalar cores. With these innovations, more than one instruction is executed concurrently, and possibly, execution is not completed in sequential order.

Pipelining and super-scalar architectures have resulted in several complications. One of the more prominent ones is the control hazard. This arises when the instruction following a branch is fetched before the branch instruction is fully executed. When that instruction is executing, it is not clear whether the branch is going to be taken or not. If the branch is taken, the address of the next instruction (the branch target address) is not yet calculated. One solution to the control hazard problem is to stop further instruction fetching until the branch is finished executing. This, however, reduces the advantage gained by pipelined and super-scalar architectures, and therefore is not a desirable solution. A better solution would be to make an educated guess at the branch direction and target address and to follow the execution accordingly. If the guess is correct, pipelining and super-scalar architectures would be allowed to fulfill their potential. If an incorrect guess is made, a recovery mechanism would need to be in place to roll back the machine to the state just after the miss-predicted branch finished executing. This process is the process of branch prediction.

It is estimated that 1 out of 5 instructions is a branch instruction. Current microprocessors demand instructions at a high rate, and attempt to fetch 4 and 6 instructions per cycle. With a pipeline of up to 15 stages deep, the number of instructions that can be executed concurrently is well over the 5 mentioned above. In order to feed such engines, an accurate branch prediction is needed. It is argued that by the year 2010 branch prediction will become the most limiting factor in processor performance, surpassing even the limitations imposed by memory systems [1].

The branch irony is that the same mechanism that helped computers evolve past the functions of a mere calculator becomes the limiting factor for future generations of computers.

#### **1.2** Solutions to the Branch Problem

A number of ways have been devised to overcome the control flow problem imposed by sequential code. Eliminating false control dependencies allows unnecessary stalls to be eliminated [3][4]. Code transformation by compilers to enlarge basic blocks reduces the occurrence of some branches. Loop unrolling, a form of basic block enlargement, is a popular technique employed by compilers to alleviate the cost of branches. Guarded (predicated) execution also allows basic blocks to be enlarged [5][6][7]. However, methods like guarded execution suffer from the need to change the instruction set architecture (ISA), which poses a problem for backward compatibility. Another group of techniques relies on branch prediction. The machine speculates on the direction of the branch, and then executes the predicted path. One way of doing prediction is to profile the program and then to include a prediction bit in the branch instruction. This is referred to as static branch prediction. It suffers from the need to change the ISA like guarded executing, which is also done by the compiler. Dynamic branch prediction, on the other hand, records the outcome of the previous branches during the run of the program, and based on this statistic, predicts the outcome of the following branches. It has been shown that dynamic branch prediction achieves better performance than other methods [8].

In order to overcome the control dependency imposed by conditional branches using dynamic branch prediction, the direction of the branch and the target address need to be predicted. In most cases, the target address can be predicted accurately by utilizing a branch target buffer (BTB) — a cache that records the target address during the previous execution of the branch. A hit in the BTB ensures a good prediction in the case of a direct branch. The target address of indirect branches is harder to predict, but indirect branches constitute a small portion of the overall branches. This dissertation concentrates on predicting the branch direction. Moreover, this dissertation is limited to dynamic branch prediction. Those dynamic predictors might employ a static method, but pure static predictors are ignored.

### **1.3** Directions in Dynamic Branch Prediction

The first branch prediction schemes were static ones, where the branch prediction was hard-coded within the processor. The need for better branch prediction led to dynamic branch predictors, where branch prediction is determined by examining past behavior of the running program. The introduction of the bimodal structure was one of the first to utilize dynamic branch prediction, and it put the field of dynamic branch prediction on the research map [35][36]. Most processors in the past few years have contained a dynamic branch prediction module.

The introduction of two-level dynamic branch prediction [61][22] was a major step in the advancement of dynamic branch predictors. From that point, research in the field has

taken four different paths<sup>1</sup>. The first path attempted to improve on the two-level branch prediction scheme by incorporating different kinds of branch-related information into the dynamically collected statistics that decide the prediction. This will be referred to here as the 'scheme path'. Once it was understood that aliasing presented a major hurdle to correct prediction, numerous branch prediction structures that alleviate the aliasing problem were conceived. The second path of research we will refer to here as the 'aliasing path.' The third path, the 'hybrid path,' is based on the observation that different branches are best predicted by different kind of predictors. Predicting each branch with its respective best predictor, should enhance prediction accuracy. The fourth path is the one least studied. It involves a 'third-level of adaptivity'. This claims that different branches are better predicted by different configurations of the same branch prediction scheme, or that different phases of the program are better predicted by different configurations of the same branch prediction scheme. We termed this path the 'third-level' path, and we note that some papers also claim that the third-level path helps prediction by reducing aliasing.

The different branch prediction research paths have been kept separate in most cases. This is apparent in the lack of comparison between the different structures. For example, the *agree* [9] predictor which is designed to reduce aliasing was never compared to the

<sup>&</sup>lt;sup>1</sup> Using value prediction to predict branches can be viewed as a fifth path that research took, or it can be conceived of as part of the scheme path. In any case, in preliminary studies not presented here, we learned that most branches predicted well by incorporating value prediction are predicted just as well by other known predictors. We have therefore chosen not to address branch prediction using value prediction in this dissertation.

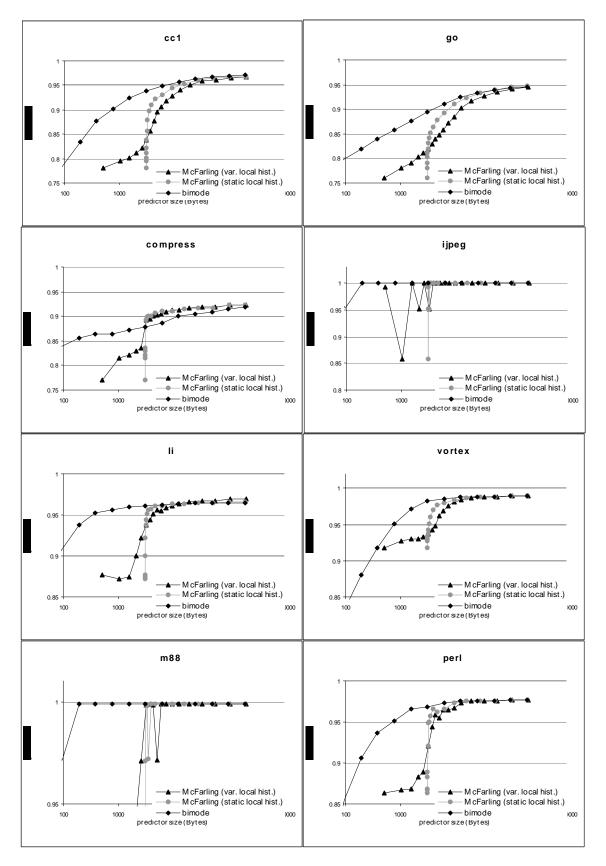

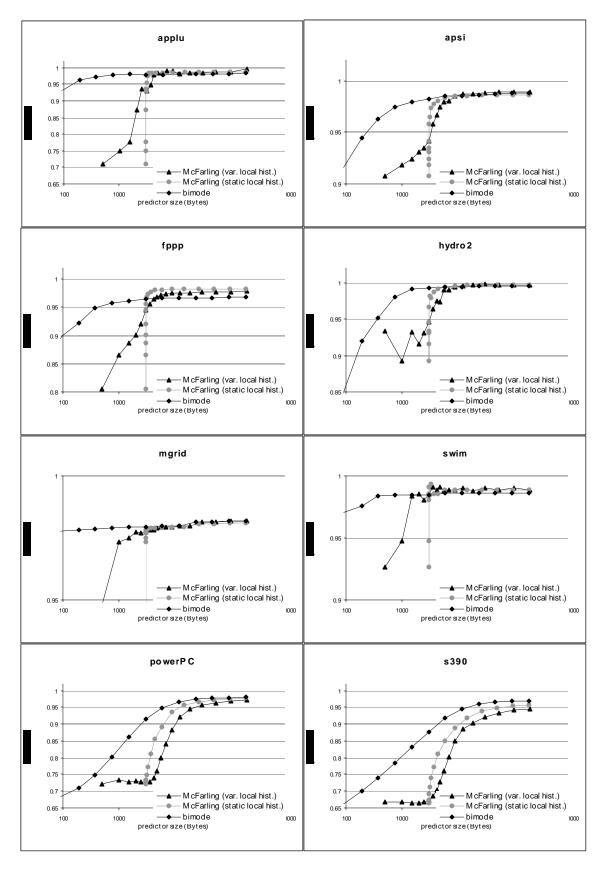

McFarling hybrid predictor [14]. The hybrid and aliasing paths were considered to be orthogonal, and a hybrid predictor, where each component reduces aliasing could be easily devised. Another example is the *bi-mode* predictor. When it was introduced, there was no mention of the classification method (discussed later) despite the striking structural similarity between the *bi-mode* and classification method. As a result of this line of thinking, there is very little knowledge regarding the interaction between the different paths.

Another problem becomes apparent when, in the rush to publish new branch prediction structures, researchers often failed to understand the reasons why the branch prediction structure worked. Instead, empirical results showing the superiority of the branch predictor have often been presented. These publications often lacked a simple limit study, which would have helped explain the underlying reasons why the branch prediction structure worked well. This omission could lead microarchitects to make poor choices of the branch predictor structure needed for a microprocessor.

### **1.4 Thesis Statement**

The need for accurate branch prediction is increasing as processors implement deeper and wider instruction fetching. Understanding why known branch predictor structures work is essential to the decision-making process of the micro-architect. It is also important to find feasible solutions to the branch prediction problem without ignoring constraints imposed by the underlying technology.

This dissertation presents a series of studies aimed at understanding why the different paths taken by dynamic branch prediction work, and what sorts of interaction have

existed between those paths. Presented here are results that show an unexpected amount of consolidates among the different paths taken in branch prediction. Those results, combined with a detailed analysis of previous studies and a look at trends in the underlying technology, lead to a set of criteria that produce an ideal model for a two-level dynamic branch prediction structure. Using those criteria, a new dynamic branch prediction structure is constructed that outperforms other known predictors from the other three paths. The microarchitect is presented with different configurations of the new predictor that fit different architectures and constraints.

### **1.5** Contributions of This Dissertation

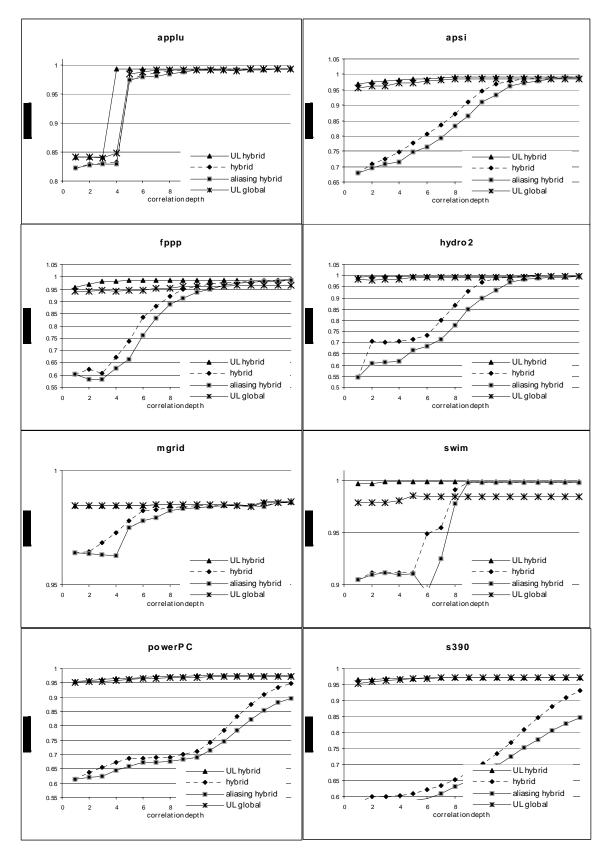

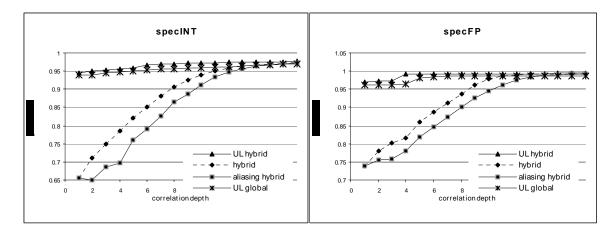

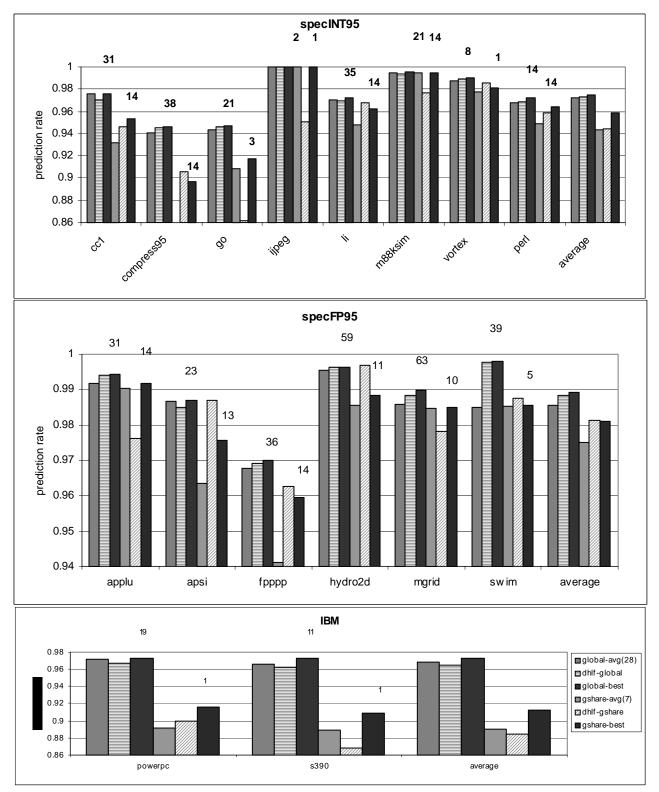

This dissertation makes several contributions to the field of branch prediction. First, it consolidates the hybrid and aliasing research paths in branch prediction by showing that most of the advantage gained in combining branch predictors is due to the selection mechanism's ability to reduce aliasing. The myth that a branch changes its best predictor during the execution of a program is refuted.

Second, this dissertation shows that a dynamic and a properly profiled static selection mechanism in hybrid predictors work well for the same main reasons. They both reduce aliasing. The prevailing factor in increasing prediction accuracy is aliasing reduction. The advantages and disadvantages of static and dynamic selection mechanisms are highlighted.

This dissertation also consolidates the third-level and aliasing research paths in the branch prediction field. Showing that most of the advantage gained by the third-level branch prediction structures is due to filtering, the third-level path is reduced to the

aliasing path. An important observation made here is that the same advantage depicted in the third-level path can be gained by picking the best history size configuration for each benchmark.

The lessons learned in this dissertation combined with a thorough analysis of the advantages and disadvantages of previously proposed branch prediction structures are used to draw a set of criteria that branch prediction structures should follow.

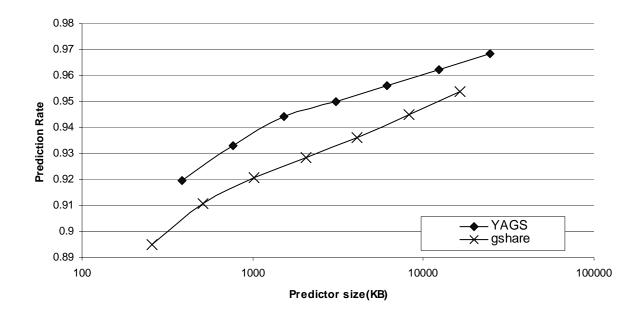

Drawing on this proposed set of criteria, a new branch prediction structures is proposed – YAGS. Utilizing the set of criteria allows YAGS to provide a significant performance improvement over existing structures at modest cost. A comparison between YAGS and previously proposed structures is presented.

A profile version of YAGS is introduced. This version makes better use of resources by allowing the branch bias to be determined statically, but might require some ISA change for certain architectures. Arguably, the best attribute of the profile version of YAGS is the ability to use it as a cascading predictor. A cascading predictor supplies a prediction in one cycle and a more accurate prediction after two cycles.

This thesis stresses the importance of a relevant limit study for research done on branch prediction. Most of the misconceptions/myths revealed in this dissertation resulted directly from the lack of a relevant limit study.

### **1.6 Organization**

This dissertation is organized as follows: Chapter 2 elaborates on the four different paths discussed above, and walks the reader through previous work performed in each path,

highlighting the pros and cons of each method. Chapter 3 discusses the experimental methodology and benchmarks used in the studies.

The next 3 chapters are each dedicated to one of the four paths discussed above. Chapter 4 presents a limit study on the different schemes belonging to the scheme path. Chapter 5 investigates what makes a hybrid predictor work well and evaluates the benefits of incorporating a hybrid predictor with a structure to reduce aliasing. Finally, Chapter 6 investigates the possibilities and limitations of the third-level path.

The remainder of the dissertation capitalizes on the conclusion of the previous chapters. First, Chapter 7 introduces a trend in micro-architecture that has generally been ignored within the branch prediction research community. Utilizing previous work and studies done earlier chapters, Chapter 8 summarizes the criteria necessary for a good dynamic branch predictor. This chapter goes on to introduce a predictor that capitalizes on these criteria to produce a better prediction compared to previous known predictors. Chapter 9 provides a summary and possible future work.

## **Chapter 2 - Previous Work**

## 2.1 Prediction Schemes

4This section walks through previous work done on the scheme path. While the first two subsections discuss one level rather than two level dynamic branch prediction schemes, they provide a foundation for the two-level branch prediction schemes discussed in the rest of this chapter.

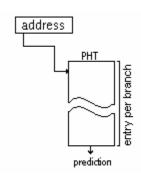

### 2.1.1 Bimodal

A table of two bit saturating counters (2bc) called a pattern history table (PHT), indexed by the branch address, was proposed early in the history of branch prediction research field [35][36]. This was one of the earliest dynamic schemes, and was later referred to as the bimodal scheme (Figure 2.1)<sup>2</sup>. The

2bc became the standard state machine and the bimodal branch predictor is frequently used as a "lower bound" branch

prediction benchmark against which to judge other branch prediction structures. In other words, a branch prediction scheme should not, under any circumstances, perform worse than the bimodal scheme. The bimodal attempts to predict the direction of a branch according to the past behavior of that branch during program execution. The 2bc

$<sup>^{2}</sup>$  The Figures in Section 2.1 show a diagram for the branch prediction scheme, although those schemes were introduced by specific branch prediction structures (see sec 4.1 for more).

provides some hysteresis so that one spurious prediction does not alter the next prediction. The branch should behave the same at least two times consecutively in order for the prediction to change. The bimodal can be seen as capturing the dynamic bias of the branch.

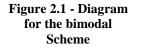

## 2.1.2 History Only Branch Predictor

A special case of the global branch prediction scheme is the history branch prediction scheme [44] (Figure 2.2). A table of 2bcs, indexed by a global history register, provides the prediction. History branch prediction schemes assume that a correlation exists between the last n branches and the current branch. Since the branch address is not involved in determining the prediction, the assumption is that the

Figure 2.2 Diagram for the history scheme

correlation works regardless of which branch is involved. In other

words, if the *n* branches preceding branch A and branch B behave the same, branches A and B will behave the same as well.

## 2.1.3 Two-level Adaptive Branch Predictors

A major milestone in the branch prediction research field was the introduction of the local two-level adaptive branch predictor [22]. It was shown to achieve up to 97% correct prediction accuracy on the early SPEC89 benchmarks. Later analysis has shown that the SPEC89 benchmarks are not hard to predict, even the bimodal predictor achieves over 90% prediction accuracy on the same set of benchmarks. The authors varied the associativity in the history table, and examined different state machines as the predictors in the PHT. This study found that the 2bc state machine performed the best among the

state machines tested. It is important to note that since that study, this assertion has not been challenged and the 2bc been accepted as a standard.

Three different classes of two-level adaptive branch predictors were identified [23], and a terminology based on taxonomy was proposed. For example, the term GAg indicates a global history register with a shared (global) PHT. The size of the PHT is 2<sup>history register size</sup> in this case. PAg indicates a table of history registers indexed by the program counter, where the PHT is shared. In contrast, PAp indicates a table of history registers, each of which has its own PHT. In practice, the PAp scheme can only be realized for very small history sizes. Separate work showed that PAp is the best predictor and GAg is the worst [24]. Notice, however, that GAg consumed the least amount of resources.

Today, the common opinion is that the global family of branch prediction can offer a better prediction accuracy than the local branch predictors for an integer workload because the branches in integer workloads tend to be highly correlated [25]. On the other hand, the local family of branch predictors offers better

prediction accuracy for scientific workloads.

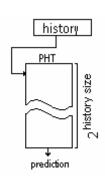

#### 2.1.4 Global Two-level Branch Predictors

The global two-level branch prediction scheme depicted in Figure 2.3 attempts to predict the branch based on the pattern of outcomes of the *n* preceding branches. When the program has a lot of if-then-else statements, the results are usually good. When the global branch prediction scheme was introduced arguments about program behavior, and snippets of high-level languages code were used to justify its merit [44]. In trace driven simulations it was shown that an implementation of the global branch prediction scheme performed better than a bimodal scheme implementation for the same amount of resources.

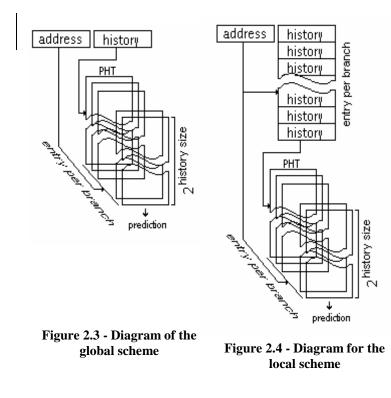

## 2.1.5 Local Two-level Branch Predictors

The local two-level branch prediction scheme shown in Figure 2.4 attempts to predict a specific branch according to the last *n* preceding outcomes of the predicted branch. A common notion is that local schemes are better than global schemes at predicting branches in scientific code. This is attributable to the presence of a large number of loops in scientific code. Having a per branch history register is beneficial for loop constructs.

## **2.1.6 Path-Based Branch Predictors**

The correlated schemes described thus far record the branch outcome in the history register. The information reflecting which branches resulted in those outcomes, is therefore lost. The inclusion of this information might be beneficial for prediction accuracy. If the last n branches preceding branch A resulted in a certain pattern, it is not

necessarily the case that when a different set of branches precedes branch *A* form the same pattern, branch *A* will behave the same.

To rectify this loss of information problem it was suggested that the addresses along the path leading to the branch be factored into the information stored in the history register [26]. Using the branch address path explicitly captures information about the addresses of the branches leading to the one being predicted, and implicitly captures the outcomes of the branches on that path as well. The mechanism proposed is a static mechanism, which is performed by software.

The next development was a dynamic path-based branch prediction mechanism [26]. This structure is similar to the global two-level branch prediction structure. It was observed that when a branch target address falls inside the branch's basic block, the branch outcome is lost in the history register, because the path leading to the branch is identical whether or not the branch was taken. This led to the idea of using the branch target address, instead of the branch address, as the information stored inside the history register.

One weakness of path-based correlation in dynamic branch predictors is that the history register needs to hold a lot of information, typically a word per branch, much more than the one bit per branch of competing schemes. Since the most important information are the least significant bits (LSBs) of the branch address, only a small portion of the address is pushed into the history register.

Path-based prediction schemes resulted in very similar prediction accuracy as did global two-level branch prediction structures of the same size. However, it was noted that the

path-based branch prediction scheme, while requiring about the same amount of resources, used less branches for the history than the global branch prediction structure.

### 2.1.7 Other Schemes

As a result of the work mentioned so far researchers observed that capturing more branch-related information improves the prediction potential of the branch prediction scheme. An attempt was made to identify the branch by the branch address, global history, and path-based history [46]. Information related to the above is "exclusive-or" (xor) together and used as the index to the PHT. A slightly better prediction accuracy was accomplished than the *gshare* scheme. No limit study was performed to assess the potential of such a scheme, and the gain in performance is so minute that it could be due to experimental error rather to the inherent capability of the prediction scheme.

### 2.1.8 Summary

A trend was established that the more information that is recorded about a branch to distinguish it from other branches, the better the prediction accuracy that will be achieved for that branch. However, more information entails more hardware dedicated to the branch prediction structure. Therefore, it might be the case that the best branch prediction scheme available does not necessary result in the most cost-effective branch prediction structure.

## 2.2 Aliasing in Global Predictors

#### 2.2.1 The Problem

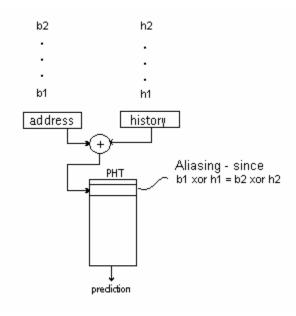

The main problem that causes prediction degradation in global branch prediction structures is aliasing [15][16] (Figure 2.5). Aliasing occurs when two indices, typically formed from history and address bits, map to the same entry in the PHT. Since the information stored in the PHT entries is either "taken" or "not taken," two aliased

Figure 2.5 – Aliasing in the gshare predictor

indices whose corresponding information is the same, will not result in mispredictions. We refer to this as neutral aliasing. On the other hand, two aliased indices with contradictory entries might interfere with each other and result in a misprediction. We call this destructive aliasing.

## 2.2.2 Aliasing Reducing Branch Prediction Structures

A lot of work has been done to reduce aliasing in the PHT. In what follows, we describe some of the more notable structures and highlight their strengths and weaknesses.

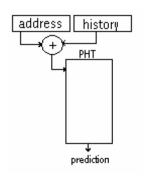

## 2.2.2.1 Gshare

The first structure to address the aliasing problem in twolevel adaptive branch predictors was *gshare* [14] (Figure 2.6). The observation that the usage of the PHT entries is not uniform when indexed by concatenations of the global history and the branch address, led to idea of using the xor

function instead of concatenation to more evenly use the

Figure 2.6 – Diagram for the gshare structure

entries in the PHT. Moreover, the usage of the xor function enables more history bits to be incorporated into the prediction and as a result, enables the predictor to increase its correlation. Detailed studies have shown that this yields a slight advantage [19].

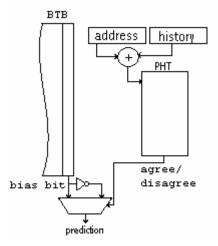

## 2.2.2.2 Agree Predictor

The *agree* predictor displayed in Figure 2.7 assigns a biasing bit to each branch in the BTB according to the branch direction just before it is written into the BTB [9]. The PHT information is then changed from "taken" or "not taken" to "agree" or "disagree" with the prediction of the biasing bit. The idea behind the *agree* predictor is that most

branches are highly biased to be either taken or not taken and the hope is that the first time a branch is introduced into the BTB it will exhibit its biased behavior. If this is the case, most entries in the PHT will "agree," so that if aliasing does occur it will more likely be neutral aliasing, which will not result in a misprediction. This observation suggests redundancy in the PHT.

Figure 2.7 – Diagram for the agree structure

A patent registered by HP [67] preceded the *agree* predictor in taking advantage of a branch's biased behavior to reduce destructive aliasing by replacing destructive aliasing with neutral aliasing. The *agree* predictor considerably reduces destructive aliasing. However, there is no guarantee that the first time a branch is introduced to the BTB its behavior will correspond to its bias. When such cases occur, the biasing bit will stay the same until the branch is

replaced in the BTB by a different branch. Meanwhile, it will pollute the PHT with "disagree" information. Also, there is still aliasing occurring between instances of a branch that do not comply with the bias, and instances where the branch does comply with the bias. When a branch is not cached in the BTB, no prediction is available.

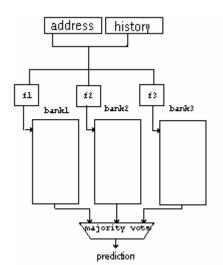

### 2.2.2.3 Skew Predictor

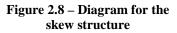

The *skew* branch predictor seen in Figure 2.8 is based on the observation that most aliasing occurs not because of a small PHT size, but because of a lack of associativity in the PHT. In other words, the major contributor to aliasing is conflict aliasing and not capacity aliasing. The best way to deal with conflict aliasing is to make the PHT set-associative, but this requires tags and is not cost-effective. Instead, the *skew* predictor emulates associativity using a special skewing function [11].

The *skew* branch predictor splits the PHT into three equal banks and hashes each index to 2bc in each bank using a unique hashing function per bank (f1, f2 and f3). The prediction

is made according to a majority vote among the three banks. If the prediction is wrong all three banks are updated. If the prediction is correct, however, partial updating will occur, which means that only the banks that made a correct prediction will be updated.

The skewing function should have inter-bank dispersion. This is necessary in order to make sure that if a branch is aliased in one bank, it will not be aliased in the other two banks. This ensures that the majority vote will produce a un-aliased prediction. The reasoning behind partial updating is that if a bank gives a misprediction when the other two give correct predictions, the bank with the misprediction probably holds information

Figure 2.9 – Diagram for the bimode structure

belonging to a different branch. In order to maintain the accuracy of the other branch, this bank is not updated.

The *skew* branch predictor tries to eliminate all instances of aliasing and thus all destructive aliasing. Unlike the other methods, it tries to eliminate destructive aliasing between branch instances that obey the bias and those that do not. However, to achieve this, the *skew* predictor stores each branch outcome in two or three banks. This redundancy of 1/3 to 2/3 of the PHT size creates capacity aliasing by putting more information in the PHT, but eliminates by a greater degree conflict aliasing, resulting in a lower misprediction rate. However, the increase in size slows warm-up on context switches.

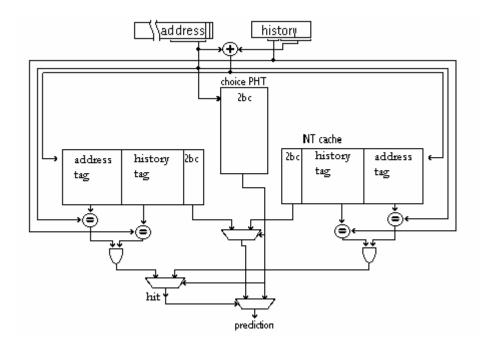

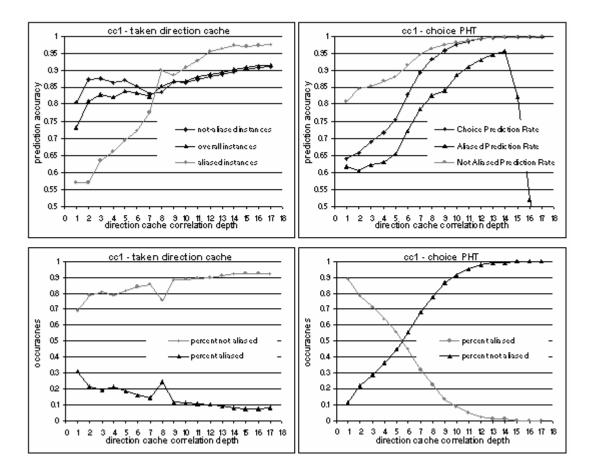

#### 2.2.2.4 Bi-Mode Predictor

The *bi-mode* predictor shown in Figure 2.9, similar to the *agree* predictor, replaces destructive aliasing with neutral aliasing [12]. The *bi-mode* PHT gets split into three even parts. One of the parts is the choice PHT, which is just a bimodal predictor (an array of 2bcs) with a slight change in the updating procedure. The other two parts are direction PHTs; one is a "taken" direction PHT and the other is a "not taken" direction PHT. The direction PHTs are indexed by the branch address xored with the global history. When a branch is present, its address points to the choice PHT entry, which in turn chooses between the "taken" and "not taken" direction PHTs. The prediction of the direction PHT serves as the prediction. Only the direction PHT chosen by the choice PHT serves as the prediction. Only the direction PHT chosen by the choice PHT is updated. The choice PHT is normally updated too, but not when it gives a prediction that contradicts the branch outcome and the direction PHT chosen gives the correct prediction.

During operation, branches that are biased to be taken will have their predictions in the "taken" direction PHT, and branches that are biased not to be taken, will have their predictions in the "not taken" prediction PHT. So at any given time most of the information stored in the "taken" direction PHT entries is "taken" and any aliasing is more likely not to be destructive. The same phenomenon happens in the "not taken" direction PHT. The choice PHT serves to dynamically choose the branches' biases. In contrast to the *agree* predictor, if the bias is incorrectly chosen the first time the branch is introduced to the BTB, it is not bound to stay that way while the branch is in the BTB and pollute the direction PHTs with destructive aliasing. It should be noted, however, that the choice PHT takes a third of all PHT resources just to dynamically determine the

bias. It also fails to solve the aliasing problem between instances of a branch that do not agree with the bias and instances that do, because both are stored in the same direction PHT.

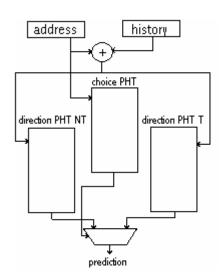

#### 2.2.2.5 Filter Mechanisms

Reducing the amount of necessary information stored in the PHT is the main point of *filter* mechanisms [10]. The idea is that highly biased branches can be predicted with high accuracy using just one bit. Easy-to-predict branches are filtered out of the PHT by a combination of a bias bit and a saturating counter for each BTB entry, which can be seen in Figure 2.10. When a branch is introduced to the BTB, the bias bit is set to the

the counter is initialized. When every branch instance is resolved, if the direction of the branch is the same as the bias bit, the counter is incremented. If not, the counter is zeroed and the bias bit is toggled. A branch is predicted using the PHT if the counter is not saturated. If the

counter is saturated, it means that the branch is

direction of the branch when it is resolved and

# Figure 2.10 – Diagram for the filter mechanism structure

highly biased in the direction indicated by the bias bit, and therefore that the bias bit is used as a prediction. In this case, when the counter is saturated, the PHT is not updated with the branch outcome – the saturated counter filters this information from the PHT. The size of the counter has to be tuned to the size of the PHT. If the PHT size is large, the amount of filtering needed is small, and therefore the size of the counters should be large. When a branch is first introduced in the BTB, the counter is initialized. It was found that it is best to initialize the counter to its maximum value so that the filtering will start to work immediately. If the branch is not highly biased, the bias bit will flip fairly quickly and the counter will be zeroed. On the other hand, if the counter is initialized to zero and the branch is highly biased, it will take time for the filtering mechanism to start working and the PHT will be polluted in the meantime. The *filter* mechanism attempts to eliminate all aliasing instances by considerably reducing the amount of information stored in the PHT. However, this mechanism has difficulty predicting instances of highly biased branches, which do not comply with the bias. Due to filtering, as the PHT size increases the predictor will never reach the full potential of the global scheme that it implements.

#### 2.2.3 Summary

The branch prediction structures discussed above use three techniques to reduce aliasing. The first takes advantage of the underlying information stored in the PHT, and converts destructive aliasing to neutral aliasing as a means of improving prediction. The second method to remove aliasing is associativity. Classical associativity (by an inclusion of tags) was determined as not cost-effective. Pseudo associativity, a different way to achieve the same effect, was devised. Third, filtering information selectively allocates greater resources for the more important information.

Those advantages come at a cost. Most of the structures carry some redundancy. For example in the *skew* predictor, the same information is stored in up to three different counters. This redundancy can exacerbate the negative effects of a cold start. In all the

above branch prediction structures, certain types of aliasing are neglected or some branches' accuracy is jeopardized.

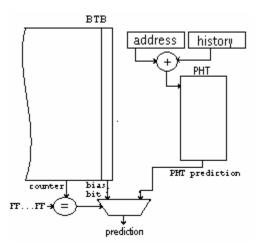

## 2.3 Hybrid Predictors

The notion that a certain kind of predictor better predicts one class of branches, while a different kind of predictor better predicts a different class of branches led to the idea of combining branch predictors. This class of branch predictors are known as the hybrid branch predictors.

Figure 2.11 depicts a general drawing of a

hybrid branch predictor. A selection mechanism is used to choose between two or more branch predictor structures to be used for the prediction of a specific branch instance.

## 2.3.1 Hybrid Branch Predictors

The first hybrid structure suggested combining the *bimodal* and *gshare* structures [14]. The selection mechanism is a table of 2bcs and is very similar to a *bimodal* structure. The selection counter is updated only if the prediction given by the two predictors is different. If only the *bimodal* predictor gives a correct prediction, the counter is decremented. The counter is incremented if only the *gshare* structure gives a correct prediction. If both predictors either give a correct or an incorrect prediction, the selection counter is not updated. Consequently, state 0 and 1 of the 2bc state machine entails a selection of the *bimodal* predictor, while state 2 and 3 result in the use of the *gshare*

structure for prediction purposes. This hybrid structure was shown to outperform all other single schemes known at that time.

It is interesting to observe the percentage of times each predictor was used. For most benchmarks, the *bimodal* was used significantly more than the *gshare* scheme. This might indicate that the this hybrid predictor performs well because it filters the easy-to-predict branches out of the *gshare* structure, and not due to the fact that each of its components better predict a different class of branches. This way, a small amount of resources are used to predict the easy-to-predict branches, leaving the majority of resources to predict the hard to predict branches.

The same study proposed that a hybrid predictor combine *gshare* and PAs structures. This hybrid predictor is known as the McFarling predictor, named after the author of the paper. The combination of global and local schemes outperformed the bimodal-*gshare* hybrid predictor only for predictors larger than 16KB. The simulations were done on the SPEC89 benchmark suite that is notorious for a small branch signature. A branch classification method was suggested to enable a branch to be predicted by a predictor best suited to predict it [13]. Branch classification was based on the observation that branches that are highly biased can be predicted well with a short history predictor, while the rest of the branches typically require a longer history. This observation led to a combination of predictors with different history lengths. The classification predictor outperformed the *gshare* scheme. The selection mechanism for the classification predictor is done via profiling.

The classification predictor does not clearly belonging to just one of the research paths. It can be seen instead as a hybrid predictor, and is therefore discussed in this section, but

can also be seen as belonging to the 'third-level' path. The two components and a selection mechanism associate it with the hybrid path. On the other hand, the two different correlation depths of the same branch prediction scheme associate it with the third-level path.

As an alternative selection mechanism to the *bimodal* structure, the two-level structure was proposed [48]. The hybrid predictor under examination was the McFarling predictor. The assumption was that since the two-level branch predictor could better predict the direction of branches, it would also be better able to select between the different branch prediction structures of the hybrid predictor. It was shown that using a two-level global structure to select between the local and global schemes yielded a very small improvement. However, this was not shown to be cost-effective, and the results were far from the ideal oracle selection mechanism.

A conglomeration of predictors was incorporated into the multi-hybrid predictor [49]. The multi-hybrid consists of the bimodal, two variations of the global predictor, and two variations of the local predictor, a loop predictor, and a static predictor. It was shown to have a slightly better prediction accuracy than the bimodal-global and the McFarling hybrid predictors when tested under context switching. No explanation was given as to why those particular predictors were chosen, or why there was a need for more than one global and local predictor. The comparison was not done against the original McFarling predictor, but rather against a revised version of it, where the selection mechanism was tied to the BTB. As the size of the predictor grew, the selection mechanism size could not grow because it was tied to the BTB. This gave an unfair advantage to the multi-hybrid predictor because its elaborate selection mechanism had to be tied to the BTB.

#### 2.3.2 Selection Mechanisms

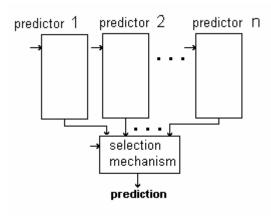

Selection mechanisms for hybrid branch predictors followed the same line of development as did single scheme branch predictors. The classes consist of a static selection mechanism, a dynamic per branch selection mechanism, and finally, a two-level selection mechanism as discussed above.

Possibly the only contribution of the multi-hybrid predictor is its selection mechanism [49]. Before the multi-hybrid hybrid predictors consisted of only two separate branch predictor components. The multi-hybrid consists of a selection mechanism that can select between an arbitrary numbers of predictors.

This selection mechanism consists of multiple 2bc per entry. The exact number of 2bc is determined by the different components of the multi-hybrid predictor. The predictor to be used is determined by the 2bc with the value of three in it. If multiple 2bcs in the selector entry have the value three, a priority encoder is used to determine which predictor to use. Once the branch is resolved, the 2bc, which corresponds to the predictors giving a correct prediction, is incremented. If one of the predictors, which had the value of 3, was correct, all 2bc that would correspond to all other predictors are decremented.

## 2.4 Third-level of Adaptivity

It was suggested that having the depth of correlation (i.e. the size of the BHR in the global scheme) adapt to the program execution or branch behavior could improve branch prediction. This observation spawned the third-level of adaptivity path.

# 2.4.1 Third-level of Adaptivity Structures

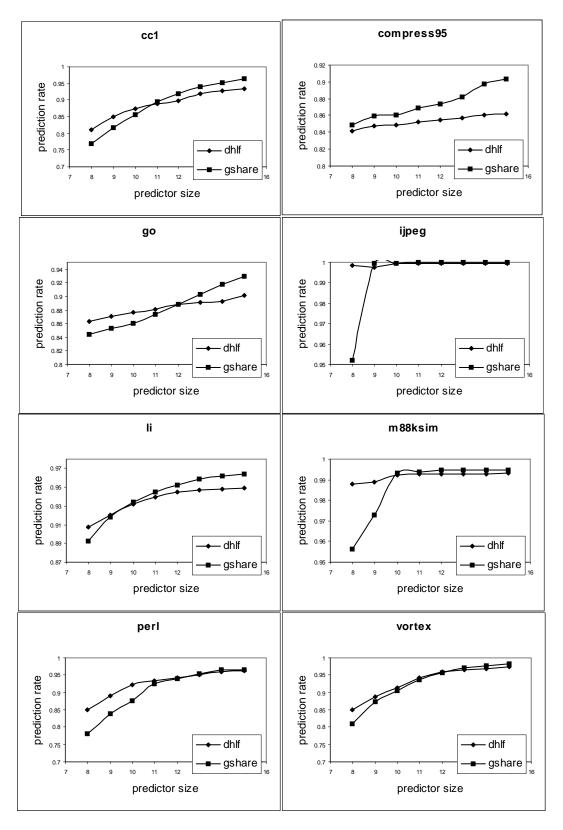

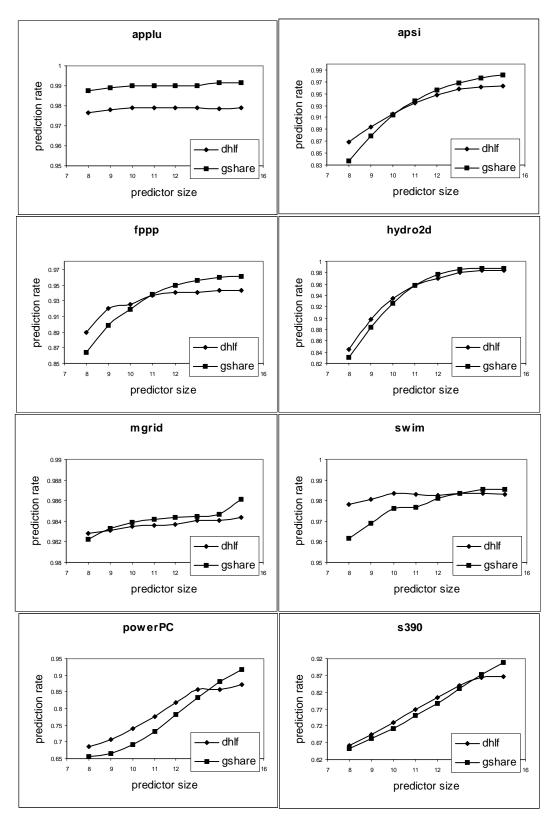

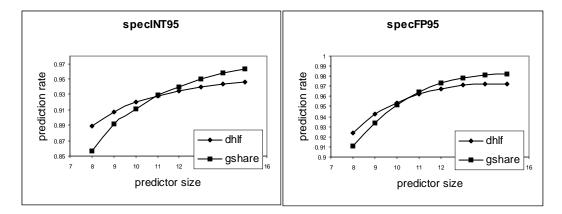

The first structure suggested was the Elastic History Buffer (EHB) [20]. The EHB took branch classification [13] to a finer granularity. Instead of having the option of choosing between two lengths of history register, the EHB gave the option for each branch to use its optimal history length. Moreover, it facilitated filtering of some easy-topredict branches from the PHT, by using a profiled bias bit instead of the PHT. Filtering the easy-to-predict branches from the PHT reduces aliasing, which in turn increases prediction accuracy. Profiling determines the history length to use for each branch, and requires a modification to the ISA. As in all profiling, there is no guarantee that the data collected during profiling is representative of the actual branch behavior during execution. The EHB structure operates under the assumption that there is an optimal history size per branch without investigating the possibility that a branch could have a different optimal history size in different phases of the program execution. The Dynamic History Length Fitting (DHLF) dynamically determines the size of the history size used [21]. DHLF divides the dynamic stream of branches into sub-streams termed steps of several thousands instructions. In every other step, the length of the history register is evaluated and might change if the evaluation method finds the change beneficial. The evaluation is done only every other step to omit the effects of cold starts from getting in the way of the evaluation method. The step was set to 16K branch instructions.

In another development, a similar idea was entertained, but instead of using branch outcomes, the variable length path branch predictor used target address in the history register [54]. Profiling was used to determine how much history to use for each static

branch. The predictor was shown to be especially useful with indirect branches, but it was not compared against the EHB [20].

### 2.4.2 Selection Mechanisms

Similar to selection mechanisms present in hybrid predictors, selection mechanisms for third-level of adaptivity can be divided into dynamic and static selection mechanisms. While a hybrid static selection mechanism usually only needs one bit of information in the ISA's branch instructions, the presence of third-level of adaptivity requires log2 bits of the BHR size.

Dynamic selection mechanism was not attempted on per branch granularity as in the hybrid dynamic selection mechanism. Instead, the dynamic BHR size is on program granularity and is examined and changed every certain number of instructions [21].

# Chapter 3 - Experimental Methodology and Benchmark Description

# 3.1 Experimental Methodology

4Throughout this work, trace driven simulations have been used to evaluate different branch prediction schemes and structures. For simplicity's sake, most simulations predict and resolve a branch, and update the branch predictor before fetching the next branch. Although this approach sacrifices some accuracy because not always the branch outcome can be used to update the history register before the next branch is fetched and predicted, studies have shown that such simulations provide a tight estimation to finer, cycle level, simulations [55][56].

| Scheme          | Description                                                                                                                                | Design Space                 | Unlimited Size                                                   |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------------------------------------------|--|

| Bimodal         | A table of 2bc accessed by the branch address                                                                                              | None                         | # branches                                                       |  |

| History         | A table of 2bc accessed by a global history register                                                                                       | History size<br>from 1 to 64 | 2 <sup>history size</sup>                                        |  |

| Global          | A table of 2bc accessed by the<br>branch address and a global history<br>register                                                          | History size<br>from 1 to 64 | # branches x 2 <sup>history size</sup>                           |  |

| Local           | A table of history registers<br>accessed by the branch address.<br>The result is used with the branch<br>address to access a table of 2bc. | History size<br>from 1 to 64 | Number of branches x<br>(2 <sup>history size</sup> + # branches) |  |

| Path-<br>Branch | Same as global but the information<br>in the history register is previous<br>branch addresses and not their<br>outcomes                    | History size<br>from 1 to 64 | # branches x<br>2 <sup>history size x word size</sup>            |  |

| Path-<br>Target | Same as global but the information<br>in the history register is previous<br>branch target addresses and not<br>their outcomes             | History size<br>from 1 to 64 | # branches x<br>2 <sup>history size x word size</sup>            |  |

All through this dissertation extensive limit studies of branch prediction schemes and combinations of multiple schemes were performed. Table 3.1 depicts the different branch prediction schemes considered in the course of this work. Table 3.1 gives a short description, the design space, and the size of the predictor if no size restriction is imposed for each branch prediction scheme.

| typedef struct hybridStruct {      |  |  |  |  |

|------------------------------------|--|--|--|--|

| unsigned long long globalPred;     |  |  |  |  |

| unsigned long long localPred;      |  |  |  |  |

| unsigned long long pathBranchPred; |  |  |  |  |

| unsigned long long pathTargetPred; |  |  |  |  |

| unsigned long long historyPred;    |  |  |  |  |

| unsigned int bimodalPred;          |  |  |  |  |

| unsigned int baddr;                |  |  |  |  |

| unsigned int btarget;              |  |  |  |  |

| unsigned int taken;                |  |  |  |  |

| } hybridElement;                   |  |  |  |  |

|                                    |  |  |  |  |

#### Figure 3.1 – Hybrid Trace Structure

To facilitate such processor and memory intensive simulations, a new trace termed the hybrid trace was created for each benchmark. Each entry in the hybrid trace contains predictions for every type of scheme for multiple correlation depth,

ranging from 0 to 63. Figure 3.1 depicts the structure used for each entry in the hybrid trace. For example, the  $3^{rd}$  bit in the global variable represents the prediction a global branch prediction scheme made with a correlation depth of 3.

#### 3.2 Benchmarks' Description

This dissertation conducted studies on a set of 16 benchmarks. Eight of these are SPECINT95 and six are SPECFP95. Two more of these benchmarks, the s390 and the PowerPC, were provided by IBM. Table 3.2 lists the characteristics of all benchmarks. The SPEC95 benchmark suite represents the typical workload a computer might expect. The IBM traces are of database applications, and are interesting for their large branch footprints compared to the SPEC95 traces.

|            | SPECFP95        |                  |                   |                  |  |

|------------|-----------------|------------------|-------------------|------------------|--|

|            | Regular Set     |                  |                   | Train Set        |  |

| Benchmark  | Static Branches | Dynamic Branches | Indirect Branches | Dynamic Branches |  |

| applu      | 1498            | 31,843,665       | 291               | 17,867,895       |  |

| apsi       | 3006            | 41,370,429       | 581               | 126,828,375      |  |

| fpppp      | 1089            | 14,550,247       | 188               | 4,540,419        |  |

| hydro2d    | 2128            | 133,675,998      | 438               | 238,609,181      |  |

| mgrid      | 1449            | 13,901,572       | 274               | 208,359,079      |  |

| turb3d     | 1626            | 52,785,185       | 305               | 238,609,181      |  |

|            | SPECINT95       |                  |                   |                  |  |

|            | Regular Set     |                  | Train Set         |                  |  |

| Benchmark  | Static Branches | Dynamic Branches | Indirect Branches | Dynamic Branches |  |

| gcc        | 13,763          | 49,193,611       | 3317              | 52,277,032       |  |

| compress95 | 495             | 196,295,114      | 49                | 6,145,300        |  |

| go         | 7401            | 147,352,115      | 3278              | 80,274,927       |  |

| ijpeg      | 2760            | 71,798,033       | 478               | 173,576,042      |  |

| li         | 1701            | 233,260,230      | 315               | 41,801,717       |  |

| m88ksim    | 1646            | 160,658,276      | 343               | 20,530,078       |  |

| perl       | 3443            | 191,717,635      | 647               | 2,144,594        |  |

| vortex     | 7581            | 158,719,765      | 765               | 238,609,181      |  |

|            | IBM             |                  |                   |                  |  |

|            | Regular Set     |                  |                   | Train Set        |  |

| Benchmark  | Static Branches | Dynamic Branches | Indirect Branches | Dynamic Branches |  |

| s390       | 21,727          | 2,360,458        | 631               | 1,360,459        |  |

| powerpc    | 16,710          | 32,497,139       | N/A               | 19,000,001       |  |

#### Table 3.2 - Benchmark Characteristics

Table 3.3 shows the datasets used as inputs for the different benchmarks. Each SPEC95 benchmark has two datasets. The first is used in most simulations, while the test dataset is used to obtain profiling information when appropriate. The IBM benchmarks were provided as traces and without an accompanying test trace. As a result, whenever profiling information was needed, the first half of the trace was used to obtain profiling and the second half was used to obtain simulations statistics. The reader is therefore

advised to place less confidence in results that used those traces in studies that include profiling.

| Benchmark | Description                                                                     | Training<br>Set | Test Set         |

|-----------|---------------------------------------------------------------------------------|-----------------|------------------|

| gcc       | GNU C compiler version 2.5.3                                                    | stmt.i          | jump.i           |

| go        | Computer program playing go                                                     | short.in        | 2stone9.in       |

| compress  | Data compression program                                                        | prof.in         | test.in          |

| ijpeg     | Image compression program                                                       | vigo.ppm        | speicmun.ppm     |

| xlisp     | XLISP interpreter                                                               | 7queen.lsp      | train.lps        |

| vortext   | Object-Oriented database                                                        | vortex.35M      | vortes.in        |

| M88ksim   | Motorola 88100 simulator                                                        | dhry.test.big   | dcrand.train.big |

| perl      | Train interpreter                                                               | primes.pl       | scrabbl.pl       |

| applu     | Solves matrix system with pivoting.                                             |                 |                  |

| apsi      | Calculates statistics on temperature and pollutants in a grid.                  |                 |                  |

| fppp      | Performs multi-electron derivatives.                                            |                 |                  |

| hydro2    | Hydrodynamical Navier Stokes<br>equations are used to compute<br>galactic jets. |                 |                  |

| mgrid     | Calculation of a 3D potential field.                                            |                 |                  |

| swims390  | Solves shallow water equations                                                  |                 |                  |

| S390      | N/A                                                                             | N/A             | Not specified    |

| powerPC   | N/A                                                                             | N/A             | Not specified    |

Table 3.3 – Benchmark description and datasets

The studies in this dissertation were conducted using the SPEC95 benchmark suite. As the name implies, those benchmarks were available in 1995. A newer version of the SPEC is available – SPEC2000. However, simulations done on the newer benchmarks revealed no indication of harder to predict branches, nor a larger number of static branches. For the most part, it seems that SPEC2000 is just a revised version of the benchmarks present in the SPEC95 suite. We therefore continued conducting the studies in this dissertation with the SPEC95 as we did before the SPEC2000 became available.

#### **3.3 Performance Metrics**

The studies in this dissertation are evaluated using the metric of branch prediction accuracy. The main disadvantage of this metric is the inability to directly convert improvement in branch prediction accuracy to improvements in overall system performance. Overall improvement in system performance can be better achieved by using a metric like Cycles Per Instruction (CPI). Previous studies have shown that a strong correlation exists between branch prediction accuracy and overall system performance [57][58][59]. As a result, the disadvantage of using branch prediction accuracy as a guide to system performance is minimal.

There are numerous advantages of using branch prediction accuracy as a metric. Using prediction accuracy detaches the evaluation of the branch predictors' performance from system dependent parameters, such as the misprediction penalty. Moreover, it facilitates concentration on improving the branch prediction mechanism without the interference of other potential system bottlenecks, such as cache misses.

In summary, using branch prediction accuracy enables concentration on global factors in branch prediction that will facilitate a better branch predictor in every system.

### **3.4 Results Presentation**

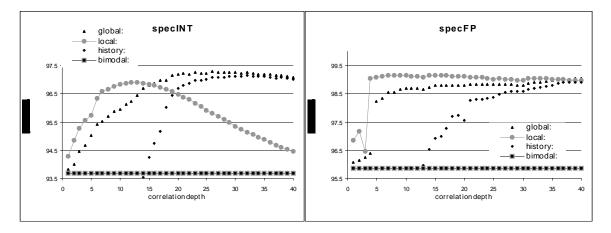

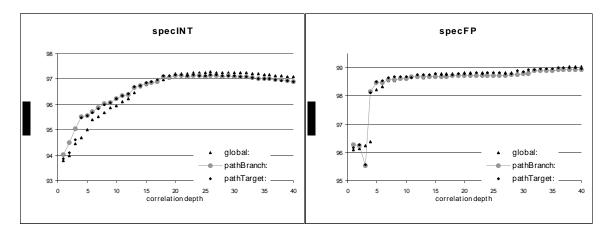

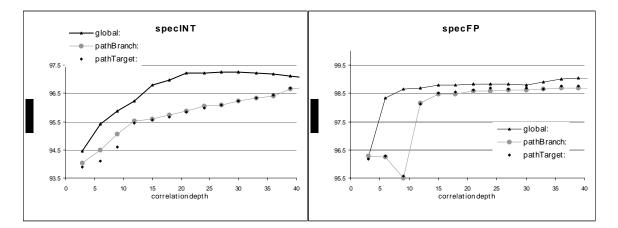

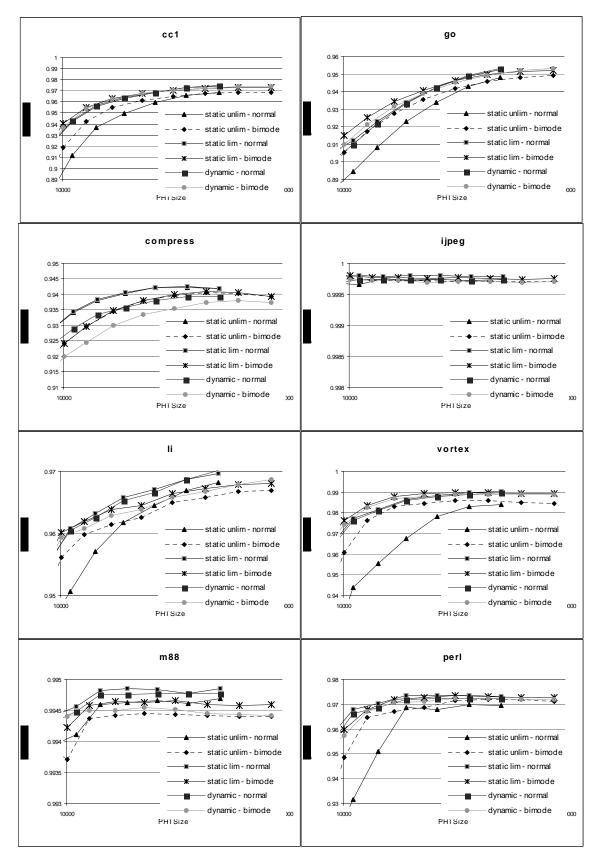

This dissertation presents 20 possible graphs: the SPEC95 benchmarks (16 different benchmarks), the PowerPC benchmark, the S390 benchmark, the arithmetic average of the SPECINT95, and the arithmetic average of the SPECFP95.

# **Chapter 4 - The Scheme of Schemes**

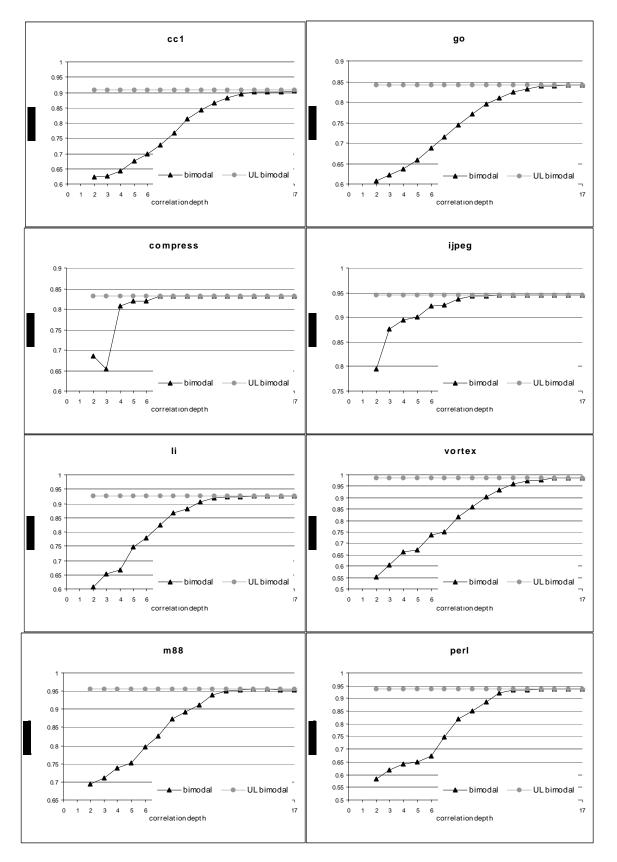

#### 4.1 The Difference Between Schemes and Structures

4Past work on branch prediction has failed to distinguish clearly between branch prediction schemes and branch prediction structures—in fact, those words have been used interchangeably. A branch prediction structure is the mechanism that implements the algorithm, which is the branch prediction scheme. For example, the global branch prediction mechanism described in Section 2.2.4 is implemented by many branch prediction structures (Sections 2.2.2.1 - 2.2.2.5). If a branch prediction structure is not limited in resources, it will reach the branch prediction scheme's peak potential. As a result, with no limits on resources, all branch prediction structures implementing the same branch prediction scheme will achieve the same prediction accuracy. The distinction between branch prediction structures and schemes is instrumental in choosing an appropriate branch predictor. Regardless of how many resources will be dedicated to the *gshare* structure, the *gshare* structure will never surpass the prediction potential of the global branch prediction scheme. It is important to be aware of the global scheme's limits. If a certain branch prediction structure approaches the prediction limits of the branch prediction scheme, Amdahl's law dictates that work should be directed towards finding new and improved branch prediction schemes, as opposed to finding new branch prediction structures that will approach the limits of the branch prediction scheme.

Throughout this dissertation, this convention of distinguishing between branch prediction structures and branch prediction schemes is followed. Next, the limits of known branch prediction schemes are studied.

#### **4.2** Limits on Branch Prediction Scheme

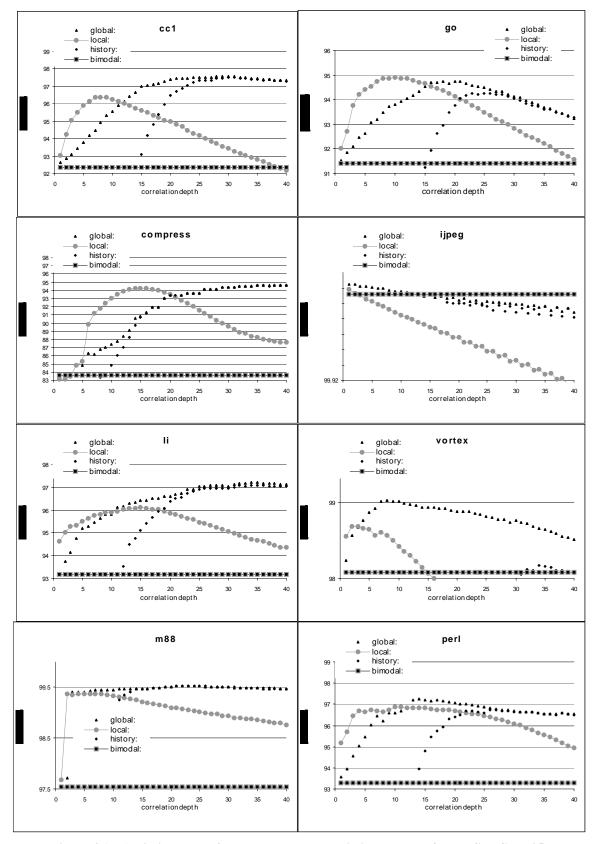

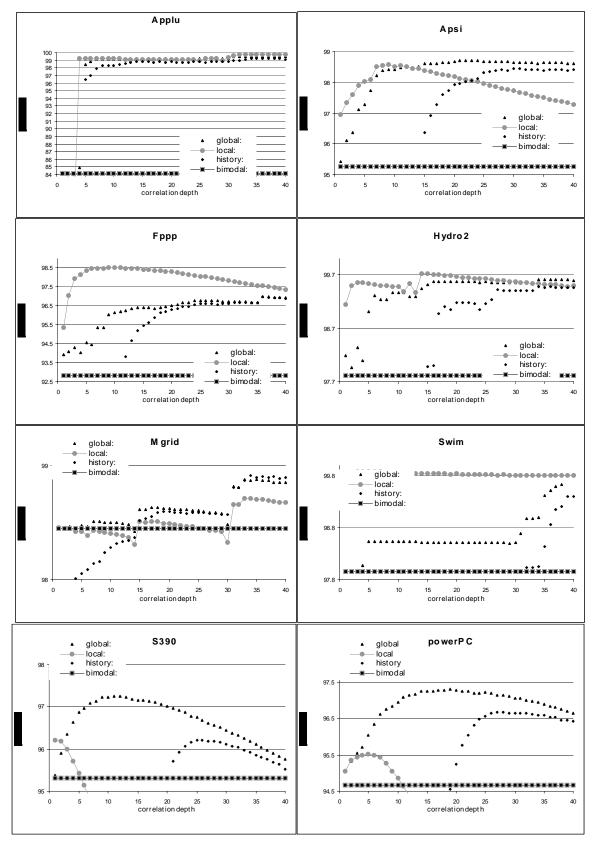

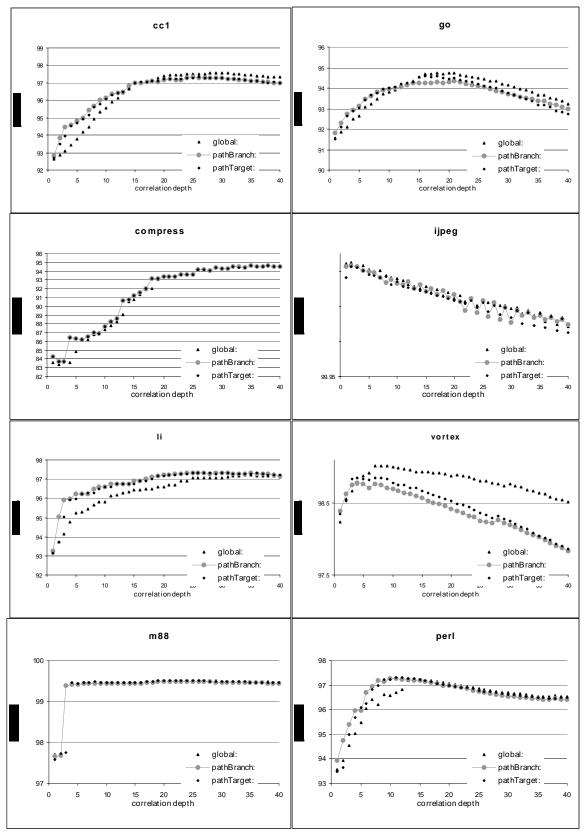

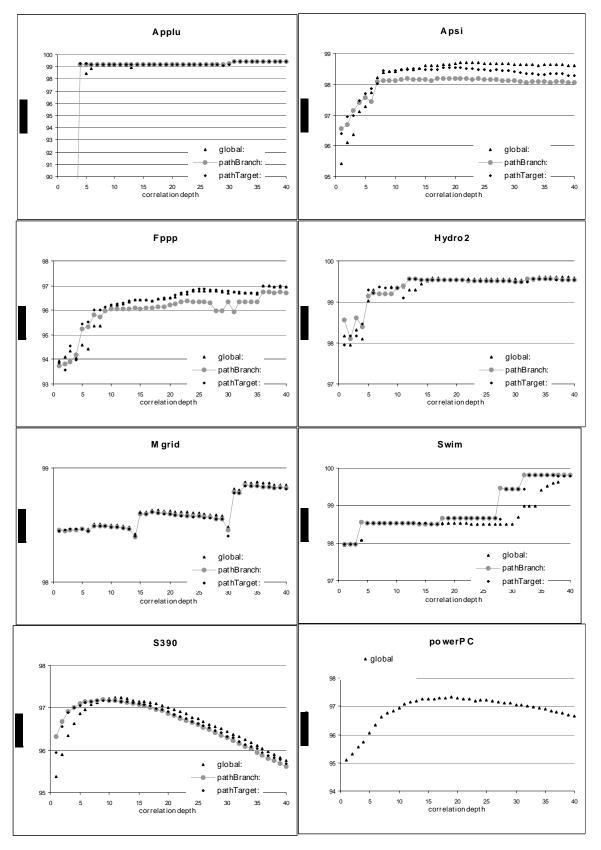

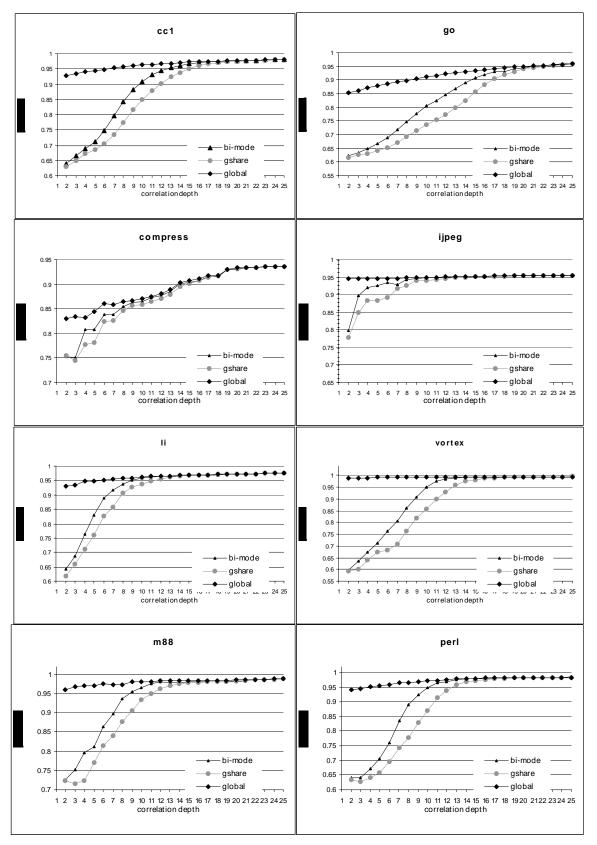

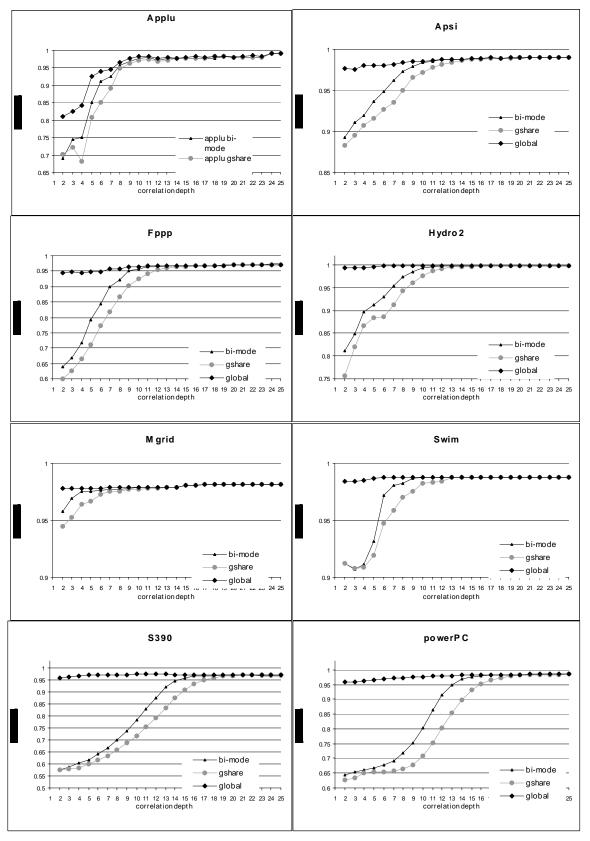

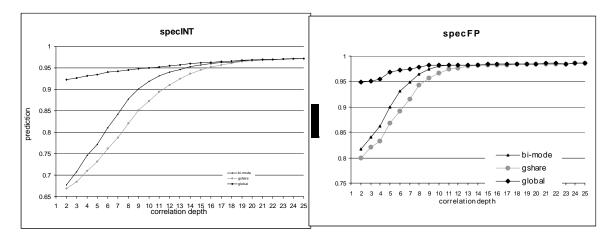

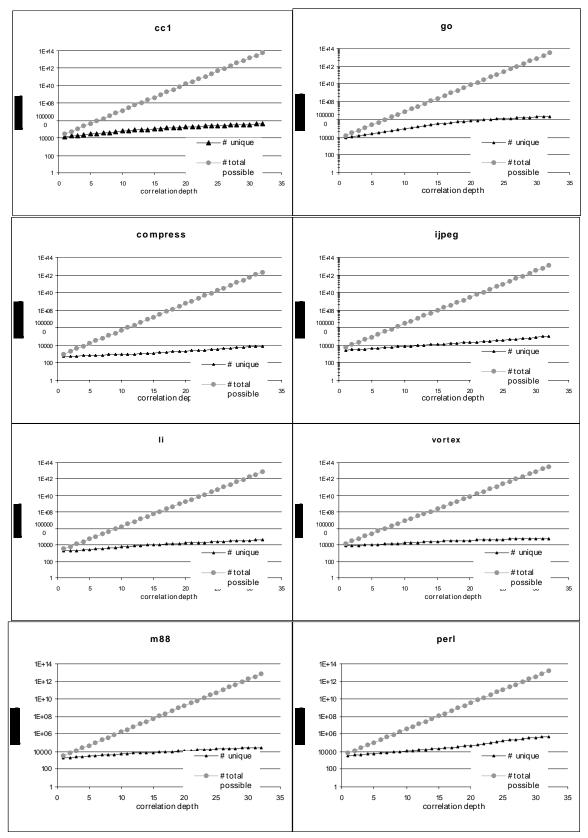

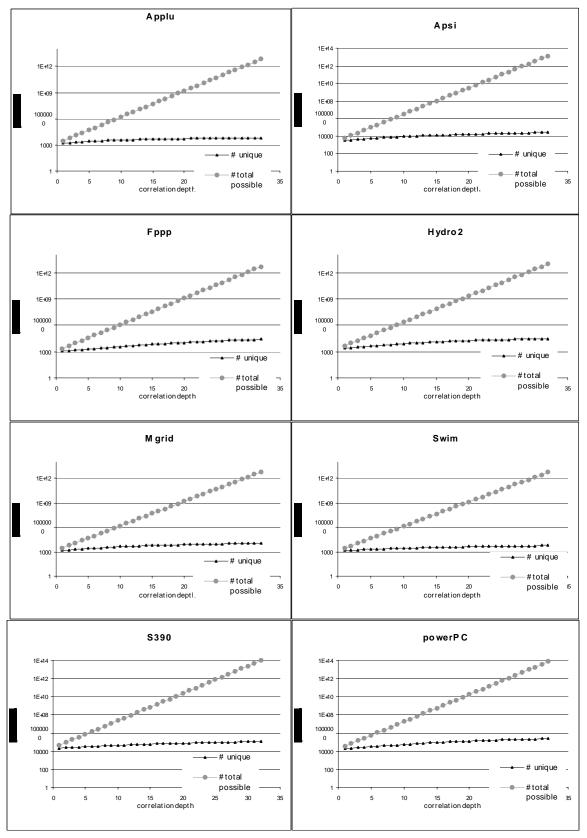

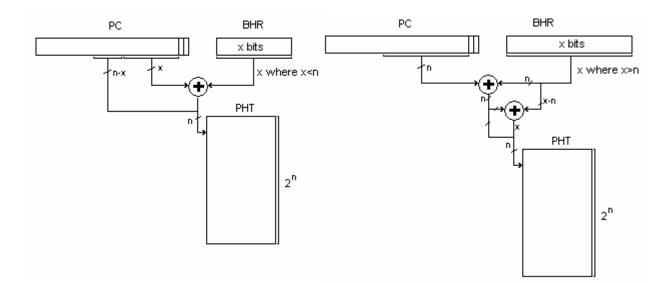

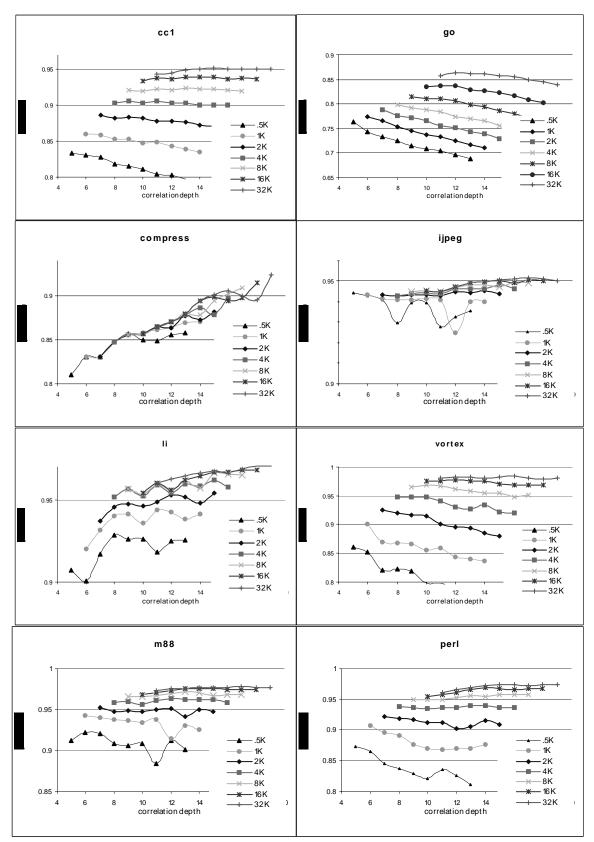

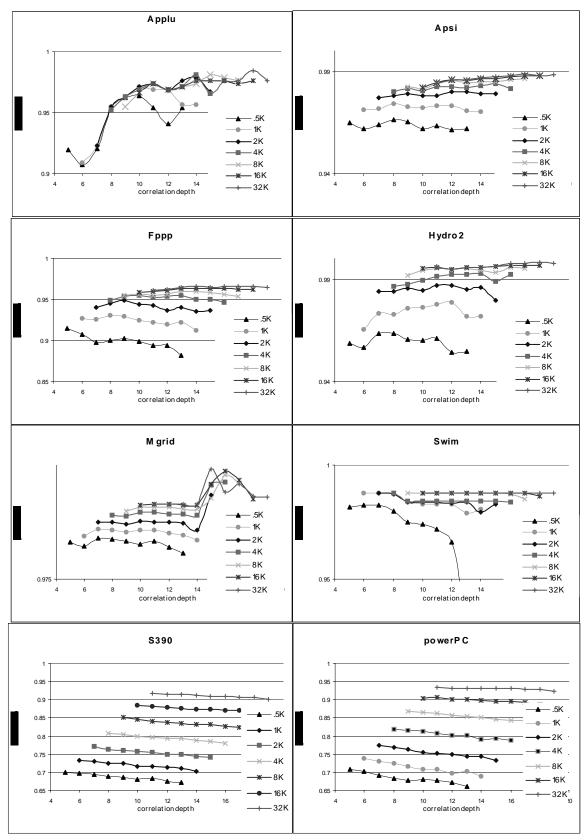

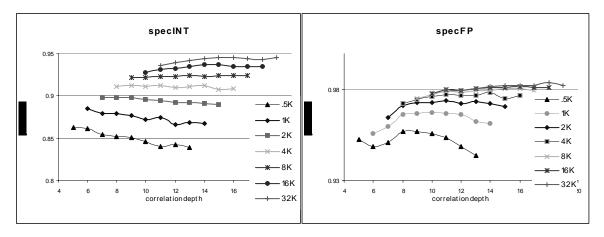

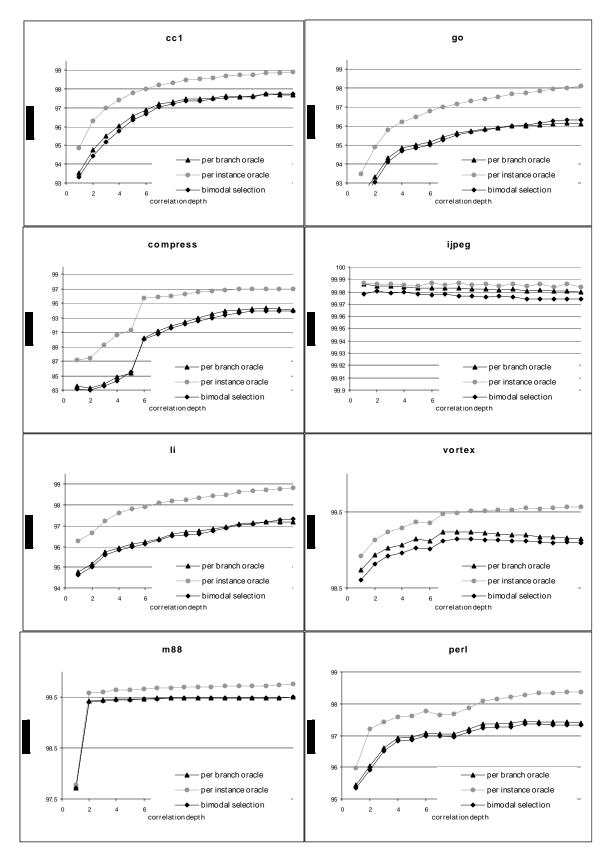

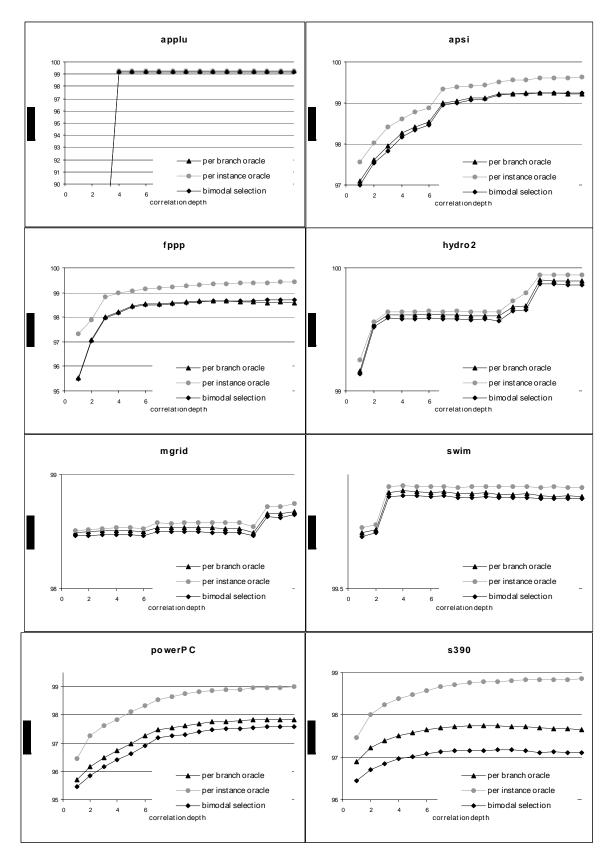

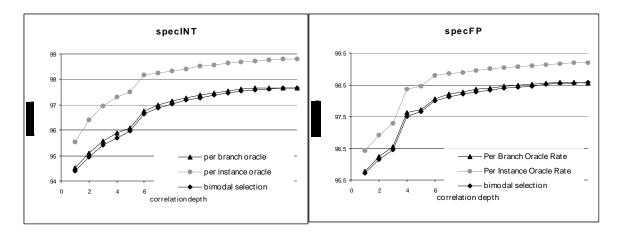

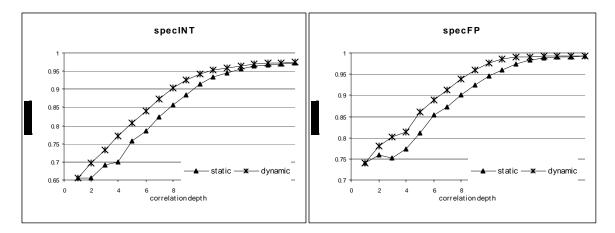

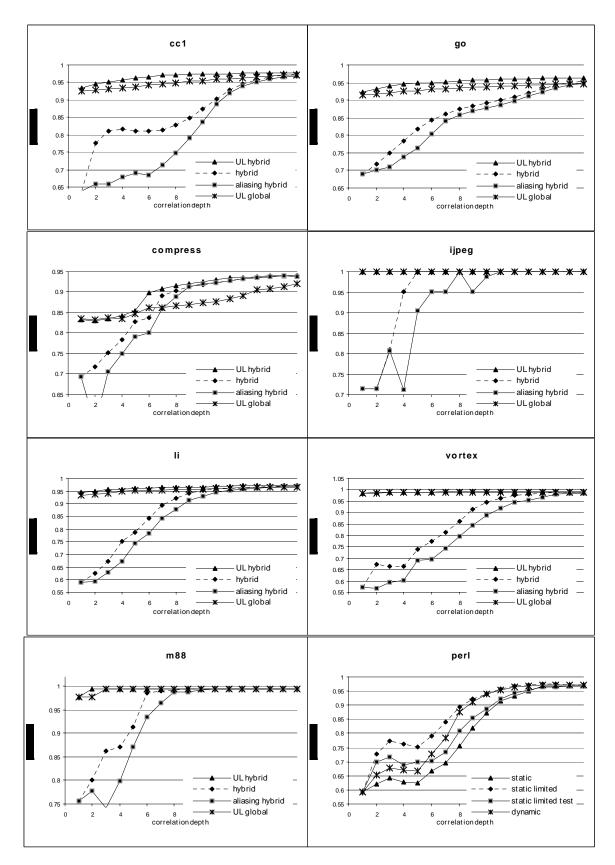

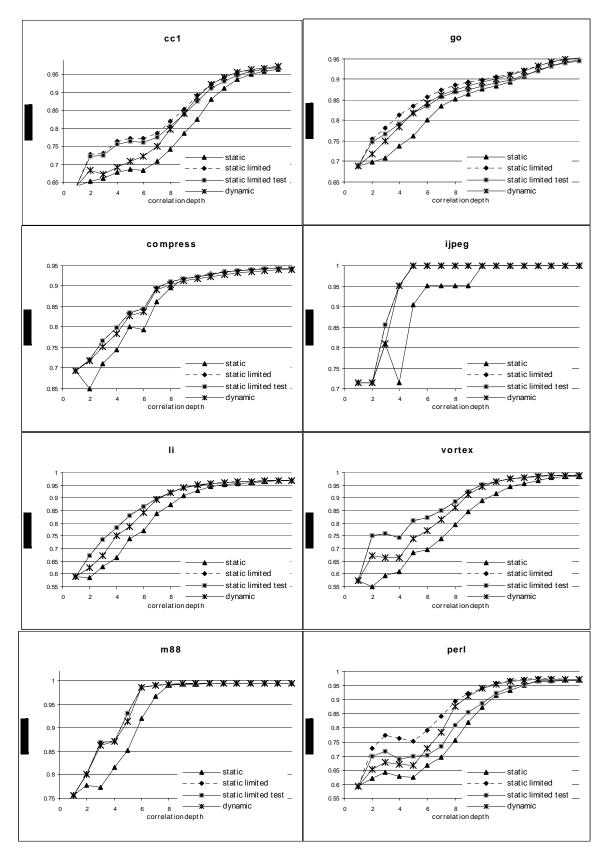

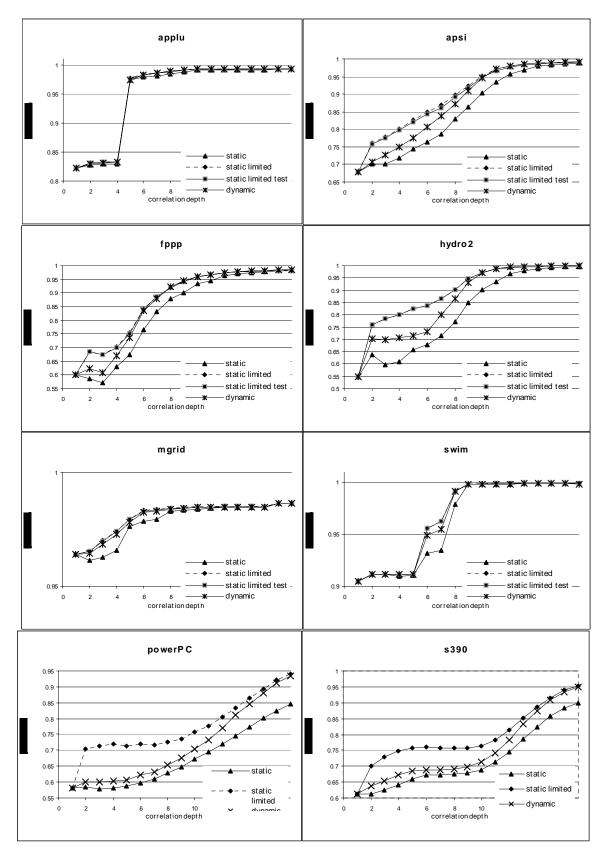

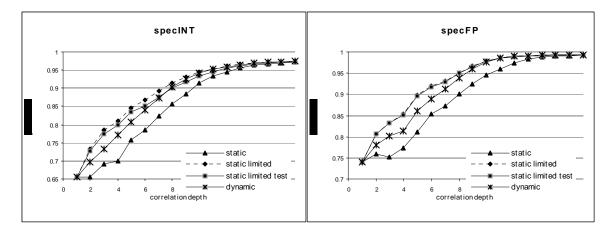

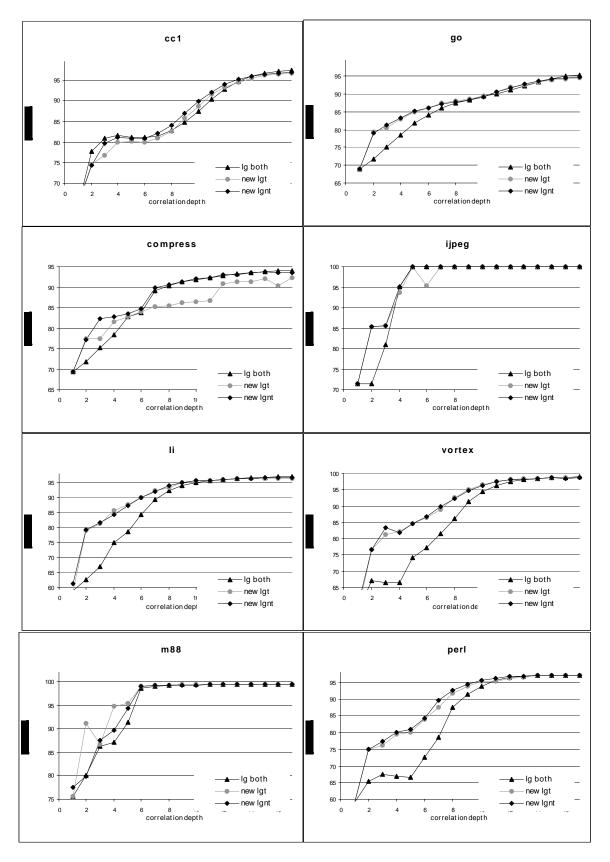

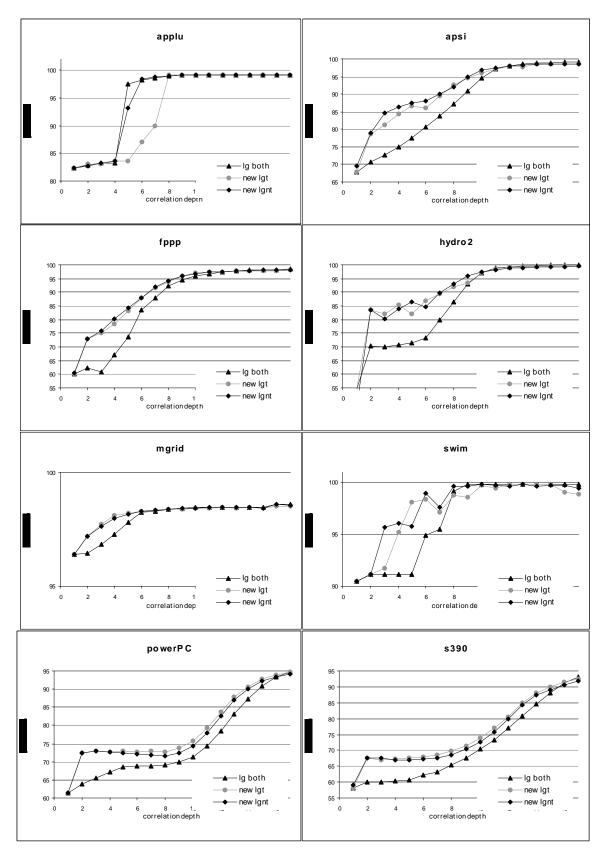

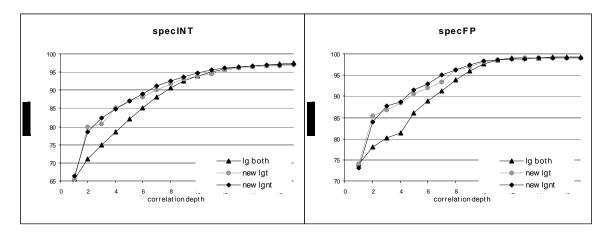

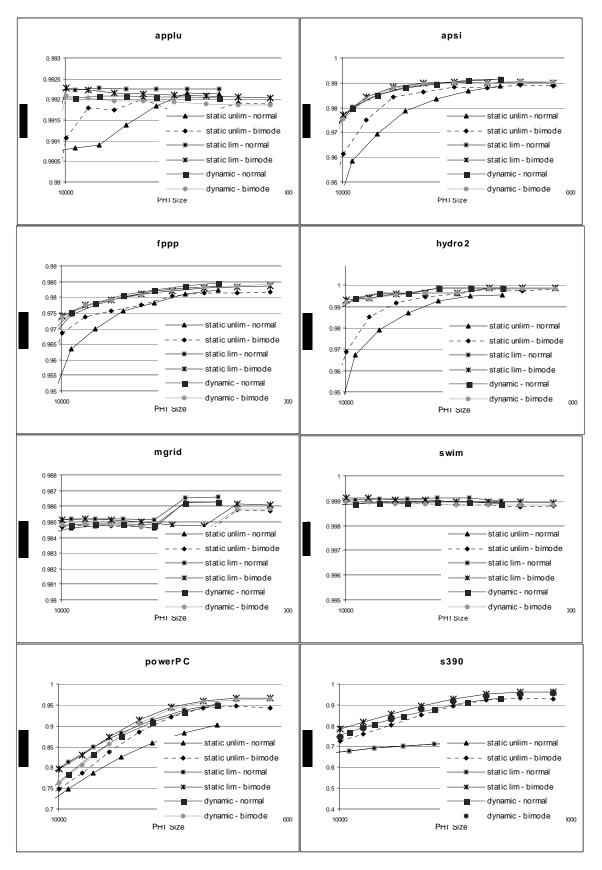

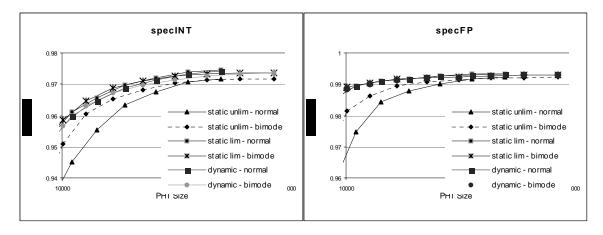

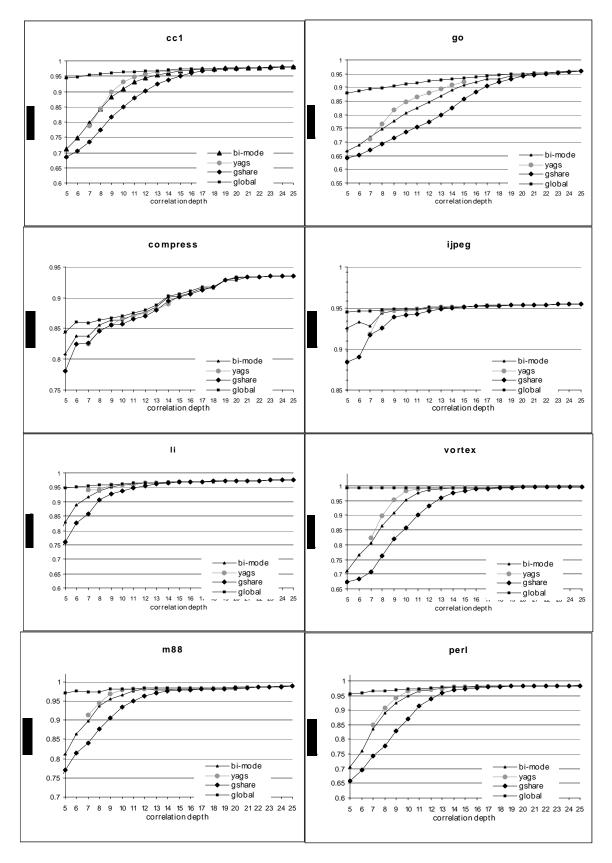

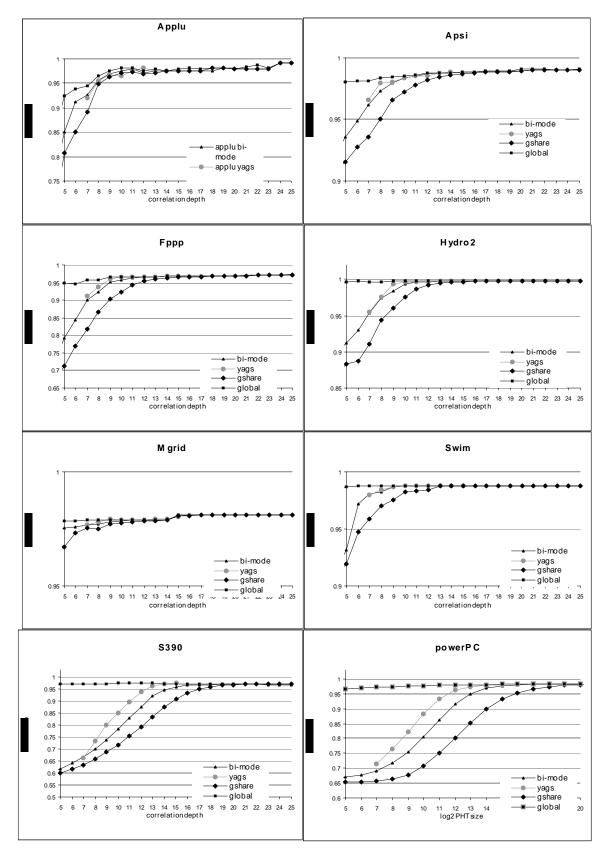

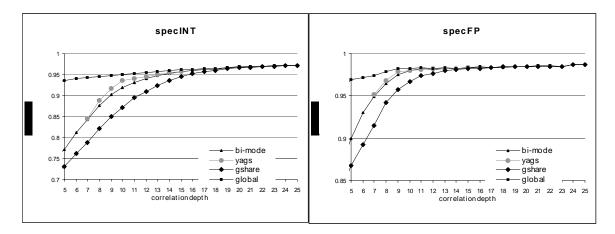

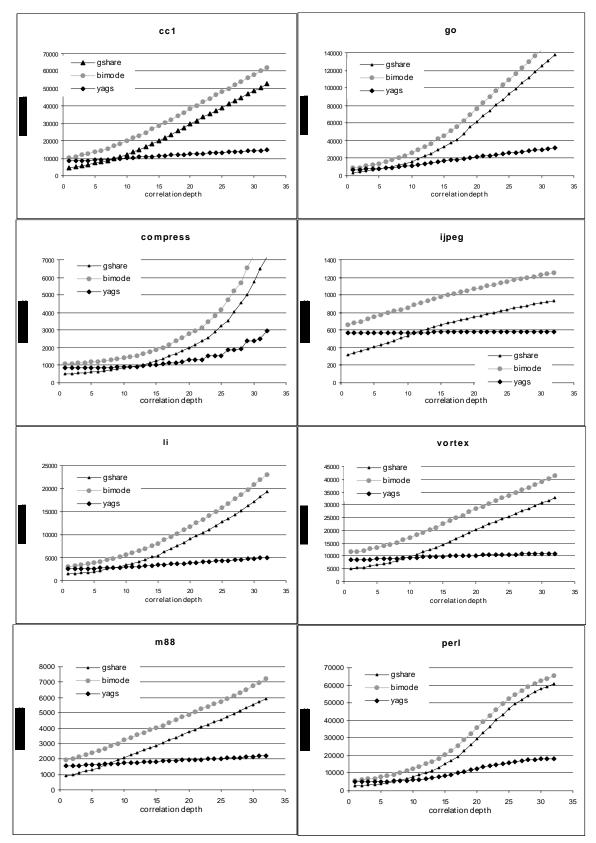

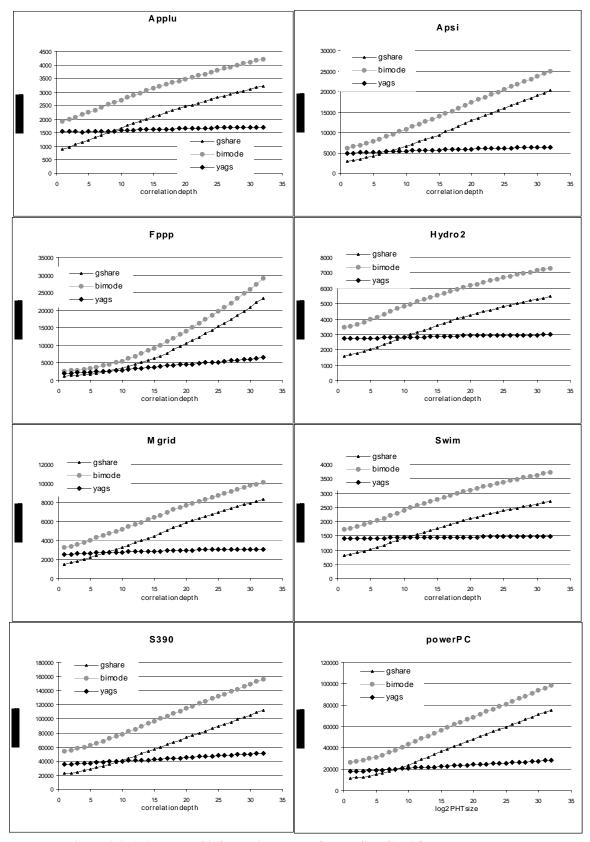

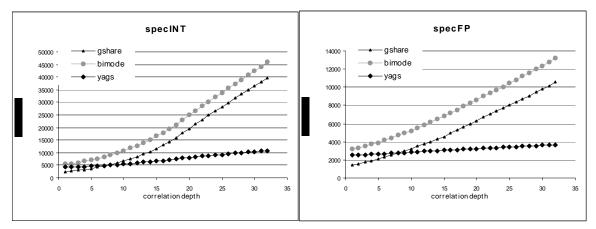

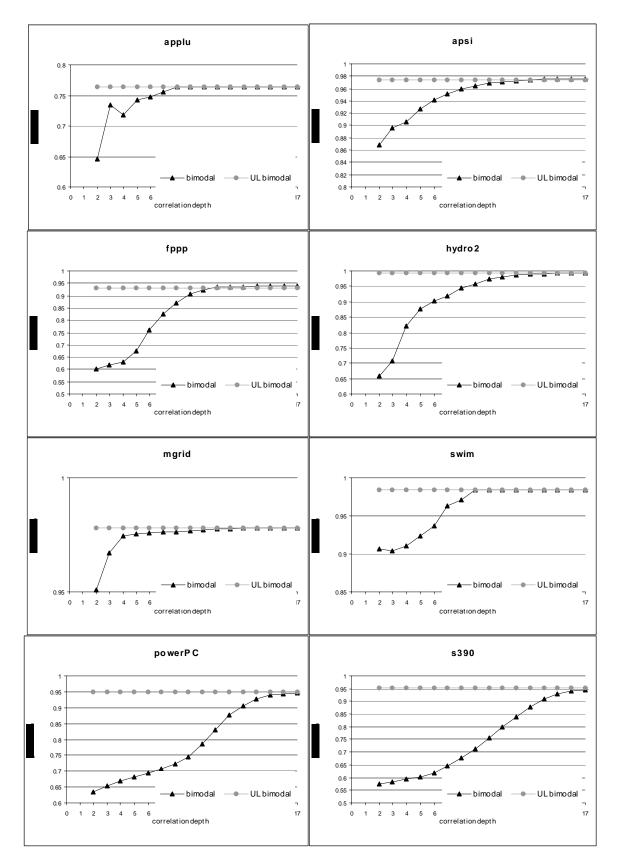

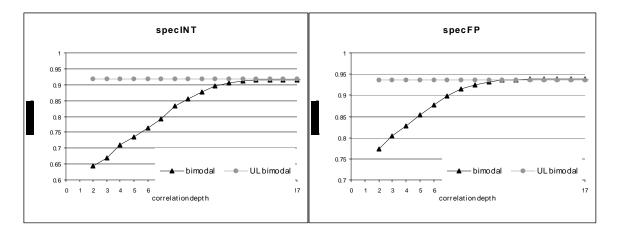

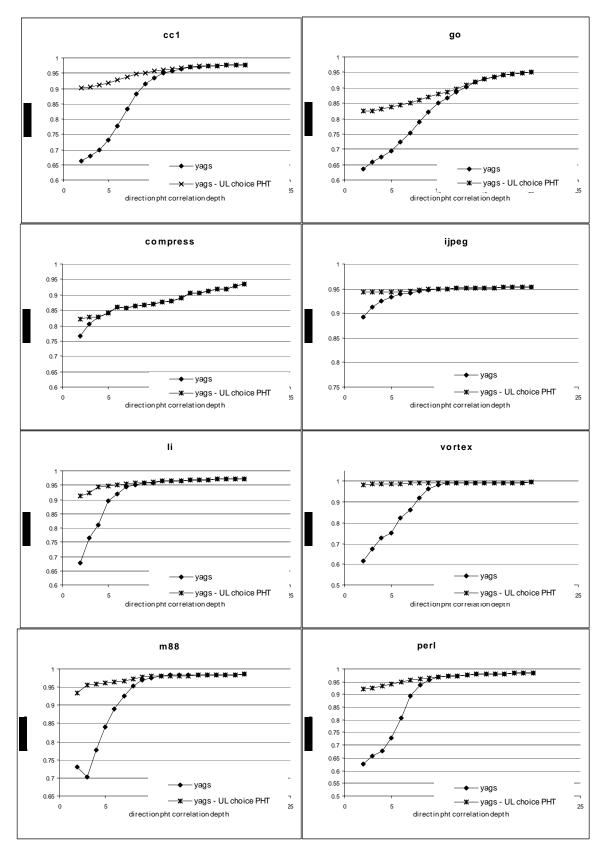

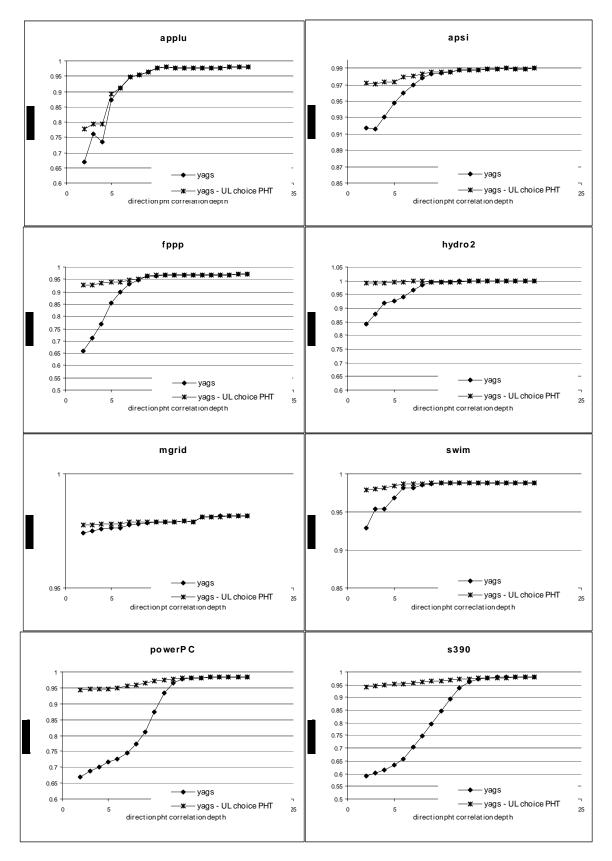

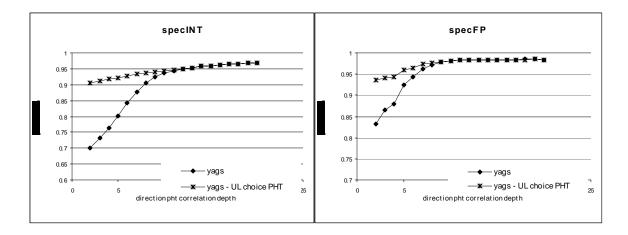

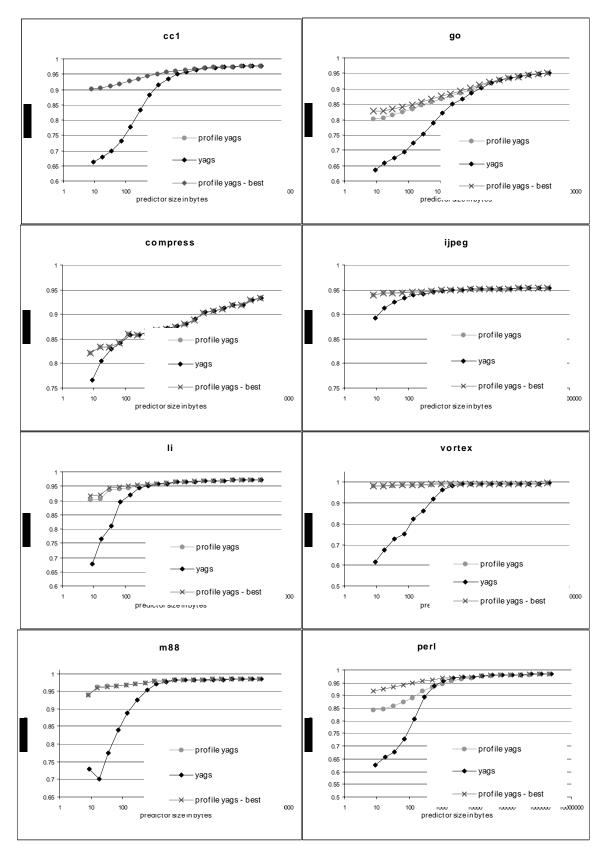

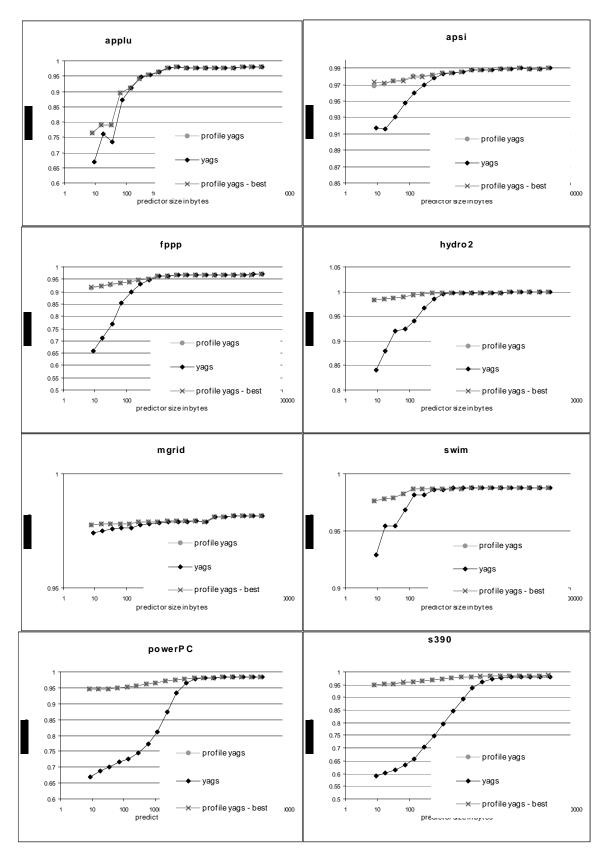

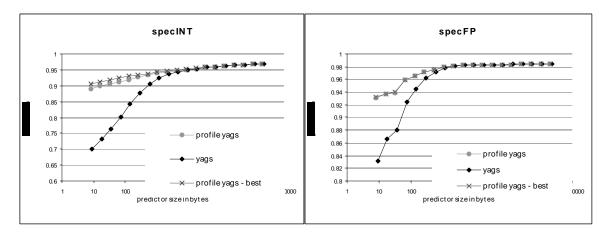

Figure 4.1 displays prediction accuracy as a function of correlation depth for four major branch prediction schemes. The four branch prediction schemes are the global scheme, the local scheme, history scheme and the bimodal scheme. All four schemes are discussed in details in Section 2.1. The graphs are presented for a) the SPECINT95 benchmarks, b) the SPECFP95 and the IBM benchmarks and c) the SPEC95 averages. Notice that the y-axis coordinates are not uniform for all graphs. For purposes of clarity, the grid line is held constant at 1% prediction accuracy for easy comparison. Correlation depth applies to the two-level schemes, but it does not apply to the bimodal scheme, which utilizes only one level. The bimodal plot is therefore constant across correlation depth. Because this is a limit study, there is no limit on resources and therefore the graph does not represent resource allocation.

It is clear that the two-level branch prediction schemes are superior to the bimodal scheme. On the other hand, the history scheme, which doesn't make use of the branch address, surpass the bimodal scheme only for large correlation depths. The global and local schemes surpass the bimodal scheme starting with correlation size of one across nearly all benchmarks. It is therefore imperative to use the two-level scheme to achieve high accuracy of branch prediction.

The ability of the history scheme to approach the prediction of the global scheme raises the question of what causes two-level branch prediction to work. Traditionally it

Figure 4.1 - a) Limits study of common branch prediction schemes for the SPECINT95

Figure 4.1 - b) Limits study of common branch prediction schemes for the SPECFP95 and IBM benchmarks

Figure 4.1 - c) Limits study of common branch prediction schemes for the SPECFP95 and SPECINT95 averages

has been thought that the two-level branch prediction schemes work well because the prediction of a branch is correlated to either previous branches in the global scheme, or to previous instances of the same branch in the local scheme. This traditional explanation is brought in question in light of ability of the history scheme to outperform the global or local scheme for several benchmarks. Remember that the history scheme applies correlation regardless of which branch is in question. One explanation could be that after a certain correlation is encountered, all branches will tend to have the same behavior, regardless of which branch is predicted and what branches came before it. However, one could easily draw different conclusions from this, and we refrain from fully addressing the topic.

It is believed that the global branch prediction scheme predicts integer programs better than the local branch prediction scheme due to the greater frequency of if-then-else statements that will cause branches to correlate to preceding branches. On the other hand, the local scheme predicts scientific programs better than the global scheme due to the large loop constructs in the program. Loops cause branches to be correlated to previous instances of the same branch. Therefore, the local scheme will outperform the global scheme for scientific code. The averages of the SPEC95 support this conventional wisdom, but it happens only at a correlation depth of 16. Looking at individual benchmarks, on the other hand, this conventional wisdom is not always the case. For example, the go benchmark, which is a prominent integer benchmark for its large branch signature, is better predicted by the local scheme. On the other hand, apsi and mgrid, which are scientific benchmarks, are better predicted by the global scheme.

The limit study presented in Figure 4.1 ignores two major considerations. The first relates to the size of a potential implementation of the scheme. Due to the mount of information stored, the local scheme is more expensive to implement in terms of hardware than the global scheme. For the local scheme correlation needs to be stored for every branch compared to only one correlation register for the global scheme. Of course an actual implementation cannot have a history register for each branch and therefore different branches must share the same history register. This aliasing effect will degrade performance. Second, the limit study ignored the warm-up effect. A static branch prediction scheme takes no time to warm up on a context switch, while the bimodal scheme needs to warm up 2bc per branch. The warm-up effect is aggravated for the global scheme that needs to warm up multiple 2bcs according to the depth of correlation used. In general, the deeper the correlation utilized, the greater the warm up time. The local scheme suffers even further due to the need to warm up the history register per branch. Nevertheless, Figure 4.1 gives an accurate indication of the maximum prediction achievable when implementing a certain branch prediction scheme.

Another notable observation is that every benchmark reaches its peak prediction performance for different correlation depths. Two extreme examples are the ijpeg benchmark that reaches its peak performance for the global scheme at a correlation depth of 2, and the cc1benchmark, which peaks at a at correlation depth of 29. If the microarchitect is able to choose the best correlation depth for each program, an overall better prediction average can be achieved.

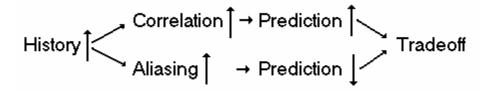

In general, we can draw the relationship between correlation and prediction accuracy

from Figure 4.1. Increasing the size of the history register increases the correlation

depth, which in turn, increases prediction accuracy. This relationship has one caveat— it

holds true only until a certain correlation depth is reached. For most programs the depth

of correlation where this relationship fails is large enough that it is not likely to be realized in hardware in the near future. Therefore, we can accept this relationship as true. The discussed drop in prediction accuracy is due to cold start effect and for long programs, increases correlation depth will entail increased prediction accuracy for even larger correlation depths than depicted in Figure 4.1.