### Architectural Trade-offs in a Latency Tolerant Gallium Arsenide Microprocessor

by

Michael D. Upton

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan

1996

**Doctoral Committee:**

Associate Professor Richard B. Brown, CoChairperson Professor Trevor N. Mudge, CoChairperson Associate Professor Myron Campbell Professor Edward S. Davidson Professor Yale N. Patt

Michael D. Upton 1996 © Michael D. C All Rights Reserved

## **DEDICATION**

#### To Kelly,

Without whose support this work may not have been started, would not have been enjoyed, and could not have been completed. Thank you for your continual support and encouragement.

### ACKNOWLEDGEMENTS

Many people, both at Michigan and elsewhere, were instrumental in the completion of this work. I would like to thank my co-chairs, Richard Brown and Trevor Mudge, first for attracting me to Michigan, and then for allowing our group the freedom to explore many different ideas in architecture and circuit design. Their guidance and motivation combined to make this a truly memorable experience.

I am also grateful to each of my other dissertation committee members: Ed Davidson, Yale Patt, and Myron Campbell. The support and encouragement of the other faculty on the project, Karem Sakallah and Ron Lomax, is also gratefully acknowledged.

My friends and former colleagues Mark Rossman, Steve Sugiyama, Ray Farbarik, Tom Rossman and Kendall Russell were always willing to lend their assistance.

Richard Oettel continually reminded me of the valuable support of friends and family, and the importance of having fun in your work.

Our corporate sponsors: Cascade Design Automation, Chronologic, Cadence, and Metasoft, provided software and support that made this work possible. A design of this complexity would not have been possible using university-developed tools.

Significant development efforts were required in all areas of microprocessor design and computer architecture to bring this project to fruition. This work was not performed in isolation, and would not have been possible without the help of many others.

**Aurora I:** Dave Johnson wrote an initial Verilog to Cascade netlist translator. Rich Uhlig designed the Verilog RTL model. Ajay Chandna, Tom Huff, Tom Hoy and I designed the modules and layout floorplan.

Aurora II: Phil Barker and PJ Sherhart designed the cell layouts used for the Aurora II

chip. Taly Budescu assisted in all the horrible tasks no-one else wanted. Tim Stanley designed much of the bus interface and a behavioral MMU to allow the Aurora II model to run real code. Bob McVay modified GCC to produce code without byte operations.

Jim Dundas tested the scan chains of the final fabrication of the Aurora II chip, and Mark Roberts and Marie Powell tested the yield of the register files.

**Aurora III:** PJ Sherhart designed the bus interface unit of the Aurora III. David Kibler did the much improved cell layouts for the Aurora III chip. Dave Putti and Sara Domonkos designed an initial version of the Load-Store Unit. Bob McVay designed an initial version of the Instruction Fetch Unit. Tim Stanley reprised his role as behavioral MMU designer, providing crucial input into the design decision of the Aurora III bus interface unit.

A special thanks is reserved for Dave Putti, who single-handedly completed the final version of the Load Store unit for the Aurora III. Without his help this work would not have been completed.

# **TABLE OF CONTENTS**

| DEDICATION       | ii    |

|------------------|-------|

| ACKNOWLEDGEMENTS | . iii |

| LIST OF FIGURES  | viii  |

| LIST OF TABLES   | . xi  |

### **CHAPTER 1**

| Introduction |                                                         |     |

|--------------|---------------------------------------------------------|-----|

| 1.1          | Technology Requirements for High Performance Processors | . 1 |

| 1.2          | Microprocessor Density Increase Over Time               | . 3 |

| 1.3          | Clock Speed Increase Over Time                          | . 6 |

| 1.4          | Research Project Goals                                  | . 7 |

### **CHAPTER 2**

| The Imp | ortance of Latency Tolerance for High Clock-Rate Processors 10 |

|---------|----------------------------------------------------------------|

| 2.1     | CPU-Memory Performance Discrepancy 10                          |

| 2.2     | Cache Miss Characterization                                    |

| 2.3     | Memory system enhancements to maintain performance             |

|         | 2.3.1 Prefetching                                              |

|         | 2.3.2 Nonblocking memory operations                            |

| 2.4     | Elements of Current Microprocessors                            |

|         | 2.4.1 R4400                                                    |

|         | 2.4.2 R8000                                                    |

|         | 2.4.3 R10000                                                   |

|         | 2.4.4 SuperSPARC                                               |

|         | 2.4.5 UltraSPARC                                               |

|         | 2.4.6 Intel Pentium Processor                                  |

|         | 2.4.7 AMD K5                                                   |

|         | 2.4.8 Motorola 88110                                           |

|         | 2.4.9 IBM/Motorola PowerPC 604                                 |

|         | 2.4.10 DEC Alpha 21064                                         |

|         | 2.4.11 DEC Alpha 21164                                         |

| 2.5     | Computational Efficiency and Delivered Performance             |

| 2.6     | Summary                                                        |

|         | •                                                              |

### CHAPTER 3

| Gallium | Arsenide Microprocessor Design Studies | 35 |

|---------|----------------------------------------|----|

| 3.1     | Gallium Arsenide DCFL Logic            | 36 |

| 3.2     | The Aurora I Processor                 | 39 |

|     | 3.2.1  | CAD Tool Development        | 41 |

|-----|--------|-----------------------------|----|

|     | 3.2.2  | Aurora I Test Results       | 42 |

| 3.3 | The A  | urora II Processor          | 44 |

|     | 3.3.1  | Timing and Optimization     | 48 |

|     | 3.3.2  | Layout Optimization         | 50 |

|     |        | I/O Pad Design              |    |

| 3.4 | Aurora | a II Results                | 53 |

|     | 3.4.1  | Error Summary               | 54 |

|     | 3.4.2  | Clocking Issues             | 56 |

|     | 3.4.3  | Exception Overhead          | 56 |

|     | 3.4.4  | GaAs Technical Difficulties | 57 |

#### **CHAPTER 4**

| Process | Modeling Studies                    | . 61 |

|---------|-------------------------------------|------|

| 4.1     | SUSPENS system performance model    | . 61 |

| 4.2     | GaAs SUSPENS Model                  | . 62 |

|         | 4.2.1 Bakoglu Equations             | . 66 |

| 4.3     | Model Sensitivity                   | . 68 |

| 4.4     | Aurora III Architectural Directions | . 69 |

| 4.5     | Aurora III Model Predictions        | . 70 |

| 4.6     | Aurora III Model Floorplan          | . 71 |

| 4.7     | Conclusion                          | . 72 |

#### CHAPTER 5

| Impact | Impact of GaAs Technology on Architecture74       |  |  |

|--------|---------------------------------------------------|--|--|

| 5.1    | Path Length Reduction                             |  |  |

| 5.2    | Interconnect Parasitics                           |  |  |

| 5.3    | Functional Decomposition                          |  |  |

| 5.4    | Circuit Design Techniques for Reduced Path Length |  |  |

|        | 5.4.1 Ling Adder                                  |  |  |

|        | 5.4.2 Pipelined Ling Adder 82                     |  |  |

| 5.5    | Summary                                           |  |  |

#### CHAPTER 6

| Aurora | III Microprocessor System Architecture and Design | 84 |

|--------|---------------------------------------------------|----|

| 6.1    | System Overview                                   | 84 |

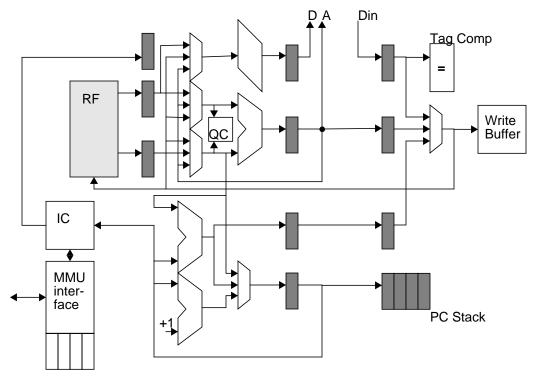

| 6.2    | Processor Organization                            | 88 |

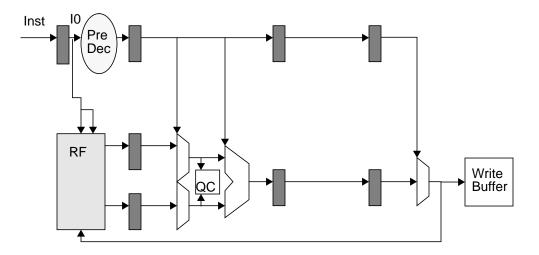

| 6.3    | Instruction Fetch Unit                            | 91 |

| 6.4    | Execution Unit                                    | 93 |

| 6.5    | Load/Store Unit                                   | 98 |

| 6.6    | Prefetch Unit 10                                  | 00 |

|        | Bus Interface Unit                                | -  |

| 6.8    | Architectural Evaluation 10                       | 04 |

| 6.9    | Study Results                                     | 05 |

| 6.10   | Summary 1                                         | 13 |

#### CHAPTER 7

| The Des | sign Process and Verification                               | 115 |

|---------|-------------------------------------------------------------|-----|

| 7.1     | Overview                                                    | 115 |

| 7.2     | Critical Path Optimization                                  | 115 |

| 7.3     | Processor Verification                                      | 118 |

| 7.4     | Scheduling                                                  | 121 |

| 7.5     | Bug Tracking                                                | 124 |

| 7.6     | A (small) Theory of System Debugging                        | 127 |

| 7.7     | Design Decision Critique                                    | 132 |

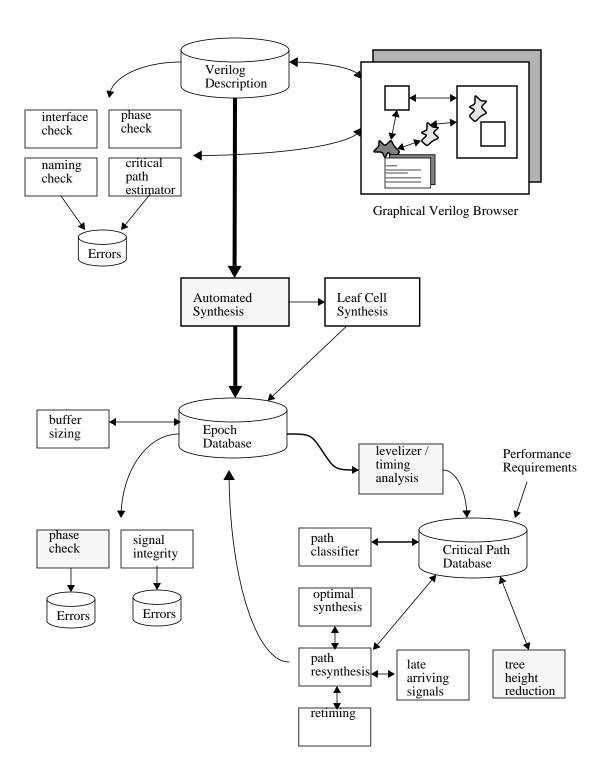

| 7.8     | A Unified CAD System for High Performance Digital IC Design | 135 |

|         | 7.8.1 Verilog Analysis Tools                                | 138 |

|         | 7.8.2 Layout Synthesis                                      | 139 |

|         | 7.8.3 Gate Level Optimization                               | 139 |

| 7.9     | Summary                                                     | 141 |

#### **CHAPTER 8**

| Conclusion |                                                         |    |

|------------|---------------------------------------------------------|----|

| 8.1        | Future Work                                             | 42 |

| 8.2        | Research Contributions                                  | 43 |

| 8.3        | Outlooks for Microprocessors                            | 47 |

| 8.4        | GaAs Microprocessors and Market Entry Dynamics1         | 47 |

|            | 8.4.1 Market Response Example: Exotic Photolithography1 | 49 |

|            | 8.4.2 Market Capture Example: NMOS vs. CMOS 1983 1      | 51 |

| 8.5        | Whither GaAs? 1                                         | 52 |

|            |                                                         |    |

# LIST OF FIGURES

| Figure 1.1  | Fabrication Facility Cost    4                    |

|-------------|---------------------------------------------------|

| Figure 1.2  | ISSCC Microprocessor Transistor Counts            |

| Figure 1.3  | ISSCC Microprocessor Clock Frequencies            |

| Figure 1.4  | Integer SPECmark Performance                      |

| Figure 1.5  | SPECint Performance vs. Clock Frequency Growth    |

| Figure 2.1  | Estimated SPECint Performance                     |

| Figure 2.2  | Cache Size Resulting in 50% of Peak Performance   |

| Figure 2.3  | Relative TPCA Performance                         |

| Figure 2.4  | Stream Buffer Organization                        |

| Figure 2.5  | Correlation of Efficiency and SPECint Performance |

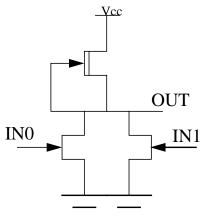

| Figure 3.1  | 2-Input GaAs NOR Gate                             |

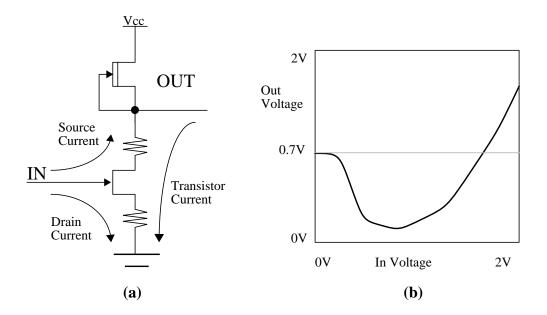

| Figure 3.2  | GaAs Inverter Transfer Function                   |

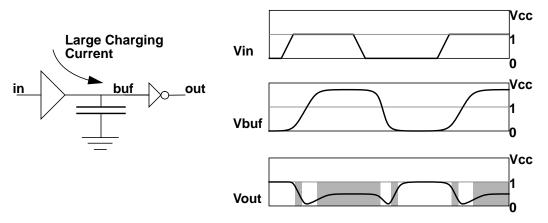

| Figure 3.3  | GaAs DCFL Buffer Overdriving                      |

| Figure 3.4  | Aurora I Pipeline Diagram                         |

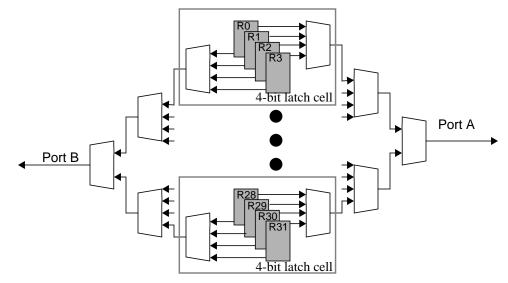

| Figure 3.5  | Aurora I Register File Organization               |

| Figure 3.6  | Aurora I Control Design                           |

| Figure 3.7  | Aurora I CAD System Flow                          |

| Figure 3.8  | Aurora II Pipeline Diagram                        |

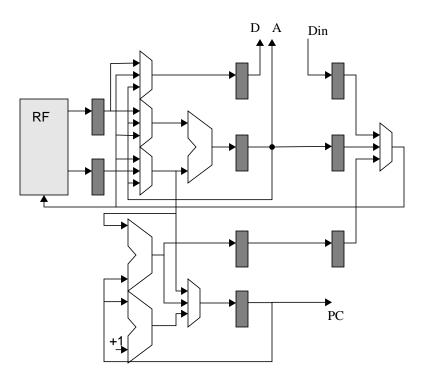

| Figure 3.9  | Aurora II Control Logic Diagram                   |

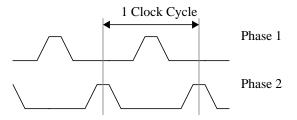

| Figure 3.10 | Two Phase Clock Diagram    48                     |

| Figure 3.11 | Manual Cycle Time Improvements                    |

| Figure 3.12 | Aurora II Critical Path                           |

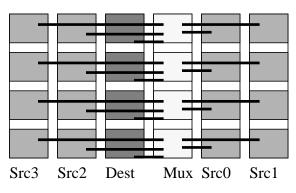

| Figure 3.13 | Column Based Datapath Example                     |

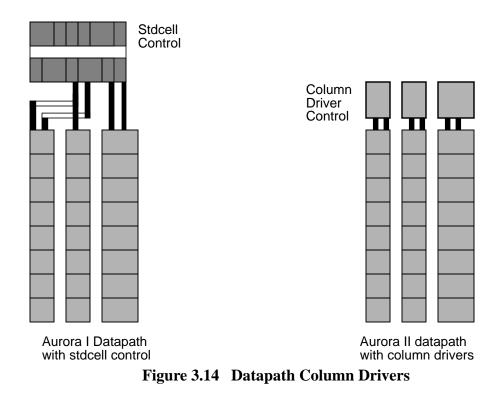

| Figure 3.14 | Datapath Column Drivers                                        |

|-------------|----------------------------------------------------------------|

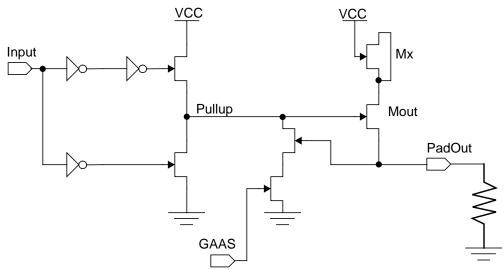

| Figure 3.15 | GaAs Electrically Programmable Output Pad53                    |

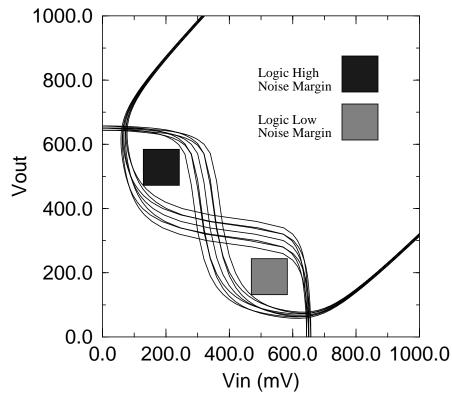

| Figure 3.16 | GaAs DCFL Noise Margin at 25 Degrees C                         |

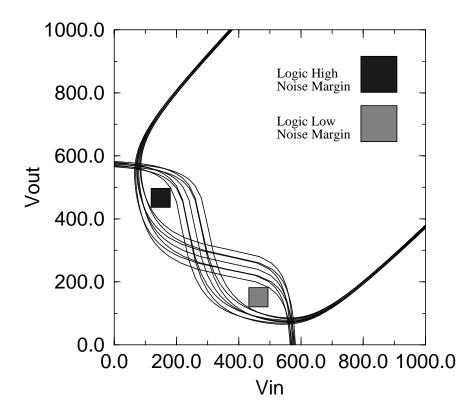

| Figure 3.17 | GaAs DCFL Noise Margin at 100 Degrees C                        |

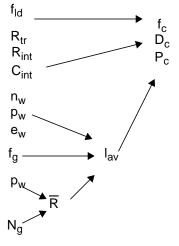

| Figure 4.1  | Parameter Flow Diagram                                         |

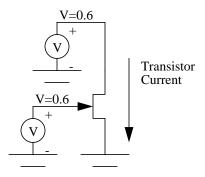

| Figure 4.2  | Transistor Resistance Calculation                              |

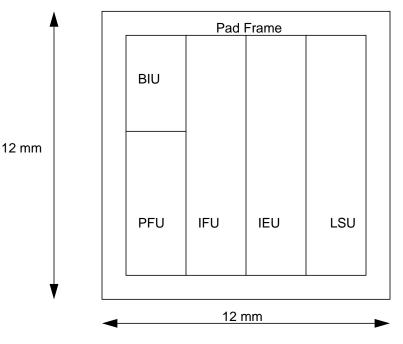

| Figure 4.3  | Target Aurora III Floorplan    72                              |

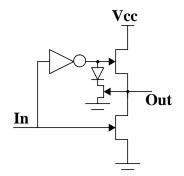

| Figure 5.1  | Feedback FET Logic Buffer Schematic                            |

| Figure 5.2  | High Drive Logic Synthesis Outputs                             |

| Figure 5.3  | Mux Based Datapath Selection                                   |

| Figure 5.4  | Tristate Based Datapath Selection                              |

| Figure 5.5  | Tristate Buffer Circuit Diagram                                |

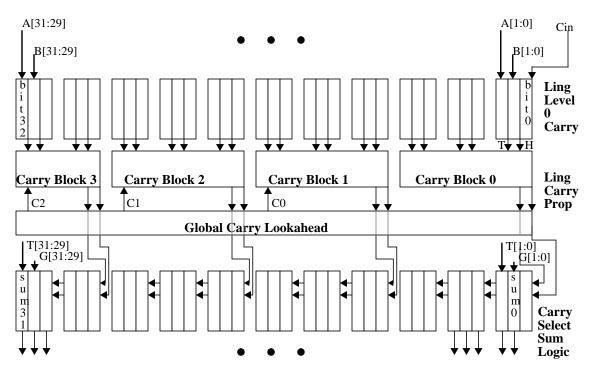

| Figure 5.6  | Ling Adder Block Diagram                                       |

| Figure 5.7  | Pipelined Ling Adder                                           |

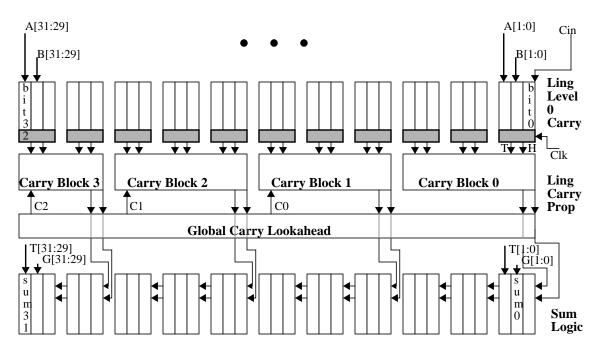

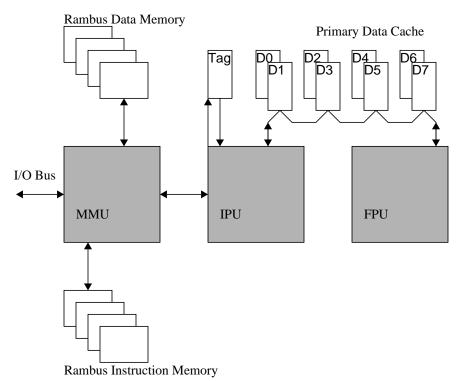

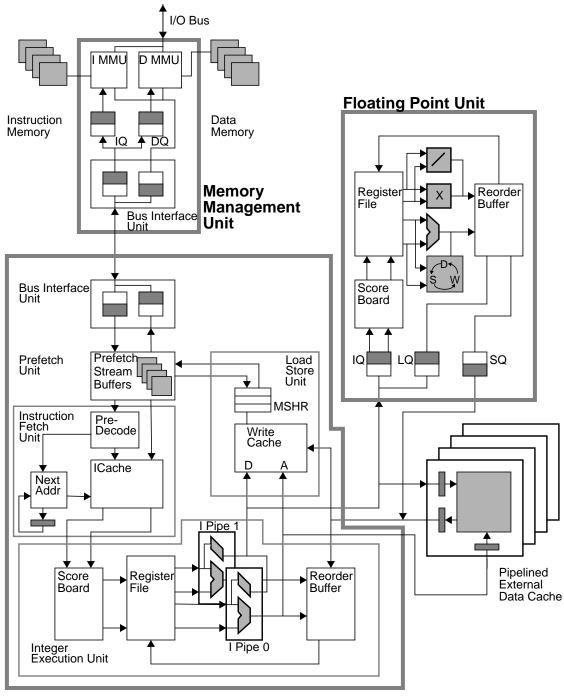

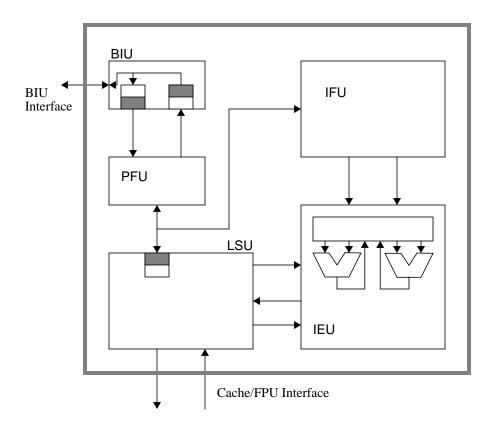

| Figure 6.1  | Aurora III System                                              |

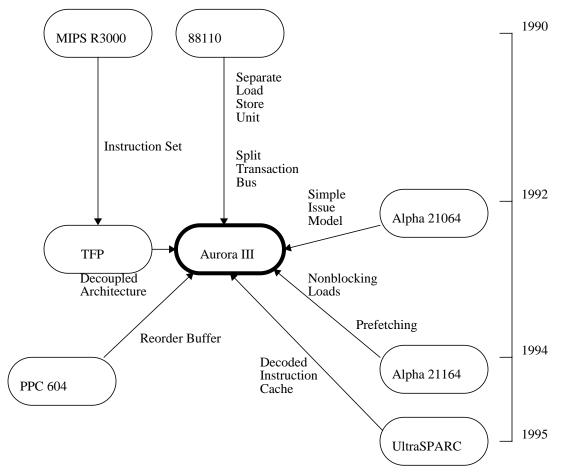

| Figure 6.2  | Architectural Heritage of the Aurora III Processor             |

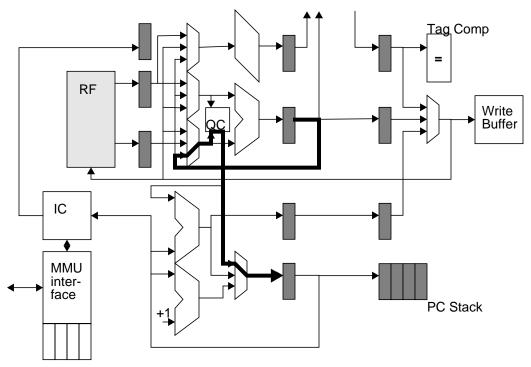

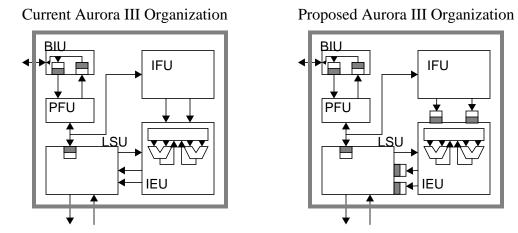

| Figure 6.3  | Processor Block Diagram                                        |

| Figure 6.4  | Integer Processing Unit Block Diagram                          |

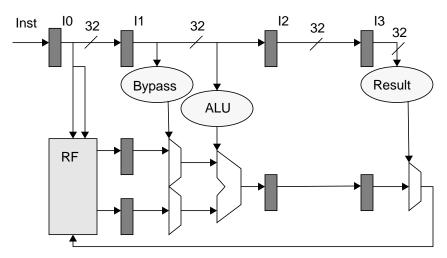

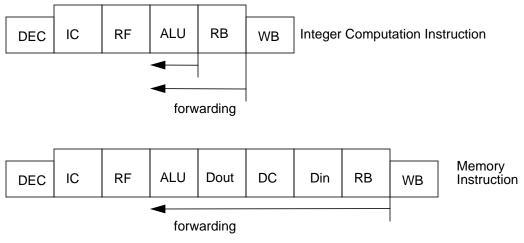

| Figure 6.5  | IPU Pipeline Forwarding Paths                                  |

| Figure 6.6  | IPU Pipeline Stages                                            |

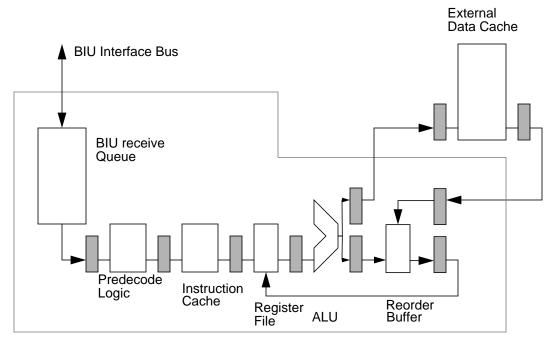

| Figure 6.7  | Decoded Instruction Cache Format                               |

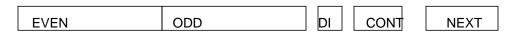

| Figure 6.8  | Traditional vs. Direct-Mapped Register Renaming                |

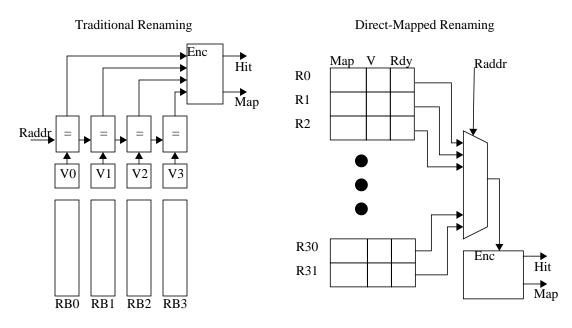

| Figure 6.9  | BIU Interface                                                  |

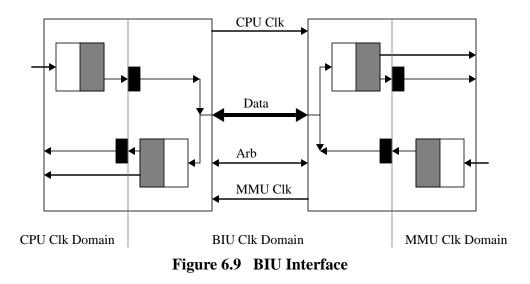

| Figure 6.10 | BIU Timing Diagram                                             |

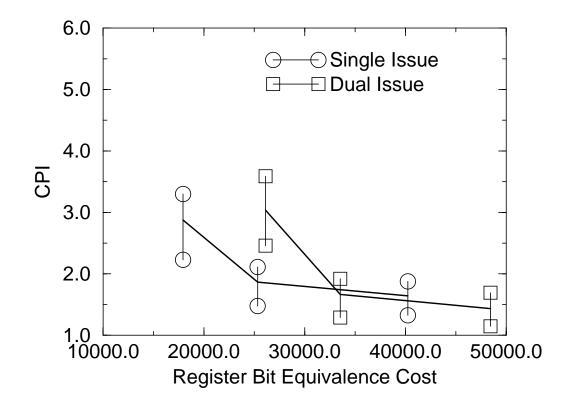

| Figure 6.11 | Dual and Single Issue Performance, 17 Cycle Memory Latency 106 |

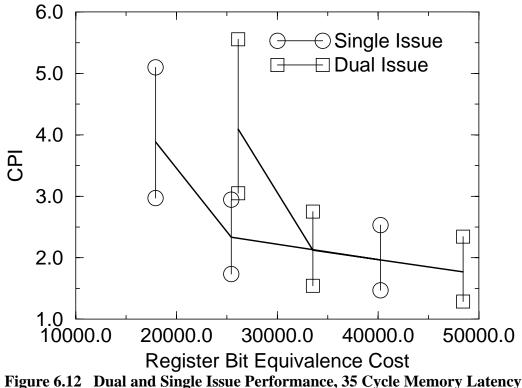

| Figure 6.12 | Dual and Single Issue Performance, 35 Cycle Memory Latency 107         |

|-------------|------------------------------------------------------------------------|

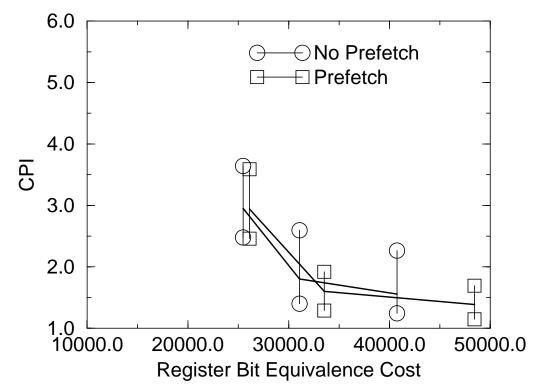

| Figure 6.13 | Effects of Prefetch Removal, 17-cycle Memory Latency, Dual Issue . 109 |

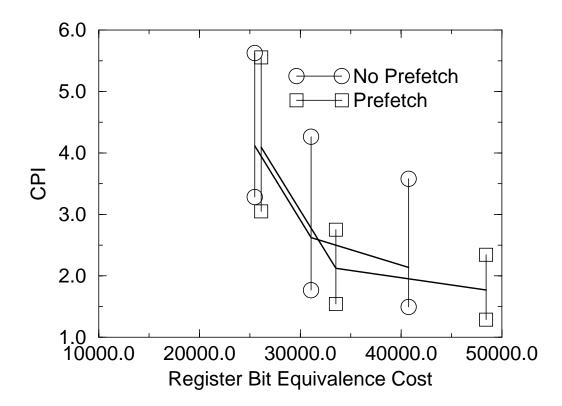

| Figure 6.14 | Effects of Prefetch Removal, 35-cycle Memory Latency, Dual Issue . 109 |

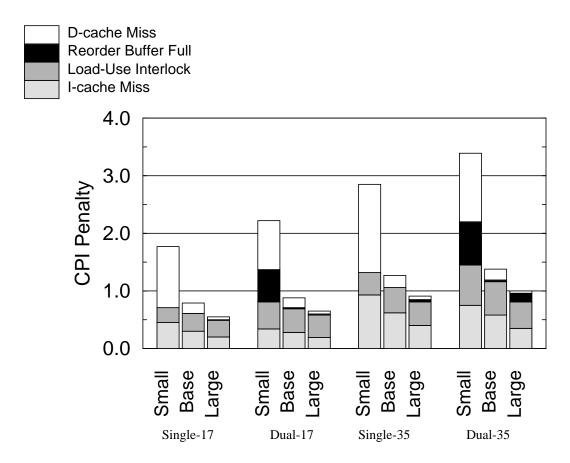

| Figure 6.15 | CPI Losses to Different Causes                                         |

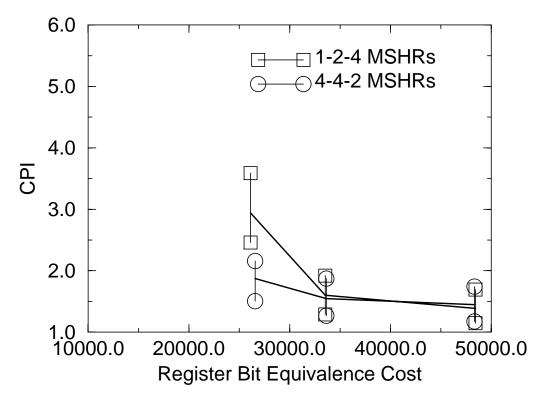

| Figure 6.16 | Effects of Changing MSHR Count on Dual Issue Model                     |

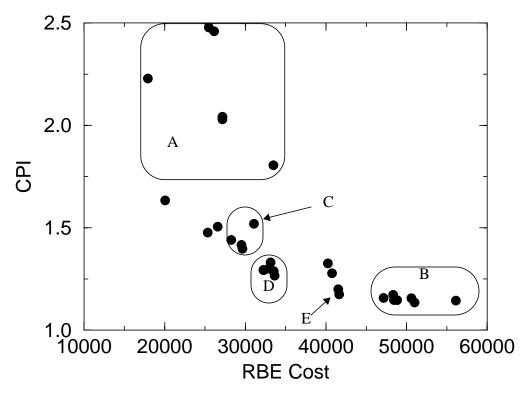

| Figure 6.17 | Espresso Full Data Set, 17-cycle Memory Latency                        |

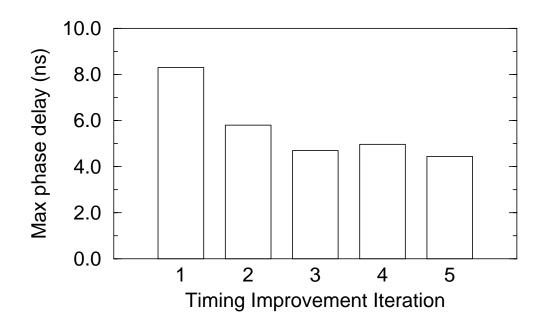

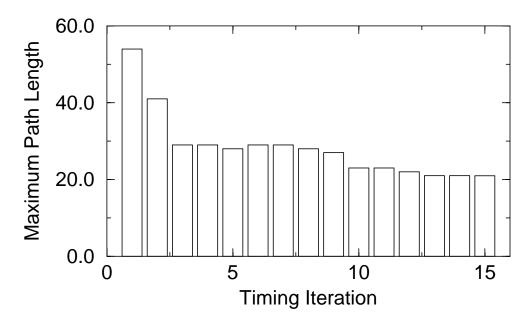

| Figure 7.1  | Critical Path Length for Aurora III CPU                                |

| Figure 7.2  | Total Number of Critical Paths Greater Than 18 Levels                  |

| Figure 7.3  | Two Phase Clock Diagram                                                |

| Figure 7.4  | Total Cumulative Verification Cycles                                   |

| Figure 7.5  | Top Level Design Schedule    122                                       |

| Figure 7.6  | Aurora III Schedule Slippage Diagram                                   |

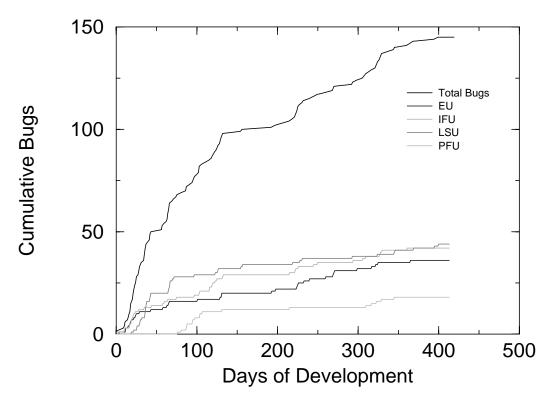

| Figure 7.7  | Total Development Bugs by Unit                                         |

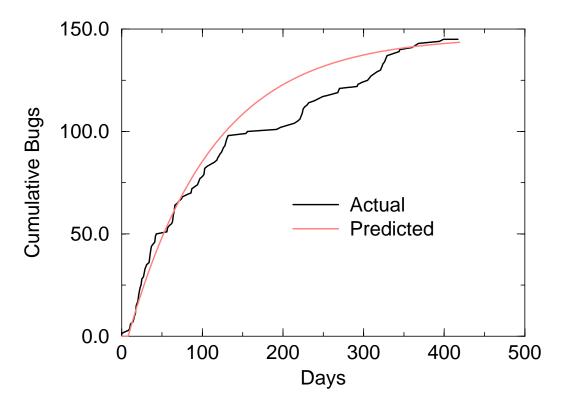

| Figure 7.8  | Predicted Cumulative Bug Data                                          |

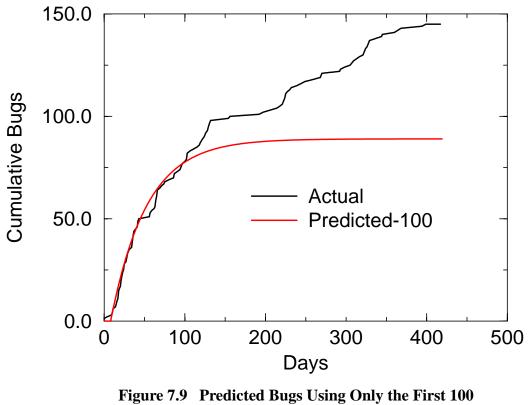

| Figure 7.9  | Predicted Bugs Using Only the First 100 Days of Data                   |

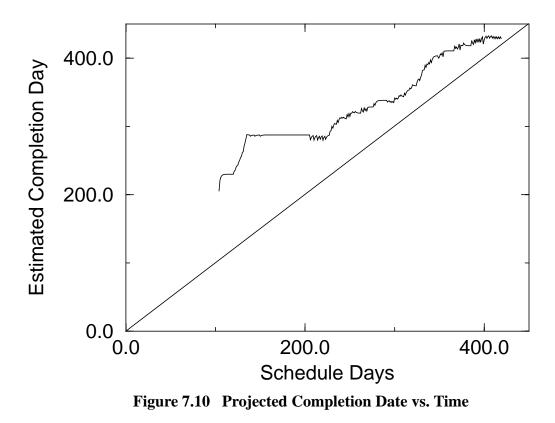

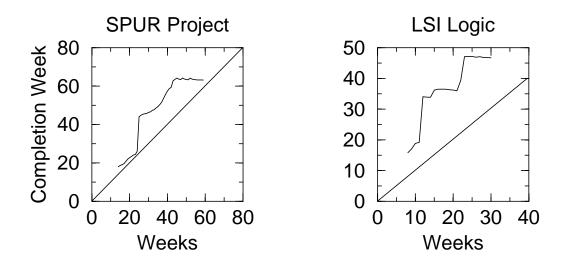

| Figure 7.10 | Projected Completion Date vs. Time                                     |

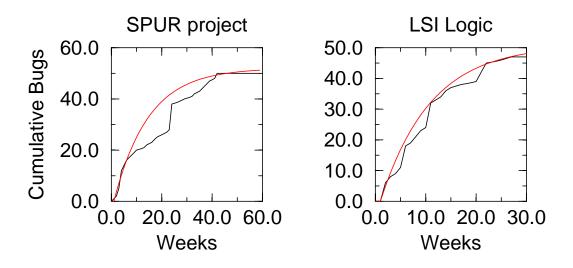

| Figure 7.11 | Cumulative Bug Data for Two Projects                                   |

| Figure 7.12 | Estimated Completion Date for Two Projects                             |

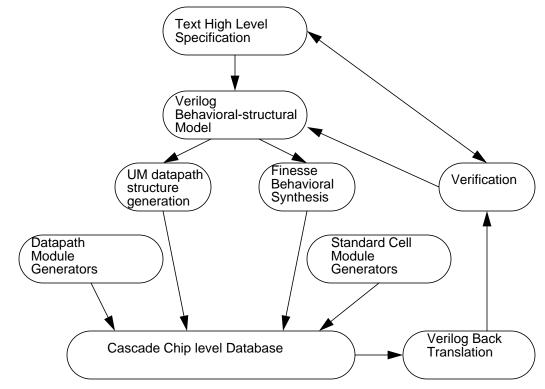

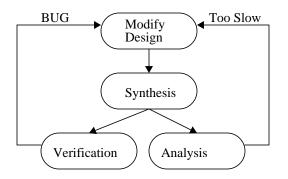

| Figure 7.13 | Behavioral Synthesis Design Loop                                       |

| Figure 7.14 | Proposed CAD System                                                    |

| Figure 8.1  | Proposed Additional Queue Locations                                    |

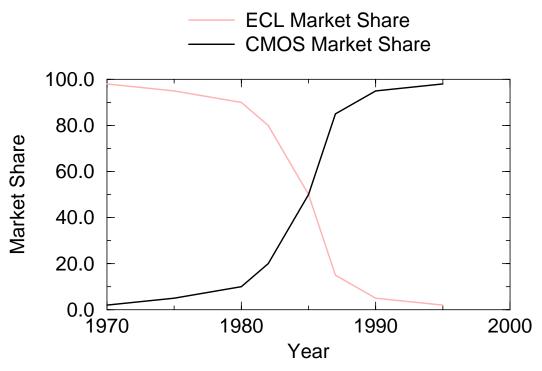

| Figure 8.2  | ECL vs. CMOS Market Response Graph                                     |

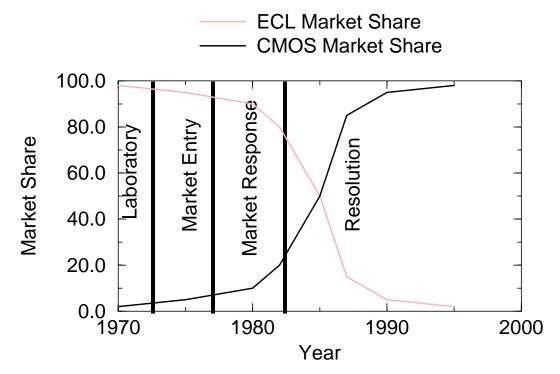

| Figure 8.3  | Four Phases of Market Dynamics                                         |

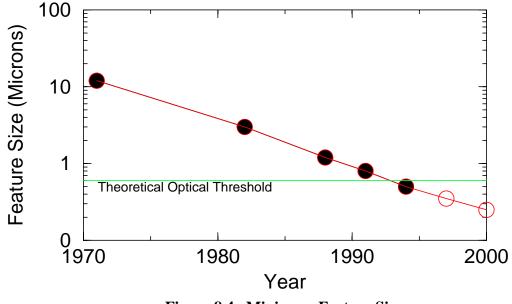

| Figure 8.4  | Minimum Feature Size                                                   |

# LIST OF TABLES

| Table 1.1  | Technology Support for Microprocessor Development 2         |

|------------|-------------------------------------------------------------|

| Table 2.1  | Integer SPEC Cache Hit Rates 12                             |

| Table 2.2  | TPC A Cache Hit Rates                                       |

| Table 2.3  | Predicted SPECint Performance                               |

| Table 2.4  | Current Processor Characteristics                           |

| Table 3.1  | Aurora I RF Yield Analysis                                  |

| Table 3.2  | Optimal Datapath Placement Results                          |

| Table 3.3  | Aurora II RF Yield Analysis                                 |

| Table 3.4  | Logic Synthesis Comparison                                  |

| Table 4.1  | Performance Estimation Parameters                           |

| Table 4.2  | HGaAs II Effective Routing Pitch                            |

| Table 4.3  | HGaAs III Effective Routing Pitch                           |

| Table 4.4  | 3 Metal Effective Routing Pitch                             |

| Table 4.5  | HGaAs II Model Predictions for Aurora I Chip                |

| Table 4.6  | HGaAs III Model Predictions for Aurora II Chip              |

| Table 4.7  | Process Parameter Sensitivity                               |

| Table 4.8  | HGaAs III Model Predictions for Aurora III Chip             |

| Table 4.9  | Predicted Aurora III Parameters in Different Processes      |

| Table 4.10 | Area Allocation for Aurora III Processor                    |

| Table 6.1  | SPECint Write Cache MicroTLB Hit Rates                      |

| Table 6.2  | The Three Machine Models and Their Associated Resources 104 |

| Table 6.3  | Processor Element Cost in RBE Units 105                     |

| Table 6.4  | Dual Issue Frequency                                        |

| Table 6.5 | Integer I Prefetch Hit Rate Percentages 108       |

|-----------|---------------------------------------------------|

| Table 6.6 | Integer D Prefetch Hit Rate Percentages 108       |

| Table 6.7 | Integer Write Cache Hit Rate Percentage           |

| Table 7.1 | Initial Critical Path Lengths 115                 |

| Table 7.3 | Design Errors by Cause                            |

| Table 7.2 | Bug Statistics by Module 125                      |

| Table 7.4 | Comparison of Estimated Completion Date           |

| Table 8.1 | Technology Support for Microprocessor Development |

# CHAPTER 1 Introduction

A processor designed in a new technology must present significant performance and cost advantages over current design practices, or it will not succeed in the marketplace. New technologies are often advertised as having great advantages over those currently in production; however, the advantages often dissipate on further investigation. Much of the difficulty faced by a new technology is caused by rapid improvements in existing technologies.

A primary purpose of this work was to critically evaluate E/D MESFET Gallium Arsenide (GaAs) process technology for the design and implementation of high performance microprocessors. Technology has a profound impact on processor microarchitectures. The prospect of high transistor switching speed made GaAs Direct Coupled FET Logic (DCFL) an interesting technology high clock rate processor investigation. A second goal of this research was to investigate the effects ever-increasing clock rates would have on superscalar instruction issue capability.

A discussion of desirable process characteristics and technology trends will provide a context for the investigation of GaAs DCFL as a technology for microprocessor design.

#### 1.1 Technology Requirements for High Performance Processors

There are two fundamental uses for transistors in a microprocessor: computation resources and state resources. To achieve good system-level performance, a technology must support both uses efficiently. The basic properties required for a high performance microprocessor include:

**Logic Gate Switching Speed**: The logical and arithmetic operations of a processor are implemented using logic gates to perform boolean operations on binary values. To achieve high performance the logic gates must be fast.

**Circuit Density**: The logic gates needed to implement a function should fit in a small area. Large area increases the interconnect capacitance, which slows the circuit and raises the power needed to switch these interconnect lines.

**On-chip Memory**: It must be possible to build memory structures on the processor chip. These memories are used both for register files and primary caches.

**Interconnect Driving Ability**: The technology must be able to rapidly drive signals that cross the chip. This means a high current buffer is needed.

**I/O Bandwidth and Latency**: Fast signal swing of external signals is important. Low voltage levels are needed to minimize noise generation.

**Low Power Dissipation**: Air cooled desktop processors require CPU power dissipations of 40 Watts or less.

**Clock Distribution**: Clock skew can consume a large percentage of the cycle time at high clock frequencies. The technology must support a low-skew clock distribution network. The on-chip frequency may be higher than the Input/Output (I/O) pin bandwidth, in which case a phase locked-loop clock multiplier is needed.

Based on these seven properties, Table 1.1 compares current technologies used in microprocessor design. Complementary Metal-Oxide-Semiconductor (CMOS) circuits dominate today's IC market. N-channel Metal-Oxide-Semiconductor (NMOS) technology was used extensively in the 1970's and early 1980's. Emitter Coupled Logic (ECL) has been in

| Technology Attribute | CMOS | NMOS      | ECL       |  |

|----------------------|------|-----------|-----------|--|

| Gate speed           | Good | Fair      | Excellent |  |

| Circuit density      | Good | Excellent | Fair      |  |

| On-chip memory       | Good | Fair      | Fair      |  |

| Drive capability     | Good | Good      | Excellent |  |

| I/O bandwidth        | Good | Fair      | Excellent |  |

| Power dissipation    | Good | Fair      | Poor      |  |

| Clocking             | Good | Fair      | Good      |  |

Table 1.1 Technology Support for Microprocessor Development

use since the 1960's and is still used in small, high frequency designs. CMOS technology has dominated recent designs, even though it excels at none of the required attributes. It provides a solid technology foundation, and unlike the other technologies has no fatal weaknesses.

By early 1990 Gallium Arsenide Direct Coupled FET Logic (GaAs DCFL) had reached a level of process maturity that would support chips of microprocessor complexity.

#### **1.2** Microprocessor Density Increase Over Time

Since the introduction of the microprocessor by Intel in 1971, the continued advance of integrated circuit (IC) processing technology has allowed rapid and sustained growth in both the complexity and performance of single chip processors. Since the late 1960's, yearly lamentations of reaching fundamental limits have been raised.

Predictions for the continued improvement in technology have fallen between two extremes. In 1964 Thornton proposed the CDC 6600 system with parallel peripheral processors because it was felt that the technology of the time was reaching fundamental limits, and further increases in clock speed were not possible [Thornton70]. At the other extreme, In 1986, Sun Microsystems' Joy proposed the following estimate for processing power in Millions of Instructions Per Second(MIPS):  $MIPS = 2^{year-1984}$ . This equation predicts that processing power would double each year, beginning with 1 MIPS in 1984. The new Alpha 21164 processor from DEC does have a peak issue rate of 1.2 billion instructions per second. Although MIPS is a poor metric for comparing the performance of dissimilar processors, the Alpha could be seen as substantiating Joy's law.

In April 1965, Intel's Moore first observed that the complexity of integrated circuits was growing exponentially, doubling in transistor count every year [Moore79]. Many have since predicted this growth rate is destined to slow soon, only to be proved incorrect. It is now predicted that the final limitation on the achievable density will be economic rather than technological; fabrication facilities needed to produce ICs as dense as possible will

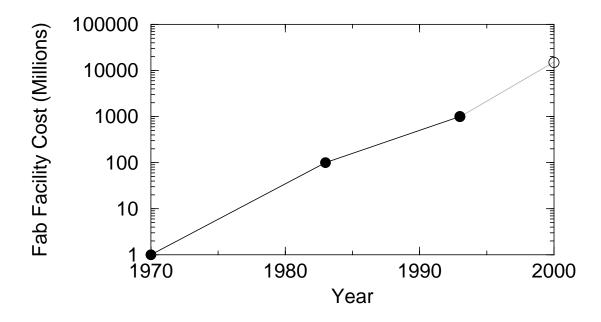

Figure 1.1 Fabrication Facility Cost

simply not be affordable [Koyima93]. Figure 1.1 plots the estimated cost of a new commodity IC fabrication line over a 30 year time span. In 1970, a typical fabrication plant cost around 1 million dollars, and each piece of fabrication equipment cost around \$50,000 [Intel93]. Today, several companies are each spending over 1 billion dollars on new plants. The cost of fabrication equipment has risen to 3 to 4 million dollars for each machine, more than the cost of an entire fab in 1970! It is projected that a new fabrication plant will cost over 10 billion dollars by the turn of the century. Such high costs limit the number of companies capable of developing the next generation of fabrication lines, because the multi-billion-dollar investments required exceed the expected return on the investment for many products. It may be that only high-margin components, such as microprocessors, will be built on the most modern lines. The large increase in cost over the past two decades has serious implications regarding the ability of a new technology to succeed in the marketplace. However, the increase in plant cost has been offset by an even larger increase in plant efficiency. The cost per area of silicon has dropped continuously, due primarily to increases in throughput allowed by larger silicon wafers.

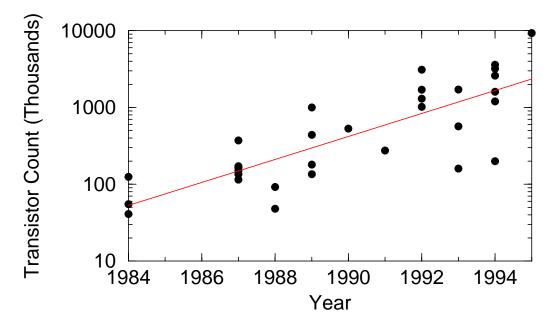

Figure 1.2 ISSCC Microprocessor Transistor Counts

The increase in fabrication plant efficiency has led to dramatic growth in the size of microprocessor chips. Figure 1.2 shows the total transistor count for processors introduced at the International Solid State Circuits Conference (ISSCC). There are three major components that have led to an increase in transistor count. First, the die size for microprocessors has grown rapidly, from 9 mm<sup>2</sup> for the 4004 in 1971 to 308 mm<sup>2</sup> for the Intel Pentium Pro processor in 1995 [Intel95]. Second, the smallest pattern capable of being reproduced on the integrated circuit, known as the feature size, has been dramatically reduced, allowing many more components to fit in the same area. The minimum feature size for the 4004 was 12 microns, and for the Pentium Pro it is 0.6 microns. Finally, newer fabrication processes provide additional metal routing layers, allowing much of the routing to occur over the top of the transistors, further reducing the area required to implement a given circuit. Together, these factors have caused a dramatic increase in the resources available for constructing processor chips.

The growth in fabrication capabilities has had a profound impact on microprocessor architecture. The continued increase in available resources has allowed many features previously seen only in large-scale computers to migrate to the desktop. Some of these features include virtual memory, execution pipelines, caches, vector processing and support for fault tolerance.

As transistor counts have increased, computer designers have sought the most effective use of these additional resources. Microprocessors have devoted these extra transistors to two primary areas: additional on-chip cache memory, and parallel functional units for added computation capability. Increasing the size of the cache can absorb any amount of extra transistors, but Olukotun has shown that the optimal cache size may not be the largest possible [Olukotun92]. As the cache gets larger, the time required for decoding the address and sensing in the RAM array increases. If a single cycle is allowed for cache access, large caches can limit the maximum operating frequency of the chip, though the miss rate is reduced. Recent research has shown that a single cycle primary cache backed up by a larger multi-cycle secondary cache gives the highest system-level performance [Farrens94, Jouppi94].

The addition of on-chip floating point units is an example of using increased resources to provide additional computational power. Additional functional units perform computation in parallel with the work of the normal execution pipeline. In the extreme, the additional functional units may replicate much or all the execution pipeline, allowing the completion of multiple instructions each clock cycle.

#### 1.3 Clock Speed Increase Over Time

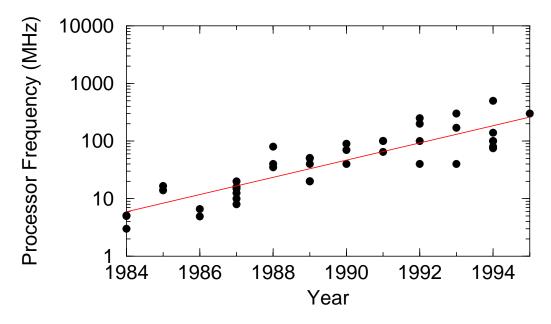

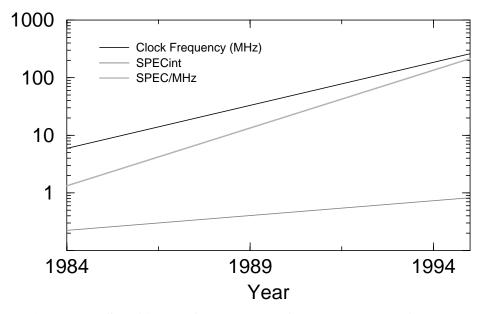

As the number of transistors in microprocessors has grown over time, the clock frequency of the microprocessors has increased significantly as well. As the minimum feature size of IC processes has shrunk, the parasitic signal loading has reduced dramatically. The reduction in area has affected performance in two ways. First, smaller transistors switch faster and have lower gate capacitance, a major contributing factor to the switching speed. Second, the size of the major components in the microprocessors has been significantly reduced, greatly reducing the parasitic loading on most signal wires. The result has been a large increase in the operating frequency of microprocessor chips. Figure 1.3 shows the clock frequency of microprocessor chips presented at the ISSCC conference over the past

Figure 1.3 ISSCC Microprocessor Clock Frequencies

ten years. Individual processors are represented by points on the graph, and the solid line gives the best exponential fit to the data. Clock frequencies have been growing at a rate of 40% per year.

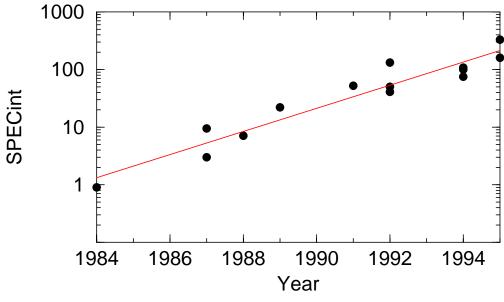

Although the raw computation frequency has risen dramatically, the system level performance has grown at an even faster rate. The most common measure of system level performance is the SPECmark, a measure of relative performance with a VAX 11/780 as the reference. Figure 1.4 presents integer SPECmark numbers for systems built from some of the chips described at ISSCC. The SPECmark numbers have been growing at a 59% yearly rate. In the past decade systems have improved in performance 100 fold.

#### **1.4 Research Project Goals**

This background of continued performance improvement sets the stage for the evaluation of GaAs processor design. When the GaAs processor project began in 1990, the fastest commercial systems were based on the 40MHz R3000 processor. At this time the goal of demonstrating a 250 MHz GaAs prototype appeared to be a significant advancement in the state of the art in processor design. Though the trends were obvious from Figure 1.2 and Figure 1.3, few people predicted the rapid increase in CPU operating frequency that has oc-

Figure 1.4 Integer SPECmark Performance

curred in CMOS processors. Current CMOS processors have far outstripped the initial goals of the GaAs processor project.

Processor performance growth has come from a combination of increased clock frequency and increased resources. Figure 1.5 shows how each component has contributed to SPECint performance. Clock frequencies have grown at 40% per year while the growth in SPECint has been 59% per year. As more resources have become available, the amount of

Figure 1.5 SPECint Performance vs. Clock Frequency Growth

work completed per clock has increased. This increase in efficiency is measured in SPEC/ MHz, and has grown at a 13% annual growth rate from about 0.2 SPEC/Mhz in 1984 to an average of 1 SPEC/MHz in 1995. The increase in SPEC/MHz has primarily resulted from the addition of superscalar execution units [Johnson90].

One premise of this research is that it will become more difficult to exploit instructionlevel parallelism as clock rates reach ever-higher levels. High Instruction Per Clock (IPC) levels are facilitated by low latency memory systems; building memory systems that provide low access latency, as measured by clock cycles, becomes difficult as CPU clock frequency is increased. This research focuses on developing a microarchitecture that can take advantage of moderate levels of instruction level parallelism without adversely affecting clock cycle time. Enhancements to the architecture to improve performance in the presence of long memory latencies are evaluated.

### **CHAPTER 2**

### The Importance of Latency Tolerance for High Clock-Rate Processors

#### 2.1 CPU-Memory Performance Discrepancy

This chapter develops an analytical model for cache behavior, and uses it to characterize two different workloads. It is shown that memory system effects will dominate processor performance if memory architectures do not change. A set of modifications to the memory system are analyzed, and their use in several current microprocessors are highlighted.

In Chapter 1, Figure 1.4, it was shown that CPU performance has increased by a factor of 100 in the past decade. In contrast, main memory speeds have improved by less than a factor of ten in the same period, making it increasingly difficult to improve system performance. As fabrication process technologies improve, CPU cycle times are decreasing rapidly. The percentage of time the CPU sits idle waiting for memory is constantly growing. To compensate for the discrepancy in operating speeds, modern systems include cache memories near the processor that operate at processor speeds [Smith82]. Not all accesses can be serviced from the cache, so some fraction of time is still spent waiting for main memory. The CDC 6600 supercomputer, introduced in 1964, had a main memory cycle time of ten cycles of 100 ns for a total of 1000 ns. Main memory accesses on the 1978 vintage minicomputer DEC VAX 11-780 required six cycles of 200 ns for a total of 1200 ns [Jouppi90]. Current RISC processors have faster memory systems; the DECstation 3100 memory accesses complete in five cycles of 62.5 ns or 312 ns. The speed discrepancy is now beginning to widen severely with the advent of 100+ MHz machines. The HP 9000/735 requires 15 cycles of 10.1 ns or 155 ns for main memory access [Johnson91].

The VAX 11/780 would run at 60% of full speed even with the cache turned off [Jouppi90]. As processor speeds continue to increase, current-generation processors run at only a small fraction of their full speeds without their caches. With caches disabled, the HP 9000/735 slows down by a factor of more than 15. The growing discrepancy between CPU and memory speeds will have a profound impact on the future of computer architecture.

The continued increase in cache miss penalty causes significant performance degradation. Faster processors, with either higher issue rate or faster clock cycle, suffer a greater performance loss than slower processors. The increase in miss penalty reduces the amount of instruction level parallelism that can be extracted from programs. Cache miss behavior differs widely by workload, with database and operating system workloads exhibiting significantly poorer performance than other typical workstation applications [Cvetanovic94, Maynard94, Nagel94]. To maintain high performance with these workloads, processor designers must change the memory system.

#### Amdahl's Law

Amdahl developed a relation explaining the performance improvement in a system when the performance of only some of the components in the system are increased [Amdahl67]. Amdahl noted that the performance of the enhanced system is dependent on both the performance boost of the enhancement and the amount of time the enhancement can be employed: an enhanced system with little performance boost gives little benefit, and a large boost must be employed a majority of the time to give a substantial improvement. Amdahl's Law expresses this in equation form as derived by Hennessy and Patterson [Hennessy90]:

$$Speedup = \frac{Time_{original}}{Time_{enhanced}}$$

(1)

$$Time_{enhanced} = Time_{original} \times \left( (1 - Fraction_{enhanced}) + \frac{Fraction_{enhanced}}{Speedup_{enhanced}} \right)$$

(2)

$$Speedup = \frac{Time_{original}}{Time_{original} \times \left( (1 - Fraction_{enhanced}) + \frac{Fraction_{enhanced}}{Speedup_{enhanced}} \right)}$$

(3)

$$Speedup = \frac{1}{(1 - Fraction_{enhanced})} + \frac{Fraction_{enhanced}}{Speedup_{enhanced}}$$

(4)

To achieve the largest speedups the improvement must provide a large performance boost, and the improvement must be used a large percentage of the time. For example, if the improvement can only be applied one half the time, then Amdahl's law says the maximum speedup for the system with the improvement is two, even if the speedup of the enhanced system is infinite. Amdahl's law shows the performance of a system is often limited by its slowest component. As microprocessors become faster, the performance becomes limited by the time needed to process cache misses.

Current microprocessors typically have between 8K and 32K bytes of on-chip cache memory. Gee simulated the SPEC benchmark suite over a wide range of possible cache configurations using MIPS R3000 traces [Gee93]. Table 2.1 shows expected cache hit rates for direct mapped caches of various sizes with 32-byte lines for this technical workload. The table shows that for larger cache sizes very low miss rates can be attained. Similar results are obtained for other cache line sizes.

Different workloads can have significantly different behaviors. Maynard reports numbers similar to Gee for the integer SPEC benchmarks running on an RS6000 simulation environment [Maynard94]. She also gives numbers for large commercial workloads that have

| Cache Size | I-Cache Hit<br>Rate | D-Cache Hit<br>Rate |

|------------|---------------------|---------------------|

| 1K byte    | 94.2                | 84.5                |

| 4K byte    | 97.1                | 92.3                |

| 16K byte   | 99.2                | 95.7                |

| 64K byte   | 99.8                | 98.3                |

| 256K byte  | 99.9                | 99.3                |

| 1M byte    | 100                 | 99.7                |

Table 2.1 Integer SPEC Cache Hit Rates

much worse cache performance. Table 2.2 shows her numbers for the TPC A transaction processing workload for a direct mapped cache with 16-byte lines.

Commercial workloads have many processes and larger executables, resulting in low hit rates for the instruction side. The tendency in these workloads is to touch many data few times, leading to much poorer data cache behavior than for the technical workloads. The minimum D-cache miss rate plateaus at a few percent, and never reaches the 99+% range of the technical workloads.

Performance is a function not only of the miss rate, but also of the miss penalty. As processors become faster, primary cache miss penalties can grow from 10 to over 100 cycles. Furthermore, superscalar machines multiply the miss penalty by the issue rate, increasing the number of instruction issue slots that have been lost.

#### System Limited by Slowest Component

The speedup equation can be used to evaluate the effects of increased clock frequency on system efficiency. Performance is determined using the concept of an average instruction, as proposed by Emer and Clark [Emer84]. The model assumes single cycle execution of instructions, with 30 percent of instructions referencing memory. This gives an average instruction that has one cycle for execution, some number of cycles for processing instruction cache misses and additional cycles for processing data cache misses. The total cache miss rate for the average instruction is the I-cache miss rate plus 0.3 times the D-cache miss rate (because the average instruction has 0.3 memory operations). A system with 95% total cache hit rate, 20 ns cycle time and 200 ns main memory would have miss penalties of 10

| Cache Size | I-Cache Hit<br>Rate | D-Cache Hit<br>Rate |

|------------|---------------------|---------------------|

| 8K byte    | 78.0                | 89.5                |

| 16K byte   | 82.0                | 92.0                |

| 64K byte   | 88.0                | 94.0                |

| 256K byte  | 96.0                | 95.5                |

| 1M byte    | 99.2                | 96.0                |

Table 2.2 TPC A Cache Hit Rates

cycles. If a scalar machine capable of completing one instruction each cycle is assumed, cache hits add no penalty, so 95% of instructions execute in a single cycle.

The 5% of accesses that miss in the cache require 10 cycles to access main memory. So the effective cycles per instruction (CPI) is:

$$CPI = Cycles_{execution} + Cycles_{Imiss} + Cycles_{Dmiss}$$

(5)

$$Cycles_{Imiss} + Cycles_{Dmiss} = (missrate_I + 0.3missrate_D) \times misspenalty$$

(6)

$$missrate_{total} = (missrate_I + 0.3missrate_D)$$

(7)

$$CPI = 1.0 + missrate_{total} \times misspenalty$$

(8)

For the configuration given above, this yields:

$$CPI = 1.0 + 0.05 \times 10 = 1.5 \tag{9}$$

Combined with the 20 ns cycle time, the 1.5 CPI gives a value of 33.3 MIPS. As described in more detail below, if the technology for the processor improved, reducing the cycle time to 10 ns, but the main memory access time remained the same, the miss penalty would double in processor cycles. With a 20 cycle miss penalty, the CPI would increase to 2.0, resulting in a processor performance of 50 MIPS. The 100% increase in CPU clock frequency would result in a system performance improvement of only 50%. According to Amdahl's Law, the maximum performance of this system could never exceed 100 MIPS, even if the processor were infinitely fast.

The equation for MIPS can be derived from Equation (8).

$$MIPS = \frac{1}{CPI \times t_c} = \frac{1}{(1.0 + missrate_{total} \times misspenaly) \times t_c}$$

(10)

Where  $t_c$  is the processor cycle time. Alternately,

$$MIPS = \frac{1}{(t_c + missrate_{total} \times t_{mem})}$$

(11)

Where t<sub>mem</sub> is the main memory access time.

As cycle time reduces toward zero, the performance becomes dominated by the cache miss behavior of the system. The performance of the machine asymptotically approaches a peak MIPS set by the main memory cycle time and the cache miss rate. Thus, with an infinitely fast machine the peak MIPS is given by Equation (12).

$$MIPS_{peak} \approx \frac{1}{missrate_{total} \times t_{mem}}$$

(12)

Even with an infinitely fast processor, the 5% of accesses that miss still take 200 ns each, giving an average miss penalty of 10 ns. This results in the maximum MIPS rate of 100MIPS. At high processor clock frequencies very low miss rates are needed to ensure hardware resources are efficiently utilized.

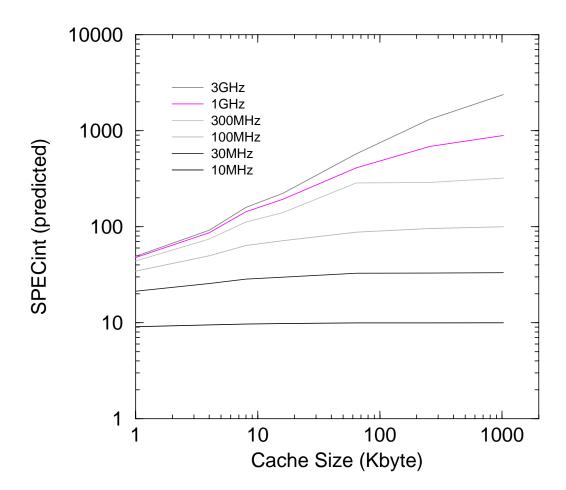

Figure 2.1 shows the estimated SPECint performance for different cache sizes and cycle times. The miss rates are estimated from published results [Gee93], and assume a 32byte line, direct mapped cache, 200 ns main memory access time, and an instruction mix that is 30% memory instructions. The cache model assumes near single cycle access times, either through a primary cache of the indicated size or a primary plus a low latency secondary cache. Advanced memory techniques, such as prefetching and nonblocking loads, are not accounted for in this simple analytical model. As will be shown Chapter 6, such techniques are needed to further improve system performance.

Several important relations are evident in Figure 2.1. First, the performance graph of slow processors is flat with increasing cache size, showing negligible performance improvement. As cycle times increase, the cache becomes a more important factor in performance. The performance plateaus at successively higher levels with larger cache sizes. At higher clock rates, more performance is gained by increasing cache size.

The estimated SPECint performance numbers indicate these benchmarks can reach high performance levels with high frequency processors and large caches. The model predicts that a 100 MHz machine could deliver 95 MIPS with a 128 K-byte cache, and a 1 GHz

Figure 2.1 Estimated SPECint Performance

machine could reach 500 MIPS with the same size cache. However, the 1GHz machine would have lost one half of its potential performance due to cache misses.

Table 2.3 compares SPECint performance predicted by Amdahl's Law with actual SPECint performance numbers [SPEC93, Rubinfeld94] for several machine organizations. Considering the crudeness of the model (its inputs are cache miss rates, processor cycle time and main memory access time), the model predicts machine performance surprisingly well. The predicted numbers are quite close, except the R3000. The R3000 estimate is less accurate because, unlike other machines listed which achieve close to 1.0 SPECint/MHz average performance, older, single issue machines like the R3000 achieve only about 0.75 SPECint/MHz, so the model overestimates their performance. Much of the lost performance in such processors is in NOP instructions used to pad out load-use delays and branch slots. On average, about 20% of the instructions executed are NOPs; this would account for

| Processor   | Clock (ns) | Cache<br>(int,ext) | SPECint Pre-<br>diction | SPECint<br>Actual |

|-------------|------------|--------------------|-------------------------|-------------------|

| R3000       | 30         | 0,64K              | 32                      | 20.9              |

| Pentium     | 10         | 8K,256K            | 95.5                    | 100               |

| Alpha 21064 | 5          | 8K,1M              | 195                     | 170               |

| Alpha 21164 | 3          | 96K,4M             | 320                     | 330               |

Table 2.3 Predicted SPECint Performance

about half of the discrepancy. Wide issue, superscalar machines like the SuperSPARC would have their performance underestimated by the model, since they are able to complete more than one instruction per cycle. Nevertheless, the model is useful for illustrating the relationship between clock speed, memory characteristics and system performance.

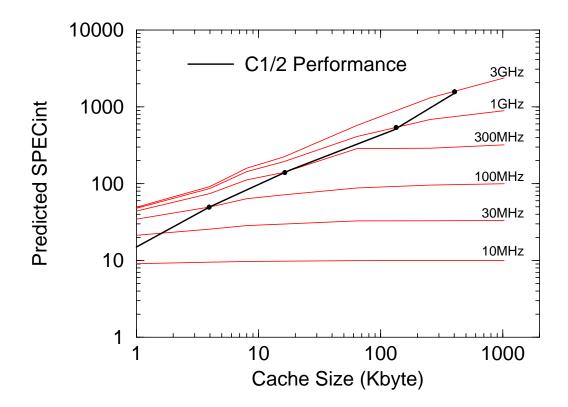

Using the analytical cache model, the amount of cache necessary at each clock frequency to achieve 50% of maximum performance can be calculated for the SPEC benchmarks. This value, called the  $C_{1/2}$  value and is analogous to the  $N_{1/2}$  value that measures the vector length needed to achieve 1/2 the peak performance in a vector machine [Hennessey90].

Figure 2.2 shows that the growth in the  $C_{1/2}$  value with increasing CPU clock frequency is geometric. A machine with a 100MHz clock needs only 4K of cache to achieve 50% of maximum performance. As clock frequencies near 1 GHz, 128K-byte of low latency cache is needed to maintain performance at 50% of maximum levels. A 1GHz machine like this would deliver 700SPECint.

Figure 2.2 Cache Size Resulting in 50% of Peak Performance

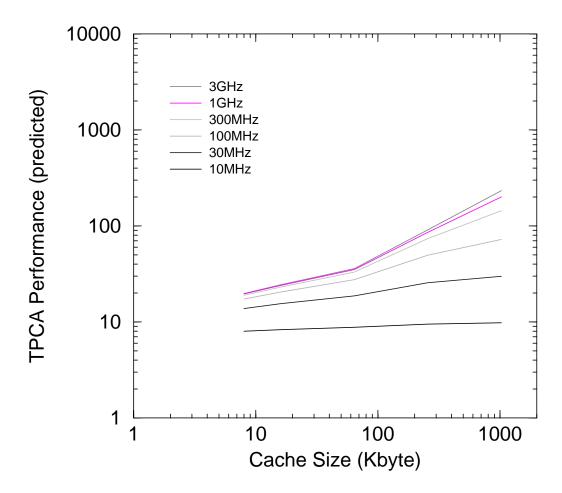

Similar predicted performance graphs can be generated for other workloads. Figure 2.3 shows relative performance improvements that can be obtained with various cache sizes and clock frequencies on the TPCA benchmark. The estimated performance for this workload is much more modest than for the SPECint workload. In fact, with less than 128K-bytes of cache, the performance improves little for clock frequencies above 100MHz.

#### 2.2 Cache Miss Characterization

Caches work by exploiting both spacial and temporal locality. Instruction and data accesses have different behaviors; tuning the parameters for the different caches can provide a substantial performance boost. In general, instruction stream accesses exhibit more spatial locality than data accesses. Cache misses can be grouped into three broad categories: Compulsory, Conflict and Capacity. Different design solutions are needed to take advantage of the different classes of cache miss.

Figure 2.3 Relative TPCA Performance

#### **Compulsory Misses**

A compulsory miss occurs the first time a memory location is referenced. Because no previous reference has been made there is no way the cache could hold the data, and a miss results.

Memory accesses are often spatially clustered, especially the instruction accesses. If a word has been accessed, it is likely that a nearby word will be accessed. This property can be exploited by increasing the line size of the cache and fetching multiple words on each cache miss. In a cache having a longer line size, only the first access to the line causes a miss. This is especially useful for instructions, because most accesses are sequential. Except for control flow instructions, the next address is guaranteed to be the next sequential memory location. For small values of N, increasing the line size by a factor of N reduces the compulsory miss rate by nearly N [Smith82].

There is a limit to how much the line size should be increased. Increasing the line size reduces the number of lines in the cache, slightly increasing the miss rate. Not all words in a cache line will be accessed; if the line becomes too long a substantial fraction of the typical line will never be used. Fetching the unused portion only adds overhead to the time needed to access the required location. Lengthening line also increases the time needed to fetch and fill the line in the cache; and increases the bandwidth needed from the memory system.

#### **Conflict Misses**

Conflict misses occur when two or more memory locations map to the same entry in the cache. There are many possible ways to map data in a cache. The most flexible mapping is known as fully associative. In a fully-associative cache, each cache line is free to occupy any cache location. A content-addressable tag memory determines which cache entry holds a requested data item. At the other extreme of mapping freedom is a direct-mapped cache. In a direct-mapped cache, each item can map to only one possible cache location. Set-associative caches lie between these two extremes in mapping freedom.

Mapping conflicts cause increased misses when compared to fully-associative caches Conflict misses can be reduced by increasing the associativity of the cache. Direct-mapped caches suffer the most from conflict misses, and can even suffer pathological access patterns where the cache hit rate drops to zero.

Cache hit rate will increase with increases in associativity, due to the reduction in conflict misses. However, most of the performance benefit of increased associativity can be achieved with low degrees of set-associativity, such as 2 or 4 way set associativity. The added time needed to select the proper set may extend the critical path, removing any performance benefit gained by higher hit rates [Hill88].

#### **Capacity Misses**

Capacity misses occur when the working set size of the data exceeds the size of the cache. If the working set is too large, data must be evicted from the cache to make room for the newly requested items. This is required regardless of the associativity of the cache.

When this data is accessed again, it will be brought back into the cache, displacing some other item. If the working set is too large to fit in the cache, the only solution is to increase the cache size.

# 2.3 Memory system enhancements to maintain performance

The memory model used in the performance estimation in Section 2.1 assumed two restrictions, the removal of which can significantly improve processor performance. The first restriction is that memory cannot be accessed before it is requested by the processor. The second is that all cache accesses are processed serially. Prefetch hardware removes the first restriction and nonblocking loads remove the second restriction.

#### 2.3.1 Prefetching

One way to maintain high performance in a deeply-pipelined machine with a high clock rate is to eliminate cache misses. Prefetching brings data on chip before it is referenced by the processor. When prefetched data is referenced, the data can be quickly supplied, eliminating the long latency associated with an off-chip access.

#### **Software Prefetch Methods**

Mowry investigated how prefetch instructions can be inserted into scientific code by the compiler [Mowry92]. This method works well for loop-based programs with regular and predictable access patterns, such as data accesses in scientific programs.

There are problems with this method when the end of the loop is reached. The inserted prefetch instructions must not access data outside the allowed array range. To do so could cause memory access exceptions and poor performance. The main drawback to software prefetch methods is that they cover only a subset of possible applications, and it is difficult to predict the access patterns of integer code [Klaiber91, Chen94].

While high performance can only be achieved through a combination of hardware and software methods, this thesis is primarily concerned with hardware solutions for improving performance.

#### **Prefetch into Cache**

Prefetching can be built entirely in hardware, without software support [Fu92]. The prefetched instruction or data can be written into either the primary cache or to an auxiliary memory buffer. However, there are drawbacks to both approaches. Prefetched items will not always be used; unused items increase bus traffic without improving performance. Prefetch items written into the cache may displace real instructions or data that will be needed by the application, thus causing additional cache misses. Pierce has shown that this is usually not a problem for the instruction stream [Pierce94]. In the other case, when prefetched items are written into an auxiliary memory rather than into the cache, extra cycles may be needed to route the data or instructions from the auxiliary memory to the execution pipeline.

#### **Stream Buffers**

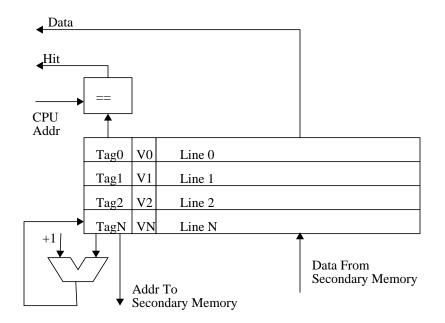

Jouppi has proposed a hardware-based prefetching scheme called the stream buffer [Jouppi90]. A stream buffer contains an address tag, a tag comparator, an incrementor and a few cache lines of data. Figure 2.4 is a diagram of a typical stream buffer organization.

Figure 2.4 Stream Buffer Organization

The hardware resources needed are modest, the primary cost being the memory needed to buffer the cache lines.

After a cache miss, the address of the next cache line is loaded into the stream buffer line 0 entry. That line is requested from the secondary memory system, and when the data returns, the line is marked valid. Subsequent cache misses compare the requested address with the tag stored in line 0. If the request matches the address tag, the data has already been requested, and can be sent to the requesting unit when it arrives from secondary memory. After supplying the data to the requesting unit the stream buffer pops the top entry from line 0, moving the successive entries up one position.

With long-latency memory systems, it may not be possible to eliminate the fetch latency prefetching single cache lines. Additional cache lines can be fetched during times when the memory bus would otherwise be idle, allowing the fetch address to get many lines ahead of the currently requested address. To minimize cost, only one comparator is used; addresses must advance to line 0 before they can be matched.

#### **Prefetching allows smaller I-cache**

I-cache miss rates can be substantially reduced with the addition of even a small prefetch buffer. Jouppi's results show that a stream buffer having only a few entries can often provide the same performance as doubling of the instruction cache size [Jouppi90]. Because of the sequential nature of instruction execution, about 70% of accesses to new cache lines reference the next sequential cache line.

The primary drawbacks to prefetching are the added complexity and memory bandwidth needed. Not all the memory requested by hardware prefetching will be used. If too much additional prefetching traffic is generated, the prefetch instructions and data will interfere with the normal cache miss memory traffic, possibly reducing performance.

#### 2.3.2 Nonblocking memory operations

A primary assumption in the performance estimates of Table 2.3 is that cache misses are processed serially. This leads to a large amount of dead time where instructions are not issued. In reality, cache misses often appear in closely associated groups, often to the same cache line. Kroft proposed a method for allowing multiple cache misses to be processed in parallel [Kroft81]. He noted that if processing could continue after a cache miss, it would be possible to detect additional misses and begin their servicing in parallel with the misses already in progress. This method is known as nonblocking-load or lockup-free caching.

This technique typically uses a small number (usually between two and eight) of nonblocking load registers. Kroft's results showed that his scheme rarely needed more than three nonblocking load registers. This is, of course, dependent on the processor issue model.

In an in-order issue machine, processing continues after the first cache miss until an operation that uses the result of the load is detected. With more sophisticated out-of-orderissue machines, processing can continue even past these dependent instructions until all available resources have been consumed. An out-of-order issue machine will stall when there are no more unexecuted instructions in the instruction queue, or when there are no more nonblocking load registers available to queue a nonblocking load request.

## 2.4 Elements of Current Microprocessors

Improvements in microprocessor performance have had two primary sources, technological improvements and architectural improvements. In 1980, microprocessors were not pipelined, contained no on-chip cache and required multiple cycles to complete each instruction. The increased transistor resource budgets of recent years have allowed each of these performance limitations to be corrected.

This section reviews some recent microprocessors to see how they address issues in high speed design; the use of instruction level parallelism, in particular, is described. Methods for maintaining a high clock rate will also be discussed. Current microprocessors can be characterized by issue width, number of memory operations performed each cycle, issue model, completion model and degree of nonblocking memory operations supported.

#### 2.4.1 R4400

The R4400 is the latest 64-bit R4000 family processor from the MIPS technology division of SGI. It is functionally the same as the R4000, but with larger on-chip caches, 16K each for instructions and data. The R4400 is a single issue, superpipelined design, with an eight-stage pipeline [Heinrich94]. The processor emphasizes clock rate over parallel issue, and operates at up to 200 MHz. Cache accesses take two internal CPU cycles. Because of the long cache access delay, a significant number of cycles are lost to branch delays and data dependencies. Hardware load interlocks are necessary to ensure correct operation because the load delay is longer than a single cycle. The chip issues and completes instructions in order, and has no branch prediction capability, but does add several instruction set extensions to minimize the impact of branch delay slot NOP instructions.

## 2.4.2 R8000

The R8000 TFP processor is a two-chip decoupled implementation of the R4000 architecture [Hsu94]. The processor runs at a relatively slow 75 MHz, but the integer and floating point units are capable of executing up to 4 instructions each cycle, for a maximum throughput of 300 MIPS or 300 MFLOPS. No more than four instructions can issue in any cycle. The basic R4000 instruction set was refined to add an IBM multiply-add style instruction that is useful in vector codes.

The processor features a unique second-level cache architecture where all floatingpoint data is cached only in a large, pipelined secondary cache. Integer data and all instructions reside in separate 16K-byte caches on the integer chip. The integer and floating point units communicate via a set of interface queues. To speed instruction fetch, branch prediction is integrated into the primary instruction cache hardware. Each cache line contains the predicted next cache index, which can be used immediately to fetch the next cache line; no branch offset calculation is required.

#### 2.4.3 R10000

The R10000 (also known as the T5) is the next processor to be introduced by the MIPS

Technology division of SGI. This processor is a significant departure from the R4400, with much wider issue and out-of-order instruction issue and completion capability. The R10000 fetches four instructions per cycle and issues them to separate queues for integer, memory, and floating point operations. To make best use of available memory bandwidth, the processor supports up to 4 outstanding cache misses. Unlike many other processors, however, the R10000 does not stall when an instruction references the result of a pending load. Instead, it scans the queues for other memory instructions that are ready to issue, and issues these instructions out of program order while waiting for the requested results.

The processor uses register renaming with a pool of 64 physical registers to map the 32 logical registers. When an exception or branch miss occurs, the previous machine state can be quickly recovered by resetting the register mapping information to a previously saved value.

## 2.4.4 SuperSPARC

The SuperSPARC (also known as Viking) processor was the fastest 32-bit SPARC processor from Sun Microsystems in 1994. It emphasizes instruction level parallelism over clock rate, issuing up to three instructions simultaneously from a four-instruction window.

There are two primary manifestations of the emphasis on parallelism. First, the processor can perform two sequential ALU operations each clock cycle. The processor contains three ALUs, arranged in a tree. The first level of the tree has two ALUs in parallel, each of which can accept an ALU operation if the two operations are independent. If the second operation is dependent on the result of the first, the first result can be fed directly to a third ALU positioned after the first two. Second, there is no delay after a load instruction before the data can be used. This requires that a complete cache access must be completed within one clock cycle. The result of these decisions is that more parallelism is available, but at a price in clock frequency and performance.

The SuperSPARC processor achieves one of the highest SPECmark ratings for a given operating frequency. However, its features dramatically reduce the maximum operating frequency of the processor. The chip was originally designed to operate at 50 MHz, but vol-

ume shipments were originally only available at 36 MHz. This speed was less than half that of its contemporary processors.

## 2.4.5 UltraSPARC

UltraSPARC corrects most of the poor design decisions made in the SuperSPARC. The cascaded ALUs have been eliminated in this quad-issue chip, and the cache access no longer sets the processor operating frequency.

Like the R8000, the UltraSPARC caches the predicted next address field for each cache line, and tags each cache line with bits to indicate the branch type, allowing branches to be issued each cycle with no address calculation delay. A unique feature of the UltraSPARC is the instruction set support for image processing primitives. Like the Motorola 88110, UltraSPARC defines a set of graphics instructions and data types that can be processed in Single Instruction Multiple Data (SIMD) function units. Although the chip can issue up to four instructions in a cycle, the fourth instruction must be a branch or floating point instruction.

The processor supports nonblocking loads; up to nine loads and eight stores can be pending. Support for a large, pipelined secondary cache is contained on chip. Because of the large size of the chip, 3.8 million transistors, the process has been switched from the BiCMOS used to fabricate the SuperSPARC to a standard CMOS process.

## 2.4.6 Intel Pentium Processor

The Pentium Processor contains a pipeline constructed for the efficient execution of the X86 instruction set [Schutz94]. This processor is a good example of how to build a fast pipelined CISC processor. The Pentium processor executes in hardwired logic a subset of the X86 architecture, and implements the remainder in microcode. Most simple operations execute in a single clock cycle, and two instructions can be issued each clock if there are no instruction dependencies and the instructions are of the proper types to be paired.

To support two simultaneous data accesses in parallel, the data cache is divided into 8 banks. If two requests map to different banks, the accesses can proceed in parallel. Since bank conflicts are rare, this design provides nearly the performance of a dual-port cache at

much lower cost. The processor issues and completes instructions in-order.

## 2.4.7 AMD K5

The AMD K5 processor is a superscalar implementation of the X86 architecture [Halfhill94]. Unlike the Pentium processor that features an in-order dual-issue CISC pipeline, the K5 dynamically translates the X86 instruction stream into fixed-length RISC-like instructions, that are executed on an out-of-order quad-issue RISC pipeline.

This design process made extensive use of CAD tools. The datapath blocks were full custom layouts, but much of the control logic was generated by logic synthesis tools from a behavioral language description and placed and routed automatically.

Instructions are flagged in the I-cache to determine the boundaries of variable length instructions. Instructions are issued to a set of reservation stations at each function unit, where they may be executed out of order. Out-of-order completion with precise exception resolution is implemented using a 16-entry reorder buffer. Instructions complete out of order into the reorder buffer, and are then written from the reorder buffer into the register file in sequential order. Like the UltraSPARC and R8000, the K5 uses in-cache next address caching to predict branches. The K5 also uses a 1 bit dynamic branch prediction.

#### 2.4.8 Motorola 88110

The 88110 is the last processor of the 88K family from Motorola [Diefendorff92]. It has a regular instruction set and dual-issue capability. The 88110 has ten independent functional units, including two integer ALUs and two graphics units. The graphics units perform SIMD operations on many pixels at once. The 88K architecture specifies a unified integer and floating point register set, which severely restricts the design options for a superscalar machine, and the 88110 designers expended significant effort working around this architectural bottleneck, adding a second complete register file for the floating point operands.

Most simple operations in the 88110 complete in three clock cycles using a 4-stage pipeline. Loads and floating point operations require additional cycles. A register file scoreboard [Thornton70] keeps track of when instruction operands are available, and de-

lays issue of an instruction until all of the input operands are ready.

A history buffer is used to record the old register contents so they can be restored after an exception. This method is viewed as inferior to other methods such as register renaming and reorder buffers used on more modern designs, primarily because of the time required to restore the machine after an exception or branch missprediction [Diefendorff92]. Exceptions cause little problem because they are rare, but restoring the state after branch misspredictions results in excessive overhead. Misspredicted branches are quite common, causing many cycles to be lost to state recovery using the history buffer.

A high-speed system bus supplies data for the 8K-byte on-chip instruction and data caches. The split transaction bus is 64 bits wide and supports bus snooping and critical-word-first requests. Although the 88110 is the last 88K processor, the system bus is being used on future Motorola PowerPC processors.

## 2.4.9 IBM/Motorola PowerPC 604

The PowerPC 604 is a high-end 32-bit PowerPC chip [Song94]. It makes extensive use of reservation stations, out-of-order issue, and out-of-order completion to achieve a high execution rate at a relatively low clock frequency.

The PowerPC architecture is an extension of the IBM RS6000 architecture, and features multiple register sets for integer, floating point and conditional operations. The separate register sets allow instruction fetch processing to be separated from the rest of the integer execution unit; all program counter processing is performed by a separate instruction fetch unit. Separating the processor into multiple independent units exposes more instruction level parallelism.

The PowerPC 604 supports out-of-order instruction issue, and uses a reorder buffer and rename registers to maintain precise exceptions. The memory system is nonblocking, supporting up to four concurrent cache misses. The system I/O uses a split transaction bus to overlap multiple bus transactions.

#### 2.4.10 DEC Alpha 21064

The first DEC Alpha processor, the 21064, was announced at the ISSCC conference in 1992 [Dobberpuhl92]. With its 200 MHz clock speed and 64-bit architecture, this processor lead the competition in performance. The Alpha processor has several unusual design features, due primarily to the requirement that the design should be able to scale in performance over 25 years. The design is clean, with few first implementation artifacts. The machine is superscalar, but with restrictive issue rules. Two instructions may issue each cycle, but the instructions must be from different classes: integer operation, floating point operation, branch or memory.

Some of the unusual design attributes include the lack of byte load and store instructions and the maintenance of precise exceptions through software synchronization instructions. Another unusual feature of the 21064 is the clocking scheme. A true-single-phase clock scheme is used with a single global clock wire driven by a very large clock buffer. One phase uses latches that are transparent when the clock is high, and the opposite phase latches are transparent when the clock is low. This scheme is only possible in complementary technologies. The clock buffer alone dissipates 9 W!

# 2.4.11 DEC Alpha 21164

The current performance leader is the next DEC Alpha chip, the 21164 [Rubinfeld94]. This chip achieves its performance through a high clock rate, simple quad-issue model and large two-level on-chip cache. The two-level cache was adopted to reduce the latency to the smaller first-level instruction and data caches. The 8K-byte size of the primary caches allows them to be accessed in a single cycle, one cycle faster than in the 21064. The smaller cache latency greatly reduces stall cycles. To provide low miss rates, the fast primary caches are backed up by an on-chip 96K-byte three-way set-associative secondary cache. Another benefit of the two-level on-chip cache hierarchy is that the primary data cache is small enough to be fully dual ported, allowing simultaneous access from both integer pipelines. The chip includes hardware prefetch support for instructions; the processor can run at full speed from the secondary cache with the help of these buffers.

| Processor  | Date | Tran<br>Count | Issue<br>Width<br>(I.M.F) | Issue Model  | Completion<br>Model | Non-<br>blocking<br>Load |

|------------|------|---------------|---------------------------|--------------|---------------------|--------------------------|

| R4400      | 1993 | 2.2M          | 1(1.1.1)                  | In-Order     | In-Order            | No                       |

| TFP        | 1994 | 2.6M          | 4(2.2.4)                  | In-Order     | In-Order            | No                       |

| T5         | 1995 | 6.8M          | 4(2,1,2)                  | Out-of-Order | Out-of-Order        | Yes                      |

| SuperSPARC | 1992 | 3.1M          | 3(2,1,1)                  | In-Order     | In-Order            | No                       |

| UltraSPARC | 1995 | 3.8M          | 4(2,1,2)                  | In-Order     | Out-of-Order        | Yes                      |

| Pentium    | 1993 | 3.1M          | 2(2.2.1)                  | In-Order     | In-Order            | No                       |

| K5         | 1995 | 4.3M          | 4(2.2.2)                  | Out-of-Order | Out-of-Order        | No                       |

| 88110      | 1992 | 1.3M          | 4(2.1.2)                  | In-Order     | Out-of-Order        | No                       |

| 604        | 1994 | 3.6M          | 4(3.1.1)                  | Out-of-Order | Out-of-Order        | Yes                      |

| 21064      | 1992 | 1.68M         | 2(1,1,1)                  | In-Order     | In-Order            | No                       |

| 21164      | 1995 | 9.3M          | 4(2.2.2)                  | In-Order     | In-Order            | Yes                      |

Table 2.4 Current Processor Characteristics

The 21164 is an in-order issue, in-order completion machine. To counteract the effects of growing memory latency, the processor supports nonblocking loads. Up to six primary data cache line fills can be pending, with as many as 21 load instructions waiting for the data. Instruction issue continues until an instruction references the result of an outstanding load miss.

Table 2.4 summarizes the features of the different machines described previously. The capabilities have progressed from scalar, in-order machines to superscalar machines supporting multiple memory references each cycle and nonblocking loads and out-of-order completion. While the latest machines are quad issue, only the PowerPC 604 supports more than two simultaneous integer operations. The other machines support issue classes, and require that the instruction stream be of the proper class mix to maintain maximum issue rate. Only two machines have added out-of-order instruction issue, but all recent machines have added support for nonblocking loads or out-of-order completion.

# 2.5 Computational Efficiency and Delivered Performance

Increasing processor clock rates without increasing memory speed proportionally re-

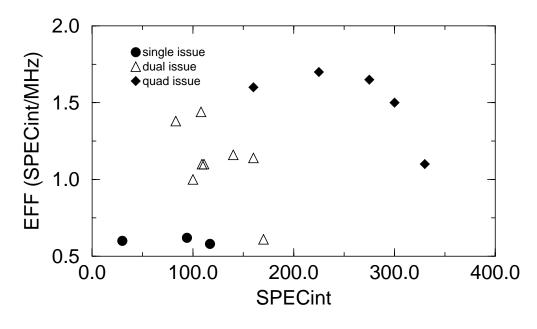

Figure 2.5 Correlation of Efficiency and SPECint Performance

duces the benefit of multiple instruction issue. Figure 1.5 showed the contribution of IPC and clock frequency to SPECint performance. Average instruction issue rate has been shown to track the SPECint performance of a processor divided by the clock frequency of the processor (SPECint/MHz). To date, clock frequency has been the major contributor to performance. Will this continue to be the case in the future?

Figure 2.5 shows the changes in performance and computational efficiency as measured by SPECint/MHz. Three machine types are shown: single issue, dual issue and quad issue. Three distinct regions of operation are seen in the figure. Single issue machines achieve nearly constant performance irrespective of architecture. These machines get about 0.6 SPECint for each MHz of clock frequency. The most effective way to speed up a single issue machine is to speed up its clock.

There is no clear optimal design for the dual issue machines. The performance of the dual issue machines is not correlated with the computational efficiency; based on the data points in Figure 2.5, both flexible instruction issue and higher clock rates are equally valid methods of improving performance of a dual-issue processor. Simpler machines can be brought to market faster than complicated machines.

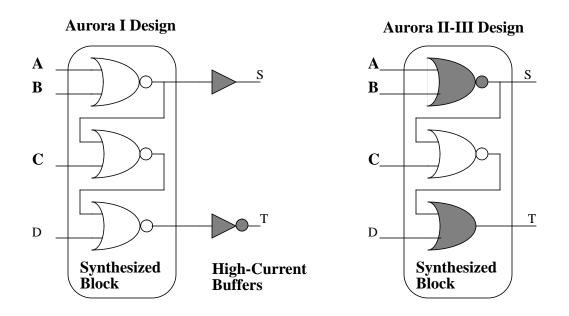

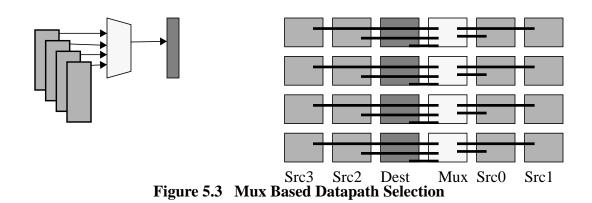

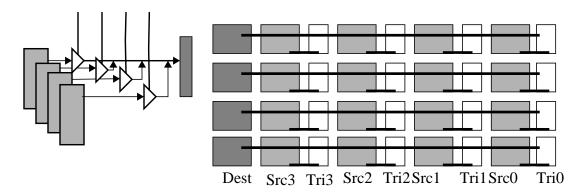

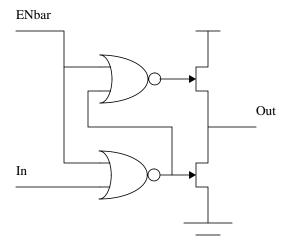

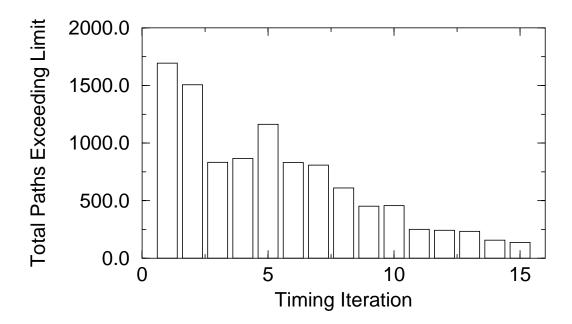

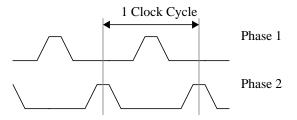

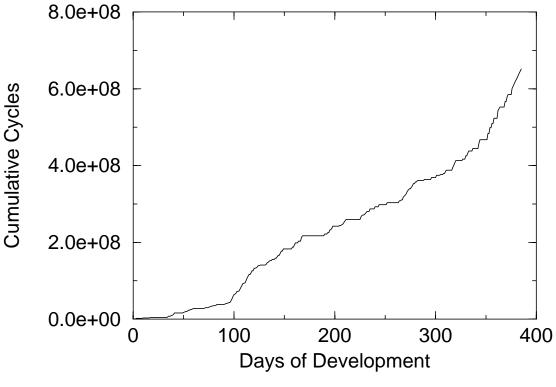

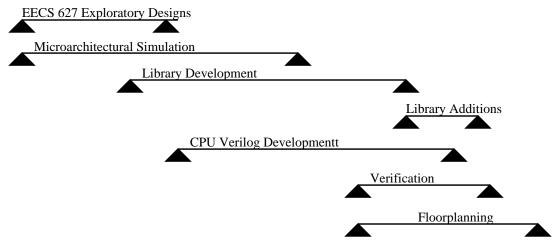

With the recent announcement of the next generation processors from several vendors, there is now sufficient data to speculate on quad-issue machine design issues. The clock rates for these machines continues to climb. The increased speed mismatch between the processor and memory system has reduced the ability of these processors to take advantage of additional parallel execution units. The quad issue machines have twice as many execution unit as the dual issue machines, but achieve a SPECint/MHz only 30% better than the dual issue machines. To compensate for increasing memory system effects, all the quad issue machines have added nonblocking memory operations.