# ARCHITECTURE AND ANALYSIS FOR NEXT GENERATION MOBILE SIGNAL PROCESSING

$\mathbf{b}\mathbf{y}$

#### Mark Woh

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2011

#### Doctoral Committee:

Professor Trevor N. Mudge, Chair Professor David Blaauw Professor William Martin Associate Professor Scott A. Mahlke Professor Chaitali Chakrabarti © Mark Woh 2011 All Rights Reserved

### **ACKNOWLEDGEMENTS**

This dissertation would not have been possible without the guidance and support of many people. First, and foremost, I would like to give thanks to my advisor, Professor Trevor Mudge. Throughout my Ph.D. he has given me support and encouragement through thick and thin. His guidance has helped me overcome many hurdles that i have encountered. Without him, this dissertation would not be possible. I would also like to thank Professors Scott Mahlke and Chaitali Chakrabarti. Without their tireless effort and help, my research would not be possible. Both have put in countless hours to develop ideas and help complete my research.

I would like to thank ARM Ltd and especially Krisztian Flautner for not only funding my research but also providing me with the valuable insight that has gotten me this far. Without the their trust and confidence in my work, I would not have gotten this far.

I would also like to thank my thesis committee members, Professors David Blaauw and William Martin. They have given their time and provided me with valuable insights which have helped me improve my thesis.

The research presented in this dissertation also would not be possible without the

support and encouragement of many of my colleagues. In particular, Dr. Yuan Lin, Dr. Sangwon Seo and Dr. Hyunseok Lee have assisted me in virtually every aspect of my graduate school life: running experiments, refining ideas, writing papers, and even picking me up when i was stranded in Auburn Hills.

I would also like to thank all of my colleagues in EECS. Many of whom I've discussed ideas with for countless hours. Their support not only as a colleague but also as a friend were crucial to my graduate school experience. I'd like to personally thank Hyunseok Lee, Amir Hormati, Shuguang Feng, Ronald Dreslinski, Geoffrey Blake, Ganesh Dasika, Shantanu Gupta, Amin Ansari, Mojtaba Mehrara, Steven Pelley, David Meisner and Hyounkyu Cho.

Finally, I would like to thank my family and long time friends for their support, encouragement, and advice. Without them I would not have enough strength to complete this long journey.

# TABLE OF CONTENTS

| ACKNOWLE        | DGEMENTS                                                   | ii   |

|-----------------|------------------------------------------------------------|------|

| LIST OF FIG     | URES                                                       | vii  |

| LIST OF TAB     | BLES                                                       | xii  |

| ABSTRACT        |                                                            | xiii |

| CHAPTERS        |                                                            |      |

| 1 Introd<br>1.1 | uction                                                     | 16   |

| 2 Overvi        | iew of Processor Designs for Mobile Software Defined Radio | 7    |

| 2.1             | SDR Overview                                               | 10   |

| 2.2             | Workload Profiling and Characterization                    | 11   |

|                 | 2.2.1 The W-CDMA Physical Layer Processing                 | 11   |

|                 | 2.2.2 W-CDMA Workload Profiling                            | 15   |

| 2.3             | Architecture Design Trade-offs                             | 18   |

|                 | 2.3.1 8-bit and 16-bit Fixed-point Operations              | 19   |

|                 | 2.3.2 Vector-based Arithmetic Computations                 | 19   |

|                 | 2.3.3 Control Plane versus Data Plane                      | 20   |

|                 | 2.3.4 Scratchpad Memory versus Cache                       | 20   |

|                 | 2.3.5 Algorithm-Specific ASIC Accelerators                 | 21   |

| 2.4             | Baseband Processor Architectures                           | 22   |

| 2.5             | SODA Processor                                             | 23   |

| 2.6             | Other SIMD-based Architectures                             | 27   |

|                 | 2.6.1 EVP                                                  | 27   |

|                 | 2.6.2 DXP                                                  | 28   |

|                 | 2.6.3 TigerSHARC                                           | 28   |

|                 | 2.6.4 MuSIC-1                                              | 29   |

|                 | 2.6.5 Sandblaster                                          | 30   |

|                 | 2.6.6 SIMT                                                 | 30   |

| 2.7             | Reconfigurable Architectures                               | 31   |

|   |            | 2.7.1 ADRES                                                      |

|---|------------|------------------------------------------------------------------|

|   |            | 2.7.2 Montium                                                    |

|   |            | 2.7.3 Adapt2400 ACM                                              |

|   |            | 2.7.4 XiRisc                                                     |

|   | 2.8        | Conclusion                                                       |

| 3 | From S     | SODA to Scotch: The Evolution of a Wireless Baseband Processor 3 |

| 0 | 3.1        | Architecture Overview                                            |

|   | 0.1        | 3.1.1 SODA Architectural Overview                                |

|   |            | 3.1.2 Ardbeg Architecture                                        |

|   | 3.2        | Architectural Evolution: SODA to Ardbeg                          |

|   | 0.2        | 3.2.1 Optimized Wide SIMD Design                                 |

|   |            | 3.2.2 LIW SIMD Execution                                         |

|   |            | 3.2.3 Application Specific Hardware Acceleration                 |

|   | 3.3        | Results and Analysis                                             |

|   | 0.0        | 3.3.1 Wireless Protocol Results                                  |

|   |            | 3.3.2 Wireless Algorithm Analysis                                |

|   | 3.4        | Conclusion                                                       |

|   | 0.1        | Conclusion                                                       |

| 4 | The N      | ext Generation Challenge for Software Defined Radio 60           |

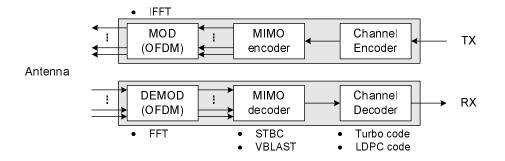

|   | 4.1        | 4G Physical Layer                                                |

|   |            | 4.1.1 OFDMA                                                      |

|   |            | 4.1.2 MIMO                                                       |

|   |            | 4.1.3 Channel Encoder/Decoder                                    |

|   | 4.2        | Computational Analysis                                           |

|   |            | 4.2.1 Baseline Architecture                                      |

|   |            | 4.2.2 Workload Profile                                           |

|   |            | 4.2.3 Computational Patterns                                     |

|   | 4.3        | Architectural Implications                                       |

|   | 4.4        | Summary                                                          |

| _ | A.1 .      |                                                                  |

| Э |            | thmic Analysis and Architectural Implications of the Next Gen-   |

|   |            | n Software Defined Radio                                         |

|   | 5.1        | SDR Processors                                                   |

|   | 5.2        | 4G Wireless Kernels                                              |

|   |            | 5.2.1 Fast Fourier Transforms (FFT and IFFT)                     |

|   |            | 5.2.2 Space Time Block Codes (STBC)                              |

|   |            | 5.2.3 Vertical Bell Laboratories Layered Space-time 94           |

|   | <b>r</b> 0 | 5.2.4 Low Density Parity-Check Codes (LDPC) 9                    |

|   | 5.3        | Methodology                                                      |

|   | 5.4        | SIMD Width Analysis                                              |

|   | 5.5        | Register Access Analysis                                         |

|   | 5.6        | Summary                                                          |

| 6 | Multir     | nedia Algorithms                                                 |

|        | 6.1    | H.264 Algorithm Analysis                                    |

|--------|--------|-------------------------------------------------------------|

|        | 6.2    | H.264 Architectural Implications                            |

|        |        | 6.2.1 Multiple SIMD Widths                                  |

|        |        | 6.2.2 Diagonal Memory Organization                          |

|        |        | 6.2.3 Bypass and Temporary Buffer Support                   |

|        |        | 6.2.4 Fused Operation                                       |

|        |        | 6.2.5 Programmable Crossbar                                 |

| 7      | Low P  | ower SIMD Architectures using a Scalable SRAM Based Swizzle |

|        |        | onnect                                                      |

|        | 7.1    | Related Works                                               |

|        | ,,,    | 7.1.1 Crossbars                                             |

|        |        | 7.1.2 Benes Network                                         |

|        |        | 7.1.3 Banyan Network                                        |

|        | 7.2    | XRAM Fundamentals                                           |

|        | 1.2    | 7.2.1 XRAM configurations                                   |

|        |        | 7.2.2 Summary of XRAM                                       |

|        | 7.3    | Case Studies                                                |

|        | 1.5    |                                                             |

|        |        | 7.3.1 FFT Engine                                            |

|        | 7.4    | *                                                           |

|        | 7.4    | $\Theta$                                                    |

|        |        | 7.4.1 Multi-core Interconnect                               |

|        |        | 7.4.2 Memory Interconnect                                   |

|        |        | 7.4.3 Reliability                                           |

|        | 7.5    | Conclusion                                                  |

| 8      | AnySF  | P: Anytime Anywhere Anyway Signal Processing 1              |

|        | 8.1    | Mobile Signal Processing                                    |

|        |        | 8.1.1 Overview of Benchmarks                                |

|        |        | 8.1.2 Algorithm Analysis                                    |

|        | 8.2    | AnySP Architecture                                          |

|        |        | 8.2.1 AnySP PE Design                                       |

|        | 8.3    | Results and Analysis                                        |

|        |        | 8.3.1 Methodology                                           |

|        |        | 8.3.2 Algorithm-Level Results                               |

|        |        | 8.3.3 System-Level Results                                  |

|        | 8.4    | Related Work                                                |

|        | 8.5    | Summary                                                     |

| 9      | Conclu | usion                                                       |

| Э      | 9.1    | Summary                                                     |

|        | 9.1    | Future Work                                                 |

|        | 9.2    | rudule WOIK                                                 |

| BIBLIC | )GRA   | <b>PHY</b>                                                  |

# LIST OF FIGURES

| Figure |                                                                                                                                                                                                                                                                                                                                                                           |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

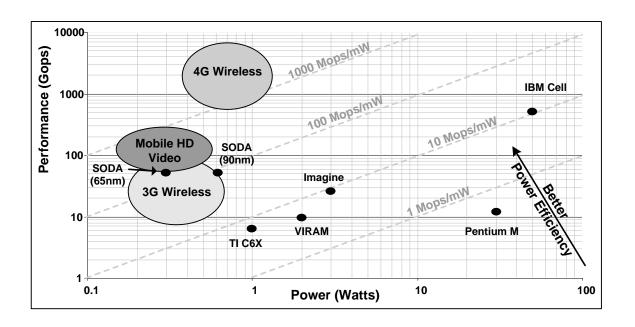

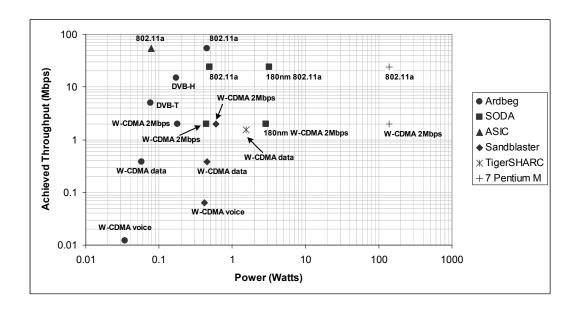

| 1.1    | Performance verses power requirements for various mobile computing                                                                                                                                                                                                                                                                                                        |

|        | applications                                                                                                                                                                                                                                                                                                                                                              |

| 2.1    | Categories of Wireless Networks                                                                                                                                                                                                                                                                                                                                           |

| 2.2    | Throughput and power requirements of typical 3G wireless protocols.  The results are calculated for 16-bit fixed point operations.)                                                                                                                                                                                                                                       |

| 2.3    | Architecture of a 3G cellular phone.)                                                                                                                                                                                                                                                                                                                                     |

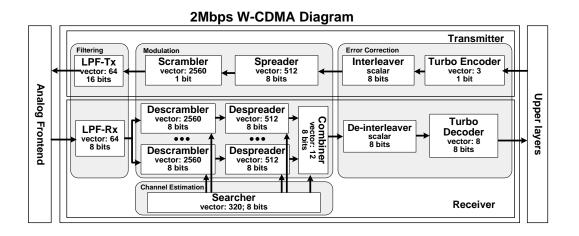

| 2.4    | Physical layer operation of W-CDMA wireless protocol. Each block includes the algorithm's name, vector or scalar computation, vector width, and the data precision. The algorithms are grouped into four categories, shown in shaded boxes: filtering, modulation, channel estimation, and error correction.)                                                             |

| 2.5    | Workload analysis result of W-CDMA physical layer processing. "Vector comp" indicates whether the algorithm contains vector-based arithmetic operations. "Vector width" lists the native computation vector width. "Bit width" lists the data precision width. "Comp Mcycle/sec" lists the peak workload of running the algorithm on a general purpose processor.)        |

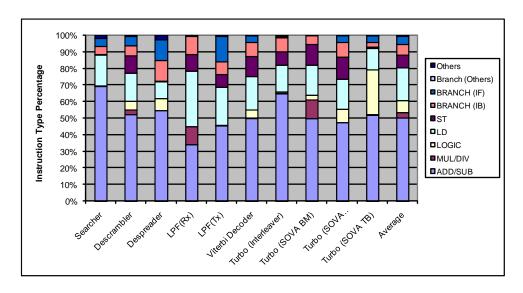

| 2.6    | W-CDMA Instruction Type Breakdown.)                                                                                                                                                                                                                                                                                                                                       |

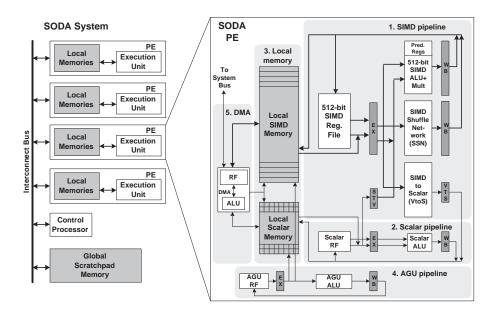

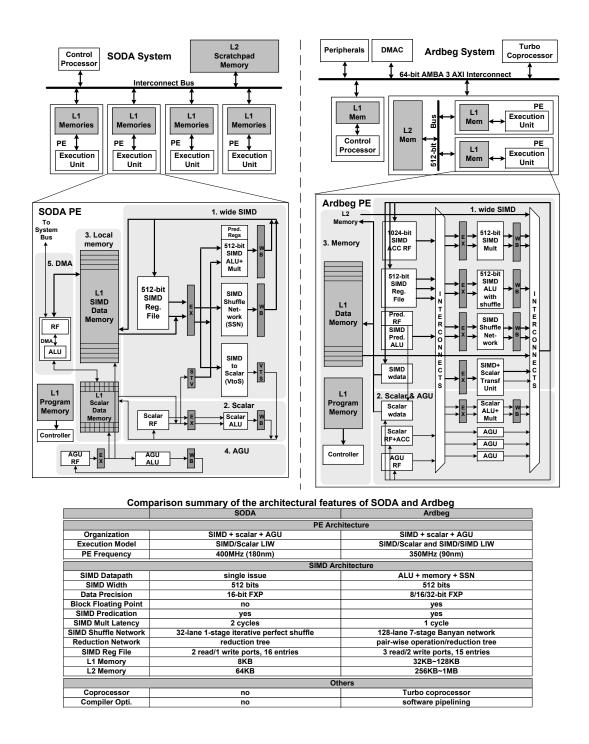

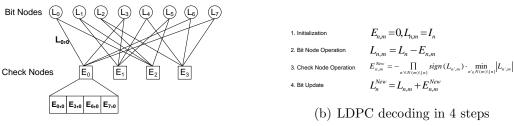

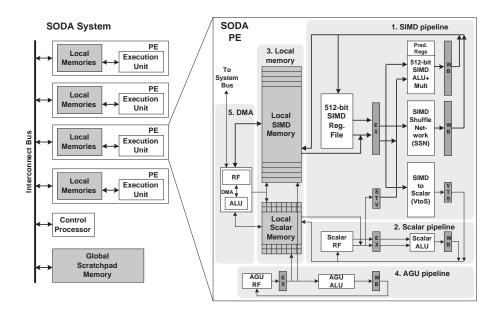

| 2.7    | SODA Architecture. The system consists of 4 data processing elements (PEs), 1 control processor, and global scratchpad memory, all connected through a shared bus. Each PE consists of a 32-lane 16-bit SIMD pipeline, a 16-bit scalar pipeline, two local scratchpad memories, an AGU for calculating memory addresses, and a DMA unit for inter-processor data transfer |

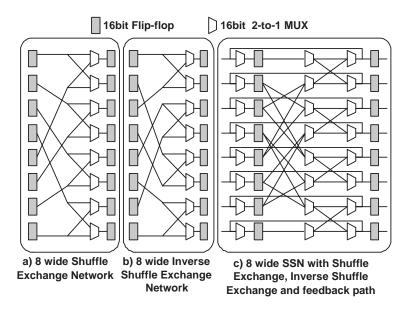

| 2.8    | 8-wide SIMD Shuffle Network(SSN)                                                                                                                                                                                                                                                                                                                                          |

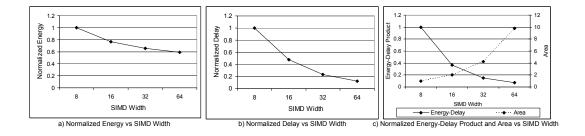

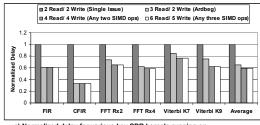

| 3.1    | Plots of normalized energy, delay, and energy-delay product versus area plots for different Ardbeg SIMD width configurations running 3G wireless algorithms. The results are normalized to the 8-wide SIMD design                                                                                                                                                         |

| 3.2  | SODA and Ardbeg architectural diagrams, and a summary of the key                                                                          |   |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|---|

| 0.0  | architectural features of the two designs                                                                                                 | 4 |

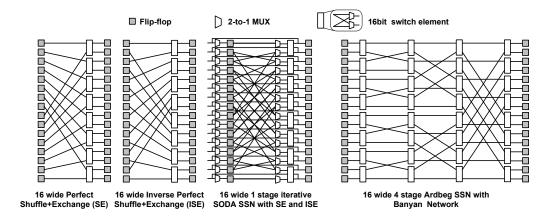

| 3.3  | SIMD shuffle network for the SODA PE and the Ardbeg PE. For illustration clarity, these graphs show 16 wide shuffle networks. The         |   |

|      | lustration clarity, these examples show 16-wide shuffle networks. The SODA PE has a 32-wide 16-bit 1-stage iterative shuffle network, and |   |

|      | the Ardbeg PE has a 128-lane 8-bit 7-stage Banyan shuffle network.                                                                        | 4 |

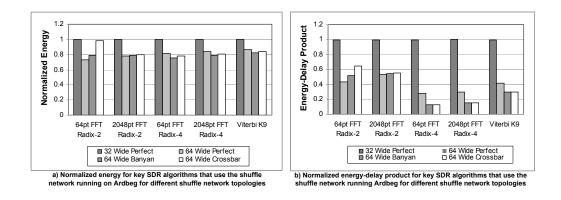

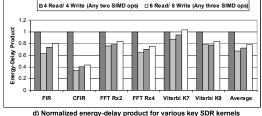

| 3.4  | Normalized energy and energy-delay product for key SDR algorithms                                                                         | 7 |

| 5.4  | running on Ardbeg for different shuffle network topologies                                                                                | 4 |

| 3.5  | Ardbeg VLIW support. The results are shown for software pipelined                                                                         | 4 |

| 5.5  | Ardbeg assembly code. Ardbeg has 7 different function units, as listed                                                                    |   |

|      | in sub-figure a. These seven function units share 3 SIMD register                                                                         |   |

|      | file read and 2 write ports. At most two SIMD operations can be                                                                           |   |

|      | issued per cycle, and not all combinations of SIMD operations are                                                                         |   |

|      | supported. Different LIW configurations are evaluated in terms of                                                                         |   |

|      | delay and energy-delay product, as shown in sub-figures c and d                                                                           | 4 |

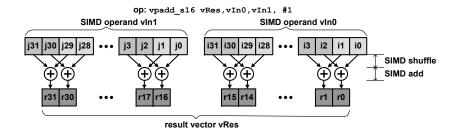

| 3.6  | Ardbeg's pair-wise butterfly SIMD operation implemented using a fused                                                                     |   |

|      | permute and ALU operation. The figure shows pairs of a 2-element but-                                                                     |   |

|      | terfly operation. Ardbeg supports pairs of 1-,2-,4-,8-,and 16-element                                                                     |   |

|      | butterfly of 8- and 16-bits. This butterfly operation uses the inverse                                                                    |   |

|      | perfect shuffle pattern because the input to each SIMD ALU lane must                                                                      |   |

|      | come from the same SIMD lane                                                                                                              |   |

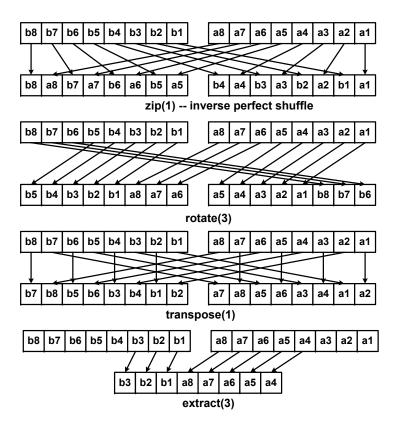

| 3.7  | SSN shuffling patterns used for matrix transpose                                                                                          |   |

| 3.8  | DSP algorithms that are used in W-CDMA, 802.11a and DVB, DVB-H                                                                            |   |

|      | wireless protocols                                                                                                                        | ļ |

| 3.9  | Throughput and power achieved for SODA and Ardbeg for W-CDMA,                                                                             |   |

|      | 802.11a and DVB-T/H. ASIC 802.11a, Pentium M, Sandblaster, and                                                                            |   |

|      | ADI TigerSharc results are also included for comparison purposes. Re-                                                                     |   |

|      | sults are shown for processors implemented in 90nm, unless stated otherwise                                                               | ! |

| 9 10 | erwise                                                                                                                                    | , |

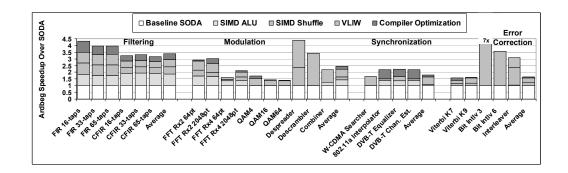

| 5.10 | wireless protocol benchmarks. The speedup is broken down into the                                                                         |   |

|      | different architectural optimizations. These include optimized SIMD                                                                       |   |

|      | ALU, wider 1-cycle SIMD shuffle network, reduced SIMD memory la-                                                                          |   |

|      | tencies through LIW execution, and compiler optimizations with soft-                                                                      |   |

|      | ware pipelining                                                                                                                           | ( |

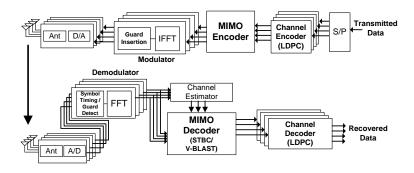

| 4.1  | The physical layer for a 4G terminal                                                                                                      | ( |

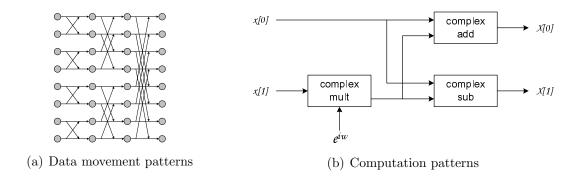

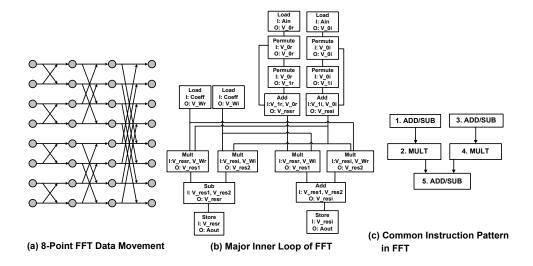

| 4.2  | The data movement of an 8 point FFT and the computations in a 2                                                                           |   |

|      | point FFT                                                                                                                                 | ( |

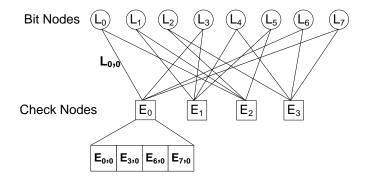

| 4.3  | Transmission code matrix and computation patterns of the Alamouti                                                                         |   |

|      | 2x2 STBC                                                                                                                                  | , |

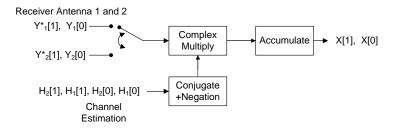

| 4.4  | LDPC graphical representation and decoding operations                                                                                     | , |

| 4.5  | SODA Architecture for SDR                                                                                                                 | , |

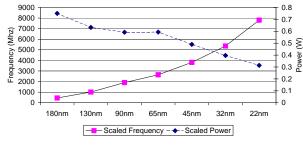

| 4.6  | Technology scaling from 180nm to 22nm with respect to Frequency, Power, Vdd on SODA for 4G                                                                                                                   | 79  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

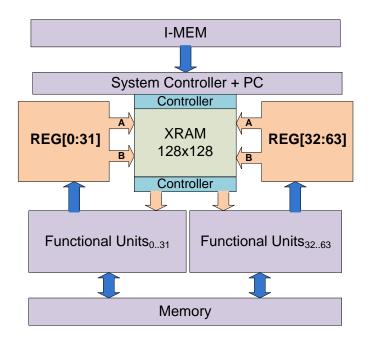

| 5.1  | SODA Architecture for SDR. The system consists of 4 data processing elements (PEs), 1 control processor, and global scratchpad memory, all                                                                   |     |

|      | connected through a shared bus. Each PE consists of a 32-wide 16-bit                                                                                                                                         |     |

|      | SIMD pipeline, a 16-bit scalar pipeline, two local scratchpad memories, an                                                                                                                                   |     |

|      | Address–Generation–Unit(AGU) for calculating memory addresses, and a Direct–Memory–Access (DMA) unit for inter-processor data transfer                                                                       | 88  |

| 5.2  | Block Diagram Overview of a 4G System                                                                                                                                                                        | 89  |

| 5.3  | For the 8-point FFT, the butterfly pattern is the cross between two different elements in the vector. The major inner loop of FFT performs the operation of the butterfly across a SIMD. The nodes represent |     |

|      | SODA instructions and the edges represent data dependencies. The                                                                                                                                             |     |

|      | instruction pattern represents the actual butterfly operation that is performed in each lane                                                                                                                 | 90  |

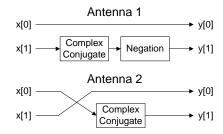

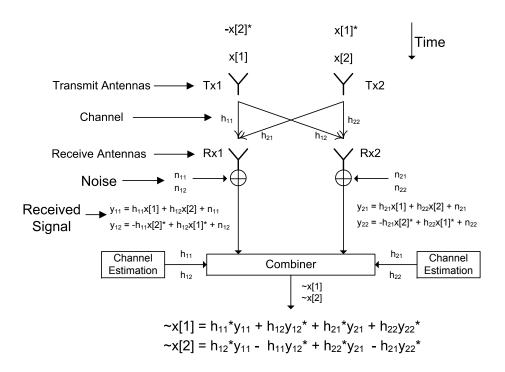

| 5.4  | STBC general operation of Alamouti scheme.                                                                                                                                                                   | 91  |

| 5.4  | The inner loop of STBC shown calculates the values $x[1]$ and $x[2]$ of                                                                                                                                      | 91  |

| 0.0  | Alamouti Scheme. The common instruction pattern as shown is the                                                                                                                                              |     |

|      | majority of the inner loop code                                                                                                                                                                              | 92  |

| 5.6  | General decoding process of V-BLAST                                                                                                                                                                          | 93  |

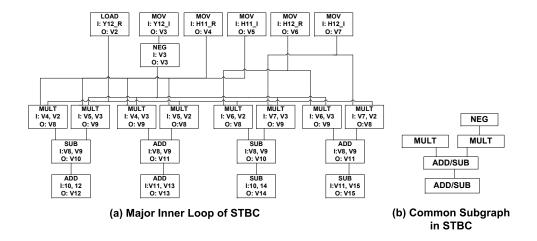

| 5.7  | These two instruction patterns are reused many times within V-BLAST.                                                                                                                                         |     |

|      | They are common in many of the matrix operations                                                                                                                                                             | 95  |

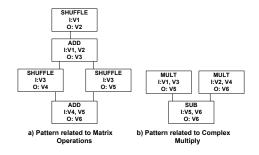

| 5.8  | LDPC graphical representation and decoding operations                                                                                                                                                        | 96  |

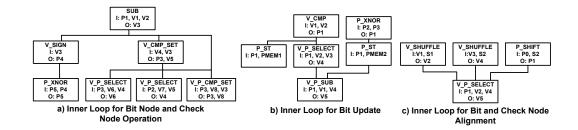

| 5.9  | The inner loop operations of LDPC. These three operations represent<br>the majority of the LDPC workload. They correspond closely to steps                                                                   |     |

|      | 2-4 of the LDPC decoding operation                                                                                                                                                                           | 97  |

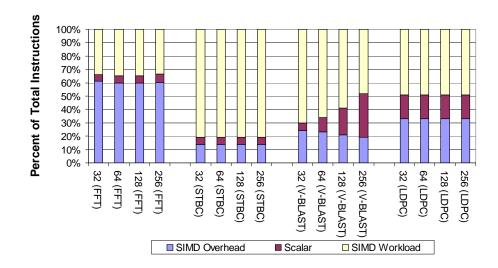

|      | Instruction breakdown of each kernel with respect to SIMD width                                                                                                                                              | 101 |

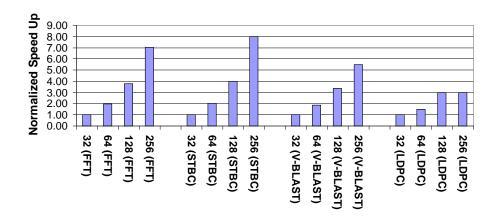

|      | Normalized speedup of each kernel with respect to SIMD width                                                                                                                                                 | 102 |

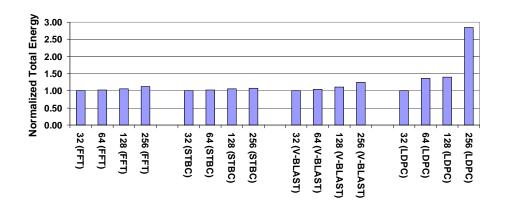

|      | Total energy consumption of each kernel with respect to SIMD width.                                                                                                                                          | 103 |

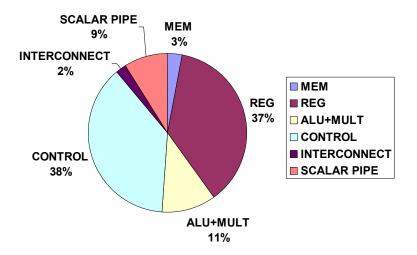

|      | Power breakdown for the kernels on SODA                                                                                                                                                                      | 104 |

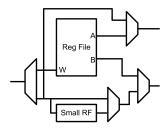

| 5.14 | Modified Register File. Data can either be written to the main register                                                                                                                                      |     |

|      | file, the small register or bypassed completely from both allowing data to be forwarded directly to the next functional unit                                                                                 | 106 |

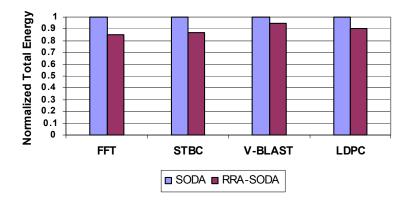

| 5 15 | Total energy consumption of each kernel with reduced register file ac-                                                                                                                                       | 100 |

| 0.10 | cess. SODA is the baseline processor where each instruction always                                                                                                                                           |     |

|      | writes back to the register file then is read when needed. RRA-SODA is                                                                                                                                       |     |

|      | the modified SODA architecture that can write the values to a smaller                                                                                                                                        |     |

|      | register file                                                                                                                                                                                                | 106 |

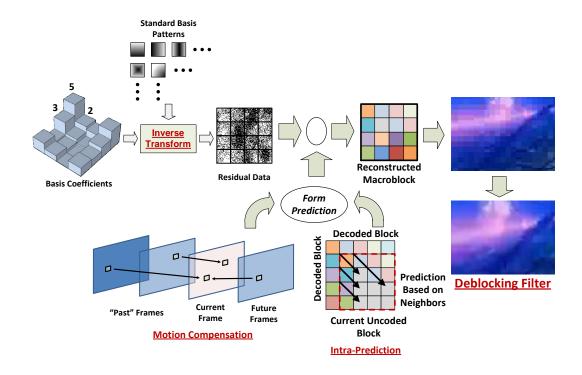

| 6.1  | Block Diagram of H264                                                                                                                                                                                        | 110 |

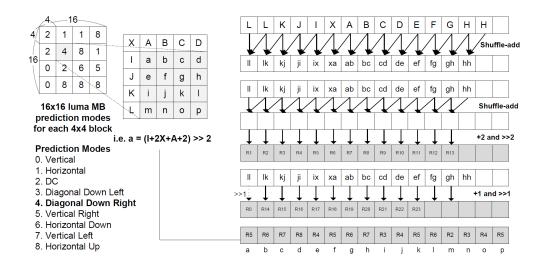

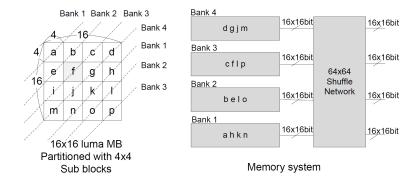

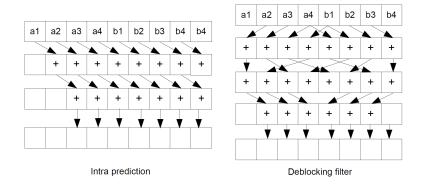

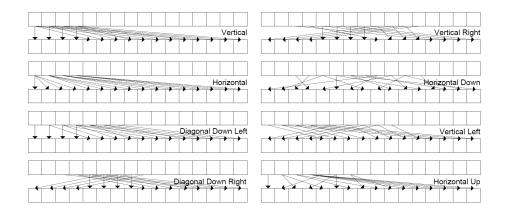

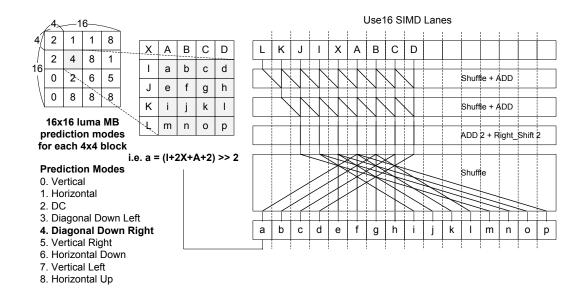

| 6.2  | Mapping a 16x16 luma macroblock intra-prediction process on the                                                                                                                                              |     |

|      | proposed architecture. Example of the Diagonal Down Right intra-                                                                                                                                             |     |

|      | prediction for a 4x4 sub block (grey block) is presented with fused                                                                                                                                          |     |

|      | operations                                                                                                                                                                                                   | 111 |

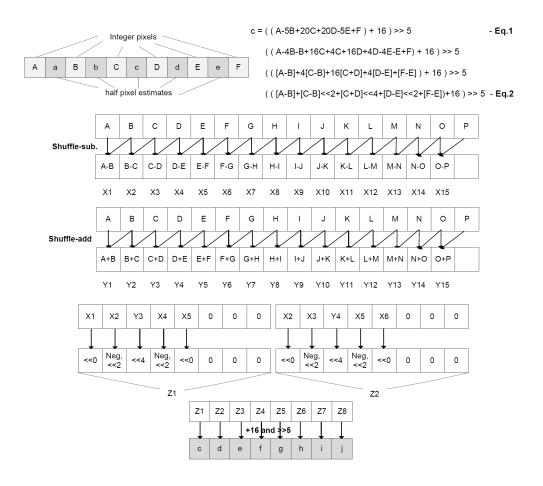

| 6.3  | Mapping a deblocking filter process when BS (Block Strength)=4                                                                                                                                                                                                                                                                                                     | 113  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 6.4  | Example of interpolation of motion compensation (half-pel)                                                                                                                                                                                                                                                                                                         | 114  |

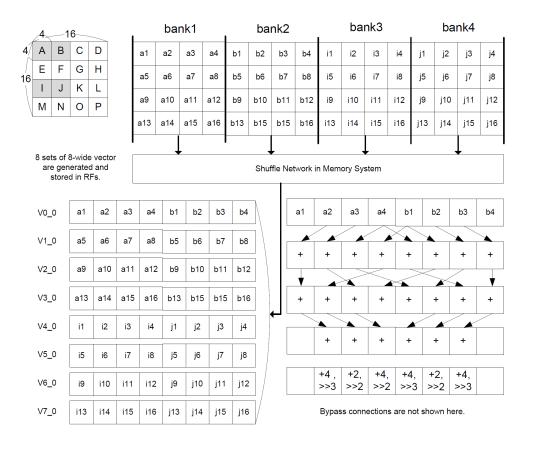

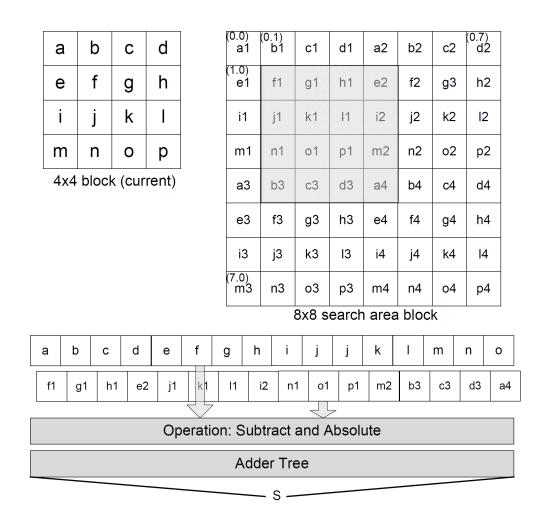

| 6.5  | Mapping a motion estimation process for a 4x4 block on the proposed                                                                                                                                                                                                                                                                                                |      |

|      | architecture; The search area is 8x8                                                                                                                                                                                                                                                                                                                               | 115  |

| 6.6  | Diagonal memory organization and shuffle network, which allows the                                                                                                                                                                                                                                                                                                 |      |

|      | horizontal and vertical memory access without conflict. The 64x64                                                                                                                                                                                                                                                                                                  |      |

|      | shuffle network realigns 64 16-bit data                                                                                                                                                                                                                                                                                                                            | 118  |

| 6.7  | Subgraphs for the inner loops for two H.264 kernels; The bypass path                                                                                                                                                                                                                                                                                               |      |

|      | is not shown for simplicity                                                                                                                                                                                                                                                                                                                                        | 118  |

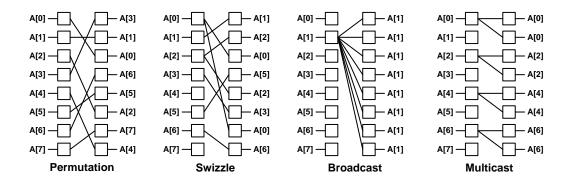

| 6.8  | Permutation Patterns for H.264 Intra-prediction Modes                                                                                                                                                                                                                                                                                                              | 120  |

| 7.1  | Permutations are 1-to-1 mappings of input to output ports. Swizzles are the generic form of duplication and permutation combined where                                                                                                                                                                                                                             |      |

|      | the output does not need to contain all the inputs. Broadcast is a                                                                                                                                                                                                                                                                                                 |      |

|      | special form of swizzle where one of the values is broadcasted to all the                                                                                                                                                                                                                                                                                          |      |

|      | outputs. Multicasting is another special form of swizzle where multiple                                                                                                                                                                                                                                                                                            |      |

|      | input ports are duplicated in a regular pattern to the outputs                                                                                                                                                                                                                                                                                                     | 124  |

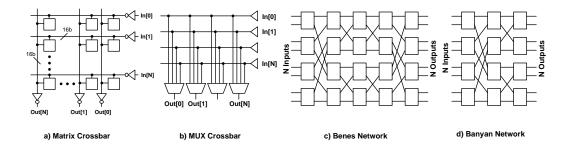

| 7.2  | Different Commonly Used Network Toplogies                                                                                                                                                                                                                                                                                                                          | 125  |

| 7.3  | Comparison between Crossbar, Benes, Banyan and XRAM networks with respect to Scalability, Speed, Energy, and Flexibility where N is                                                                                                                                                                                                                                |      |

|      | the number of ports in an NxN network                                                                                                                                                                                                                                                                                                                              | 129  |

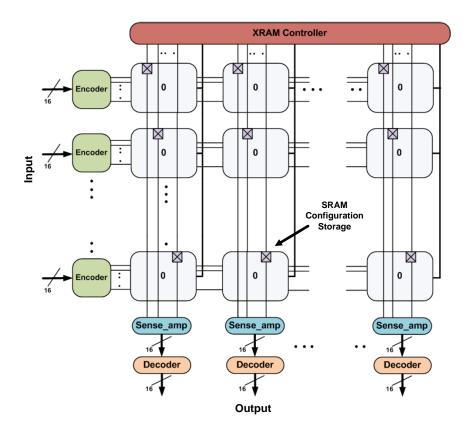

| 7.4  | XRAM is a low power high performance matrix style crossbar that re-<br>uses output buses for control programming and stores multiple swizzle<br>configurations at the cross points using SRAM cells. The XRAM con-<br>troller sends the control line to pick which configuration SRAM cell to<br>use. The encoder and decoder are the transition encoding/decoding |      |

|      | logic used to minimize the switching power when the input and output                                                                                                                                                                                                                                                                                               |      |

|      | bits do not change values                                                                                                                                                                                                                                                                                                                                          | 131  |

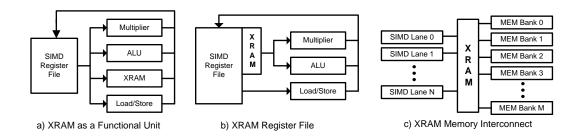

| 7.5  | Different Placements of XRAM within the Processor Architecture. For                                                                                                                                                                                                                                                                                                |      |

|      | the memory interconnect benefits occur when $M \geq 2N$                                                                                                                                                                                                                                                                                                            | 134  |

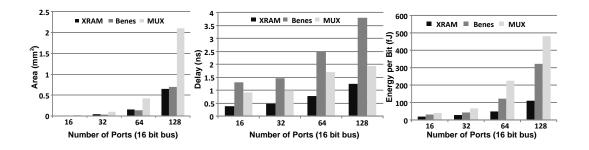

| 7.6  | Comparison between the XRAM, Benes and MUX crossbar network                                                                                                                                                                                                                                                                                                        |      |

|      | with respect to Area, Delay and Energy per bit (total bits = number                                                                                                                                                                                                                                                                                                |      |

|      | ports * 16-bit)                                                                                                                                                                                                                                                                                                                                                    | 136  |

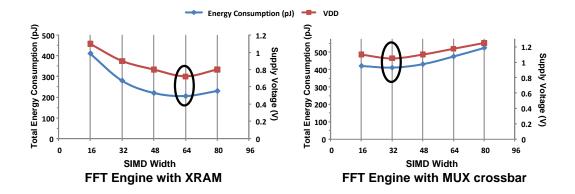

| 7.7  | FFT Engine                                                                                                                                                                                                                                                                                                                                                         | 138  |

| 7.8  | FFT results                                                                                                                                                                                                                                                                                                                                                        | 139  |

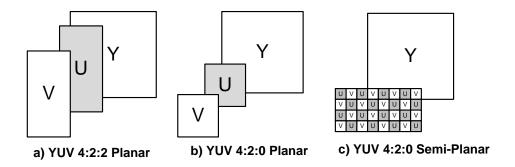

| 7.9  | Examples of different YUV modes. In each YUV mode the Y plane                                                                                                                                                                                                                                                                                                      |      |

|      | is always written out to memory then the U plane followed by the Y                                                                                                                                                                                                                                                                                                 |      |

|      | plane. In YUV 4:2:0 semi-planar, the U and V data are interleaved                                                                                                                                                                                                                                                                                                  | 1.40 |

| 7 10 | together. The typical size of the Y plane is 16x16 pixels                                                                                                                                                                                                                                                                                                          | 140  |

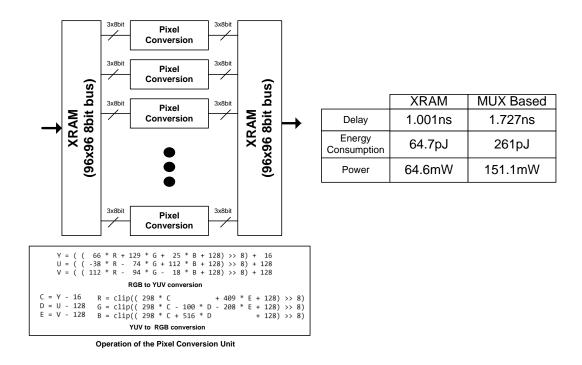

| 7.10 | Color Space Conversion Hardware                                                                                                                                                                                                                                                                                                                                    | 142  |

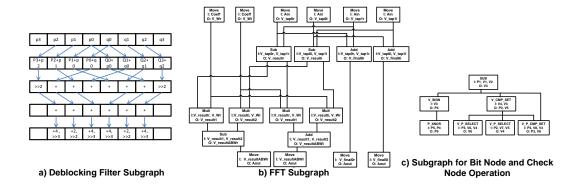

| 8.1  | Select subgraphs for the inner loops of MSP algorithms                                                                                                                                                                                                                                                                                                             | 153  |

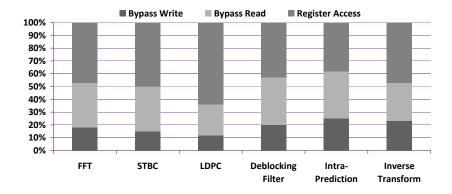

| 8.2  | Register file access for the inner loops of MSP algorithms. Bypass write and read are the RF read and write accesses that do <i>not</i> need to use |      |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------|

|      | the main RF. Register accesses are the read and write accesses that do                                                                              |      |

|      | need to use the main RF                                                                                                                             | 155  |

| 8.3  | Instruction pair frequencies for different MSP algorithms                                                                                           | 157  |

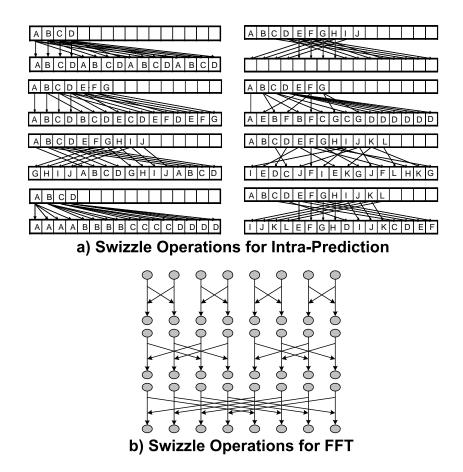

| 8.4  | A set of swizzle operations that are required for a subset of MSP algo-                                                                             | 10.  |

| 0.1  | rithms                                                                                                                                              | 159  |

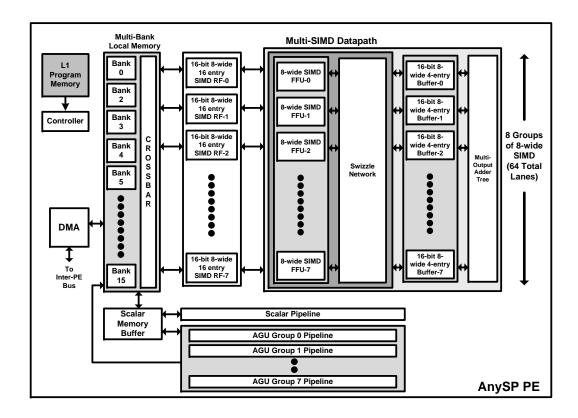

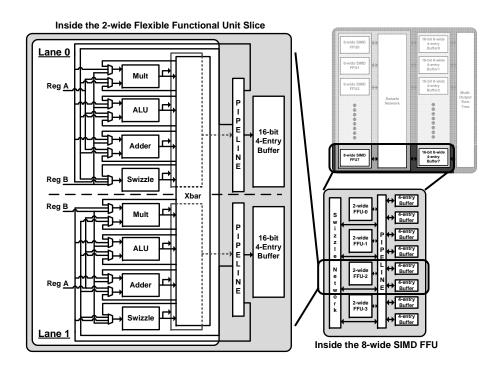

| 8.5  | AnySP PE. It consists of SIMD and scalar datapaths. The SIMD                                                                                        | 100  |

| 0.0  | datapath consists of 8-groups of 8-wide SIMD units, which can be                                                                                    |      |

|      | configured to create SIMD widths of 16, 32 and 64. Each of the 8-                                                                                   |      |

|      | wide SIMD units are composed of groups of Flexible Functional Units                                                                                 |      |

|      | (FFUs). The local memory consists of 16 memory banks; each bank is                                                                                  |      |

|      | an 8-wide SIMD containing 256 16-bit entries, totalling 32KB of storage                                                                             | .161 |

| 8.6  | Flexible Functional Unit                                                                                                                            | 164  |

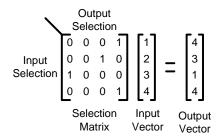

| 8.7  | The swizzle operation in computer graphics. The rows of the selection                                                                               |      |

|      | matrix correspond to the input vector and the columns correspond to                                                                                 |      |

|      | the output vector selected. Each row can only have a single 1, but                                                                                  |      |

|      | columns can have multiple 1s which allow for selective multi-casting of                                                                             |      |

|      | the data                                                                                                                                            | 166  |

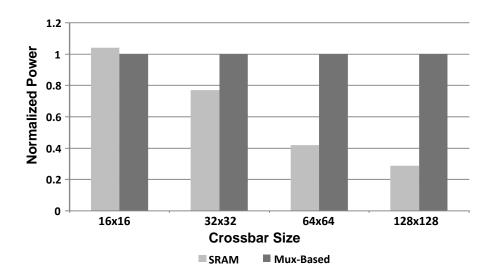

| 8.8  | Comparison of power between the SRAM-based swizzle network and                                                                                      |      |

|      | MUX-based crossbar. The values are normalized to the MUX-based                                                                                      |      |

|      | crossbar for different crossbar widths with 16-bit data inputs. These                                                                               |      |

|      | results correspond to a switching activity of 0.50                                                                                                  | 167  |

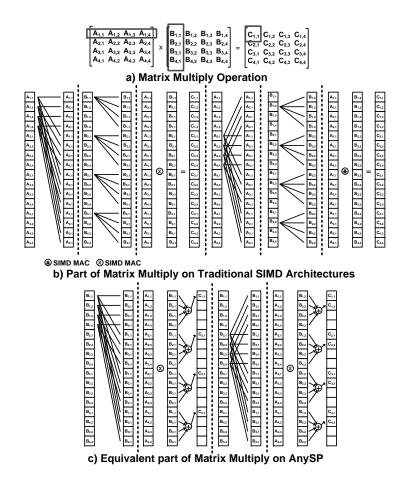

| 8.9  | Demonstration of the output adder tree for matrix multiplication                                                                                    | 169  |

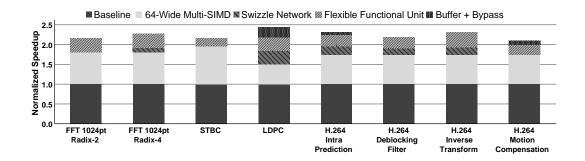

| 8.10 | AnySP speedup over SODA for the key algorithms used in 4G and                                                                                       |      |

|      | H.264 benchmarks. The speedup is broken down into the different                                                                                     |      |

|      | architectural enhancements - wider SIMD width, single-cycle SRAM-                                                                                   |      |

|      | based crossbar, fused-operations and buffer support                                                                                                 | 171  |

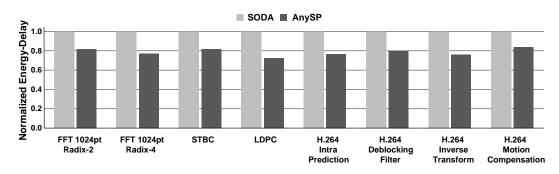

| 8.11 | Normalized Energy-Delay product for each kernel algorithm                                                                                           | 171  |

| 8.12 | Mapping a luma 16x16 MB intra-prediction process on AnySP; Exam-                                                                                    |      |

|      | ple of the Diagonal Down Right intra prediction for a 4x4 sub block                                                                                 |      |

|      | (grey block) is presented with each cycle's operations listed                                                                                       | 173  |

| 8.13 | PE Area and Power Summary for AnySP running 100Mbps high mo-                                                                                        |      |

|      | bility 4G wireless and H.264 4CIF video at 30fps                                                                                                    | 174  |

| 8.14 | Performance verses power requirements for various mobile computing                                                                                  |      |

|      | applications                                                                                                                                        | 176  |

# LIST OF TABLES

| Table |                                                                            |     |

|-------|----------------------------------------------------------------------------|-----|

| 4.1   | Cycle Count of Major 4G Kernels on SODA                                    | 77  |

| 4.2   | Computational Pattern of 4G algorithms                                     | 78  |

| 5.1   | Data level parallelism analysis for major 4G kernels                       | 99  |

| 5.2   | Percent of total register file access that are produced and consumed       |     |

|       | within a subgraph. These register file accesses can use the small register |     |

|       | file                                                                       | 104 |

| 6.1   | Shuffle patterns for six intra prediction modes for 4x4 luma               | 112 |

| 6.2   | Kernel operations, SIMD workload, required SIMD width, and the             |     |

|       | amount of thread level parallelism (TLP) for H.264 encoder/decoder         |     |

|       | algorithms                                                                 | 116 |

| 6.3   | Instruction pair frequency for H.264 kernel algorithms                     | 119 |

| 8.1   | Data level parallelism analysis for MSP algorithms. Overhead work-         |     |

|       | load is the amount of instructions needed to aid the SIMD operations       |     |

|       | like data shuffle and SIMD load/store                                      | 150 |

**ABSTRACT**

ARCHITECTURE AND ANALYSIS FOR NEXT GENERATION MOBILE

SIGNAL PROCESSING

by

Mark Woh

Chair: Trevor N. Mudge

Mobile devices have proliferated at a spectacular rate, with more than 3.3 billion

active cell phones in the world. With sales totaling hundreds of billions every year,

the mobile phone has arguably become the dominant computing platform, replacing

the personal computer. Soon, improvements to todays smart phones, such as high-

bandwidth internet access, high-definition video processing, and human-centric inter-

faces that integrate voice recognition and video-conferencing will be commonplace.

Cost effective and power efficient support for these applications will be required.

Looking forward to the next generation of mobile computing, computation re-

quirements will increase by one to three orders of magnitude due to higher data

xiii

rates, increased complexity algorithms, and greater computation diversity but the power requirements will be just as stringent to ensure reasonable battery lifetimes. The design of the next generation of mobile platforms must address three critical challenges: efficiency, programmability, and adaptivity. The computational efficiency of existing solutions is inadequate and straightforward scaling by increasing the number of cores or the amount of data-level parallelism will not suffice. Programmability provides the opportunity for a single platform to support multiple applications and even multiple standards within each application domain. Programmability also provides: faster time to market as hardware and software development can proceed in parallel; the ability to fix bugs and add features after manufacturing; and, higher chip volumes as a single platform can support a family of mobile devices. Lastly, hardware adaptivity is necessary to maintain efficiency as the computational characteristics of the applications change. Current solutions are tailored specifically for wireless signal processing algorithms, but lose their efficiency when other application domains like high definition video are processed.

This thesis addresses these challenges by presenting analysis of next generation mobile signal processing applications and proposing an advanced signal processing architecture to deal with the stringent requirements. An application-centric design approach is taken to design our architecture. First, a next generation wireless protocol and high definition video is analyzed and algorithmic characterizations discussed. From these characterizations, key architectural implications are presented, which form the basis for the advanced signal processor architecture, *AnySP*.

### CHAPTER 1

### Introduction

In the coming years, the deployment of untethered computers will continue to increase rapidly. The world has more than 3 billion active cell phones [3], each a sophisticated multiprocessor built around application specific integrated circuits (ASICs). With mobile sales and usage totaling hundreds of billions of dollars every year, the cell phone has arguably become the dominant computing platform, a candidate for replacing the personal computer. We expect to see both the types and numbers of mobile digital devices to increase in the near future. New devices will improve on the mobile phone by incorporating advanced functionality, such as faster internet access, high quality video and human-centric interfaces that integrate voice recognition and video-conferencing. We can already see elements of advanced functionality in mobile devices from the major manufacturers, and with fourth generation (4G) wireless broadband and mobile high definition video on the horizon, cost effective and power efficient support for these applications will be required in the very near future.

The next generation of mobile computing will have higher data rates, increased

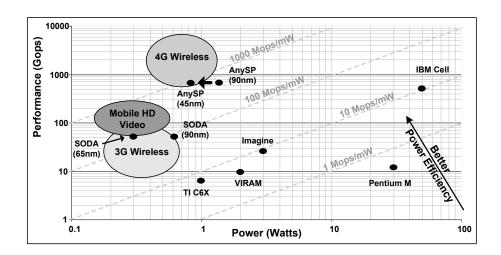

**Figure 1.1:** Performance verses power requirements for various mobile computing applications.

complexity algorithms, and greater computation diversity but the power requirements will be just as stringent. Mobile devices perform signal processing as one of their primary computational activities due to their heavy usage of wireless communication and their rendering of audio and video signals. Fourth generation wireless technology (4G) has been proposed to increase the bandwidth to maximum data rates of 100 Mbps for high mobility and 1 Gbps for low mobility. This translates to an increase in the computational requirements of 10-1000x over previous third generation wireless technologies (3G) with a power envelope that can only increase by 2-5x [90]. Other signal processing tasks, such as high-definition video, are also 10-100x more compute intensive than current mobile video. Scaling of existing approaches will not suffice, instead, the inherent computational efficiency, programmability, and adaptability of the hardware must change.

Figure 1.1 presents the demands of the 3G and 4G protocols in terms of the peak processing throughput and power budget. Conventional processors cannot meet the power-throughput requirements of these protocols. 3G protocols, such as W-CDMA, require approximately 100 Mops/mW. Desktop processors, such as the Pentium M, operate below 1 Mop/mW, while digital signal processors, such as the TI C6x, operate around 10 Mops/mW. High performance systems, like the IBM Cell [69], can provide excellent throughput, but its power consumption makes it infeasible for mobile devices [69]. Research solutions, such as VIRAM [43] and Imagine [4], can achieve the performance requirements for 3G, but exceed the power budgets of mobile terminals. SODA improved upon these solutions and was able to meet both the power and throughput requirements for 3G wireless [54]. Companies such as Phillips [88], Infineon [73], ARM [91], and Sandbridge [27] have also proposed domain-specific systems that meet the requirements for 3G wireless.

Current solutions for high performance mobile devices has been to wrap multiple digital signal processing (DSP) cores around ASICs and fixed function accelerators. As new applications are developed, these mobile platforms are redesigned with additional ASICs. As more applications and features are added to the phone, this becomes increasingly expensive for the consumer and manufacture in terms of development and material costs. Furthermore, current designs which are inflexible become obsolete. An example of a new application that many companies invested resources in is WiMAX. In order to stay ahead of the market, many companies like Intel and Motorola invested large amounts of resources into the development of a WiMAX platform. As

technology improved, the WiMAX standard became replaced with a new 4G wireless standard (LTE) even before WiMAX was deployed. Because the building blocks for these systems were designed specifically for WiMAX, these companies were left with inflexible designs that may not be able to adapt to future technologies. To solve these problems, many companies are looking for ways to design programmable mobile platforms that can support multiple standards and applications. These platforms will have to meet the stringent demands which each application requires.

Mobile computing platforms are not limited to performing only wireless signal processing. High-definition video is also an important application that these platforms will need to support. Figure 1.1 shows that the performance requirements of video exceed that of 3G wireless, but are not as high as 4G wireless. Thus the power per Gops requirement is further constrained. Moreover, the data access complexity in video is much higher than wireless. Wireless signal processing algorithms typically operate on single dimension vectors, whereas video algorithms operate on two or three dimensional blocks of data. Thus, video applications push designs to have more flexible higher bandwidth memory systems. High definition video is just one example of a growing class of applications with diverse computing and memory requirements that will have to be supported by the next generation of mobile devices.

The design of the next generation of mobile platforms must address three critical issues: efficiency, programmability, and adaptivity. The existing computational efficiency of 3G solutions is inadequate and must be increased by at least an order of magnitude for 4G. As a result, straightforward scaling of 3G solutions by

Programmability provides the opportunity for a single platform to support multiple applications and even multiple standards within each application domain. It also provides faster time to market and higher chip volumes, thereby reducing manufacturing cost. Lastly, hardware adaptivity is necessary to maintain efficiency as the core computational characteristics of the applications change. 3G solutions rely heavily on the widespread amounts of vector parallelism in wireless signal processing algorithms, but lose most of their efficiency when vector parallelism is unavailable or constrained as in other application domains like high-definition video.

This thesis presents a set of design proposals for realizing an advanced signal processing architecture that targets the next generation mobile computing. In order to design a solution that can meet the lofty requirements, this thesis takes an application-centric approach – evaluate and optimize all aspects of the design based on the characteristics of the applications. We must first understand the workings of the different applications and their algorithms. With the insights from the applications, a mobile signal processing architecture is designed and optimized for these applications. This thesis makes the following contributions:

- Analysis and design of a commercial software defined radio architecture, Ardbeg, for current generation wireless protocols.

- Algorithmic characterization of two mobile signal processing applications: a fourth generation wireless protocol and high definition mobile video.

- Architectural insights derived from the characterizations of mobile signal processing applications.

- An advanced signal processing architecture, AnySP, that targets multiple applications domains, specifically 4G wireless communication and high-definition video decoding within the power budget of a mobile device.

# 1.1 Organization

The remainder of this dissertation is organized as follows. Chapter 2 introduces software defined radio and discusses previous architectures that have been proposed to solve the current generation signal processing challenge. Chapter 3 provides details about the architectural design of the Ardbeg processor which targets current generation wireless protocols. Chapter 4 provides analysis on the software characteristics of next generation wireless protocols. Chapter 5 uses these characterizations of the next generation wireless protocols and proposes key architectural insights to help guide us in development of a low power architecture. Chapter 6 provides analysis of a high definition mobile video application, H.264. Chapter 7, a low power scalable SRAM based swizzle interconnect is analyzed. And finally, in Chapter 8, an advanced signal processing architecture, AnySP, is proposed that targets the next generation mobile computing.

# CHAPTER 2

# Overview of Processor Designs for Mobile

# Software Defined Radio

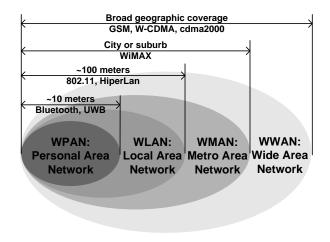

Wireless communication has become one of the dominating applications in today's world. Mobile communication devices are the largest consumer electronic group in terms of volume. In 2007, there was an estimated 3.3 billion mobile telephone subscriptions. This number is roughly half of the world's population. Applications like web browsing, video streaming, email and video conferencing have all become key applications for mobile devices. As technology becomes more advanced, users will require more functionality from their mobile devices and more bandwidth to support them. Furthermore, in recent years, we have seen the emergence of an increasing number of wireless protocols that are applicable to different types of networks. Figure 2.1 lists some of these wireless protocols and their application domains, ranging from the home and office WiFi network to the city-wide cellular networks. With the proliferation of wireless mobile communications, the next generation mobile devices

will enable users to connect to information ubiquitously from every corner of the world.

Figure 2.1: Categories of Wireless Networks

One of the key challenges in realizing ubiquitous communication is the seamless integration and utilization of the multiple existing and future wireless communication networks. In many current wireless communication solutions, the physical layer of the protocols are implemented with non-programmable ASIC processors. This means that the communication device would consist of multiple processors, one for each wireless protocol. Such a solution is not scalable and is clearly infeasible. Software Defined Radio (SDR) promises to deliver a cost effective and flexible solution by implementing a wide variety of wireless protocols in software, and running them on the same hardware platform. A software solution offers many potential advantages, including but not limited to the following:

- A programmable SDR processor would allow multimode operation, running different protocols depending on the available wireless network, GSM in Europe, CDMA in the USA and some parts of Asia, and 802.11 in coffee shops. This is possible with less hardware than custom implementations.

- A protocol implementation's time to market would be shorter because it would reuse the hardware. The hardware integration and software development tasks would progress in parallel.

- Prototyping and bug fixes would be possible for next-generation protocols on existing silicon through software changes. The use of a programmable solution would support the continuing evolution of specifications; after the chipset's manufacture, developers could deploy algorithmic improvements by changing the software without redesign.

• Chip volumes would be higher because the same chip would support multiple protocols without requiring hardware changes.

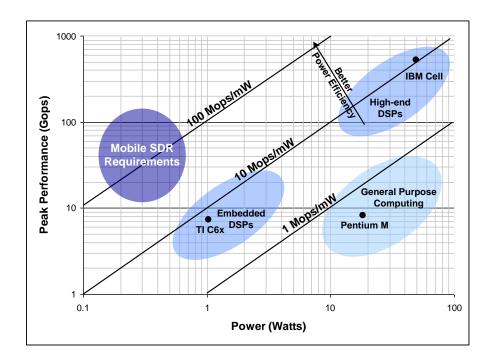

**Figure 2.2:** Throughput and power requirements of typical 3G wireless protocols. The results are calculated for 16-bit fixed point operations.)

Designing a SDR processor for mobile communication devices must address two keys challenges — meeting the computational requirements of wireless protocols while operating under the power budget of a mobile device. The operation throughput requirements of current third-generation (3G) wireless protocols are already an order of magnitude higher than the capabilities of modern DSP processors. This gap is likely to grow in the future. Figure 2.2 shows the computation and power demands of a typical 3G wireless protocol. Although most DSP processors operate at an efficiency of approximately 10 million operations per second (Mops) per milliwatt (mW), the typical wireless protocol requires 100 Mops/mW.

This chapter presents the challenges and trade-offs in designing architectures for baseband processing in mobile communication devices. It gives an overview of baseband processing in SDR, followed by workload and performance analysis of a representative protocol. Next it describes the architectural features of a low power baseband architecture, SODA, followed by brief descriptions of other representative processor prototypes.

#### 2.1 SDR Overview

SDR promises to solve the problems of supporting multiple wireless protocols and address future challenges. The SDR Forum, which is a consortium of service operators, designers and system integrators, defines SDR as:

"A collection of hardware and software technologies that enable reconfigurable system architectures for wireless networks and user terminals. SDR provides an efficient and comparatively inexpensive solution to the problem of building multi-mode, multi-band, multi-functional wireless devices that can be enhanced using software upgrades. As such, SDR can really be considered an enabling technology that is applicable across a wide range of areas within the wireless industry."

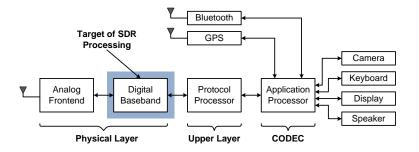

Figure 2.3 shows the architecture for a typical third generation cellular phone. The architecture includes four major blocks: analog front-end, digital baseband, protocol processor, and application processor. The physical layer of wireless protocols includes both the analog front-end and the digital baseband. The analog front-end is usually

Figure 2.3: Architecture of a 3G cellular phone.)

implemented with analog ASICs. The digital baseband block performs the remaining physical layer operations and is also typically implemented with ASICs. The upper layers are implemented by the protocol processor and application processor which are usually SoCs and consist of general purpose embedded and DSP processors.

The objective of SDR is to replace the baseband ASICs with a programmable hardware platform, and to implement the baseband processing in software. Designing programmable analog front-ends is quite a challenge and is beyond the scope of this chapter. Here we focus on design of programmable digital baseband processing engines for SDR.

# 2.2 Workload Profiling and Characterization

# 2.2.1 The W-CDMA Physical Layer Processing

We select the wide-band code division multiple access (W-CDMA) protocol as a representative wireless workload case study for designing the SDR processor. This section provides a brief summary of its algorithms and characteristics. A more de-

**Figure 2.4:** Physical layer operation of W-CDMA wireless protocol. Each block includes the algorithm's name, vector or scalar computation, vector width, and the data precision. The algorithms are grouped into four categories, shown in shaded boxes: filtering, modulation, channel estimation, and error correction.)

tailed analysis can be found in [49].

The W-CDMA system is one of the dominant 3G wireless communication networks where the goal is multimedia service including video telephony on a wireless link [36]. It improves over prior cellular protocols by increasing the data rate from 64 Kbps to 2 Mbps. The protocol stack of the W-CDMA system consists of several layers. At the bottom of the stack is the physical layer which is responsible for overcoming errors induced by an unreliable wireless link. The next layer is the medium access control (MAC) layer which resolves contention in shared radio resources. The upper layer protocols including MAC are implemented on a general purpose processor due to their relatively low computation requirements. In this section we focus on the computation model of the W-CDMA physical layer.

Figure 2.4 shows a high level block diagram of the digital processing in the W-

CDMA physical layer. It shows that the physical layer contains a set of disparate DSP kernels that work together as one system. There are four major components: filtering, modulation, channel estimation, and error correction.

Filtering. Filtering algorithms are used to suppress signals transmitted outside of the allowed frequency band so that interference with other frequency bands are minimized. The FIR filter operations in WCDMA can be very easily parallelized.

#### Modulation.

Modulation algorithms map source information onto the signal waveforms of the transmitter, and the receiver demodulates the signal waveforms back into source information. Two sets of codes are used for modulation: channelization codes and scrambling codes. Channelization codes are used so that the same radio medium can be used to transmit multiple different signal streams. Scrambling codes are used to extract the signal of a specific terminal among many transmitting terminals. On the receiver side, despreader is used to decode the channelization codes and descrambler is used to decode scrambling codes. Demodulation requires the transmitter and receiver to be perfectly synchronized. However, radio transmission suffers from multi-path fading effect, where multiple delayed versions of the same signal stream are received due to environment interference. A searcher is used to find the synchronization point of each of the delayed signal streams and each of these delayed signals is decoded with its own despreader and descrambler. The decoded output of the despreader/descrambler pairs are then combined together as the demodulated output.

Channel Estimation. Channel estimation algorithms calculate the channel con-

ditions to synchronize the two communicating terminals to ensure lock-step communication between the sender and the receiver. W-CDMA uses a searcher as its channel estimation algorithm. Searcher is called once per W-CDMA frame. There are two types of searchers — full searcher and quick searcher. In a group of 8 frames, the full searcher is used for the first frame, and the quick searcher is used for the remaining 7 frames. Both types of searchers consist of four steps: correlation, filtering out high frequency noise, detecting peaks, and global peak detection.

Error Correction Algorithms. Error correction algorithms are used to combat noisy channel conditions. The sender encodes the original data sequence with a coding scheme that inserts systematic redundancies into the output, which is decoded by the receiver to find the most likely original data sequence. Two types of error correction algorithms are used – convolutional coding and Turbo coding. Turbo coding is used for the 2Mbps data channel, while convolutional coding is used for all the other channels. For decoding, the Viterbi decoder is used for convolutional codes and the Turbo decoder is used for Turbo codes. Turbo decoding is usually the most computationally intensive algorithm in baseband processing. The corresponding decoder consists of two component decoders that are typically of type SOVA (Software Output Viterbi Algorithm) or based on MAP (Maximum A Posteriori) and connected together by interleavers. The interleaving pattern is specified by the W-CDMA standard, but the choice of component decoder is left to the designers.

| Algorithms                                                                                     | Configurations                  | Vector<br>Comp. | Vector<br>Length | Bit<br>Width | Comp.<br>Mcycles/sec |

|------------------------------------------------------------------------------------------------|---------------------------------|-----------------|------------------|--------------|----------------------|

|                                                                                                | W-CDMA (2Mbps)                  |                 |                  |              |                      |

| Scrambler                                                                                      | Defined in W-CDMA standard      | yes             | 2560             | 1,1          | 240                  |

| Descrambler*                                                                                   | 12 fingers, 3 base stations     | yes             | 2560             | 1,8          | 2,600                |

| Spreader                                                                                       | Spreading factor = 4            | yes             | 512              | 8            | 300                  |

| Despreader*                                                                                    | 12 fingers, 3 base stations     | yes             | 512              | 8            | 3,600                |

| PN Code (Rx)                                                                                   | 3 base stations                 | no              | 1                | 8            | 30                   |

| PN Code (Tx)                                                                                   | Defined in W-CDMA standard      | no              | 1                | 8            | 10                   |

| Combiner*                                                                                      | 2Mbps data rate                 | partial         | 12               | 8            | 100                  |

| FIR (Tx)                                                                                       | 4 filters x 65 coeff x 3.84Msps | yes             | 64               | 1,16         | 7,900                |

| FIR (Rx)                                                                                       | 2 filters x 65 coeff x 7.68Msps | yes             | 64               | 8,8          | 3,900                |

| Searcher*                                                                                      | 3 base stations, 320 windows    | no              | 320              | 1,8          | 26,500               |

| Interleaver                                                                                    | 1 frame                         | no              | 1                | 8            | 10                   |

| Deinterleaver                                                                                  | 1 frame                         | partial         | 1                | 8            | 10                   |

| Turbo Enc.                                                                                     | K=4                             | yes             | 3                | 1,1          | 100                  |