# Cache Resource Allocation in Large Scale Chip Multiprocessors

by

Lisa Rufeng Hsu

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctorate of Philosophy (Computer Science and Engineering) in The University of Michigan 2009

Doctoral Committee:

Associate Professor Steven K. Reinhardt, Co-Chair Professor Trevor N. Mudge, Co-Chair Associate Professor Scott Mahlke Associate Professor Dennis M. Sylvester Ravishankar Iyer, Intel © Lisa Rufeng Hsu 2009 All Rights Reserved To my parents, De Dzwo and Ellen Hsu

#### ACKNOWLEDGEMENTS

This dissertation marks the single most trying, thrilling, educational, and lengthy period of my life. Through the research and experiences that have led to finishing this work, I have grown, both intellectually and emotionally, into a person I am proud to be.

I certainly could not have gone through this process alone — I have had the help of many wonderful people to guide me and support me through this doctoral process. First, I must acknowledge my parents, whom I feel lucky to have every single day. The level of friendship and trust I feel with my mother and father have enabled me to be myself and pursue my goals without fear of judgement. In the summer of 2005, I had an internship at Intel Corporation in Hillsboro, Oregon. I planned to drive from Michigan to Oregon so that I could have a car during the summer, and I asked my parents if they would join me on the road trip. When I tell people that I came up with this idea on my own, they think that I am the craziest person in the world. But I think this anecdote best represents how much I love and am loved by my parents. I am truly lucky. And, by the way, we had a wonderful time together.

Next, I cannot express the gratitude I feel for having married the best husband I could ask for. My husband Tom is my biggest fan, always encouraging me to be the best I can be. He genuinely feels happy and proud when I accomplish something, and knowing I have him in my corner makes the world an easier place to live in. When I was working on deadlines, Tom would cook meals for me and bring them to my desk as I stared at my computer screen, encourage me to go outside for fresh air when I

had closeted myself indoors for days, and give me unsolicited backrubs when I was at my most stressed. I am more grateful to him than he knows, and I am so glad he is my partner in life.

Of course, I must also thank my little sister, Leslie, for her support these last few years. I am several years older than Leslie, and have always been accustomed to taking care of her. As she has grown older herself, and the age gap feels narrowed, she has come to take care of me on occasion. I often turn to my sister first when I need cheering, and she is always successful in making me feel better. Her infectious bubbliness when I am down remind me that the world is a beautiful place and bring me back to my usual happy self. I am proud to call her my sister and my friend, and I am grateful for her love and support.

I would be in remiss if I did not also acknowledge my primary advisor, Steve Reinhardt. I truly believe I could not have asked for a better advisor; in fact, there are days when I am uncertain that I could have navigated the waters of graduate school without Steve's support. Steve created an environment that allowed me to get comfortable, grow, and learn; and he sometimes had to play the role of psychologist as well as advisor. The numbers don't lie — computer science can be a tough field for women, but if more advisors were like Steve I believe the attrition rate would be much lower. Steve, I thank you a hundred times for your role in my completion of this dissertation.

I must also thank the other members of my committee: Trev, who gamely stepped in as co-chair when Steve left the University, and advised me beyond my expectations even though I was not working on any project of his, and can always be counted on for a laugh or a wry comment; Scott, who never seemed annoyed that I often visited with his grad students and their group turtle, Bowser; Dennis, who was willing to step in and be on my committee when another member of my committee left the University; and to Ravi, my technical mentor during that summer at Intel, whom I have always felt great affection for, and I regret not keeping in better touch with since my internship.

During my days as a graduate student, I also had a great amount of peer support. Within my research group, I could not have asked for a greater mentor than Nate Binkert, who taught me so very much about computers. He literally taught me nearly all of the tools I needed to be an effective researcher. Without him, I would not be who I am today. Ali Saidi, with whom I share great camaraderie, was a pleasure to have as an officemate, and he made dreary days in the lab go by much more quickly. I should also mention Kevin Lim, Ron Dreslinski, Korey Sewell, and Gabe Black, with whom I enjoyed working in our little office in CSE on developing M5 and other projects.

I am also incredibly grateful to my friends Victoria Fossum and Christine Vehar Jutte, with whom I shared a bond of being female graduate students in engineering entering the same year. We supported each other throughout the years, encouraging, venting, and propping up when the others were down, and I truly believe our little trio of PhDs was a major reason for all of us making it to the end. I love them both dearly and am so glad we met.

Gratitude also goes to Mike Chu, who was not only a friend during our tenure in the CSE department at Michigan, but who also helped me when I needed it as I tried to juggle finishing this dissertation with a full time job in Bellevue, Washington, where he now lives as well.

Thanks must also be given to the Lucent Foundation for funding the first four academic years of my PhD; and the Intel Foundation, for funding the last two, along with providing Joel Emer as my mentor, who is an incredible architect and took the time to speak with me and invite me to a talk at Intel Hudson. I am grateful for the opportunities and advice he provided.

Finally, I must thank my friends. I cannot name them all, but special thanks must

go to Karin Kin and Catherine Holahan, who are two of my dearest friends, and who would love me even if I never finished this dissertation.

# TABLE OF CONTENTS

| DEDICATION       | ii  |

|------------------|-----|

| ACKNOWLEDGEMENTS | iii |

| LIST OF FIGURES  | х   |

| LIST OF TABLES   | xii |

#### CHAPTER

| 1 | Introdu | uction                                   | 1  |

|---|---------|------------------------------------------|----|

|   | 1.1     | Why CMPs?                                | 2  |

|   | 1.2     | Large Scale CMPs and the Cache Hierarchy | 5  |

|   | 1.3     | Resource Allocation for a Shared Cache   | 7  |

|   | 1.4     | Thesis Statement                         | 9  |

|   | 1.5     | Contributions                            | 10 |

|   | 1.6     | Organization                             | 11 |

| 2 | Backgr  | cound                                    | 12 |

|   | 2.1     |                                          | 13 |

|   |         | 2.1.1 The Shift to Multicore             | 14 |

|   | 2.2     | Shared Cache Performance Optimization    | 15 |

|   |         | 2.2.1 Partitioning for Optimality        | 15 |

|   |         | 2.2.2   | Other Approaches to Resource Management $\ . \ . \ .$ . | 20 |

|---|---------|---------|---------------------------------------------------------|----|

|   | 2.3     | Qualit  | y of Service                                            | 24 |

|   | 2.4     | Other   | Related Work                                            | 27 |

|   |         | 2.4.1   | Operating systems involvement in cache management       | 27 |

|   |         | 2.4.2   | Latency optimizations for distributed caches            | 27 |

|   | 2.5     | Conclu  | usion                                                   | 28 |

| 3 | Shared  | Cache   | Metrics                                                 | 29 |

|   | 3.1     | Metho   | odology                                                 | 32 |

|   |         | 3.1.1   | Performance Target Selection                            | 32 |

|   |         | 3.1.2   | Optimal Cache Allocations                               | 35 |

|   |         | 3.1.3   | CMP Thread Model                                        | 40 |

|   | 3.2     | Result  | S                                                       | 41 |

|   |         | 3.2.1   | Optimal Partitions                                      | 41 |

|   |         | 3.2.2   | Comparing the "-isms"                                   | 45 |

|   |         | 3.2.3   | Baseline Weighting Choices                              | 48 |

|   |         | 3.2.4   | Policy Metrics                                          | 49 |

|   |         | 3.2.5   | Policy Evaluation                                       | 51 |

|   | 3.3     | Conclu  | usions                                                  | 55 |

| 4 | Machir  | ie Lear | ning Techniques for Discovering Salient Characteristics |    |

|   | of Poor | Perfo   | rmance                                                  | 58 |

|   | 4.1     | Metho   | odological Approach                                     | 61 |

|   | 4.2     | Ridge   | Regression                                              | 62 |

|   |         | 4.2.1   | Background                                              | 62 |

|   |         | 4.2.2   | Isolating Features of Poor Performance                  | 67 |

|   |         | 4.2.3   | Evaluation Environment                                  | 71 |

|   |         | 4.2.4   | Results                                                 | 74 |

|           | 4.2.5    | Conclusions                                 | 77  |

|-----------|----------|---------------------------------------------|-----|

| 4.3       | Decisi   | on Tree Analysis                            | 78  |

|           | 4.3.1    | Background                                  | 78  |

|           | 4.3.2    | Isolating Features of Poor Performance      | 81  |

|           | 4.3.3    | Evaluation Environment                      | 83  |

|           | 4.3.4    | Results                                     | 84  |

| 4.4       | Conclu   | usions                                      | 90  |

| 5 Scalab  | le Light | tweight Adaptive Management                 | 92  |

| 5.1       | SLAM     | ι                                           | 95  |

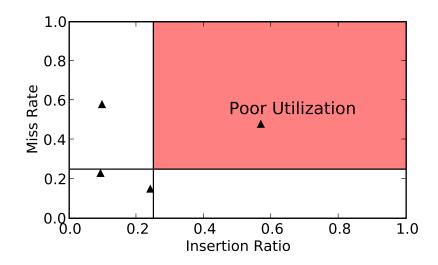

|           | 5.1.1    | Detecting Poor Utilization                  | 96  |

|           | 5.1.2    | Mitigating Poor Utilization with Throttling | 99  |

|           | 5.1.3    | Honing SLAM                                 | 99  |

|           | 5.1.4    | Using SLAM for QoS                          | 102 |

| 5.2       | Metho    | odology                                     | 103 |

|           | 5.2.1    | Metrics                                     | 104 |

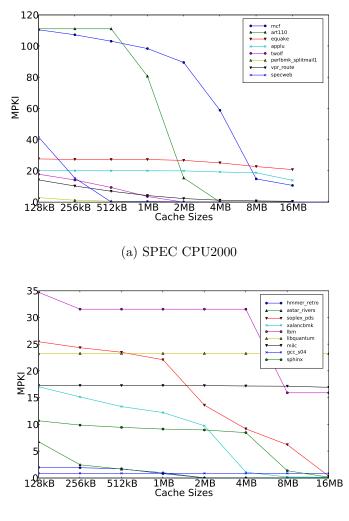

|           | 5.2.2    | Benchmarks                                  | 104 |

|           | 5.2.3    | Simulation Environment                      | 107 |

| 5.3       | Result   | S                                           | 108 |

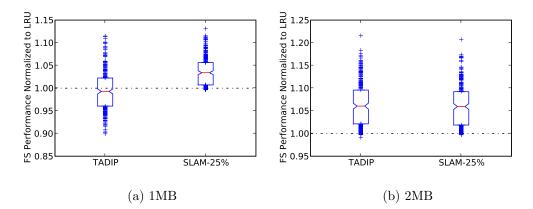

|           | 5.3.1    | Detailed Studies                            | 108 |

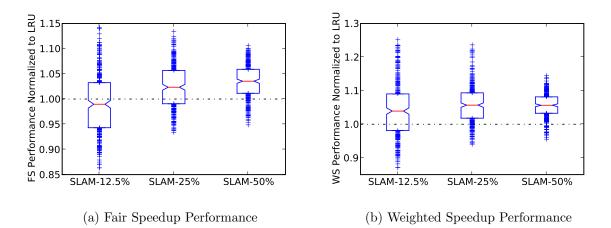

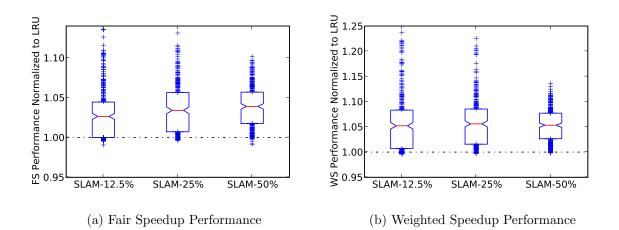

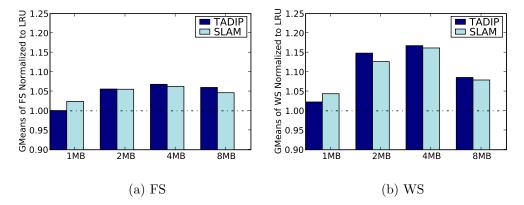

|           | 5.3.2    | Comprehensive Studies                       | 110 |

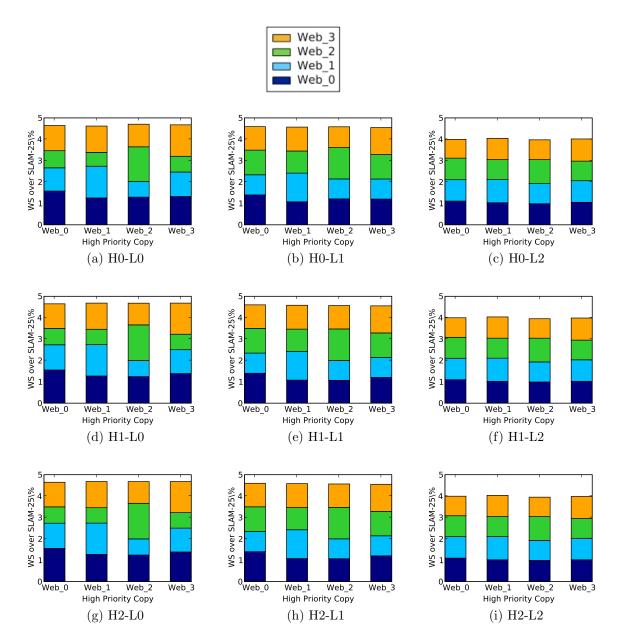

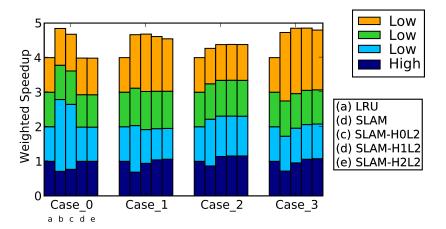

|           | 5.3.3    | QoS                                         | 112 |

| 5.4       | Conclu   | usions                                      | 117 |

| 6 Conch   | usions a | nd Future Work                              | 119 |

| BIBLIOGRA | PHY .    |                                             | 123 |

# LIST OF FIGURES

### Figure

| 1.1  | LCMP cache sharing                    | 5   |

|------|---------------------------------------|-----|

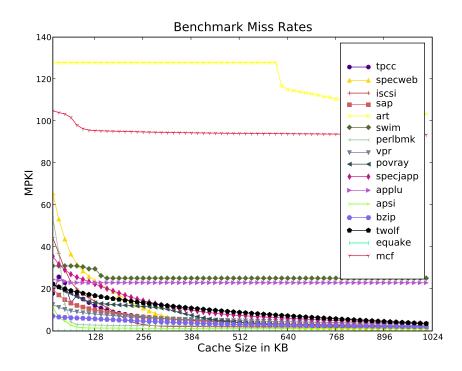

| 3.1  | Miss Rate Curves                      | 38  |

| 3.2  | Two-application Partitioning Example  | 41  |

| 3.3  | Four-application Partitioning Example | 42  |

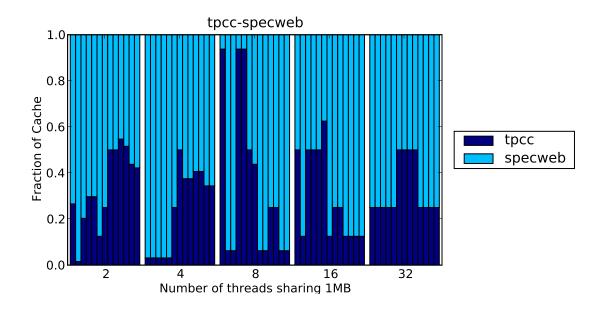

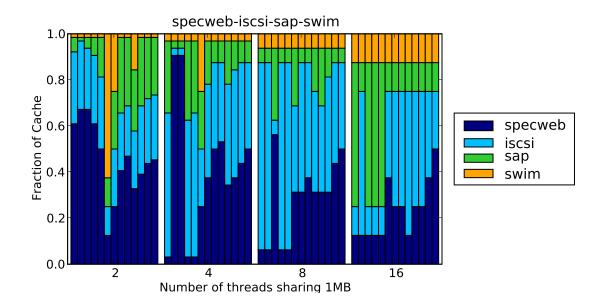

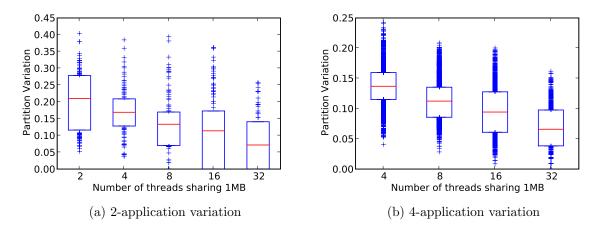

| 3.4  | Partition Variation                   | 43  |

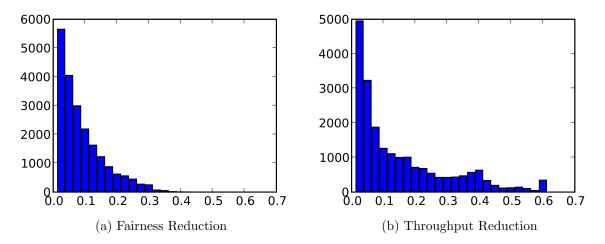

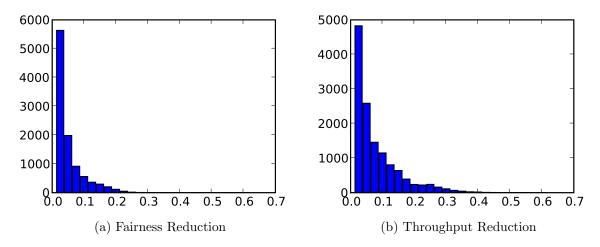

| 3.5  | Communist vs. Utilitarian Histograms  | 45  |

| 3.6  | Utopian Histograms                    | 48  |

| 3.7  | Baseline Weighting Choices            | 49  |

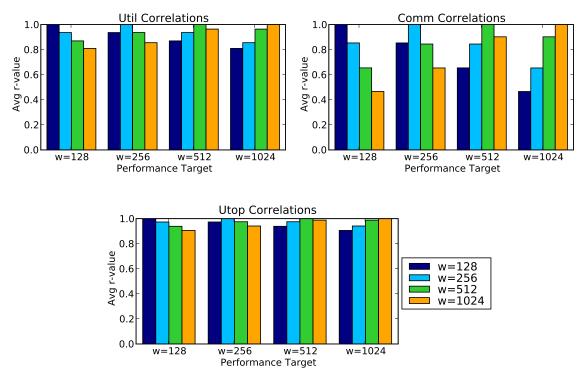

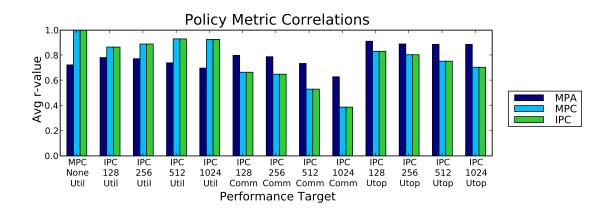

| 3.8  | Policy Correlations                   | 51  |

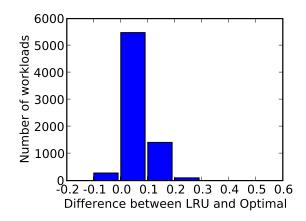

| 3.9  | LRU vs. Perfect Raw MPC Partitioning  | 52  |

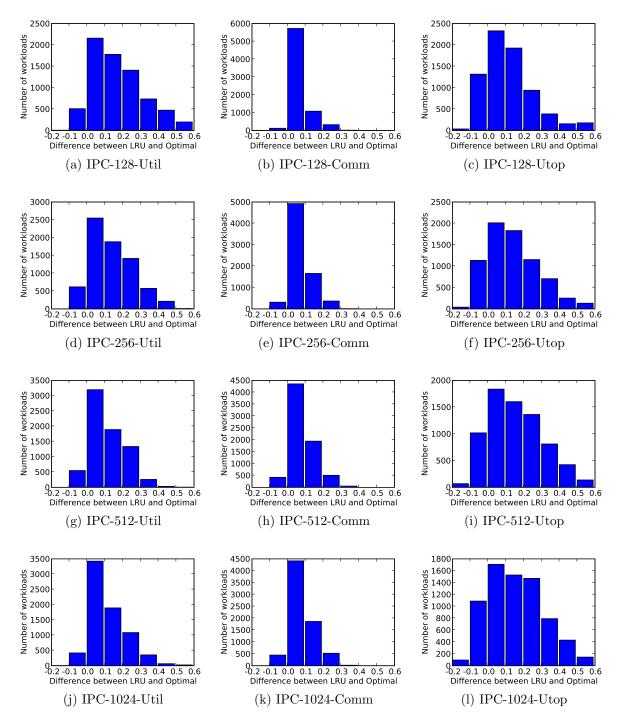

| 3.10 | Policy Evalutaions                    | 54  |

| 4.1  | Sample Workload Plot                  | 70  |

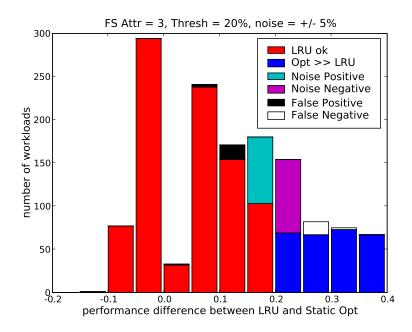

| 4.2  | Stacked Histogram Results             | 76  |

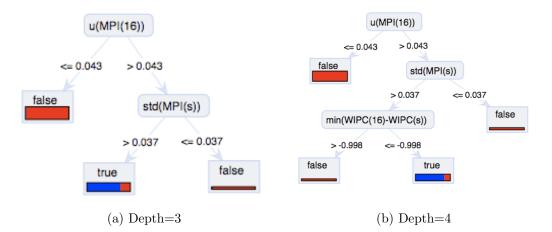

| 4.3  | Decision Tree: YAGGA Feature Set      | 84  |

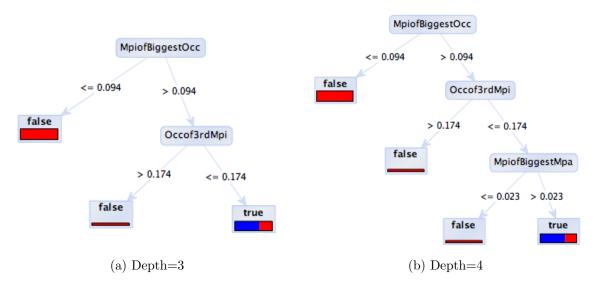

| 4.4  | Decision Tree: New Feature Set        | 85  |

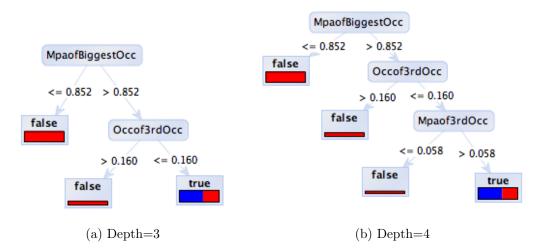

| 4.5  | Reduced Feature Decision Tree         | 87  |

| 5.1  | SLAM Intuition                        | 97  |

| 5.2  | Varying MPAC Threshold                | 00  |

| 5.3  | SLAM with Dueling                     | 01  |

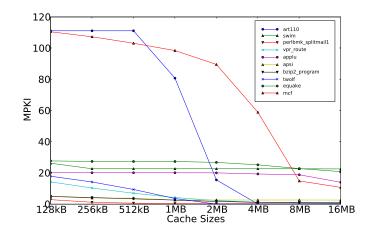

| 5.4  | MPKI Graph                            | .05 |

| 5.5  | MPKI for SPEC2000 Benchmarks          | .07 |

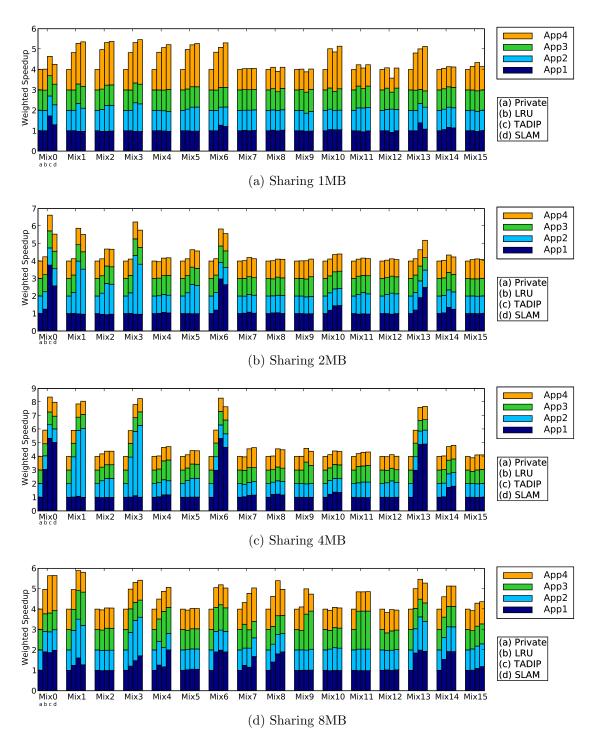

| 5.6  | Detailed Results                      | 09  |

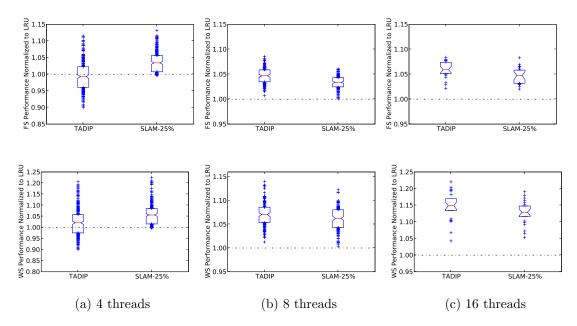

| 5.7  | Geometric Mean Results    | 110 |

|------|---------------------------|-----|

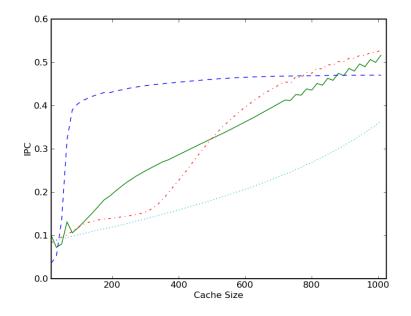

| 5.8  | Varying Cache Size        | 111 |

| 5.9  | Scalability Results       | 112 |

| 5.10 | Strawman Proof of Concept | 114 |

| 5.11 | QoS Results               | 116 |

## LIST OF TABLES

#### Table

| 2.1 | Cache Partitioning Proposals                                                                  | 16  |

|-----|-----------------------------------------------------------------------------------------------|-----|

| 3.1 | Performance Targets                                                                           | 33  |

| 3.2 | 16 workloads $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 36  |

| 4.1 | Sample Supervised Learning Data                                                               | 59  |

| 4.2 | 214 Member Feature Set                                                                        | 67  |

| 4.3 | 125 Member Feature Set $\ldots$                                                               | 82  |

| 4.4 | Learning Results                                                                              | 90  |

| 5.1 | Workload Mixes                                                                                | 106 |

| 5.2 | Service Level Thresholds                                                                      | 113 |

## CHAPTER 1

#### Introduction

The processor industry has recently undergone a rapid and dramatic shift from uniprocessor systems to chip multiprocessor (CMP) systems, where multiple compute cores reside on a single silicon die. Intel's latest notebook/desktop processor, the Core i7, has four cores on a chip [27], while their latest Xeon server processors, the 7400 series, have up to six cores on a single die [28]. Similarly, AMD has gone the multicore trajectory with six cores announced for the Phenom on the desktop, and six cores currently in the latest Opteron server offering [2, 3]. Sun's UltraSPARC T2 processor, known as the Niagara 2, is aimed at the server market and has eight cores on a single chip [59]. This, when as late as 2005, the desktop domain was universally uniprocessor, with each silicon chip having only a single core on it. Not only has the industry rapidly moved to a multicore paradigm, but there is ample evidence that the number of cores on each chip will continue to increase, as major vendors continually announce plans for chips with more and more cores.

On these CMPs, there are a number of resources that, for flexibility and/or cost reasons, are not replicated for each core. These resources are thus shared between all cores on the platform. This situation naturally leads to potential resource contention issues, and the problem is exacerbated when the number of cores on a chip increases. One of the primary resources vulnerable to contention issues is the on-chip cache. In a uniprocessor system, the stream of memory accesses going from the CPU to the cache comes from a single application at a time, while in a CMP system the accesses are finely multiplexed between the simultaneously running threads, which may not be cooperative. The fundamental issue is one of destructive interference, where oblivious and disparate threads may disrupt the cache usage of the other threads sharing the cache.

This dissertation specifically examines the effects of contention for the shared onchip cache resource in large-scale chip multiprocessors. As CMPs continue to scale, the potential for problems in resource allocation only increases. Additionally, as multi-core offerings increasingly become multi-threaded, as Sun's Niagara and Intel's Nehalem processors are, the issue of cache contention becomes even more dramatic when considering hardware threads, and not just cores.

Alongside contention issues, it is unclear how best to measure performance for a cache shared by large numbers of threads. Given that the resource is shared, there is a tension between overall good and the welfare of individuals. In this dissertation I present an analysis of ways to measure performance in a CMP system, present an analytical process based on machine learning techniques to examine the nature of sharing problems, and introduce a highly scalable mechanism for managing a shared cache to mitigate highly destructive sharing situations. This mechanism is also easily extensible to providing differentiated quality of service in shared caches.

### 1.1 Why CMPs?

In the continual march towards higher performance computers, there have been two overarching methods for extracting improvement: higher clock speeds (*i.e.*, working faster) and greater parallelism (*i.e.*, doing more at once). Combining these two methods has yielded the spectacular rise in computing performance in the last several decades. Historically, achieving greater parallelism has meant finding ways to extract what is called instruction level parallelism (ILP) from running applications, *i.e.*, finding instructions from the same instruction stream to execute simultaneously. Designers have squeezed out more and more ILP over the years using techniques like out-of-order execution, having large instruction windows, using branch predictors, and superscalar execution in order to find more instructions to have in flight at the same time.

However, this two-pronged approach has become problematic in recent years due to thermal issues. Each time a transistor switches, it uses energy, resulting in power usage as shown by Equation 1.1, where P is power, C is the capacitance discharged at every transistor, V is the supply voltage used to power the transistor, and f is the operating frequency:

$$P \propto C V^2 f \tag{1.1}$$

At the same time, maximum operating frequency is roughly linear in V:

$$f \propto V$$

(1.2)

Thus, increasing frequency of operation causes roughly *cubic* increases in power. We have reached the point where further increases in power are infeasible, and as Mudge tells us, reducing power consumption should be a "first class" design constraint in computer architecture [44].

At the same time, extracting ILP is rapidly coming to a point of diminishing returns, for several reasons. First, the low-hanging fruit is has been picked, and it is becoming more and more difficult to eke out smaller and smaller increases in ILP. Second, adding more ILP-improving widgets generally means much higher power consumption; meanwhile reducing power consumption is now an important design consideration, as just described. Moore's Law is still providing designers with more transistors at each generation, but these transistors can no longer be used primarily to create more ILP-extracting widgets. These additional transistors can, however, be used for extra processor cores on a die.

Putting multiple compute cores on a die has a number of effects. The first is that, in theory, a given task T could be completed in 1/Nth the time of a single-thread machine by merely splitting the task into N equal pieces and running it on N threads simultaneously. The second is that given this scenario, a chip with N simultaneous threads could reduce its operating frequency by 1/Nth, and still finish T in the same amount of time as a single-thread machine. Recall the cubic relationship between frequency and power consumption, and suddenly multicore is a means to get off the trajectory of exponential relationships of power to performance. However, there is the practical consideration that it is much easier said than done to split a task into perfectly overlapping pieces. The amenability of a task or program to be easily subdivided into independent chunks is called Thread Level Parallelism (TLP).

The shift to CMPs has thus taken different trajectories. For the desktop/notebook domain, the "multi" in multicore is on a small scale. Intel's Core line now has four relatively powerful cores on a chip, owing to the fact that desktop applications continue to have plentiful ILP but little TLP. In the server domain, however, TLP is abundant but there is much less ILP available [19]. In this market, it makes sense to have larger-scale CMPs, where many cores share a single die to maximize throughput rather than single-thread performance. Sun's latest Niagara is a 64-way multi-threaded processor, while Intel's plans for their Nehalem architecture to have up to eight cores with two threads each, or 16 simultaneous threads. I expect this number to increase in the coming decade, and the remainder of this dissertation focuses on large server-scale platforms.

#### 1.2 Large Scale CMPs and the Cache Hierarchy

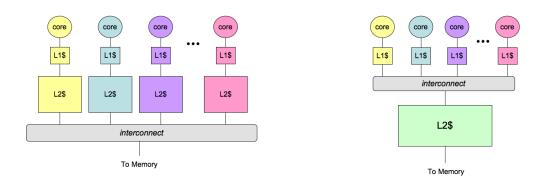

This dissertation focuses on the design and performance of the cache hierarchy for a large-scale CMP (LCMP). The most naive and straightforward design is to have all levels of the cache be private to their own cores; *i.e.*, a core cannot utilize cache space that does not belong to it. This scheme is demonstrated in Figure 1.1a in a CMP with a two-level hierarchy.

The downfall to this approach is the lack of flexibility. If core A's particular sub-hierarchy is not being fully utilized due to the nature of the application running on that core, while core B's sub-hierarchy is being taxed to the limit, there is no flexibility to allow for core B to use the unused space owned by core A. Even worse, in CMP designs where a core is shut down for power savings, the cache attached to that core is totally useless.

(a) LCMP with private caches

(b) LCMP with shared caches

Figure 1.1: LCMP cache sharing - On the left is a naive cache hierarchy implementation for LCMPs. Each core has a private cache hierarchy of several levels all to itself. On the right is a more flexible implementation, where each core has potential access to the entire L2 cache.

Given the likelihood of this scenario, the natural next step is to consider shared caches. If all cores can access any available cache on the platform, flexibility is maximized and the likelihood of unused blocks is limited. However, this flexibility also comes at a cost in terms of access times. If the L1 cache were shared across a platform, L1 access and hit times – vital to the performance of a platform – would be negatively affected. Thus, a typical platform will have private caches closer to the core, in order to preserve small sizes, close proximity, and fast access and hit times; but have shared caches closer to memory, where these latencies are not so tightly constrained. An example of this style of platform with a two-level cache hierarchy is shown in Figure 1.1b. This thesis focuses on this two-level topology.

The reasons for sharing a last-level cache (LLC) do not stop here. First, different software threads from server workloads often run the same binary but on different data, so that instruction addresses are shared between threads. Having every instruction address be replicated across all (private) last-level caches seems intuitively wasteful. Having a single copy of instruction data reside on the die to be shared amongst relevant software threads makes much more sense. Furthermore, many servers are operated as virtual machine hosts, and different clients who may be running the same guest operating system can also run the same operating system binary [61]. Both of these scenarios involve read-only instruction addresses, but studies show that there is also data sharing in a number of commercial server applications, where data is being passed between different threads for reading as well as writing [19, 36]. By sharing a cache, this shared data can be kept coherent without coherence traffic, which is yet another reason for sharing.

For these reasons, this shared last-level cache approach is used by Sun's Niagara 2, which has a shared L2 cache across all 64 threads on the platform; as well as all of Intel's multicore processors in a scheme known as Smart Cache, where the L3 is shared by all cores; and also AMD's multicore machines in a scheme known as AMD Balanced Smart Cache.

#### **1.3** Resource Allocation for a Shared Cache

As with any shared resource, there comes a risk for contention issues and/or suboptimal allocation. Caches as we know them today do not have explicit mechanisms to ensure fairness amongst sharers; indeed typical caches today do not even track which accesses are on behalf of which thread — thus all accesses from all threads are treated equally. The thread-blind nature of caches makes it difficult to perform any regulation of resource usage, and leaves the cache ripe for potential sharing problems.

Destructive interference occurs when threads spend their time evicting each others blocks and waiting while bringing their own blocks back into the cache rather than making forward progress. The lack of cooperation among threads can easily create situations such as these, particularly in the presence of streaming workloads, which stream their way through large numbers of accesses and fill the cache (thus evicting others' data) with blocks that will not be used again.

These scenarios are likely to be exacerbated and become more common as the number of threads on a platform increase, making protection mechanisms to circumvent such issues a necessary part of shared cache design. The essential problem is that of resource allocation—finding a way to intelligently allocate cache space amongst different threads in order to provide good performance.

The classic approach to solving resource allocation uses marginal cost analysis [21], which utilizes marginal gain calculations with incremental increases in resources to determine optimal allocations. There are several flavors of marginal cost analysis algorithms, depending on domain specifics such as whether the marginal gain function is convex or concave, whether the resource being allocated is continuous or integer, *etc.* However, all of these algorithms are compute intensive and assume a high level of abstraction when performing these calculations.

There have been a number of attempts [60, 57, 48], however, to translate these algorithms into cache management heuristics, where the general structure of the so-

lution follows a "assign, monitor/enforce, and adjust" format. Execution is divided into epochs, where re-allocations occur in between epochs, which cannot be too short in order to capture the full effect of the last re-allocation, but must be short enough to be nimble and capture changes in application behavior. Convergence to a solution would be tricky enough for four or eight threads, but convergence with hundreds of agents will be very difficult if not impossible under current design constraints. I will discuss these approaches in further detail in Chapter 2.

The distinct nature of the particulars of a cache resource allocation make the problem inappropriate for marginal cost analysis. There are few points to keep in mind for the shared cache resource allocation problem:

- 1. There is a distinct latency between the time cache space is given or taken away and the time to know whether that change has the desired effect. The implication is that changes in allocation cannot be made too rapidly because the effects of each change must be known before making the next change.

- 2. The nature of an application's memory access stream may change over time. The implication here is that not only would convergence to an optimal allocation take a long time due to the latency mentioned above, but the goal may itself be a moving target due to the transient nature of application behavior.

- 3. Hit times to a cache (*i.e.*, the amount of time it takes for a requested block that resides in the cache to be returned to the CPU), are a vitally important performance characteristic and cannot be sacrificed. In other words, the allocation decision mechanism must not affect hit times any computation or calculation must not be on the critical path.

- 4. The cache is a highly optimized piece of hardware on a chip; ideally whatever mechanism is proposed would incur minimal changes to cache design.

5. In the domain of LCMPs, any mechanism would need to scale well. Many mechanisms that would have reasonable complexity in the small-scale can quickly become untenable in the large.

Based on this characterization of the problem, it is evident that marginal cost analysis is an overly complex approach to large-scale cache allocation problems.

I propose another approach that is "correlatively optimal", which, rather than explicitly searching for optimal, exploits some characteristic that will trend towards a good solution in the general case. I take as my inspiration the simple Least Recently Used (LRU) replacement algorithm that dictates cache block allocation in caches today. Current caches to not try to explicitly perform optimal replacement in a cache; rather they use LRU to exploit the temporal locality properties of most programs, resulting in generally good performance. Similarly, cache prefetching algorithms do not try to explicitly perform perfect prefetching; instead they exploit some known tendencies of memory access patterns and prefetch cache blocks based on that principle. In both of these examples, the cost/benefit ratio falls strongly in favor of the simple solution that provides generally good (though not optimal) performance, rather than a complex solution that might provide minimal added performance benefit.

#### 1.4 Thesis Statement

This thesis examines the interaction between cache space and system performance in the domain of large-scale chip multiprocessors in order to inform the design of a scalable, feasible shared cache management mechanism that provides good performance. This thesis demonstrates that selecting a specific definition of "good performance" for shared caches is inherently difficult, given that there are many competing definitions of "good" that can be quite incompatible with one another. As a result, a preferable approach is to search for correlatively optimal characteristics that would put a floor on the performance of pathologically poor situations under any measure, instead of focusing on a single particular metric of performance.

This dissertation uses offline machine learning techniques to effectively extract salient characteristics in poor cache-sharing situations. These characteristics can be used to predict poor performance in previously unseen environs, *i.e.*, with application mixes not used in training the machine learning algorithm.

This approach to building a mechanism to improve cache sharing is validated by the success of SLAM (Scalable, Lightweight, Adaptive Management), a framework for shared caches which can detect and mitigate pathological cache sharing situations, designed with the information yielded from the machine learning techniques. SLAM demonstrates the validity of using correlatively optimal characteristics to shape cache allocation rather than a complex and explicit search for optimal; SLAM is scalable, feasible, has light-weight implementation requirements, and good performance results. In addition, SLAM is a natural candidate for providing differentiated quality of service (QoS) in caches, whereby certain threads are given preferential treatment because of higher priority.

#### 1.5 Contributions

The contributions of this thesis include:

- an exploration of the objective function space for shared caches resulting in meaningful insights into the selection of cache design objectives;

- demonstrating the utility of existing machine learning techniques for effective offline analysis of the cache resource allocation problem;

- a comparison of two machine learning techniques, one effective, the other not, for this particular problem space;

- the presentation of a mechanism to provide scalable fairness in shared caches, suitable for implementation even in large-scale chip multiprocessors, costing only tens of bits per thread, and is actually feasible in present implementations;

- the presentation of two performance measurement techniques called MPAC (Misses Per Access Counter) and RIT (Relative Insertion Tracker) for tracking shared cache performance characteristics, which are the cornerstone of SLAM and could be useful in other system optimization domains;

- the demonstration of the SLAM framework as a natural provider of differentiated quality of service in the cache.

### **1.6** Organization

The remainder of this thesis is organized as follows. Chapter 2 discusses some background and related work for the cache resource allocation problem. Chapter 3 discusses my examination of the objective function and metric space for shared caches. Chapter 4 discusses the machine learning techniques used for the analysis in this dissertation. Chapter 5 discusses the major contribution of this thesis, the SLAM framework for managing shared caches. I conclude and discuss future work in Chapter 6.

### CHAPTER 2

### Background

A modern computer performs its tasks by following a program written prior to the execution of the task. To do this, a computer must access the stored program instructions, then execute the instruction in the CPU, which may involve accessing previously stored data. When finished, the CPU may be instructed to store results back to memory. Thus, there can be non-trivial amounts of data movement between the CPU and stored memory.

Unfortunately, from the earliest days of computing there has been a gap between processor instruction execution speeds and memory speeds. In other words, memory cannot keep up fast enough to feed the CPU with instructions nor the data required to execute the instructions.

To address this problem, designers began using caches (small, fast buffer memories between the CPU and memory) in order to try to hold portions of memory that will be used in the near future [52]. The IBM System/360 Model 85 is one of the first documented machines to utilize caching [40], and from there, caches have moved from being external to the silicon die to residing on-chip, increased in size, and changed from a mono-level system to two and three levels of cache on a chip. The cache has become an integral part of system design, and plays a large role in the overall performance of a computational system, particularly as the disparity between CPU speeds and memory speeds has continued to increase.

#### 2.1 The Basics of Cache Operation

Vital to the efficacy of these high-speed cache buffers is the selection of the subset of addresses to place in the buffers. At the crux of the question is not which addresses to bring into the cache, but *what to replace* when the cache is full. Research involving the paging of virtual memories in multiprogrammed environments had already led to the concept of a *working set* (*i.e.*, a set of data of which quick access times would provide efficient performance of the corresponding process) [14]. Denning, who coined the term working set, posited that pages used in the recent past were a good predictor for pages to be used in the near future. Around the same time, Belady performed a study of replacement heuristics for virtual memory and found that employing a *least recently used* (LRU) algorithm, which evicted pages that had been used furthest in the past, generally provided performance closest to optimal [6]. These two ideas together led to the *locality principle*, which has become a cornerstone of resource allocation resolution in virtually all of computer science [15]. These principles apply just as well to cache memories as virtual memories.

For the purposes of cache management, the locality principle means that memory addresses from a given application tend to exhibit both temporal and spatial locality. Temporal locality implies that an address used now is likely to be used again in the near future. Spatial locality implies that an address used now is likely to be near or adjacent to an address to be used in the future. The intuition behind the success of the LRU algorithm is how it takes advantage of the temporal locality principle by keeping the most recently used address blocks close to memory.

Since fully associative memories tend to be both expensive and slow [52], caches are generally built as smaller sets of associative memories. Any address requested in the cache is indexed into only a single associative set, and any address block to be replaced to make room for the incoming block is taken solely from within this set. The associativity of a cache indicates the number of blocks within a set, such that an n-way associative cache would have n blocks within each set, and the LRU block refers to least recently used block in that set of n blocks.

Addresses are used to index into a set based on a subset of the address bits; the remainder is stored in the cache along with the affiliated data in a *tag array* as an address tag. Address tags are used to distinguish between the multiple addresses that can index into a set [52].

Modern caches are generally all built as described, and this thesis evaluates all proposals under the lens of feasibility in this paradigm.

#### 2.1.1 The Shift to Multicore

LRU is quite effective as a replacement policy for caches in uniprocessor systems because LRU acts as a predictor for which address blocks are to be used in the near future within the stream of instructions from its affiliated process. However, once a cache becomes shared among multiple simultaneous threads of execution, LRU may not be as effective because the stream of accesses to the cache is no longer from a single source. Rather, accesses can be finely interleaved among all simultaneous processes. As a result, researchers have moved their focus towards making caches thread-aware and differentiating between accesses from different threads in order to make space allocations decisions in the context of a shared cache [12, 18, 33, 35, 37, 48, 54, 57, 64, 65, 66]. Whereas the goal of the LRU replacement policy is to try to ensure that blocks to be used in the near future are kept close to the processor, the goal of any new mechanism has to balance the needs of multiple threads.

Likely the first piece of work on studying a cache shared between separate streams of accesses is by Stone, *et al.* While not involving a multicore platform, this study developed a model for evaluating the optimal allocation of cache memory between distinct streams of accesses, noting that the overall miss rate of a cache shared by multiple streams is just the average of the miss rates of the contributing streams [55]. Thus, finding an optimal allocation among streams requires modeling a function of the form

$$F(Cache Allocation) = MissRate$$

for each stream, summing them, and solving for the minimum. Additionally, Stone, et al. performed empirical studies involving optimizing allocation for data streams versus instructions streams in a single application, and found that empirically, LRU did remarkably well relative to optimal—but they were unable to mathematically bound the delta between LRU and optimal in a rigorous manner.

#### 2.2 Shared Cache Performance Optimization

With the move towards shared caches and the potential for inter-thread interference in cache usage, a number of proposals have emerged for shared cache performance optimization, many using the marginal gain analysis approach described in Chapter 1. The various proposals are described below.

#### 2.2.1 Partitioning for Optimality

Cache partitioning is a prominent strategy for shared cache management, in which a scheme tries to dynamically determine a specific optimal cache partition for each hardware thread [57, 65, 18, 35, 48]. Each scheme monitors and enforces cache usage, and then adjust partitions based on recorded measurements on an epoch granularity. These schemes each have four attributes: 1) measurement techniques, whereby marginal utility is measured over an epoch, 2) partition assignment heuristics, whereby data from the measurement techniques are used to assign partition

| Proposal                        | Measurement            | Partitioning Heuristic | Partition Enforcement | Proposed Epoch Length |

|---------------------------------|------------------------|------------------------|-----------------------|-----------------------|

| Dynamic Partitioning [57]       | Per-way Hit Counters   | Per-block Greedy       | Modified LRU          | 5M cycles             |

| Fast and Fair [65]              | Per-Thread Shadow Tags | 256KB Greedy           | Modified LRU          | 100M cycles           |

| Partitioning-aware LRU [17]     | Per-Thread Victim Tags | Local Search           | Modified LRU          | 2000 misses           |

| Fair Caching [35]               | Profile + Miss Rates   | Local Search           | Modified LRU          | 10K accesses          |

| Utility Cache Partitioning [48] | Per-Thread UMON        | Per-block Greedy       | Modified LRU          | 5M cycles             |

Table 2.1: Cache Partitioning Proposals - This table describes the approaches for several optimal cache partitioning proposals with respect to four major attributes.

sizes to each hardware thread for the next epoch, 3) partition enforcement techniques, whereby the assignments are enforced during an epoch, and 4) epoch length. Table 2.1 describes the approaches for these schemes.

Dynamic Partitioning, proposed by Suh, *et al.* use per-thread, per-way hit counters to approximate the marginal gain of each way for each thread. Each time a hit occurs in a particular way for a particular thread, the affiliated counter is incremented. Thus each counter approximately represents the marginal gain in cache hits for its thread by having that way. Every 5 million cycles, it uses a greedy algorithm to partition the cache, block by block, to individual sharers based on the measured marginal gains. A modified LRU policy (described later in this section) enforces partitions [57].

Fast and Fair, proposed by Yeh and Sherwood, uses per-thread shadow tags, *i.e.*, a complete set of duplicated tag arrays, for each hardware thread in the system to track what *would* happen to the hit rates of each thread assuming sole ownership of the cache. Every 100 million cycles, the cache is partitioned in chunks of 256kB to individual sharers based on the shadow tag measurements. A modified LRU policy enforces partitions [65].

Partitioning-aware LRU, proposed by Dybdahl, *et al.* use per-thread victim tags to measure the marginal gain for each thread of having one more way. Each cache set has a single extra tag associated with it for storing the most recent eviction; hits to this victim tag indicate that one more way allocation would have resulted in more hits. There is also a counter per thread for the LRU way of the cache, which is also incremented upon hits in that way. Every 2000 misses, if the thread with the most to gain from having an additional way as measured by the victim tag counter exceeds the thread with the most to lose from having its LRU way taken away, an additional block per set is allocated for the gaining thread for the next epoch. A modified LRU policy enforces partitions [17].

Fair Caching, proposed by Kim, *et al.* focus on maximizing fairness in a cache rather than minimizing miss rates; thus the measurement technique is quite different. Applications are profiled beforehand running alone on a shared platform to get baseline miss rates. At run time, shared miss rates are tracked and compared against these baseline rates. Every 10,000 accesses, blocks are taken from the thread performing the best relative to baseline rates and given to threads performing the worst. A modified LRU policy enforces partitions [35].

Utility Cache Partitioning, proposed by Qureshi and Patt, uses a monitoring mechanism called UMON (Utility Monitor) for each hardware thread. Essentially, a UMON is a sampled version of the shadow tags used by the Fast and Fair proposal; instead of having a full duplicate of tags for each thread, only a subset of sets are used for measurement in order to save tag storage space. The subset is presumed to be representative of the entire cache. Every 5 million cycles, a greedy algorithm allocates blocks to each thread, block by block, based on the measurements of the UMONs. A modified LRU policy enforces partitions [48].

An analysis of the overheads of each portion of each technique is described further below.

Measurement techniques: Dynamic Partitioning relies on per-way hit counters to measure the approximate marginal gain of a way for a thread. The technique is lightweight (one counter per way, per thread), but is prone to inaccuracies because of noise from inter-thread interference, which would increase as a platform scales to greater numbers of threads. Fast and Fair, on the other hand, is a storage heavyweight and cites 32-way shadow tags per thread to measure the exact marginal gains of 256KB chunks of cache, which they estimate to be a 10% area overhead on a 4-thread platform. Partitioning-aware LRU needs two counters and one register per thread, plus a single shadow tag per set per thread, representing the most recent eviction of of each set, which is relatively lightweight. Fair Caching requires a static profile of a thread's entire execution, and miss rates are then measured online. While this is low storage overhead, in practice the profiling is unlikely. Finally, the UMONs used in Utility Cache Partitioning (UCP) are sampled shadow tags, *i.e.*, shadow tags for a subset of the sets in a cache. There is one UMON per thread in a system. Out of these proposals, only Partitioning-aware LRU, with a measurement storage overhead of 3N counters/registers and TagWidth \* NumSets \* N bits of shadow tag storage; and UCP, with a measurement storage overhead of Assoc \* TagWidth \* 32 \* N bits for shadow tags, could conceivably be scaled into the hundreds of threads.

**Partitioning heuristics:** The partitioning heuristics used by these schemes can be divided into two camps — greedy algorithms and local search algorithms. The schemes with greedy algorithms attempt to achieve the optimal partition based on measurements from the previous epoch, while the local search algorithms only perturb allocations slightly, such that each epoch is only a step in the search for convergence to an optimal partition. The computation required for the greedy algorithms as number of threads increases simply does not scale; indeed most of the proposals were tested on two-thread systems. The exception is Fast and Fair, which was evaluated on a 4-thread system and mitigates potential scaling issues by allocating on a granularity of 256KB at a time rather than on a block granularity, but is still not scalable. The schemes employing local search require much simpler computation, but are slow to converge, even more so as platforms scale. Both Fair Caching and Partitioning-aware LRU make a single pass through their measurements from the previous epoch and trade block allocation from the best and worst performers. Even on a platform with 64 threads, convergence could be painfully slow.

**Partition enforcement:** One thing all the schemes in Table 2.1 share is the use of a modified LRU replacement policy, whereby all blocks in a cache are tagged with a thread-ID bitfield, amounting to  $log_2(N)$  bits for every block in the cache, where is Nis the number of hardware threads. This is significant overhead as the value of N and cache sizes increase. The cache usage of every thread is tracked by incrementing its usage counter when a line is brought into the cache, and decrementing it when a line belonging to it is evicted. In order to maintain assigned allocations, upon replacement the LRU block of the desired thread is found and evicted. While replacement may not be on the critical path, this departure is not a trivial modification in modern caches, which by and large employ pseudo-LRU algorithms because true LRU is too high overhead for high-associativity caches. PLRU algorithms (described by Al-Zoubi, et al. [1]) take shortcuts to evict a block close to but not necessarily LRU, but the problem characteristics that are leveraged to achieve these shortcuts disappear when seeking the LRU block belonging to a certain thread, increasing the costliness of the replacement algorithm.

Worthy of note here is a proposal from Xie and Loh [64], which is essentially an alternative to partition enforcement and could be used in conjunction with any of the measurement techniques, partitioning heuristics, or epoch lengths described in Table 2.1. The authors present a novel way to pseudo-partition caches in order to avoid bit-tagging overheads from exact cache tracking. Promotion/Insertion Pseudo-Partitioning effects allocations close to prescribed partitions by manipulating the insertion and promotion policies of the cache, such that blocks can be placed in arbitrary locations in a set, and can be promoted arbitrary numbers of spots on an access, rather than always going to the MRU position. In practice, and particularly with respect to pseudo-LRU algorithms, this is very difficult to implement.

**Epoch length:** Epoch length admittedly should differ from between local search heuristics and greedy algorithms. In cases of local search, the algorithm takes small steps towards optimal every iteration; thus epoch length should be relatively short in the hopes that convergence could happen within a reasonable number of iterations. But since each iteration of the greedy algorithm is computationally intensive and hopes to find an optimal allocation each time, the epoch length should be longer in order to amortize computation cost, as well as measure enough information to make a good decision. However, an epoch that is too long risks missing phase changes in program behavior or context switches. In practice it is difficult to determine an epoch length that is appropriate for the plethora of workloads that could be potentially run on a CMP platform. Sherwood et al. [51] show that it is not possible to have a universal phase length that applies to workloads in a general sense and, even within an application, phase lengths can vary. Su et al. [56] find that, while reconfigurations of a shared cache based on optimal phase lengths determined offline can provide good performance, fixing an optimal phase length is not effective across workloads, nor is it easy to dynamically predict phase lengths that approach the offline optimal.

#### 2.2.2 Other Approaches to Resource Management

In general, partitioning for optimality is unrealistic in the large scale for several reasons:

- 1. The convergence to an optimal solution in a system with many agents is likely to be overly complex and take multiple iterations (of epochs taking non-trivial amounts of time) to approach optimality.

- 2. At the same time, the nature of the domain being optimized is constantly shifting—in the large scale, phase changes and context switches are likely to occur before convergence.

- 3. Enforcement is also a non-trivial task, generally requiring the tracking of each thread's usage and the restriction of which thread's data can be replaced in the cache, which would represent a significant departure from the functionality of current caches.

- 4. Research has also shown that determining appropriate epoch lengths is not a simple task [51, 56], an area of research in and of itself.

Fundamentally, optimality is precise, and being precise when juggling the needs of N agents, where N is large, is bound to be complex and difficult. This is exacerbated when enforcing precision is not totally straightforward in practice, and the precise definition of optimality is not static. There are a number of other papers that approach shared cache resource allocation in a different way than the partitioning paradigm.

Chang and Sohi propose Cooperative Cache Partitioning (CCP) [12]. CCP consists of a hybrid approach, using Cooperative Caching(CC) [11] and Multiple Timesharing Partitions (MTP). CC approaches the cache sharing problem from a different level of abstraction. It is fundamentally a LRU-based scheme and does not evaluate the relationship between cache space and performance, rather it is a mechanism for optimizing latencies within a distributed shared cache structure. MTP, however, is a partitioning approach that time-shares cache partitions rather than using a single partition allocation. While MTP is not exactly a proposal to partition for optimality, it maintains many of the drawbacks of the schemes described in the previous section. MTP essentially cycles threads through large, unfair allocations of cache so that over a larger time quantum, macro-level fairness is achieved. Thus MTP has two forms of epochs—the first is the macro-epoch, which identifies the time-share partitions and how long each should run, and the micro-epoch, which is the time of each time-share. MTP is an intriguing concept but can take very long periods of time not only to adapt to changes in program behavior due to the necessarily long nature of the macro-epoch, but will be difficult to scale. Since all threads "take turns" at having generous cache allocations, the more hardware threads there are the longer each thread has to wait before getting its turn. The tension between having long enough micro-epochs and the resultant O(N) increase in wait time before obtaining the generous cache allocations makes this an unlikely solution for large scale machines.

Srikantaiah, et al. present Adaptive Set Pinning [54], a mechanism to avoid misses that result from contention between hardware threads sharing a cache. Rather than focusing on space in general, they focus on addresses. The crux of their approach is to identify "hot blocks," blocks from a thread which are frequently accessed and the cause of the displacement of blocks belonging to other threads. To do this, they introduce set pinning, a way to pin a cache set to a particular hardware thread such that no references from other threads may displace anything from that set. Instead, references to pinned sets belonging to other threads are placed into a Processor Owned Private (POP) caches, which are basically small, associative caches operating under LRU replacement. In essence, these POP caches will capture the hot blocks of their associated threads, and since the sets of the main cache are all pinned to a certain thread, thrashing between threads is reduced to zero. The key to the performance of this scheme is judicious assignment of sets to threads, which Srikantaiah et al. do with saturating counters for each set roughly approximating hit/miss ratios of the pinned and unpinned threads. This mechanism does avoid the epoch-based approach of partitioning, while taking a fuzzier approach to partitioning by avoiding precise allocation prescriptions. However, this part-private, part-shared scheme necessitates a significant overhaul to current cache designs, while limiting cache usage flexibility. Not only do designers have to decide *a priori* the size of each private cache, but power-saving schemes that turn off cores when not in use would lose the ability to utilize the cache space in the POPs belonging to the powered down threads.

Jaleel et al. proposes a mechanism called Thread Aware Dynamic Insertion Policy (TADIP) for managing shared caches [33]. It is an extension of Qureshi and Patt's Dynamic Insertion Policy (DIP) [47]. Fundamentally, DIP is a simple mechanism for voting between the LRU replacement policy (which inserts new blocks into the Most Recently Used, or MRU, position), and a modified policy called BIP (Bimodal Insertion Policy) which inserts new blocks into the LRU position with high probability. The key observation in DIP is that a few sampled sets (empirically set at 32) dedicated to different policies can approximate the performance of that policy over the entire cache. Leveraging the knowledge that cache usage for a stream of accesses can be throttled by adopting LRU insertion, first used to deprioritize prefetching accesses [39], DIP chooses between normal operation and performing LRU insertion to improve cache performance in single-threaded platforms where the cache is not quite large enough to handle the footprint of the running application. TADIP is a natural extension of DIP for CMP platforms, where every hardware thread is assigned a pair of sampled sets (32 sets for each policy) to duel. TADIP samples the global miss rates of the cache between the two groups of pinned sets, which vary only the insertion policy for one thread. TADIP then selects the policy for that thread that yields a lower global miss rate, which that thread follows upon accesses to remaining sets. TADIP is the most scalable, feasible, and high-performing scheme for shared cache performance optimization in the literature.

Kron, Brooks, and Loh also extend Qureshi's DIP in a scheme they call Double-DIP [37]. The key observation for Double-DIP is that if a set is accessed by different threads at different rates, the more frequently accessing thread will very quickly push out the blocks of the lower frequency thread by virtue of constantly promoting its own blocks to the MRU position of the set. To mitigate this problem, a dueling mechanism is added to the original DIP to select between a standard MRU promotion policy, where a block moves to the MRU position every time it is accessed, or a less aggressive promotion policy, where a is chosen to be promoted 1, 2, 4, or n steps towards MRU (where n is the associativity of the cache). This scheme avoids any requirement of knowing which accesses are from which threads, and uses only local information to lead to better performance; however it is unclear how this scheme would be implemented in an actual cache, which generally uses pseudo-LRU and is not literally a spectrum from LRU to MRU. Additionally, varied levels of promotion are not a trivial mechanism to implement in practice.

# 2.3 Quality of Service

Another aspect of shared caches is the idea of quality of service (QoS), most commonly used in the networking domain, where it is a mature concept. Cisco Systems defines network QoS in their *Internetworking Technology Handbook* [13] as:

Quality of Service (QoS) refers to the capability of a network to provide better service to selected network traffic....The primary goal of QoS is provide priority....Also important is making sure that providing priority for one or more flows does not make other flows fail.

Essentially, networks are shared by numerous flows of network traffic, and QoS considerations guide the allocation of network resource among these flows. With the advent of virtualization in computing, where multiple distinct systems can each run multiple distinct programs on a single platform, there is an increased likelihood of non-cooperative processes running simultaneously on a CMP. In many commercial virtualization situations, some applications may be more important than others, and even in client environments, background processes may be less important than foreground processes. Thus, QoS is an emerging need in computing platforms as well.

As such, there have been a number of studies [31, 32, 23, 22] about the need for the ability to provide differentiated quality of service to different virtual machines and present architectural frameworks to do so.

Iver [31] describes the need for a priority-based resource allocation framework by illustrating the strong impacts threads could have on one another when sharing a platform.

Iyer, et al. [32] describe a comprehensive platform which enables a software layer to dictate several forms of QoS, as well as a taxonomy for describing them. *Re*source Usage Metrics (RUM) track the exact usages of each sharer on a resource, and employ the modified LRU replacement algorithm as listed in Table 2.1 and described in Section 2.2.1. A thread's RUM allowance could be dictated by the user, or be dictated by an algorithm trying to achieve QoS goals. Iyer's framework also describes resource performance metrics (RPM), which measure the performances of individual sharers and does local search optimization of the cache partition in order to satisfy the requirements set by the software layer. Finally, Iyer describes overall performance metrics (OPM), which allow for high priority threads to obtain more and more resources until the platform performance degrades to a certain level. While there is value in the taxonomy provided, the framework also has the same issues as optimal partitioning proposals involving epoch length, scalability of convergence, and enforcement/measurement overhead.

Rafique, *et al.* [50] propose an interface to allow for the setting of usage quotas for the cache via operating system and a hardware enforcement layer which is thread-aware. Essentially, it is a framework to enforce RUM with a thread-aware replacement policy, with a software interface to allow for software dictated allocations from arbitrary policies at the OS-level. Nesbit, *et al.* [45] have similar cache allocation enforcement within their framework of providing systemic QoS in a virtualized environment. Both rely on exact cache usage knowledge for enforcement.

Guo, *et al.* [23] proposes a detailed policy framework in which a CMP is able to assess its own ability for providing certain guarantees of performance for a given job,

and accept or reject the job based on this assessment. However, this work operates at a level different than this thesis. Even so, this work does presume cache allocation enforcement on the basis that each block is tagged with an owner bitfield.

In many ways, the QoS problem space as addressed by the above proposals faces the same obstacles as the shared cache optimization space; QoS just enforces allocations for a different end goal than for performance optimization. But underlying mechanisms for one can be used for another; likewise difficulties in implementation for one are shared by the other. Namely, the tracking of exact cache usage requires thread-IDs per block, and enforcement of exact allocations in the form of modified LRU are a burden in realistic hardware design.

As far as I know, all cache QoS frameworks in the literature require exact usage tracking of the cache in order to enforce exact allocations prescribed by some higher level policy, and is thus fundamentally limited by the need to attribute every cache block to an owner.

In this thesis, I make the case for not guaranteeing absolute levels of resources in for cache QoS because of the difficulties just listed. After all, even Cisco describes three different types of QoS levels: guaranteed service, differentiated service, and best effort service [13], where guaranteed service is an absolute reservation of resources, differentiated service provides preferential treatment to higher priority flows without absolute guarantees, and best effort makes no distinction between flows. Their *Internetworking Technology Handbook* also states, "Fundamentally, QoS enables you to provide better service to certain flows. This is done by either raising the priority of a flow or limiting the priority of another flow." The emphasis is not upon guaranteed allocation of resources. This thesis contends that the computing community should take a cue from the networking domain and focus on differentiated QoS rather than guaranteed QoS because not only is there a clear, established domain where customers accept such a model of service, but it is much simpler for platforms to be designed to provide differentiation than exact resource guarantees.

## 2.4 Other Related Work

#### 2.4.1 Operating systems involvement in cache management

Some studies move upward in the stack and utilize the operating system for managing the sharing of shared caches. Fedorova and Seltzer investigate using the OS scheduler to ensure that contentious processes are not run simultaneously [20], while Rafique, Lim, and Thottethodi present a mechanism for providing architectural support for OS-driven cache management to enforce partitions [50] (while not presenting a policy for generating partitions).

#### 2.4.2 Latency optimizations for distributed caches

In distributed shared caches, the last level cache is distributed in that it is not a monolithic structure and is banked, but is shared in that any thread can have blocks in any bank. Accesses to a bank that is closer to a processor is lower-latency than accesses to a faraway bank, thus the aim for these studies is to make sure needed blocks are as close to their requesting processors as possible.

Beckmann, Marty, and Wood use dynamic monitoring techniques to assess the needs of running applications to decide whether to replicate data across banks [5]. The scheme, called Adaptive Selective Replication, determines the expected tradeoff between lower latencies and smaller effective cache size and makes its decision.

Other studies parameterize the level of private and shared use of each distributed bank [16, 66], adapting at run-time to maximize performance.

Cooperative Caching, presented by Chang and Sohi [11], uses private caching as its baseline but appends cooperative techniques to achieve the benefits of a shared cache. Cooperative techniques include the spilling of data from an overtaxed private cache to an underutilized one, rather than evicting it from the chip entirely.

Qureshi takes this lateral spilling to another level with set dueling, the concept behind DIP, TADIP, and Double-DIP. In this scheme, a private cache is pegged either as a spiller (*i.e.*, belonging to a thread with a large cache footprint), or a receiver (*i.e.*, having capacity to spare for spiller cache victims), such that a cache cannot be both [49].

# 2.5 Conclusion

It is clear that while shared cache management is not a new area of study, there is opportunity for a scheme that scales, is feasible, provides good performance, and meets the emerging need for QoS in shared computing platforms. This thesis seeks to address this opportunity by first assessing the problem of metrics. In order to craft a good solution, a reasonable metric for measuring the quality of solution must be defined; in the area of shared caches there are a number of metrics to choose from.

The next chapter assesses this metric space in a rigorous manner, setting the stage for measurement for the remainder of this dissertation.

# CHAPTER 3

# Shared Cache Metrics

To begin studying the best approach to managing shared caches in a CMP context, the question is immediately raised as to what the *optimal* policy might be. Naturally, the answer to this question hinges on the objective for which we optimize. What is more important, maximal overall system performance, or fairness across threads? Given one of these goals, what specific metric do we seek to maximize or equalize? While the notion of performance in single-threaded uniprocessors is straightforward, multithreaded systems are amenable to multiple definitions, including instruction processing rates and miss rates, both raw (absolute) and weighted—and among weighted metrics, multiple weighting factors may be selected.

Thus, in a dissertation about shared cache management, I begin with a study about the impact of varying definitions of "optimal performance" on the partitioning of a shared cache among multiple threads. Specifically, I seek to answer the following questions:

- 1. To what extent does the definition of "optimal" impact the resulting partitions and performance?

- 2. In targeting one definition of "optimal", how well does the system fare with regard to other reasonable definitions? In particular, how do policies targeting

overall performance rate in terms of fairness, and how do policies targeting fairness rate in terms of overall performance?

3. If optimality is defined based on metrics that are not readily available online, are there online measurable metrics that correlate well that could be used to drive an online policy?

Borrowing loosely from economics terminology, I define four high-level policies for cache allocation. A "Communist" approach seeks to maximize fairness, ensuring that each thread bears an equal portion of the cache sharing penalty, or alternatively derives an equal benefit from the presence of the cache. The goal of a "Utilitarian" policy is to maximize the total benefit for the aggregate group - e.g., by maximizing total throughput – without regard to individual thread performance. A "Utopian" policy attempts to balance throughput and fairness. Finally, a "Capitalist" cache policy is an unregulated free-for-all—the most common policy in use today.

Intuitively, either a Communist or Utilitarian policy seems preferable to a Capitalist policy, as these seek to maximize some desirable property, while the Capitalist policy makes no effort toward any form of "goodness". The Utopian policy seems even more preferable—as a balance of fairness and throughput it seems ideal. Studies have suggested the use of harmonic mean for effecting a balance between overall performance and fairness [41, 12], and this study evaluates harmonic mean as a way of implementing a Utopian policy.

In addition to the question of which policy to use, there is the issue of which metric to apply on these policies. Miss rate is a common metric for cache performance, but miss rate is not always proportional to perceived performance. Memory bandwidth is a scarce commodity in CMPs, so it may be appropriate for a Utilitarian policy to minimize total bandwidth. Throughput is often the bottom line, but raw IPC is not a very useful metric, since different threads have different levels of ILP (Instruction Level Parallelism, discussed in Chapter 1). Weighted IPCs [53] are attractive and have been used in past studies, but raise the question of what weighting factor should be used.

Overall, I identify four distinct aspects of a cache partitioning policy: *performance* targets, evaluation metrics, policies, and policy metrics.

- A *performance target* is the end goal. A performance target may be for all threads to have the same miss rate, or that all threads should have the same IPC relative to some baseline configuration. The performance targets examined are: minimizing total memory bandwidth, maximizing weighted IPC with respect to various baselines, equalizing weighted IPC with respect to various baselines, and maximizing harmonic mean of weighted IPC with respect to various baselines.

- The *evaluation metric* is the metric used to express the performance target and to evaluate the extent to which the target is achieved. For example, if the target is to maximize total weighted IPC, then the evaluation metric is weighted IPC.

- A *policy* is the aspect of the cache implementation which makes allocation decisions. One well-known policy is LRU replacement, intended to achieve low miss rates in the general case. This study compares LRU, the general default policy, to policies that perform allocation based on metric values measured from application behavior. To keep the focus on fundamental behavior rather than specific implementations, these policies are modeling using static optimal partitioning based on offline analysis.

- A *policy metric* is a metric used to drive an allocation policy (the offline optimal policies in our case). Ideally, the policy metric and evaluation metric would be identical. However, the desired evaluation metric may not be measurable online, and thus may not be useful in driving policy decisions. Practical implementations may be forced to use policy metrics that are online observable metrics that merely correlate with the evaluation metric.

The primary contribution of this chapter is to provide a rigorous analysis of the objective function space in shared cache design along numerous axes. This study concludes that the optimal partition for a shared cache can vary greatly as different but reasonable definitions of optimality are applied. Additionally, none of these definitions of optimality encompass every positive attribute for shared cache performance; no metric is a functional superset of the rest. As a result, this investigation concludes that it is folly to pursue optimality along a particular metric in shared cache design. This conclusion further shows that marginal cost analysis in shared caches, which persistently pursue an optimal partition along some metric, is not the ideal approach for shared cache management. A better approach is to pursue a broadly applicable policy which provides good performance in the general case and prevents poor performance as measured under any reasonable metric. Experiments in this chapter show that LRU, the policy *de rigeur*, is insufficient for this purpose.

This study also makes the distinction between the pursuit of optimality along a metric, *i.e.*, using a metric as an objective function; and the use of a metric to measure performance. Results show that harmonic mean-based metrics do provide somewhat Utopian properties by not diverging very excessively from optimal fairness or throughput; in other words Utopian metrics are generally preferable to *measure* performance results, if not as an objective function.

## 3.1 Methodology

#### 3.1.1 Performance Target Selection

A performance target is some function of the overall cache allocation which we seek to minimize or maximize by adjusting the allocation. The notation  $(p_1, p_2, p_3, ..., p_N)$ is used to denote the set of cache allocations for an N-thread workload, such that  $p_i$ is the cache allocation for thread i and  $\sum_{i=1}^{N} p_i = C$ , where C is the total cache space

|    | Target Name   | Description                                                    |

|----|---------------|----------------------------------------------------------------|

| 1  | MPC-None-Util | Minimizing Overall Bandwidth                                   |

| 2  | IPC-128-Util  | Maximizing IPC weighted wrt 128KB performance                  |

| 3  | IPC-256-Util  | Maximizing IPC weighted wrt 256KB performance                  |

| 4  | IPC-512-Util  | Maximizing IPC weighted wrt 512KB performance                  |

| 5  | IPC-1024-Util | Maximizing IPC weighted wrt 1MB performance                    |

| 6  | IPC-128-Comm  | Equalizing IPC weighted wrt 128KB performance                  |

| 7  | IPC-256-Comm  | Equalizing IPC weighted wrt 256KB performance                  |

| 8  | IPC-512-Comm  | Equalizing IPC weighted wrt 512KB performance                  |

| 9  | IPC-1024-Comm | Equalizing IPC weighted wrt 1MB performance                    |

| 10 | IPC-128-Utop  | Maximizing Harmonic Mean of IPC weighted wrt 128KB performance |

| 11 | IPC-256-Utop  | Maximizing Harmonic Mean of IPC weighted wrt 256KB performance |

| 12 | IPC-512-Utop  | Maximizing Harmonic Mean of IPC weighted wrt 512KB performance |

| 13 | IPC-1024-Utop | Maximizing Harmonic Mean of IPC weighted wrt 1MB performance   |

Table 3.1: Performance Targets - Performance targets used in this study.

available.

As discussed previously, targets can be either Communist, Utilitarian, or Utopian in nature, emphasizing either fairness, overall performance, or a balance of the two. Each of these high-level targets can be applied to a variety of metrics.

A metric has two components: a "base" metric and an (optional) weighting factor. Included in this study are three base metrics:

- *Misses per access (MPA), i.e.*, miss rate. This is a fundamental cache performance metric that is easy to measure online.

- *Misses per cycle (MPC)* measures bandwidth usage. We include this metric because off-chip bandwidth may be a precious resource in future servers.

- Instructions per cycle (IPC) is instruction rate. For a fixed program path length, e.g., no spin-wait loops, IPC directly corresponds to throughput, and is thus a direct measure of observed performance.

A meaningful performance target should reflect some tangibly useful goal. Because IPC directly indicates performance, this study focuses primarily on IPC-based targets. Since MPC may prove useful as a target for severely bandwidth-constrained systems, MPC-based targets are also included. MPA-based performance targets are not considered, since low miss rates do not directly translate into measurable improvement on the system level. Nevertheless, MPA is attractive because of its ease of online measurement; MPA will be revisited in Section 3.2.4 to consider whether it is useful as a policy metric, *i.e.*, a measurable proxy for other more significant metrics.

The other component, the weighting factor, was born out of SMT processor performance studies [53]. Any of the metrics defined above can be weighted, i.e.:

$$Metric_{weighted}(p_i) = \frac{Metric(p_i)}{Metric(baseline)}$$

(3.1)