# Pseudo-Vector Machine For Embedded Applications

by

Lea Hwang Lee

A dissertation submitted in partial fulfillment of the requirements for the degree of

**Doctor of Philosophy** (Computer Science and Engineering)

> at the The University of Michigan 2000

**Doctoral Committee:**

Prof. Trevor Mudge, Chairperson Prof. Richard Brown Prof. Ed Davidson Prof. Marios Papaefthymiou Prof. Karem Sakallah

"We are moving into a third stage of computing. In the first, the mainframe world, there was one computer for many people. In the second, the PC world, there was a computer for each person. In the next stage there will be many computing devices for each person..."

Roy Want, Palo Alto Research Center, Xerox Corp., Palo Alto, CA. Source: PC Week Online, January 3, 2000 © Lea Hwang Lee All Rights Reserved

- 2000

To My Mother, Chern, Der-Shin, And My Sister, Lee, Deek Ann,

For their unfailing care and support.

#### ACKNOWLEDGEMENTS

I joint the M-CORE<sup>TM</sup> Technology Center (MTC), Motorola Incorp., Austin, Texas, as a summer intern in 1994. At that time, the group (under a different name) had just embarked on developing a new ISA for targeting mid-to-low end embedded markets. I spent the next two years (1995 and 1996) working and traveling between Austin, Texas and Ann Arbor, Michigan. I became a full-time employee towards the end of 1996.

This dissertation work is not formally nor directly funded by any organization. However, I did receive a lot of assistance from the MTC. In particular, they had given me access to various software tools and benchmark programs. For a brief period of time, they had also kept me on the payroll while I was working full-time on my dissertation - what a perfect way to fund a research project.

I am deeply indebted to my manager, John Arends, for all the constant guidance he had provided to me. From day one, he has always been there to renter his help, technically or otherwise.

I am very grateful to my co-worker and my best friend, Jeff Scott. He is one of the most talented, energetic, motivated and creative engineer I have ever met. I am also very grateful to Bill Moyer for all his technical assistance and insightful advises. His insights has always made my "research life" much more interesting and challenging.

I am also deeply indebted to Prof. Trevor Mudge for all his technical assistance and advises, without which, this dissertation work would be impossible.

Lastly, but not the least, I would like to thank the entire MTC team, for all their support they have given to me. I feel honored, to have such a great opportunity to work with this talented and motivated group of people.

#### PREFACE

The focus of this dissertation is on designing low-cost, low-power and high performance processors for mid-to-low end mobile embedded applications. In particular, the main goal of this work is to *explore ways to add a minimum amount of hardware to a single issued machine to improve its performance on critical loop executions* - since many of these applications spend a significant amount of their execution time on a handful of critical loops. Improve the performance on these loops provides the biggest bang for the buck.

This dissertation borrows many existing architectural ideas from vector processors and DSP processors, and combines them into a single execution model.

Vector processing paradigm is well known for its excellent cost/performance trade-off. The processing paradigm proposed in this dissertation, called the *pseudo-vector machine*, exploits, as much as possible, the low-cost, low-power and high performance aspects of vector processing paradigm.

As we will see later in this dissertation, the characteristics of the critical loops found in our benchmarks vary greatly, from *highly vectorizable*, to *difficult* (and *costly*) *to vectorize*, to *impossible to vectorize*.

For example, a loop that performs a vector operation described by C[i] = A[i] \* B[i], for i=0,...,n-1, for some vectors A, B and C of length n, is a highly vectorizable loop. A loop that performs a vector operation described by  $C[i] = (A[i]>B[i])? A[i]^2 : A[i]+B[i]$ , for i=0,...,n-1, is more difficult (or costlier ) to vectorize.

The vector arithmetic represented by some hard-to-vectorize loops, in this work, is called *pseudo-vector arithmetic* (PVA). For this type of loops, the DSP's style of processing, which focuses on optimizing the program loop executions, is more suitable. These optimization techniques include: (i) using the "while" or "repeat" instructions to remove loop control overheads; (ii) using data streaming buffers to remove overhead associated with constant-stride

memory operations.

The pseudo-vector machine proposed in this dissertation can execute two types of vector arithmetic: a "true" vector arithmetic and a "pseudo" vector arithmetic, as described in the preceding paragraph. Depending on the type of loops, the machine sometime behaves like a vector processor; it sometime behaves like a DSP processor. The compilers, for this machine, decide which execution modes to use for each critical loop.

In addition, this machine uses a single datapath to execute all the vector arithmetic as well as the scalar portion (the non-loop portion) of the program code - an efficient reuse of the hardware resources.

# TABLE OF CONTENTS

| DEDICATION                          | ii    |

|-------------------------------------|-------|

| ACKNOWLEDGEMENTS                    | iii   |

| PREFACE                             | iv    |

| TABLE OF CONTENTS                   | vi    |

| LIST OF FIGURES                     | XV    |

| LIST OF TABLES                      | xviii |

| FREQUENTLY USED M-CORE INSTRUCTIONS | xiv   |

# **CHAPTER I**

| INTRODUCTION: LOW-COST, LOW-POWER DESIGNS FOR EMBED-   |  |  |

|--------------------------------------------------------|--|--|

| DED APPLICATIONS                                       |  |  |

| 1.1 The World Of Mobile Computing1                     |  |  |

| 1.2.1 Alternate Operating Modes                        |  |  |

| 1.2.2 Performance vs. Instantaneous Power              |  |  |

| 1.2 Important Characteristics Of Mobile Systems        |  |  |

| 1.3 Execution Modes For Mobile Systems                 |  |  |

| 1.4 Pseudo-Vector Machine - An Architectural Overview  |  |  |

| 1.5 The Strength of Vector Processing                  |  |  |

| 1.6 Vector Processing vs. Pseudo-Vector Processing     |  |  |

| 1.7 The Basic Framework For This Dissertation          |  |  |

| 1.8 Profile-Based Performance Evaluations - An Example |  |  |

| 1.9 Contributions Of This Dissertation                 |  |  |

| 1.10 A Note On Vector Processing Paradigm              |  |  |

# **CHAPTER II**

| <b>RELATED WORK</b>                                               |

|-------------------------------------------------------------------|

| 2.1 Software Loop Unrolling                                       |

| 2.2 Software Pipelining and Register Rotation                     |

| 2.3 Stream Data Buffers In WM and SMC Architectures               |

| 2.4 Data Address Generators                                       |

| 2.5 Compute And Memory Move Instructions                          |

| 2.6 Special Loop Instructions For Removing Loop Control Overheads |

| 2.6.1 The TriCoreTM ISA                                           |

| 2.6.2 The SHARC ADSP ISA                                          |

| 2.7 Vector Processing                                             |

| 2.7.1 Cray-1 Vector Machine - A SISD Vector Machine               |

| 2.7.2 PowerPC AltiVec - A SIMD Vector Processor                   |

| 2.9 Decoupled Access/Execute Machine - Astronautics ZS-1          |

| 2.10 The Transmeta's CrusoeTM Processors                          |

| 2.11 Pseudo-Vector Machine - Comparisons With Related Work        |

| 2.12 General Comparisons With Related Work                        |

# **CHAPTER III**

| VECTOR   | R ARITHMETIC                            | 3 |

|----------|-----------------------------------------|---|

| 3.1 Cano | onical Vector Arithmetic                | 3 |

| 3.1.     | .1 Compound CVA                         | ) |

| 3.1.     | .2 Reduction CVA                        | l |

| 3.1.     | .3 Hybrid CVA                           | 2 |

| 3.1.     | .4 Some Examples Of CVA                 | 2 |

| 3.2 Pseu | do-Vector Arithmetic                    | ł |

| 3.3 Vect | tor Arithmetic with Early Termination46 | 5 |

# **CHAPTER IV**

| PRO | OGRAN   | IMING MODELS                                             | 50 |

|-----|---------|----------------------------------------------------------|----|

| 4.1 | Execut  | ion Modes                                                | 50 |

| 4.2 | Consta  | nt-Stride Load/Store Operations                          | 50 |

|     | 4.2.1   | cs-load And cs-store For CVA Executions                  |    |

|     | 4.2.2   | cs-load And cs-store For PVA Executions                  | 55 |

| 4.3 | Special | l Registers For Vector Executions                        | 57 |

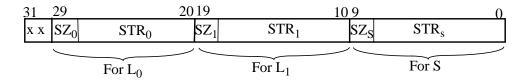

|     | 4.3.1   | Stride and Size Register                                 |    |

|     | 4.3.2   | Count Index Register (CIR)                               |    |

|     | 4.3.3   | Register For Storing Constant-Stride Load Addresses      |    |

|     | 4.3.4   | Register For Storing Constant-Stride Store Addresses     | 59 |

|     | 4.3.5   | Scalar Results For Reduction And Hybrid CVA              | 59 |

|     | 4.3.6   | Scalar Source Operands For CVA Executions                |    |

| 4.4 | Vector  | Instructions                                             | 60 |

| 4.5 | Termin  | nating Conditions                                        | 62 |

|     | 4.5.1   | Early Termination for CVA Executions                     | 62 |

|     | 4.5.2   | Early Termination for PVA Executions                     | 63 |

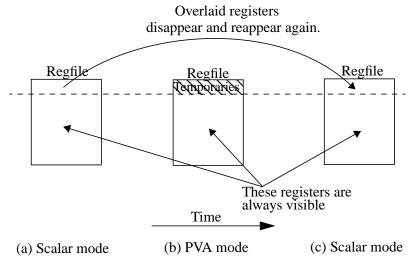

| 4.6 | Registe | er Overlay                                               | 63 |

| 4.7 | Machir  | ne States Maintenance For Vector Executions              | 65 |

|     | 4.7.1   | Saving The Execution Modes                               | 65 |

|     | 4.7.2   | Saving The Minimum Vector Contexts                       | 66 |

|     | 4.7.3   | Updates of Temporary and Overlaid Instances of R0 and R1 | 67 |

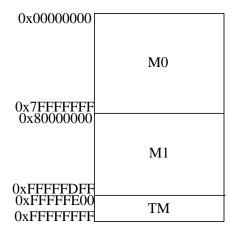

| 4.8 | Memor   | ry Organization                                          | 67 |

|     | 4.8.1   | Memory Bandwidth Requirements For Vector Executions      | 68 |

|     | 4.8.2   | Memory Map For M0, M1, TM                                | 68 |

| 4.8.3 | Temporary Memory    | 69 |

|-------|---------------------|----|

| 4.8.4 | Strip Mining For TM | 70 |

# CHAPTER V

| PSE | CUDO-VECTOR MACHINE IMPLEMENTATIONS              |

|-----|--------------------------------------------------|

| 5.1 | Datapath Implementations                         |

| 5.2 | Scalar Executions                                |

| 5.3 | CVA Executions                                   |

| 5.4 | PVA Executions                                   |

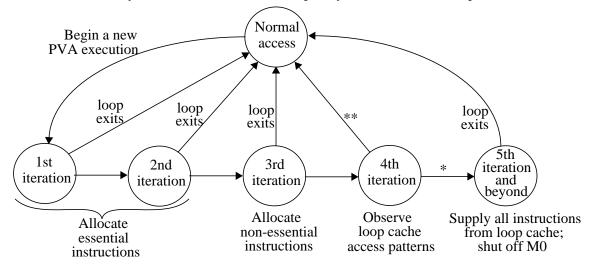

| 5.5 | Managing The PVA Loop Executions                 |

| 5.6 | Implementing The Temporary Registers             |

| 4.7 | Machine States Maintenance For Vector Executions |

| 5.7 | Implementing The Memory System    83             |

| 5.8 | Loop Cache For Storing PVA Program Loops         |

# **CHAPTER VI**

| BENCHMARKS CHARACTERISTIC AND PERFORMANCE EVALUATIONS               |

|---------------------------------------------------------------------|

| 6.1 Metrics For Performance Evaluations                             |

| 6.2 Benchmark Programs And Their Characteristics                    |

| 6.3 Performance Evaluation Methodologies - Overview                 |

| 6.4 Vector Setup and Exit Costs                                     |

| 6.4.1 Special Registers Initialization Costs                        |

| 6.4.2 Vector Instruction Decode Costs                               |

| 6.4.3 Additional Pipeline Warm-Up Costs                             |

| 6.4.4 Vector Mode Exit Costs                                        |

| 6.4.5 Initial Access Conflicts At M0                                |

| 6.5 PVA-Only Executions - Three Types Of Loop Execution Overheads   |

| 6.6 Cycle Saving Calculations for Vectorizing a Typical Scalar Loop |

| 6.6.1 Saving Calculations For Typical PVA Executions                |

| 6.6.2 Saving Calculations For Typical CVA Executions                |

| 6.7 CVA-Only vs. PVA-Only vs. CVA/PVA Executions                    |

| 6.8 TM Strip-Mining Costs 104                                       |

| 6.9 Throughput Rates For CVA Executions With Memory Conflicts       |

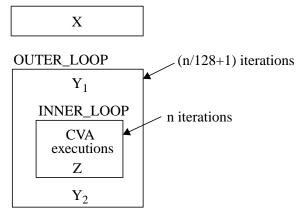

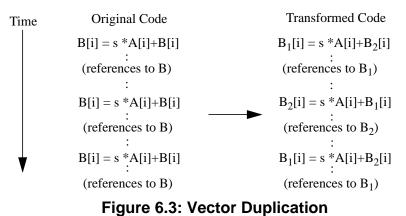

| 6.10 Maximizing The Use Of TM via Vector Duplication                |

| 6.10.1 Software Implementation of Vector Duplication                |

| 6.10.2 Execution Overheads of Vector Duplication                    |

| 6.11 Instruction Fetch Bandwidth                                    |

# **CHAPTER VII**

| EXI | PERIM   | ENTAL RESULTS113                                   |

|-----|---------|----------------------------------------------------|

| 7.1 | Overal  | Speedups                                           |

|     | 7.1.1   | CVA-Only vs. PVA-Only Executions                   |

|     | 7.1.2   | Allowing CVA-Only Executions To Terminate Early115 |

| 7.2 | Speedu  | ps During Program Loop Executions116               |

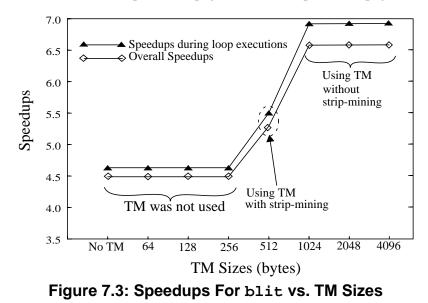

| 7.3 | Perform | nance Impact By Varying The Sizes Of TM117         |

|     | 7.3.1   | TM Strip-Mining Costs vs. TM Sizes                 |

|     | 7.3.2   | Average Speedups vs. TM Sizes                      |

| 7.4 | PVA-C   | Only Executions                                    |

| 7.5 | Instruc | ction Fetch Bandwidth Reductions                   |

|     | 7.5.1   | Normalized IReq From Processor Core                |

|     | 7.5.2   | Normalized IFetch From The Memory M0125            |

| 7.6 | Summa   | ary                                                |

## **CHAPTER VIII**

| A   | rchitectural Extensions For DSP Applications   | 30 |

|-----|------------------------------------------------|----|

| 8.1 | Architectural Extensions - VLIW/Vector Machine | 30 |

| 8.2 | Implementing The IIR Filter                    | 33 |

| 8.3 | Implementing The FFT                           | 34 |

#### **CHAPTER IX**

| Summary |  |

|---------|--|

|---------|--|

# **APPENDICES A**

| CRITICAL LOOP VECTORIZATIONS AND CYCLE SAVING CALCULA- |

|--------------------------------------------------------|

| <b>TIONS</b>                                           |

|                                                        |

| <b>3LIOGRAPHY</b> 187 |

|-----------------------|

|-----------------------|

# LIST OF FIGURES

| Figure 1.1:  | Instantaneous Power Of A Mobile Computing System                          |

|--------------|---------------------------------------------------------------------------|

| Figure 1.2:  | Energy versus power consumption                                           |

| Figure 1.3:  | Various Execution Modes On The Pseudo-Vector Machine7                     |

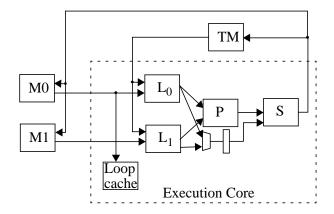

| Figure 1.4:  | The CPU Architecture for the Pseudo-Vector Machine                        |

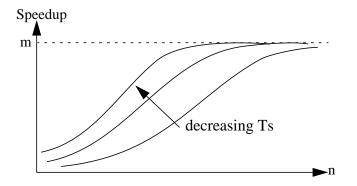

| Figure 1.5:  | Dependency Graphs for Three Types of CVA9                                 |

| Figure 1.6:  | Data dependency graph for Example 1.1 10                                  |

| Figure 1.7:  | Relationships Between Speedup and n with Tr=1 11                          |

| Figure 1.8:  | Various Processing Paradigms                                              |

| Figure 2.1:  | Software Loop Unrolling                                                   |

| Figure 2.2:  | Software Pipelining                                                       |

| Figure 2.3:  | Software Pipelining With Register Rotation                                |

| Figure 2.4:  | SMC Architecture - A Dynamic Access Ordering System                       |

| Figure 2.5:  | ADSP-2106x SHARC Block Diagram                                            |

| Figure 2.6:  | Source Registers For Multifunction Computations (ALU and Multiplier) . 23 |

| Figure 2.7:  | Program loops using special loop instructions                             |

| Figure 2.8:  | Block Diagram For Cray-1 Vector Machine                                   |

| Figure 2.9:  | Block Diagram of PowerPC with AltiVec Technology                          |

| Figure 2.10: | AltiVec Vector Unit                                                       |

| Figure 2.11: | MultiTitan Floating-Point Architecture                                    |

| Figure 2.12: | FPU ALU Instruction Format                                                |

| Figure 2.13: | The Astronautics ZS-1                                                     |

| Figure 2.14: | A FORTRAN Loop and Its ZS-1 Assembly Code                                 |

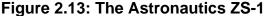

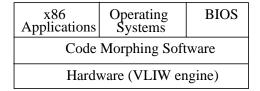

| Figure 2.15: | Applications/Code Morphing Software/Hardware Layers                       |

|              |                                                                           |

| Figure 2.16: | Comparison Between a 2-Wide VLIW Machine and a 2-Deep Vector               |

|--------------|----------------------------------------------------------------------------|

| Machine      |                                                                            |

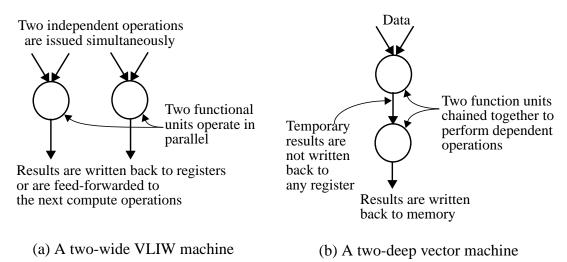

| Figure 2.17: | The General Structure of a PVA Program Loop                                |

| Figure 3.1:  | A Generic Data Dependency Graph                                            |

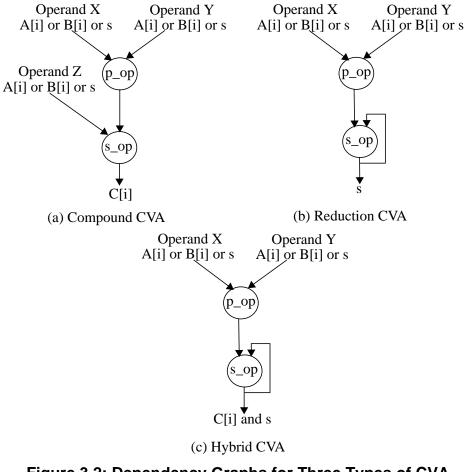

| Figure 3.2:  | Dependency Graphs for Three Types of CVA                                   |

| Figure 3.3:  | Basic Datapath Structure for Executing CVA                                 |

| Figure 3.4:  | A Program Loop with Multiple Exits                                         |

| Figure 4.1:  | Various Execution Modes On The Pseudo-Vector Machine                       |

| Figure 4.2:  | Dependency Graphs Showing the Relationships Between L0, L1 and Source      |

| Operands X,  | Y and Z                                                                    |

| Figure 4.3:  | Data Dependency Graph for Example 4.4                                      |

| Figure 4.4:  | Stride Size Register, SSR                                                  |

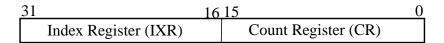

| Figure 4.5:  | Count Index Register, CIR                                                  |

| Figure 4.6:  | Format of CVA and PVA Instructions                                         |

| Figure 4.7:  | Register Overlay                                                           |

| Figure 4.8:  | A Simplistic View Of The Memory Organization                               |

| Figure 4.9:  | Memory Map For M0, M1, TM                                                  |

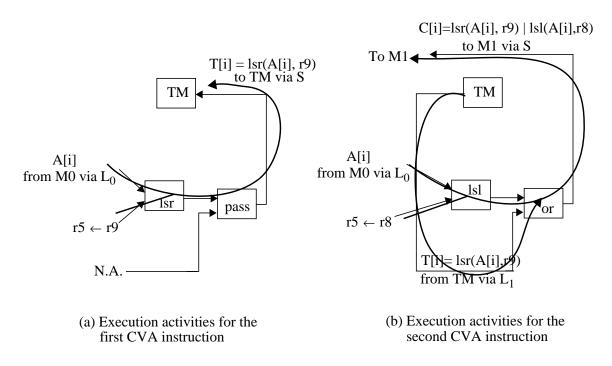

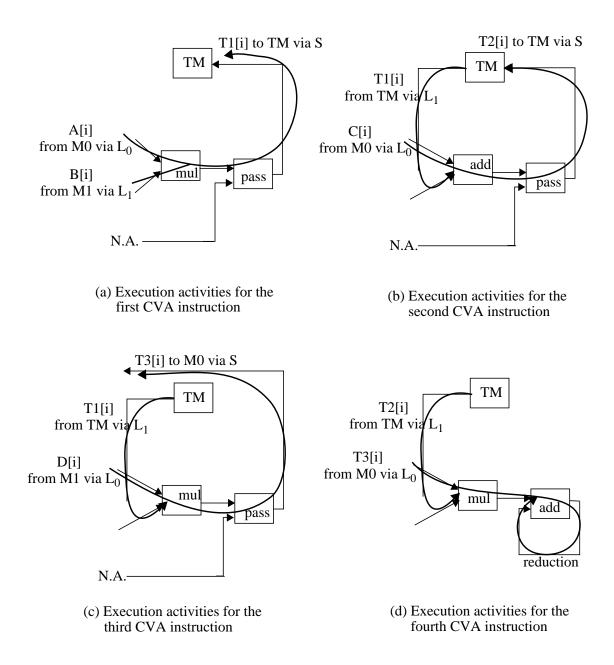

| Figure 4.10: | Execution Activities For The Two CVA Instructions                          |

| Figure 4.11: | Execution Activities For The Four CVA Instructions Using Solution (II) .73 |

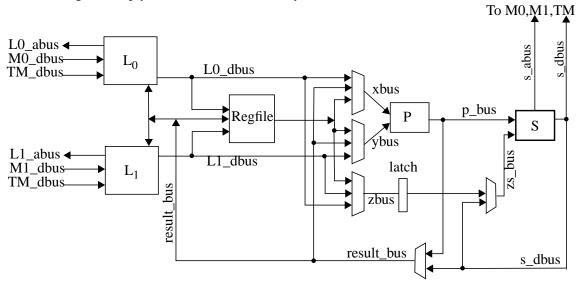

| Figure 5.1:  | The CPU Architecture for the Pseudo-Vector Machine                         |

| Figure 5.2:  | Datapath for a Single-Issued, Four-Stage Pipelined Machine                 |

| Figure 5.3:  | Datapath For The Pseudo-Vector Machine                                     |

| Figure 5.4:  | The Implementations of L0, L1 and S Units                                  |

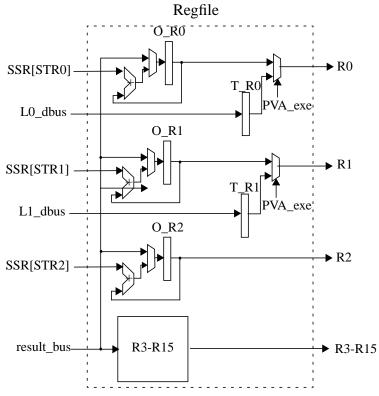

| Figure 5.5:  | Updates of Local R0 in L0 and Overlaid Instance of R0 in Regfile 80        |

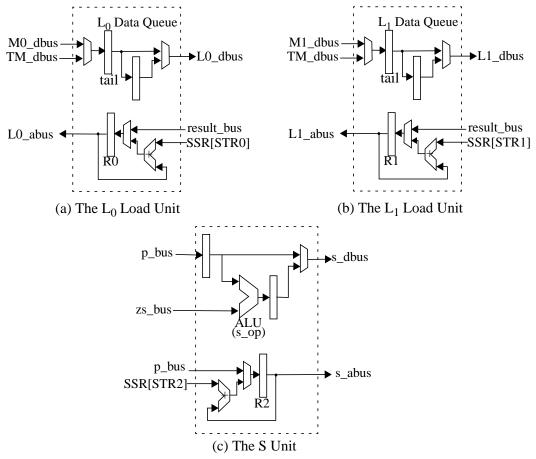

| Figure 5.6:  | The IXR Register                                                           |

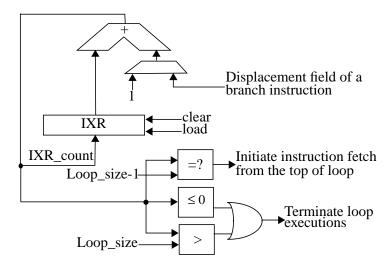

| Figure 5.7:  | Register File with Temporary and Overlaid Instances of R0 and R1 82        |

| Figure 5.8:  | Loop Cache Controller                                                      |

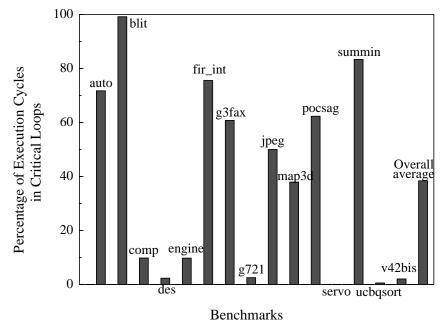

| Figure 6.1:  | Percentage of Execution Cycles Spent in Critical Loops             |

|--------------|--------------------------------------------------------------------|

| Figure 6.2:  | Execution Costs For TM Strip-Mined Code                            |

| Figure 6.3:  | Vector Duplication                                                 |

| Figure 6.4:  | Transformed Code For Vector Duplication                            |

| Figure 6.5:  | IReq from Processor Core versus IFetch from Memory M0110           |

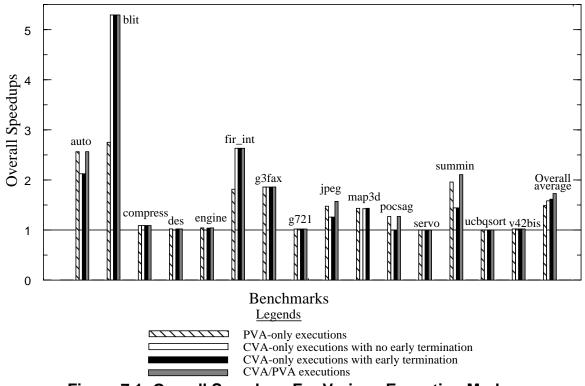

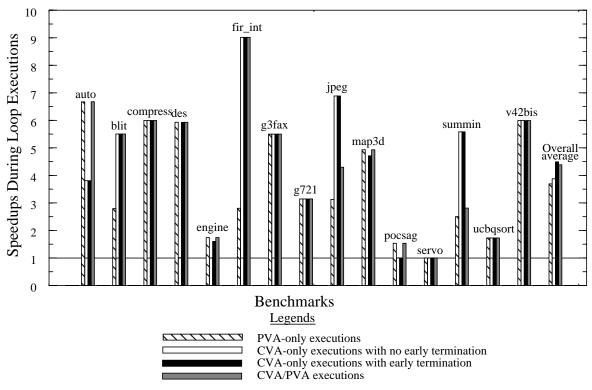

| Figure 7.1:  | Overall Speedups For Various Execution Modes                       |

| Figure 7.2:  | Speedups During Loop Executions For Various Execution Modes 117    |

| Figure 7.3:  | Speedups For blit vs. TM Sizes                                     |

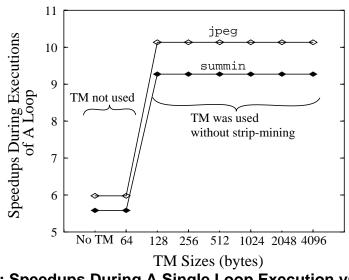

| Figure 7.4:  | Speedups During A Single Loop Execution vs. TM Sizes (For jpeg and |

| summin)      |                                                                    |

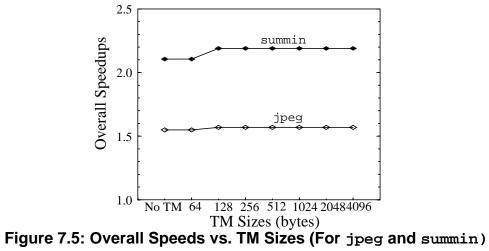

| Figure 7.5:  | Overall Speeds vs. TM Sizes (For jpeg and summin) 120              |

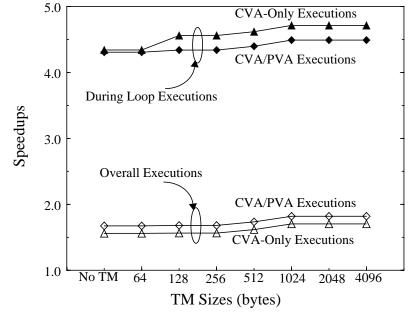

| Figure 7.6:  | Speeds vs. TM Sizes - Average of All Benchmarks                    |

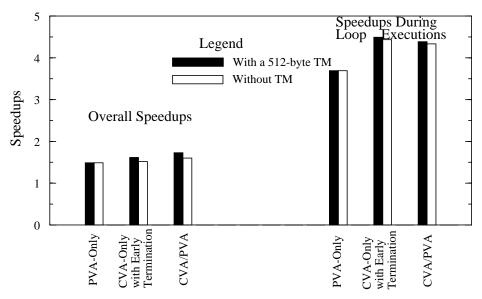

| Figure 7.7:  | Performance Benefits of Using a 512-Byte TM121                     |

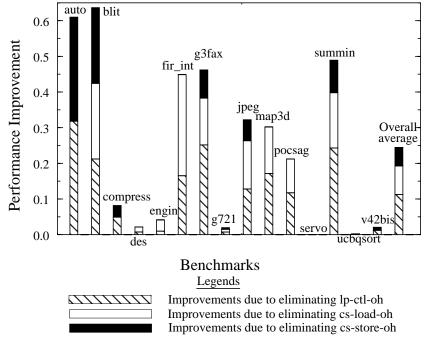

| Figure 7.8:  | Performance Improvements Using PVA-Only Executions 122             |

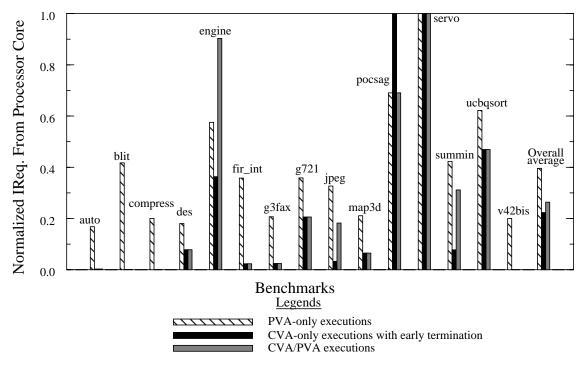

| Figure 7.9:  | Normalized IReq From Processor Core During Loop Executions 125     |

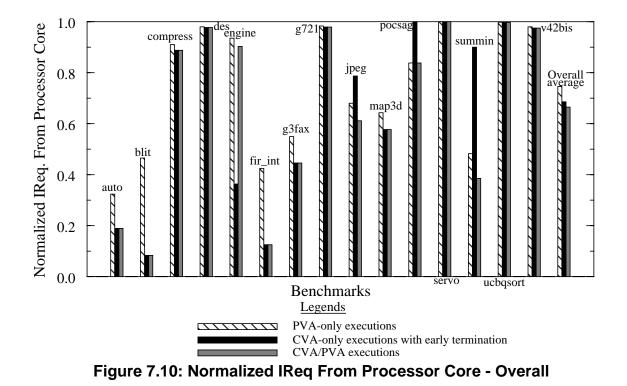

| Figure 7.10: | Normalized IReq From Processor Core - Overall                      |

| Figure 7.11: | Normalized IFetch From Memory M0127                                |

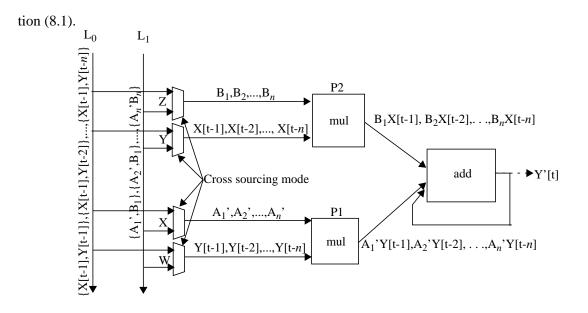

| Figure 8.1:  | Datapath for the Extended Pseudo-Vector Machine                    |

| Figure 8.2:  | Dependency Graphs For Three Types of CVA Executions                |

| Figure 8.3:  | Enhanced Datapath For Implementing IIR Filters                     |

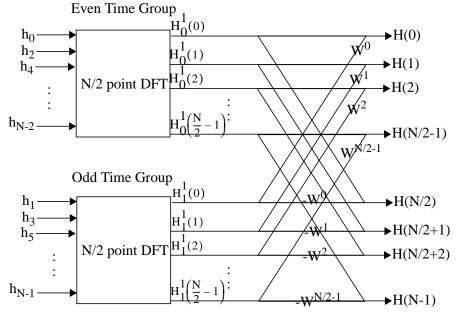

| Figure 8.4:  | DIT Decomposition of a N-point FFT                                 |

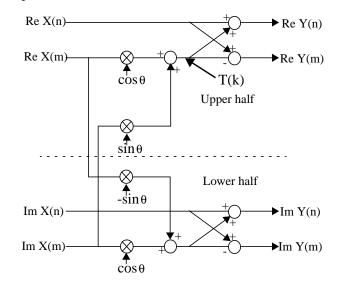

| Figure 8.5:  | Generalized Butterfly Computation Diagram                          |

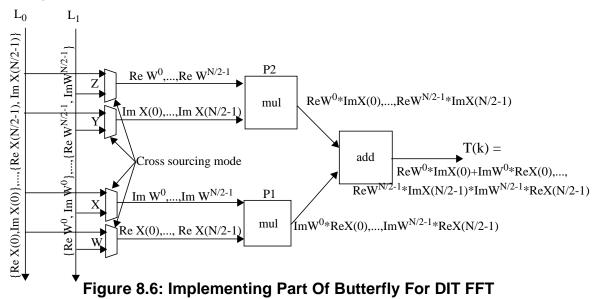

| Figure 8.6:  | Implementing Part Of Butterfly For DIT FFT                         |

# LIST OF TABLES

| Table 3.1:  | Some Examples of CVA                                                        |

|-------------|-----------------------------------------------------------------------------|

| Table 4.1:  | Special Registers For Vector Executions                                     |

| Table 4.2:  | Overlaid and Temporary Instances of R0/R1                                   |

| Table 4.3:  | Accessibilities of M0, M1 and TM                                            |

| Table 4.4:  | Two Possible Solutions For Allocating The Temporary Vectors T1, T2 and T3   |

|             |                                                                             |

| Table 6.1:  | PowerStone Benchmarks                                                       |

| Table 6.2:  | Percentage Execution Time Spent In Program Loops                            |

| Table 6.3:  | Additional Registers Initialization Costs                                   |

| Table 6.4:  | Performance Improvements Due to Eliminating Various Types of Loop           |

| Execution   | Overheads                                                                   |

| Table 6.5:  | Performance Improvements Due to Eliminating Various Types of Loop           |

| Execution   | Overheads                                                                   |

| Table 6.6:  | "auto" Critical Loop 1                                                      |

| Table 6.7:  | Profile For Critical Loop 1                                                 |

| Table 6.8:  | Vectorizing A Loop For Performing C[i] = A[i] * B[i] 101                    |

| Table 6.9:  | A Critical Loop From "jpeg"                                                 |

| Table 6.10: | Vertorizing Critical Loop 1 From Benchmark "blit"                           |

| Table 6.11: | Profile For Critical Loop 1 From Benchmark "blit"                           |

| Table 6.12: | Vectorizing The Loop Shown in Example 1.1                                   |

| Table 6.13: | Normalized IReq For PVA and CVA Executions                                  |

| Table 7.1:  | Overall Speedups For Various Combinations of Execution Modes 114            |

| Table 7.2:  | Speedups During Loop Executions For Various Combinations of Execution xviii |

| Modes      | 1                                                | 16 |

|------------|--------------------------------------------------|----|

| Table 7.3: | Speedups For CVA/PVA Executions vs. TM Sizes     | 20 |

| Table 7.4: | Speedups For CVA-Only Executions vs. TM Sizes    | 20 |

| Table 7.5: | Performance Improvements For PVA-Only Executions | 22 |

| Table 7.6: | Normalized IReq From The Processor Core          | 24 |

| Table 7.7: | Normalized IFetch From Memory 12                 | 26 |

| Table 7.8: | Normalized IFetch From Memory M0                 | 28 |

| Table 7.9: | Possible Sources for Operands W, X, Y and Z      | 31 |

| Table 9.1: | Speedups For Various Execution Modes             | 39 |

#### FREQUENTLY USED M-CORE INSTRUCTIONS

The following contains brief descriptions of M-CORE instructions that are frequently used throughout this dissertation.

In this ISA, an instruction typically has the following format: ops rx, ry, where rx and ry are source registers; and rx is also the destination register [MCORE98].

| Mnemonic                          | Description Example                                                                                                                                           |                                         |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| ldb, ldh, ldw<br>stb, sth, stw    | Load byte; load halfword; load wordldwr6, (r2)Store byte; store halfword; store wordstbr7, 4(r3)                                                              |                                         |

| bf, bt                            | Branch if c-bit clear; branch if c-bit set bt TARGET                                                                                                          |                                         |

| cmplt<br>cmpne<br>cmphs<br>cmpnei | Compare less than, set c-bit if truecmplt r4, r7Compare not equal, set c-bit if truecmpnei r6, 3Compare higher or same, set c-bit if truecmpnei r6, 3         |                                         |

| add, addi,<br>sub, subi,<br>rsub  | Add; add immediate<br>Subtract (rx = rx - ry); subtract immediate<br>Reverse subtract (rx = ry - rx)                                                          | add r6, r8<br>subi r8, 2<br>rsub r9, r2 |

| decne<br>declt                    | Decrement, then set c-bit if not equal 0decne r1Decrement, then set c-bit if less than 0declt r1                                                              |                                         |

| mov, movt                         | Move; move if c-bit set mov r3, r6                                                                                                                            |                                         |

| lsr, lsri<br>lsl, lsli<br>asri    | Logical shift right; logical shift right immediatelsrr7, r5Logical shift left; logical shift left immediatelslir7, 8Arithmetic shift right immediateasrir7, 8 |                                         |

| or, xor                           | Logical or; exclusive-or                                                                                                                                      | or r2, r3                               |

| clrt                              | Clear register if c-bit set                                                                                                                                   | clrt r8                                 |

| mul                               | multiply                                                                                                                                                      | mul r3, r4                              |

| ixh                               | Index halfword ( $rx = rx + (ry \ll 1)$ )                                                                                                                     | ixh r4, r1                              |

| tst                               | Test with zero (clear c-bit if (rx & ry) == 0; set otherwise)                                                                                                 | tst r4, r5                              |

| zextb                             | Zero extent least significant byte zextb r3                                                                                                                   |                                         |

| lrw                               | Load relative word: load a word from DATA_LABEL into rx                                                                                                       | lrw r2, [DATA_LABEL]                    |

| mtcr, mfcr                        | Move to control register from general purpose register; move<br>from control register to general purpose registermtcr r3, SSR                                 |                                         |

**Table 1: Frequently Used M-CORE Instructions**

#### Trademarks

M-COREis a trademark of Motorola Corporation.

i500plus is a trademark of Motorola Corporation.

Palm VII is a trademark of 3Com Corporation.

Palm.Net is a trademark of 3Com Corporation.

SmartPhone is a trademark of Neopoint Incorporation.

WebBank is a trademark of Leonia Bank Corporation.

SHARC is a trademark of Analog Devices Corporation.

TMS320Cxx is a trademark of Texas Instrument Incorporation.

PowerPC AltiVec is a trademark of Motorola Corporation.

Cray-1 is a trademark of Cray Research Incorporation.

IA-64 is a trademark of Siemens Incorporation.

Crusoe is a trademark of Transmeta Corporation.

StarCore is a trademark of Transmeta Corporation.

# **CHAPTER 1**

# **INTRODUCTION: LOW-COST, LOW-POWER DESIGNS FOR EMBEDDED APPLICATIONS**

Low-cost, low-power designs have been gaining importance in microprocessor systems primarily due to increasingly wide spread use of portable and handheld applications. These applications are also known as *mobile applications*.

Mobile computing and mobile applications, for the purpose of this work, refer to computing systems for consumers' portable and handheld applications that include pagers, cellular phones, personal digital assistants (PDA), global positioning systems (GPS), etc. These applications are powered by a battery system that has a limited energy storage capacity.

In this Chapter, we will examine the importance of mobile computing systems and their future trends. We will also examine some of the important characteristics and requirements of such systems. We will give an overview of our proposed execution model, called the *pseudo-vector machine*, for mobile applications. We will then examine the strength of vector processing and their suitability for such systems.

#### 1.1 The World Of Mobile Computing

The Personal Computer (PC) market has been enjoying tremendous growth in the past two decades. The growth in this market, in terms of profit margins, has recently been slowed down. The sharpest growth has been gradually shifting from the low volume and high profit margin, to the high volume and low profit margin PC market - a sign of a maturing market. The market as a whole will continue to grow, primarily being sustained by: (i) the general break down of the world's traditional trading boundaries, opening up the world's mass markets; and by (ii) the rapid advances and growth in the internet.

We are entering an era of *personal communication*. Early nineties marks the beginning of this era where we saw the rapid growth in computing, pagers, cellular phones and web-based mobile applications. This era is characterized by the needs of an individual to acquire the information and knowledge he or she needs, at any time, at anywhere, precisely and instantly.

The personal communication era was enabled by the adaptation and popularization of the internet. With the society becomes increasingly mobile, accessing to the internet via the traditional workstations or desktop computers can no longer satisfy the changing needs of the consumers. These needs range from stock trading, accessing to the weather forecasts, to locating a restaurant. Mobile computing serves these needs. The growth of the internet will continue to benefit the mobile computing market.

3Com Corp. has been offering Palm VII<sup>TM</sup> Connected Organizer since 1998. In conjunction with the Palm.Net<sup>TM</sup> internet access service provided by 3Com, a user can use Palm VII to send/ receive emails, obtain stock quote, sports scores, check flight information or the weather, etc. [PALMVII98].

Motorola Incorp., through Nextel Communications Incorp., has been offering iDEN i500plus<sup>TM</sup> multi-service digital wireless phone. This WML (Wireless Markup Language)-compliant phone features Internet microbrowser, two-way e-mail and wireless modem functionality. A user of this phone can check news, weather and stocks, find phone number and address information, and even get driving directions [IDEN99].

Nokia Corp. and Palm Computing Inc. (a 3Com company) have recently announced a broad joint development and licensing agreement to create a new pen-based product line that integrates telephony with data applications, personal and professional information management [PALMVII99].

Neopoint Inc. has recently announced its availability of its Smartphone<sup>TM</sup> (through Sprint) - a cellular phone with limited web browsing capabilities [NEOPOINT99a, NEOPOINT99b].

Leonia Bank of Finland will be offering its customers online banking services, WebBank<sup>TM</sup>, through the WAP (Wireless Application Protocols) phones, in the spring of 2000. These services are based on Public Key Infrastructure (PKI), digital signatures and strong encryption. The bank will identify the customer with digital signatures located on a SIM card of a mobile phone. Customers using digital signatures do not need cumbersome passwords anymore. With digital signatures mobile phone banking will be a lot easier and more secure than before [LEONIA00].

Very soon, we will be seeing all the consumers' mobile applications, including email, fax, pager, personal organizer, cellular phone, GPS, stock quote, weather forecast and other web-based applications integrated into a single, lightweight, device that everyone carries.

#### **1.2 Important Characteristics Of Mobile Systems**

One of the important factors that decides whether a portable product can succeed in the market place is "how long can the product operate before its battery needs to be replaced or recharged". Other important factors are the system costs and performance.

Perhaps to the surprise of some readers, in many mobile systems, improving the performance can often help solve the "energy problems." Unfortunately, the "low-power objective" for mobile computing systems is not a straight forward concept. To begin with, the low power design goal for such a system is not to maximize the battery life, but to maximize the number of operations performed per battery discharge.

In order to further understand the "power problem" in mobile computing, we will first need to understand some characteristics of a mobile computing system.

#### **1.2.1 Alternate Operating Modes**

To conserve energy, power-down techniques are widely employed in mobile computing systems, at all levels of design hierarchies. A mobile application typically operates alternatively between two operating modes: (i) burst mode (or active mode), where active computations are performed; and (ii) power-down mode (or sleep mode), where the system is asleep waiting for a new computational event to occur. A paging system, for example, is only awaken to process an incoming message, and is put back to sleep once the computation is completed.

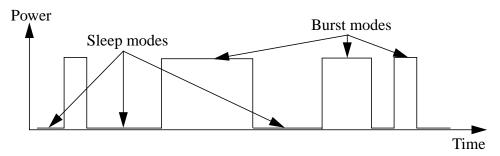

Figure 1.1 shows an example of the instantaneous power of a mobile computing system, going through a series of burst and sleep modes.

Figure 1.1: Instantaneous Power Of A Mobile Computing System

A mobile computing system typically consists of a digital subsystem, among with other subsystems. A cellular system, for example, these other subsystems include receiver/transmitter subsystem, the display subsystem, the keypad subsystem, etc.

From the energy consumption point of view, if the digital subsystem consumes only a small fraction of the overall system power, then it will be advantageous to design that subsystem to improve the overall system performance. By shortening the time the system is in burst mode (thus shortening the time the system is consuming high power), the overall energy consumption can be reduced.

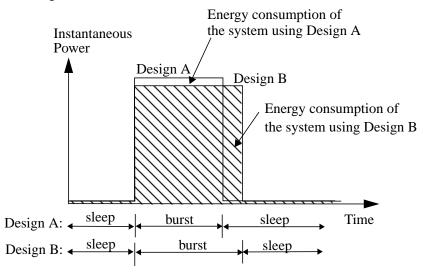

Figure 1.2 shows the instantaneous power of two competing designs operating through a "sleep-burst-sleep" sequence. Design A has higher performance with slightly higher power during burst mode, while Design B has lower performance with slightly lower power during burst mode. Design A completes the computational task earlier and immediately puts the system to sleep. Since energy consumption is the integration of power over time (given by the area under the power-time curve), the overall energy consumption of the system using Design A, in this case, is lower than that of Design B.

Figure 1.2: Energy versus power consumption

#### 1.2.2 Performance vs. Instantaneous Power

From the above example, it is arguable that *if a digital subsystem (microprocessor included) consumes only a small fraction of the overall system power, then it is advantageous to design the subsystem to improve the overall system performance.* That is, we solve the "power problem" by improving the performance, possibly at the expense of slightly higher power consumption during burst mode.

The battery systems are, unfortunately, not ideal. They possess internal resistance. If higher power is continuously drawn from these batteries, then less useful energy will be available to the rest of the system due to this internal resistance. To reduce such dissipations, one would argue that we should operate a mobile system at a lower power level, possibly at the expense of performance. That is, we solve the "power problem" by lowering the power consumption during burst modes [Martin99, Surampudi99].

By now it should become clear that as far as the digital subsystem is concerned, to achieve the "low-energy" object, one needs to perform complex trade-offs that involve the operating voltage and frequency of the digital subsystem, as well as the system environments which include the power consumption characteristics of other subsystems, and the battery subsystem itself.

In this dissertation work, we will focus on designing microprocessor cores for *mid to low*end, ultra-lightweight, embedded mobile applications. In these specific design environments, the digital subsystems often consume a small fraction of the overall power. We will thus adapt the "high performance" approach in solving the "power problem", as described in Section 1.2.1. In summary, the design goals in our design environments are (in order of importance):

- 1. Low cost (low chip area);

- 2. High performance;

- 3. Low power.

The above ordering has the following implications. Once an area budget is set for a specific application, we should then design the digital subsystem to improve the overall performance, as much as possible. In doing so, we can often (though not always) lower the overall energy consumption. Furthermore, any low-power design technique that can reduce power consumption during burst mode, should only be used *if* they do not degrade the overall performance.

Conversely, if a design technique that reduces power consumption of the digital subsystem during burst mode but degrades the system performance, then the overall energy consumption may reduce or increase, depending on the system power relative to the power consumption of the digital subsystem.

#### **1.3 Execution Modes For Mobile Systems**

At certain time, many mobile applications require the machines to perform some highly repetitive DSP functions. Large amount of instruction level parallelism (ILP) is present in these applications. But at some other time, they require the machines to perform control intensive functions.

To address the needs for mobile computing, some desktop CPUs have been incorporating some DSP capabilities into their instruction set and designs [Massana99, Lexra99, etc.]. On the other hand, some DSP processors are now incorporating some general control functions into their designs [SHARC97,StarCore98].

Some systems use dual-core solutions to address this problem [DSP56654,etc.]. In these systems, one core performs all the control intensive functions; while the other core performs the specialized DSP functions. The two cores communicate through some communication channels, such as a shared memory. These systems often employ dual instruction streams, one for each execution cores. The high development costs associated with this approach could only be justified if the specialized market segment where the system is designed to, has sufficiently large market volume to amortize these non-recurring engineering costs.

#### 1.4 Pseudo-Vector Machine - An Architectural Overview

In this dissertation, we will present a processing paradigm that is capable of executing in two modes: (i) a scalar execution mode for control functions; and (ii) a vector execution mode for exploiting the ILP that is present in these applications.

The vector execution mode can be further divided into a "true" vector mode and a "pseudo" vector mode. For loops that are highly vectorizable, the machine uses a "true" vector processing paradigm to process the loops. For loops that are difficult or impossible to vectorize, the machine uses a "pseudo" vector processing paradigm (similar to the DSP's style of processing) to process the loop.

This machine executes all these modes on a single datapath using a single instruction stream. Each instruction in this stream can be classified as either a scalar instruction or a vector instruction. When a vector instruction is fetched and decoded, the machine enters a vector execution mode. The machine only exits the vector mode via a few pre-defined mechanisms. We will call this execution model the *pseudo-vector machine*.

The following are some important features of the pseudo-vector machine.

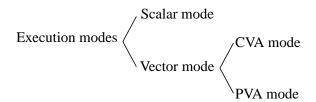

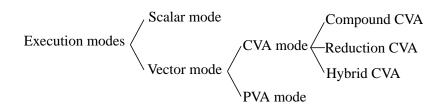

- The pseudo-vector machine has two major execution modes: scalar mode and vector mode.

- While in vector mode, this machine can perform two types of vector arithmetic: the Canonical

*Vector Arithmetic* (CVA) and the *Pseudo-Vector Arithmetic* (PVA). Correspondingly, there are two vector instructions: a CVA instruction and a PVA instruction. Figure 1.3 shows all the execution modes in this machine.

#### Figure 1.3: Various Execution Modes On The Pseudo-Vector Machine

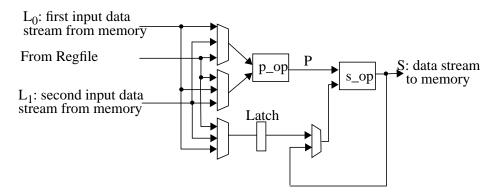

- When executing in a vector mode, the vector instruction (CVA or PVA instruction) can optionally enable up to two input data streams from the memory (denoted as L<sub>0</sub> and L<sub>1</sub>) and one output data stream to the memory (denoted as S).

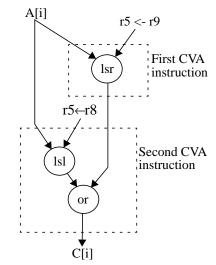

- When the machine executes in a CVA mode, data are continuously streamed from the memory, processed by a chain of functional units and streamed back to the memory, in a highly pipelined fashion. The CVA mode represents a "true" vector processing paradigm.

- When the machine executes in a PVA mode, the corresponding assembly code consists of a PVA instruction followed by a *loop body*. The loop body is composed of multiple scalar instructions. The PVA instruction is very similar to the "DO UNTIL" or "REPEAT" instructions in the traditional DSP processors. A PVA instruction can optionally enable up to two constant-stride load operations (L<sub>0</sub> and L<sub>1</sub> streams) and one constant-stride store operation (S stream) to be automatically performed during loop executions. The PVA mode represents a "pseudo" vector processing paradigm similar to the DSP's style of processing.

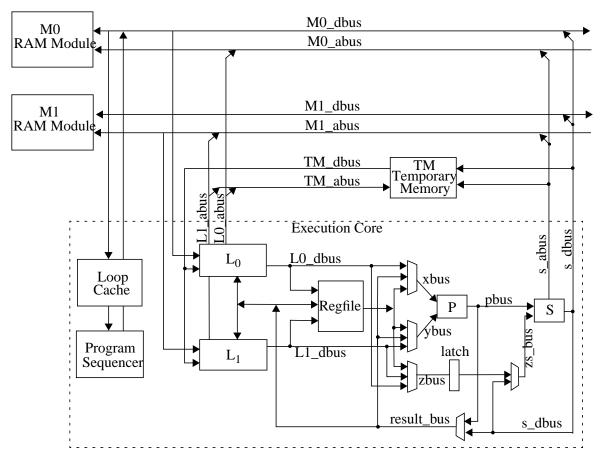

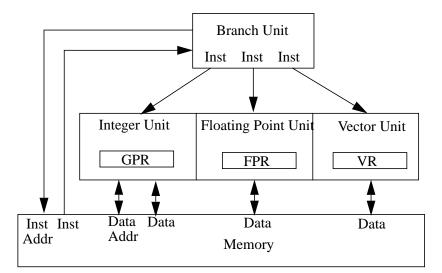

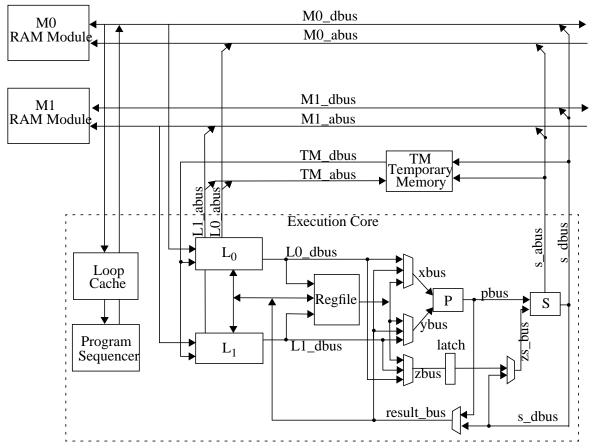

- The CPU architecture of the pseudo-vector machine is shown in Figure 1.4.

- When executing in a vector mode (CVA or PVA mode), the memory system can support up to two data reads, one data write and one instruction fetch in each cycle.

- In this machine, there are three independent on-chip memory modules, M0, M1 and TM. M0 supplies instructions and data, while M1 supplies data only. TM (temporary memory) is a small memory block used to store temporary vectors only.

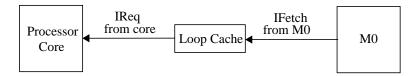

- When executing program loops, a small *loop cache* is used to store the instructions.

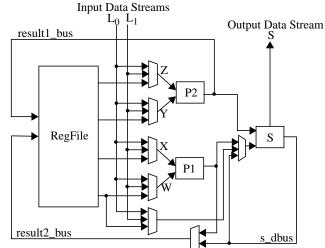

- Within the execution core, there are two load units, L<sub>0</sub> and L<sub>1</sub>, a store unit S, a register file Regfile and a general purpose functional unit P (see Figure 1.4).

- Besides performing the memory store operations, the S unit can also perform some simple, commutative arithmetic and logical functions, such as "add", "and", "or", "xor", etc.

- When executing in a scalar mode, the execution core behaves like a single-issued pipelined

Figure 1.4: The CPU Architecture for the Pseudo-Vector Machine

machine. It uses the Regfile and the P unit for computation, and  $L_0$  and S units for memory load and store operations, respectively.

- When executing in a PVA mode, the execution core also behaves like a single-issued pipeline machine, except that it can optionally enable up to: (i) two input data streams L<sub>0</sub> and L<sub>1</sub>; and (ii) one output data stream S. In addition, the machine uses some special loop count register to remove execution overheads associated with branches and loop control mechanisms.

- When executing in a CVA mode, data are continuously streamed in from M0/M1/TM, through the L<sub>0</sub> and L<sub>1</sub> units, processed by the P and S units, and optionally streamed back to M0/M1/TM. When executing in this mode, two distinct scalar arithmetic, p\_op and s\_op, can be simultaneously performed at P and S, respectively.

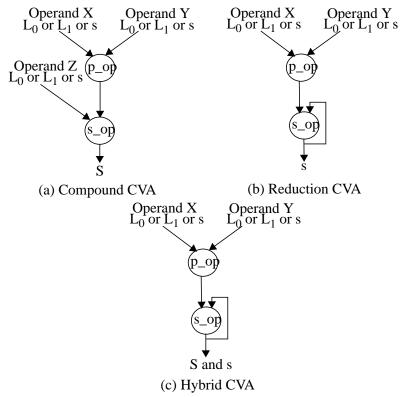

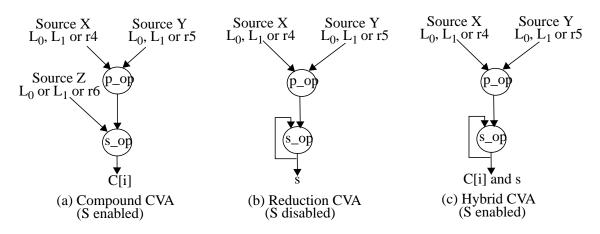

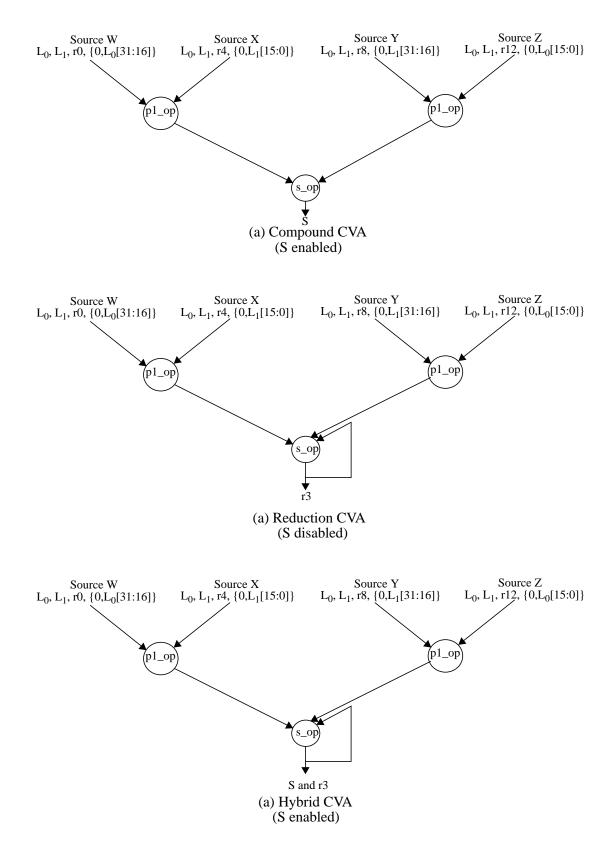

- There are three types of CVA executions: *Compound CVA*, *Reduction CVA* and *Hybrid CVA*. The data dependency graphs for these three types of executions are shown in Figure 1.5. In this Figure, operands X, Y and Z can source from input streams L<sub>0</sub>, L<sub>1</sub> or a scalar s. The outputs of these executions can be written to an output stream S or to a scalar destination s.

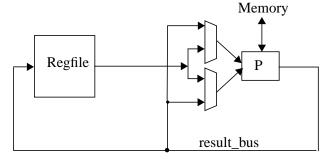

- In this datapath, all scalar and vector executions use the same P unit. This means that many

arithmetic functions that are available to the scalar executions are also available to the vector executions.

#### 1.5 The Strength of Vector Processing

In this Section, we will attempt to motivate the strength of vector processing, in the context of low-cost, low-power embedded computing environments. Readers who are familiar with vector processing may skip this Section entirely. Consider the following example.

#### Example 1.1:

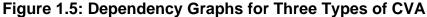

The following program loop performs an element-wise multiplication on two vectors. In vector form, it is performing: C[i] = A[i] \* B[i], for all i. The data dependency graph of this program loop is shown in Figure 1.6.

| L1:  |         |                         |

|------|---------|-------------------------|

| addi | r2,2    | // update stride value  |

| ld.h | r7,(r2) | // load A[i]            |

| addi | r3,1    | // update stride value  |

| ld.b | r6,(r3) | // load B[i]            |

| mul  | r7,r6   | // multiply A[i] * B[i] |

Figure 1.6: Data dependency graph for Example 1.1

In this example, intermediate values are produced and then consumed immediately. They are continuously being written back to and read from registers R6 and R7. These values are marked in Figure 1.6 as "\*". Since they are produced and consumed only once, it is inefficient to store these values in the often limited register storage space. This situation, unfortunately, is inevitable when a vector operation, such as the one shown in Example 1.1, is expressed using a scalar program in a load-store ISA.

A more efficient approach, is to chain a number of functional units together, with each unit performing a specific task. Thus when an intermediate value is produced by a functional unit, it is directly passed on to the next functional unit down the chain, thereby avoiding all the read and write traffic to the register file associated with this value.

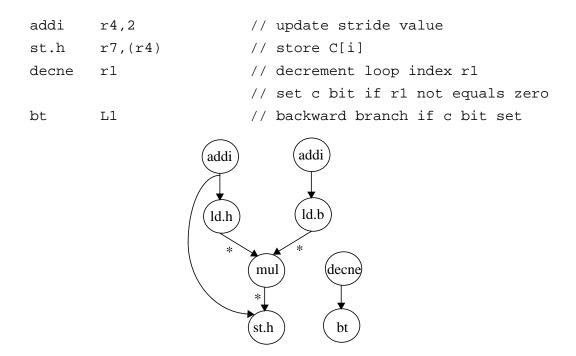

Besides saving power, we could also pipeline the vector executions, such that one result could be produced in every cycle. The time required to perform a vector operation is given by Ts + n/Tr, where Ts is the initial setup cost, n is the vector length and Tr is the throughput rate in number of results produced per cycle. If a scalar machine takes m cycles to execute one iteration of the equivalent program loop, then the speedup using the vector machine is given by nm/(Ts+n/ Tr), or nm/(Ts+n) for Tr=1. Maximum speedup could be achieved when Ts is sufficiently small and n is sufficiently large. In this case, the speedup approaches m, the number of cycles it takes for

10

the scalar machine to execute one iteration of the program loop. The relationship between speedup and n with Tr=1 is shown in Figure 1.7.

Figure 1.7: Relationships Between Speedup and n with Tr=1

Another subtle benefit of vector processing is its low instruction fetch bandwidth. Take Example 1.1 for example. The scalar program loop requires 8 instructions to be fetched during each iteration. In a vector machine, after fetching the initial vector setup code and the vector instruction itself, the machine does not need any further instruction fetch to perform the entire vector operation. As a result, the instruction fetch bandwidth and its associated memory traffic are much lower.

In summary, the strength of vector processing arises from:

- The ability to pipeline various operations on a single data stream (to improve performance);

- Efficient data storage and movement (large amount of temporary data are produced and consumed by adjacent functional units without going through the register file or the memory system); and

- Smaller routing area (result produced by a functional unit is routed directly to its destination functional unit, instead of broadcasting it to the entire datapath);

- Lower instruction fetch bandwidth.

Furthermore, efficient data movements and lower routing area could also mean lower power consumption. The strength of vector processing makes it very suitable for the low-cost, low-power embedded computing systems.

#### 1.6 Vector Processing vs. Pseudo-Vector Processing

When a DSP algorithm or function is implemented on a DSP machine, it is often being transformed into program loops. The optimizing compiler then tries to re-structure the loop such that all the possible parallelism can be easily exploited by the machine.

#### **Vector Processing**

In mobile applications, some program loops are highly vectorizable, in the sense that they perform well defined vector operations. For example, a loop that performs a vector operation described by C[i] = A[i] + B[i], for all i, is a highly vectorizable loop. Highly vectorizable loops can be most efficiently executed using a "true" vector processing paradigm. In this paradigm, data are continuously streamed from the memory and are processed by a chain of functional units in a highly pipelined fashion. The processed data are then continuously streamed back to the memory. All temporary results produced during the vector operations are not written to or read from the register file.

#### **Pseudo-Vector Processing**

Some program loops, however, are impossible or difficult to vectorize. They may become vectorizable after being transformed by the compiler to "fit" the vector processing paradigm. These transformations involve adding some addition vector operations that may include mask generations, gather and scatter operations, etc. There are, however, overheads associated with these operations. In this dissertation, we will call these type of vector arithmetic *pseudo-vector arithmetic* (PVA).

For example, a loop that performs a vector operation described by C[i] = (A[i]>B[i])?  $A[i]^2 : A[i]+B[i]$ , for all i, is difficult (or costly) to vectorize. It is considered here to be a PVA arithmetic.

Many today's DSP machines can execute the PVA arithmetic efficiently. They include Analog Devices' ADSP-2106X SHARC<sup>TM</sup> chip [SHARC97] and Texas Instrument's TMS320Cxx<sup>TM</sup> family of chips [TMS320C3x]. These machines improve the performance by removing many of the overheads associated with: (i) loop control mechanism; (ii) constant-stride load; and (ii) constant-stride store.

# **1.7 The Basic Framework For This Dissertation**

In this work, we will use the M-CORE instruction set architecture (ISA) for the purposes of illustration and evaluation. The M-CORE ISA uses 16-bit fixed length instruction encoding. It has one of the highest code density among all the commercially available ISA. Furthermore, the ISA provides extensive bits and bytes manipulation operations that are ideal for many real time embedded control and DSP applications [MCORE98,Moyer98].

An assembly program written for the pseudo-vector machine consists of regular scalar instructions (the M-CORE instructions in this case), with two additional vector instructions. The first vector instruction, the CVA instruction, vectorizes critical loops that are "highly vectoriz-able". These vectorized loops are then executed on this machine using a "true" vector processing paradigm.

The second vector instruction, the PVA instruction, vectorizes critical loops that perform pseudo-vector arithmetic. These vectorized loops are then executed on this machine using a "pseudo"-vector processing paradigm.

For the purpose of this work, when a program loop is replaced by its equivalent code that consists of one or more vector instructions (CVA and/or PVA instructions), the program loop is said to be *vectorized*. This vectorized code segment is also called the *vector equivalent* of the original scalar program loop, as they both perform the same function. Vectorization can occur at the assembly level or at the source code level.

A program loop that can be vectorized only using CVA instruction(s) is called a *CVA vectorizable loop*. A program loop that can be vectorized using PVA instruction(s) is called a *PVA vectorizable loop*. The PVA execution represents a more general vectorizing mechanism. Thus a loop *that is CVA vectorizable, is also PVA vectorizable.*

#### **Profile-Based Performance Evaluations**

In this work, developing a vectorizing compiler for this machine is beyond the scope of this work. Without a vectorizing compiler, there is no vectorized assembly code. Without which, it is impossible to evaluate exactly the performance benefits by using a detail simulation model of the machine. Instead, the following approach is adopted.

The benchmarks were not re-compiled to vectorize the critical loops. Cycle-based simulations were first performed on a single-issued, four-stage pipelined machine. This scalar machine, which executes M-CORE instructions, does not have any vector processing capability. The performance statistics collected on this scalar machine were used as a base result. This machine is also referred to here as the *base machine*.

The original scalar programs were dynamically profiled. Each program loop in these benchmarks was marked, and the number of invocations and the number of iterations were recorded. We then vectorized these critical loops by hand, at the assembly level.

The number of cycles saved for each loop were then computed using the profiled statistic. All the vector startup and exit costs were subtracted from these savings. We then summed up the net savings for each loop to give the total saving.

Throughout this dissertation, examples will be extensively used to illustrate some important concepts, procedures and techniques for vectorizing program loops. They will also be used to give detail illustrations on how we estimate execution cycle saving by using various vector constructs. These detailed examples may bore some of our readers; however, we think that this level of details is necessary in order to fatefully and accurately disseminate these information. The detail workings of evaluating the performance, for each critical loop, in each benchmark program, are given in Appendix B.

# **1.8 Profile-Based Performance Evaluations - An Example**

We will use the following example to illustrate how we can estimate the performance improvements on this machine.

#### Example 1.2:

Vectorize the loop shown in Example 1.1 on page 9 using a CVA instruction. This loop is executed on a single-issued scalar machine for 100 iterations. This single-issued machine takes two cycles to execute a load instruction, and 2 cycles to execute a multiply instruction. Estimate the speedup when this loop is executed on the pseudo-vector machine using a CVA instruction.

This loop performs a vector operation described by C[i]=A[i]\*B[i], for all i. The loop takes 12 cycles per iterations to execute, except for the last iteration where it takes only 11 cycles to execute (the branch instruction "bt" takes one cycle to execute when it is not taken; 2 cycles otherwise). Thus the execution cycles, on the scalar machine, is 12x99 + 11x1 = 1199 cycles.

The loop can be vectorized using a CVA instruction as follows.

<Some initialization code> // assign L0 to A, L1 to B, S to C. CVA mul @L0, @L1, @S;

In this example, stream  $L_0$ ,  $L_1$  and S are enabled and are assigned to vector A, B and C, respectively. The CVA instruction multiplies, element-wise, between vectors A and B and writes the results to vector C.

The initialization code preceding the CVA instruction sets up the starting load/store addresses, operand sizes, constant stride values and vector length for vectors A, B and C. Executing this initialization code adds overhead to the vector executions. In addition, there are also other costs associated with this vector execution: vector instruction decode, pipeline warm-up cost, vector mode exit cost, etc. The total vector setup and exit costs, in this example, is 11 cycles (vector setup and exit costs will be described in detail in Section 6.4 in Chapter 6).

The P unit that performs the multiply function is fully pipelined. After these initial vector setup and exit costs, the pipeline can produce *one* result in *every* cycle. The execution cycles on the pseudo-vector machine is thus given by: 11 + 100 = 111 cycles. The speedup over the single-issued scalar machine is thus: 1199/111 = 10.80.

Unlike the traditional DSP processors, this machine can access three data streams per cycle during vector computations.

# **1.9** Contributions Of This Dissertation

As we will see later in this dissertation, with comparable hardware costs, for loops that are highly vectorizable, the CVA execution (the "true" vector processing) often offers higher performance benefits and lower power consumptions. For loops that are impossible or too costly to vectorize, the PVA execution (DSP's style of processing) offers better performance benefits.

In this dissertation, we propose a CPU architecture to perform both the "true" vector arithmetic and the "pseudo" vector arithmetic on a single datapath. The optimizing compiler for this machine tries to "vectorize" the critical loops by selecting between a "true" vector processing paradigm, a "pseudo" vector processing paradigm, or a combination of both. As we will see later on, by providing the ability to execute both of these processing paradigms, we can achieve performance improvements that are higher than any of the individual paradigm. A drawback of this dissertation is that a single-issued pipelined machine is used as a base machine. All performance results given in this dissertation are expressed in terms of improvements over this base machine. This dissertation would have been more interesting if the performance results are given relative to, say, a traditional DSP machine, similar to the ADSP-2106X SHARC chip.

Nevertheless, this dissertation has certainly explored some architectural *alternatives* to exploit ILP found in these embedded applications. In particular, it tries to exploit parallelism in a "vertical" (or "depth") direction, rather than in a "horizon" (or "width") direction as in a conventional wide-issued VLIW machine. This different will be described later in Section .

# 1.10 A Note On Vector Processing Paradigm

The first commercially available vector machine was the Cray-1<sup>TM</sup> vector machine, built in 1974 [Cray1]. In this machine, multiple function units can be chained together to perform different scalar arithmetic functions simultaneously.

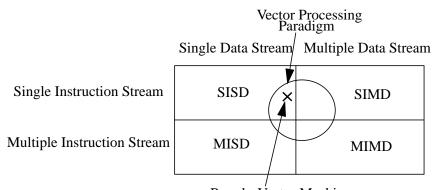

Later machines extended this idea to *array processing*, where a single instruction stream is executed by multiple PEs, each operates on a single data stream. These later machines can be classified as SIMD (single instruction stream and multiple data stream) vector machines. PowerPC's AltiVec<sup>TM</sup> is a recent example of such machines [ALTIVEC98].

The Cray-1, on the other hand, has only one Processing Elements (PE). Each instruction in this machine only processes and consumes a single data stream. This machine can thus be classified as a SISD (single instruction stream and single data stream) vector machine.

Our pseudo-vector machine can also be classified as a SISD vector machine, since it has only a single PE, processing a single data stream. Figure 1.8 shows how the pseudo-vector machine relates to the various types of processing paradigms.

The rest of this dissertation is organized as follows. Chapter 2 describes related work. Chapter 3 classifies and discusses two types of vector arithmetic that can be performed on this machine. They are the CVA and the PVA arithmetic. Chapter 4 describes the programming model, on this machine, for vector executions. It also describes various special registers used for these executions. Chapter 5 describes the implementations of this machine. Chapter 6 describes the benchmarks used in this work and the performance evaluation methodologies. Vector setup costs and expressions for performance evaluation for typical program loops will also be derived in this

Pseudo-Vector Machine

# Figure 1.8: Various Processing Paradigms

Chapter. Chapter 7 presents some experimental results. Chapter 8 presents some architectural extensions for DSP applications. Chapter 9 summaries the dissertation.

# CHAPTER 2 Related work

This Chapter describes related work to this dissertation.

# 2.1 Software Loop Unrolling

In software loop unrolling, multiple iterations from a loop are combined into a single iteration, with the branch instructions interleaving between the iterations being removed. The registers in each copy of the loop body are given different names to avoid unnecessary WAW (Write-After-Write) and WAR (Write-After-Read) data dependences. In a wide-issued machine (VLIW or superscalar machine), loop unrolling exposes the available ILP to the hardware by creating longer sequences of straight-line code.

Figure 2.1 shows an example of software loop unrolling. Figure 2.1(a) shows the original loop; Figure 2.1(b) shows that the loop is unrolled twice; and Figure 2.1(c) shows the unrolled loop is register renamed and re-scheduled so that dependent instructions are further apart. In the unrolled loops, R9 is assumed to be appropriately initialized for proper loop exit condition.

Software loop unrolling, however, results in a larger static program loop. Larger code size has an adverse affect on system cost as well as on instruction cache performance. In addition, software loop unrolling also increases register pressure on the compiler due to register renaming.

# 2.2 Software Pipelining and Register Rotation

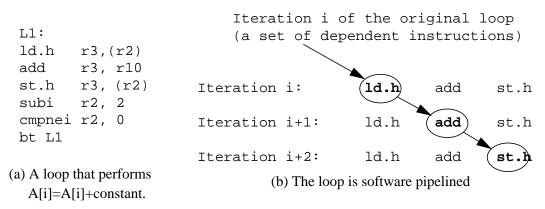

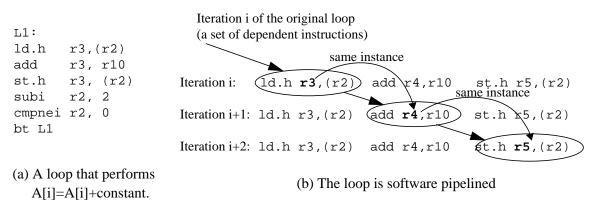

Software pipelining is frequently used in wide-issued machines (VLIW and superscalar machines). This technique reorganizes loops such that each iteration in the software-pipelined code is made from instructions chosen from different iterations of the original loop. The scheduler

| L1:<br>ld.h r3,(r2)<br>add r3, r10<br>st.h r3, (r2)<br>subi r2, 2<br>cmpnei r2,0<br>bt L1 | L1:<br>ld.h r3,(r2)<br>add r3,r10<br>st.h r3,(r2)<br>subi r2,2<br>ld.h r3,(r2)<br>add r3,r4<br>st.h r3,(r2)<br>subi r2,2<br>cmpnei r2,0<br>bt L1 | L1:<br>ld.h r3,(r2)<br>ld.h r7,2(r2)<br>add r3,r10<br>add r7,r10<br>st.h r3,(r2)<br>st.h r7,2(r2)<br>subi r2,2<br>cmpnei r2,0<br>bt L1 |

|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| (a) A loop that performs<br>A[i]=A[i]+constant.                                           | (b) The loop is unrolled twice.                                                                                                                  | (c) The loop is register renamed<br>and re-scheduled so that dependent<br>instructions are further apart.                              |

# Figure 2.1: Software Loop Unrolling

essentially separates the dependent instructions that occur within a single loop iteration. Figure 2.2 shows conceptually how a loop is being software pipelined [Patterson96].

Figure 2.2: Software Pipelining

In a software pipelined loop, a multi-cycle instruction (such as a load instruction) may produce result that is only consumed in the next iteration; that is, an instruction may consume result that was produced in the previous iteration. To avoid over-writing a result before it is being consumed, the software pipelined loop may need to be unrolled and registers be renamed in software. Thus, software pipelining also enlarges code size and increases register pressure.

#### **Register Rotation**

In Intel's IA-64<sup>TM</sup> architecture, a technique called register rotation is used to minimize the code size expansion problem associated with software pipelining. In this technique, the hardware automatically renames the register by adding to the register number, a rotating register base (rrb) register. The rrb register is decremented when certain special software pipelined loop branches are

executed at the end of each iteration. Decrementing the rrb register makes the value in register X appear to move to register X+1 in the next iteration [IA64].

Figure 2.3 shows conceptually how a loop can be software pipelined using register rotation. In this example, register instance R3 in iteration i, is the same instance as register instance R4 in the iteration i+1; in turn, this register instance is the same instance as register instance R5 in iteration i+2, and so on.

Figure 2.3: Software Pipelining With Register Rotation

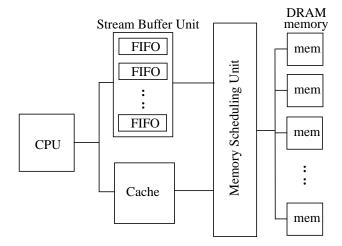

# 2.3 Stream Data Buffers In WM and SMC Architectures

In the WM architecture, Wulf first proposed using stream data buffers, under program control, to prefetch data from the memory into data buffers [Wulf92]. These buffers are organized as first-in-first-out (FIFO) queues. This technique can be illustrated using the following code segment for performing a vector dot product. In this code, "r0-r31" denotes integer registers and "f0-f31" denotes floating-point registers.

```

Sin32F f0, r6, r5, 4

Sin32F f1, r6, r5, 4

Loop:

f4 = (f0 * f1) + f4

JNI f0, Loop

```

A single instruction, *streamin*, informs a stream control unit that a sequence of data operands is to be read from the memory, starting at a specified location, with a specified stride and count. The starting location and the count are specified in registers R6 and R5, respectively. The stride value (4 in this example) is specified in the Sin32F instructions (streamin 32-bit floatingpoint operands). The first two Sin32F instructions set up two stream buffers. They designate registers f0 and f1 as the "head" of the two FIFO queues. Within the loop body, a read from one of these two registers dequeues a data item from the appropriate queue.

McKee et. al. [McKee95a,McKee95b] extended this work by proposing a Stream Memory Controller (SMC) architecture. In this architecture, multiple stream buffers were used to store: (i) data prefetched from the memory (input queue); and (ii) data to be stored to the memory (output queue). The heads of these FIFO queues appeared to the processor as memory mapped registers. After these streams are properly set up, a read from a designated memory location dequeues a data operand from an input queue; a write to a designated memory location enqueues a data operand to an output queue.

Figure 2.4 shows the block diagram of a SMC architecture. It shows how the CPU is interfaced with the memory system through a cache and a Stream Buffer Unit (SBU). The heads of the FIFO queues in the SBU appeared to the CPU as some pre-defined memory locations. These buffers are also used to buffer some single-use vectors to avoid polluting the cache.

Figure 2.4: SMC Architecture - A Dynamic Access Ordering System

In addition to the stream buffers, there is also a Memory Scheduling Unit that dynamically reschedules the access requests made by the SBU and the cache. The unit coalesces and reschedules these requests to take advantage of the page access behavior of the DRAM memory [McKee95a,McKee95b].

# 2.4 Data Address Generators

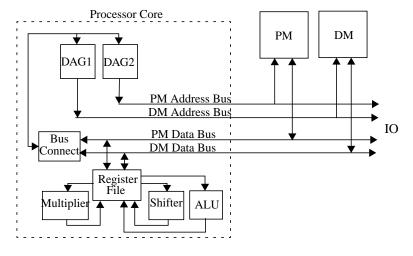

On the Analog Devices SHARC ADSP-2106x CPU, there are two independent on-chip memory modules: the Program Memory (PM) and the Data Memory (DM). PM is used to store

program instructions and data; while DM is used to store data only. In this CPU, there are two Data Address Generation units, DAG1 and DAG2. These two DAGs can independently generate two load/store addresses, enabling the processor core to access two operands (any combinations of read and write) in each cycle. The block diagram of the ADSP-2106x CPU is shown in Figure 2.5 [SHARC97].

Figure 2.5: ADSP-2106x SHARC Block Diagram

Each of these DAGs contains eight I registers and eight M registers that are accessible to a program. A load or store instruction can access the memory by specifying an I register and a M register. For example, the following load instruction loads the memory content from the PM, with an address stored in I0; the value I0+M3 is then automatically written back to register I0 after the load operation (i.e. that address stored in I0 is automatically post-incremented by the amount stored in M3). The data loaded from PM is stored into register R6 [SHARC97].

R6 = PM(I0, M3); // indirect addressing with post-modify.

# 2.5 Compute And Memory Move Instructions

The ADSP-2106x chip can also provide a "compute-and-move" instruction that combines a compute function with up to two memory load/store operations. These operations are performed in parallel, in a single cycle. An example of such instructions is shown below.

R7 = R6 + R0, DM(I0,M3)=R5, PM(I11,M15)=R4;

This instruction performs an add, and two memory store operations, all in a single cycle. The two memory operations can be any combination of load and store operations. The ADSP-2106x chip also provides some multifunction computations that combine parallel operations of the multiplier and the ALU, or the multiplier and dual functions in the ALU. The following shows two examples of such multifunction instructions [SHARC97].

| R3 = | R3 | * | R7, | R4 | = | R8 - | - F | R13; |    |   |    |   |      |

|------|----|---|-----|----|---|------|-----|------|----|---|----|---|------|

| R3 = | R3 | * | R7, | R5 | = | R11  | +   | R15, | R4 | = | R8 | _ | R13; |

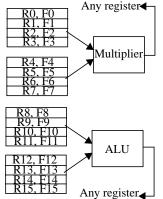

There are, however, certain restrictions on how these independent operations can read their source registers. Some of these restrictions are illustrated in Figure 2.6. This Figure shows that each of the four input operands for computations that use both the ALU and multiplier are constrained to a different set of four register file locations. The X operand to the ALU, for example, can only be R8, R9, R10 or R11. This is a limited form of VLIW machine [SHARC97].

Figure 2.6: Source Registers For Multifunction Computations (ALU and Multiplier)

# 2.6 Special Loop Instructions For Removing Loop Control Overheads

Several commercial DSP ISA have special loop instructions for removing the overheads associated with the loop control mechanism [SHARC97,TMS320C3x,TRICORE97].

# 2.6.1 The TriCore<sup>TM</sup> ISA

In the TriCore ISA, for example, three special branch instructions are used to handle program loops. They are JNEI, JNED and LOOP instructions. The JNEI and JNED instructions are like normal jump-not-equal instructions, but with an additional increment or decrement operation on a data register operand. The LOOP instruction only requires execution time in the first and last iteration of the program loop. For all other iterations of the loop, the LOOP instruction has zero execution time. Here are some examples of loops using these instructions [TRICORE97].

| mov d3, 3     | mov a2, 99 |

|---------------|------------|

| L1:           | L1:        |

|               |            |

| jnei d3,10,L1 | loop a2,L1 |

(a) A loop that executes d3=3,...,10 (b) A loop that executes 100 times

## Figure 2.7: Program loops using special loop instructions

The JNEI, JNED and LOOP instructions in the TriCore ISA are capable of removing almost all the overheads associated with the branches at the end of the original loop. They do not, however, remove overheads associated with the cs-load and cs-store operations, if there is any in the loop.

## 2.6.2 The SHARC ADSP ISA

On the Analog Devices' ADSP-2106x chip, a DO UNTIL instruction is available for program loop executions. There are two types of DO UNITL loops. One is the counter-based and the other is not. In a counter-based loop, the iteration count is first written to a special register called Loop Count Register (LCNTR), prior to the loop execution. An example of such loop is shown below.

```

LCNTR=30, DO label UNTIL LCE;

. . . loop body . . .

label: [last instruction of the loop body]

```

The number of iterations can be specified as an immediate field in the DO UNTIL instruction; or, the instruction can also specify a universal register that contains the loop count. LCNTR is decremented by one for each iteration executed. The loop continues to execute until the Loop Counter Expires (LCE).

In a non-counter based DO UNTIL loop, the terminating condition is specified in the instruction. The iteration count, however, is not. In this case, the loop exits when the terminating condition is met. An example of such loops is shown below.

DO label UNTIL AC; // exits when ALU Carry out is set . . . loop body . . . label: [last instruction of the loop body]

This machine supports three hardware stacks: PC stack; Loop Address Stack and Loop Count Stack. These three stacks work in a synchronized manner for loop executions. When the ADSP-2106x executes a DO UNTIL instruction, the program sequencer pushes the address of the

last loop instruction and the termination condition for exiting the loop (both specified in the instruction) into the Loop Address Stack. It also pushes the top-of-loop address, which is the address of the instruction following the DO UNTIL instruction, on the PC stack. When a loop exits, all three stacks are popped. The three-stack mechanism allows the removal of loop control overheads for nested loops.

# 2.7 Vector Processing

A vector processor can be classified as a SISD machine, a SIMD machine, among other paradigms (see Section 1.10 on page 16).

#### 2.7.1 Cray-1 Vector Machine - A SISD Vector Machine

The first commercially available vector machine, the Cray-1 vector machine, was primarily built for massively parallel scientific computations. Figure 2.8 shows the block diagram of the machine [Cray1].

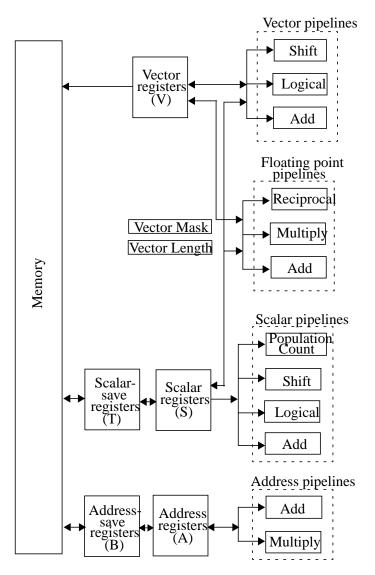

There are three sets of primary registers: vector registers (V); scalar registers (S); and address registers (A). In addition, there are also scalar-save registers (T) and address-save registers (B). These registers act as buffers between the memory and the primary registers.

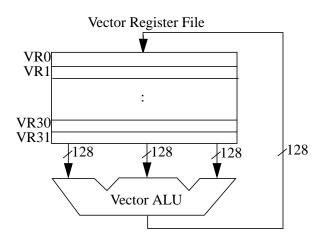

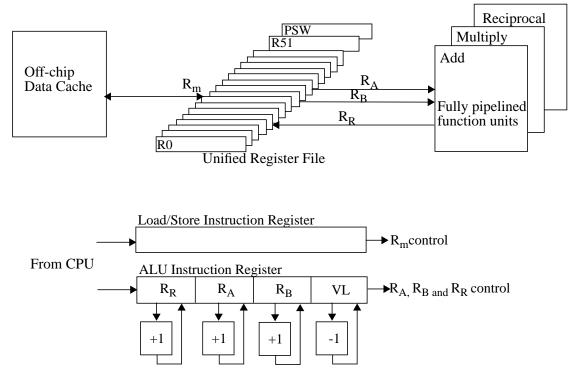

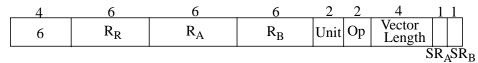

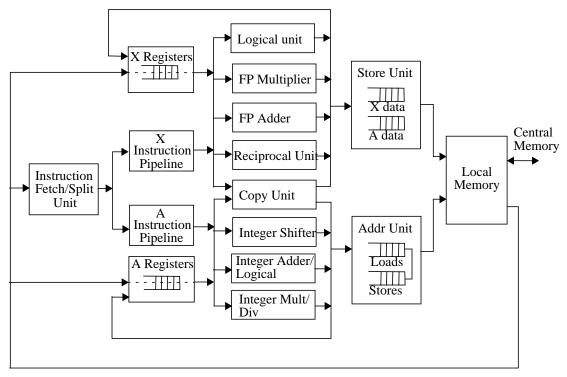

There are altogether 12 functions units in this machine. These functional units are organized into four groups: address, scalar, vector and floating-point pipelines. The vector pipelines obtain operands from one or two V registers and an S register. Results from a vector pipe are delivered to a V register. When a floating-point pipe is used for a vector operation, it can function similar to a vector pipe.