# **Disaggregated Memory Architectures for Blade Servers**

by

## Kevin Te-Ming Lim

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 2010

#### **Doctoral Committee:**

Professor Trevor N. Mudge, Co-Chair Associate Professor Steven K. Reinhardt, Co-Chair Professor Peter M. Chen Professor James S. Freudenberg Dr. Parthasarathy Ranganathan, Hewlett-Packard Labs © <u>Kevin Te-Ming Lim</u> 2010 All Rights Reserved

## **Table of Contents**

| Table of Contents                                       | ii   |

|---------------------------------------------------------|------|

| List of Figures                                         | vii  |

| List of Tables                                          | viii |

| Abstract                                                | ix   |

| Chapter 1 Introduction                                  | 1    |

| 1.1 Memory Capacity Trends                              | 4    |

| 1.2 Heterogeneity Opportunities in Enterprise Workloads | 7    |

| 1.3 Blade Servers                                       | 8    |

| 1.4 Thesis Statement                                    | 8    |

| 1.5 Contributions                                       | 10   |

| 1.6 Organization                                        | 11   |

| Chapter 2 Background                                    | 12   |

| 2.1 Current Main Memory Architectures                   | 12   |

| 2.1.1 Main Memory Architecture and DRAM                 | 12   |

| 2.1.2 Recent Designs for Increased Capacity             | 13   |

| 2.1.3 Distributed Shared Memory Architecture            | 16   |

| 2.2 Software Needs for Memory Capacity                  | 18   |

| 2.3 Servers and Blade Systems                           | 21   |

| 2.4 Data Centers                               |

|------------------------------------------------|

| Chapter 3 Disaggregated Memory Architecture    |

| 3.1 Disaggregated Memory Concept               |

| 3.2 Memory Blade Architecture                  |

| 3.2.1 Memory Blade Design                      |

| 3.2.2 Memory Blade Mapping                     |

| 3.2.3 Remote Memory Allocation and Revocation  |

| 3.3 System Architecture with Memory Blades     |

| 3.3.1 Page-Swapping Remote Memory (PS)         |

| 3.3.2 Fine-Grained Remote Memory Access (FGRA) |

| Chapter 4 Evaluation of Disaggregated Memory   |

| 4.1 Methodology                                |

| 4.1.1 Simulation Methodology                   |

| 4.1.2 Simulation Parameters                    |

| 4.1.3 Workloads                                |

| 4.2 Memory Expansion for Individual Benchmarks |

| 4.3 Power and Cost Analysis                    |

| 4.4 Server Consolidation                       |

| 4.5 Ensemble-level Memory Sharing              |

| 4.6 Alternate Designs                          |

| 4.6.1 FGRA with Page Migration55               |

| 4.6.2 FGRA Tunneled Over PCIe                  |

| 4.6.3 Simulated Hypervisor Sensitivity Study               | 56 |

|------------------------------------------------------------|----|

| 4.7 Discussion                                             | 57 |

| 4.7.1 Simulation Methodology                               | 57 |

| 4.7.2 Evaluation Assumptions                               | 58 |

| 4.7.3 Impact of the Memory Blade on Ensemble Manageability | 58 |

| 4.8 Summary                                                | 59 |

| Chapter 5 Hypervisor Prototype of Disaggregated Memory     | 61 |

| 5.1 Motivation                                             | 62 |

| 5.2 Prototype Design Choices                               | 63 |

| 5.3 Hypervisor Modifications                               | 65 |

| 5.3.1 Paravirtualization                                   | 66 |

| 5.3.2 Shadow Page Tables                                   | 67 |

| 5.3.3 Hardware Assisted Paging                             | 68 |

| 5.3.4 Implementation Limitations                           | 70 |

| 5.4 Evaluation and Validation of Simulation Results        | 71 |

| 5.5 Lessons Learned                                        | 75 |

| Chapter 6 Extending Disaggregation                         | 77 |

| 6.1 Motivation and Contributions                           | 78 |

| 6.2 A Benchmark Suite for the Internet Sector              | 80 |

| 6.2.1 Key Challenges                                       | 80 |

| 6.2.2 The Warehouse-Computing Benchmark Suite              | 81 |

| 6.3 Metrics and Models                         | 84  |

|------------------------------------------------|-----|

| 6.3.1 Metrics                                  | 84  |

| 6.3.2 Server and Data Center Cost Models       | 84  |

| 6.3.3 Performance Evaluation                   | 87  |

| 6.4 A New Server Architecture                  | 88  |

| 6.4.1 Cost Analysis and Key Issues             | 88  |

| 6.4.2 Compute Disaggregation                   | 89  |

| 6.4.3 Compaction and Aggregated Cooling        | 96  |

| 6.4.4 Memory Disaggregation                    | 98  |

| 6.4.5 Flash as Disk-cache with Low-power Disks | 102 |

| 6.5 Unifying the Architectural Solutions       | 105 |

| 6.5.1 Two Unified Designs                      | 106 |

| 6.5.2 Evaluation                               | 106 |

| 6.6 Discussion                                 | 107 |

| 6.6.1 Benchmark Suite                          | 107 |

| 6.6.2 Metrics and Models                       | 108 |

| 6.6.3 Amdahl's Law Limits on Scale-out         | 108 |

| 6.7 Summary                                    | 109 |

| Chapter 7 Related Work                         | 111 |

| 7.1 Disaggregated Memory                       | 112 |

| 7.1.1 Remote Memory Capacity                   | 112 |

| 7.1.2 Shared Memory Capacity                  | 112 |

|-----------------------------------------------|-----|

| 7.1.3 Increasing Memory Capacity              | 114 |

| 7.1.4 Multi-level Memory Hierarchies          | 115 |

| 7.2 Extending Disaggregation                  | 115 |

| 7.2.1 Warehouse Computing Workloads           | 115 |

| 7.2.2 Compute Disaggregation                  | 116 |

| 7.2.3 Flash in the Disk Subsystem             | 117 |

| 7.2.4 Data Center Architectures               | 117 |

| Chapter 8 Future Work                         | 118 |

| 8.1 Extending Memory Disaggregation           | 118 |

| 8.1.1 Policy Exploration and Other Workloads  | 118 |

| 8.1.2 Software Exposure of the Memory Blade   | 119 |

| 8.1.3 Memory Area Network                     | 120 |

| 8.1.4 Memory Cloud                            | 121 |

| 8.2 Synergy with Emerging Memory Technologies | 122 |

| 8.3 Content-Based Page Sharing                | 122 |

| 8.4 Fast Virtual Machine Migration            | 124 |

| 8.5 Memory Appliance Evolution                | 125 |

| 8.6 Improved Warehouse-Computing Workloads    | 125 |

| 8.7 Extending Compute Disaggregation          | 126 |

| Chapter 9 Conclusions                         | 127 |

| References                                    | 130 |

# **List of Figures**

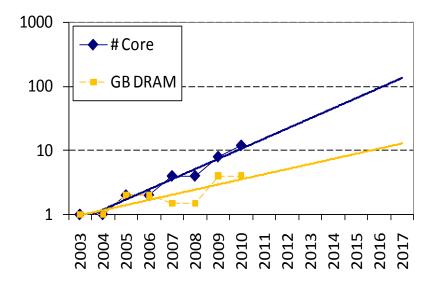

| Figure 1: Projected annual growth in number of cores and memory capacity  | 5        |

|---------------------------------------------------------------------------|----------|

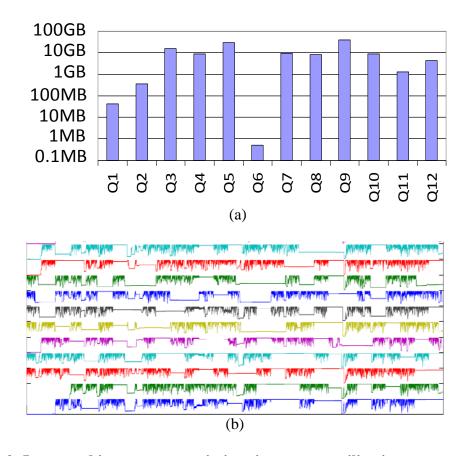

| Figure 2: Intra- and inter-server variations in memory utilization        | 6        |

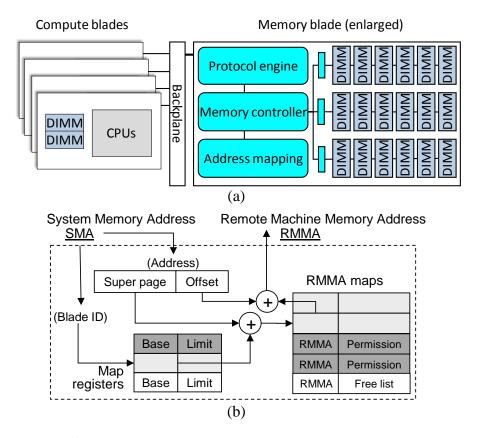

| Figure 3: Design of the memory blade                                      | 30       |

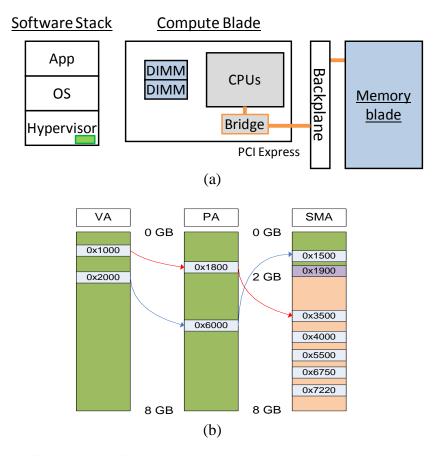

| Figure 4: Page-Swapping (PS) Remote Memory Design.                        | 35       |

| Figure 5: Fine-Grained Remote Memory Access (FGRA) Design                 | 37       |

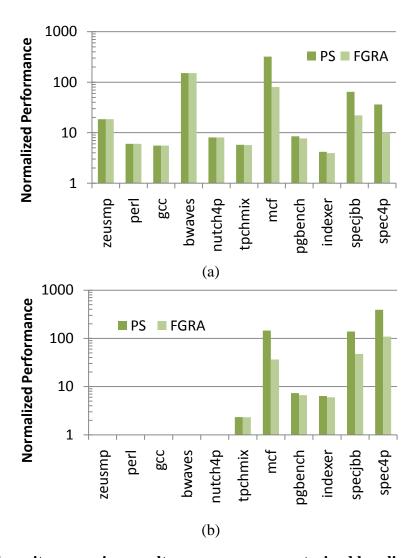

| Figure 6: Capacity expansion results over memory-constrained baselines    | 44       |

| Figure 7: Capacity expansion results over worst-case provisioned baseline | 46       |

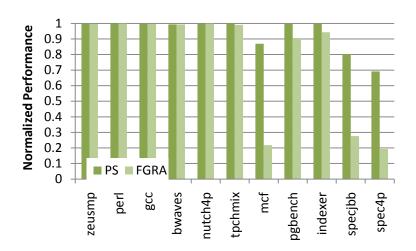

| Figure 8: Cost analysis of the memory blade                               | 47       |

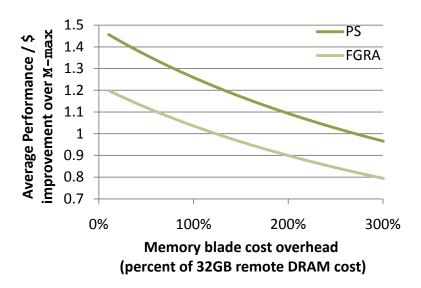

| Figure 9: Consolidation improvements enabled by disaggregated memory      | 49       |

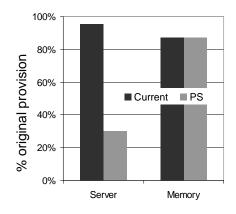

| Figure 10: Ensemble level sharing results.                                | 53       |

| Figure 11: Alternate FGRA design that supports page movement.             | 54       |

| Figure 12: Alternate FGRA designs that tunnels accesses over PCIe         | 55       |

| Figure 13: Average access time per remote page                            | 72       |

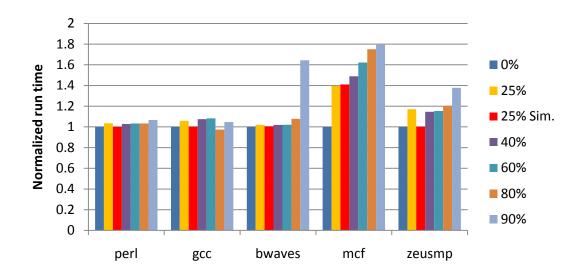

| Figure 14: Performance SPEC CPU benchmarks with varying percentages of    | remote   |

| memory.                                                                   | 74       |

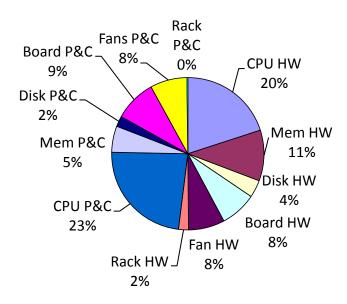

| Figure 15: Contribution of cost components for srvr2                      | 87       |

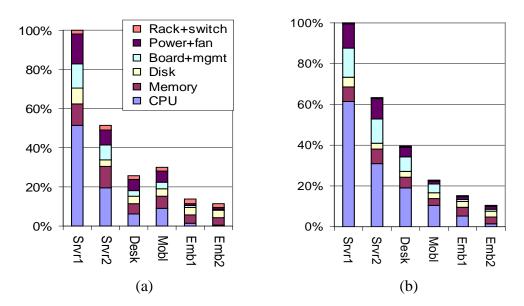

| Figure 16: Infrastructure and power and cooling cost comparisons across n | nultiple |

| system classes.                                                           | 92       |

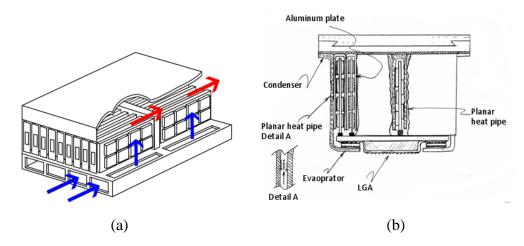

| Figure 17: New proposed cooling architectures                             | 96       |

| Figure 18: Cost and power efficiencies for the two unified designs        | 105      |

# **List of Tables**

|    | Table 1: Simulation parameters and descriptions of workloads and traces            | . 41 |

|----|------------------------------------------------------------------------------------|------|

|    | Table 2: Details of the new benchmark suite representing internet sector workloads | . 82 |

|    | Table 3: Individual cost and power models components for two classes of servers    | . 86 |

|    | Table 4: Summary of systems considered                                             | . 91 |

|    | Table 5: Summary of benefits from using low-cost low-power CPUs from non-sec       | rver |

| ma | ırkets                                                                             | . 93 |

|    | Table 6: Memory sharing architecture and results.                                  | 100  |

|    | Table 7: Low-power disks with flash disk caches.                                   | 103  |

Abstract

Disaggregated Memory Architectures for Blade Servers

by

Kevin Te-Ming Lim

Co-Chairs: Trevor N. Mudge and Steven K. Reinhardt

Current trends in memory capacity and power in servers indicate the need for memory

system redesign. First, memory capacity is projected to grow at a smaller rate relative to

the growth in compute capacity, leading to a potential memory capacity wall in future

systems. Furthermore, per-server memory demands are increasing due to large-memory

applications, virtual machine consolidation, and bigger operating system footprints. The

large amount of memory required for these applications is leading to memory power

being a substantial and growing portion of server power budgets. As these capacity and

power trends continue, a new memory architecture is needed that provides increased

capacity and maximize resource efficiency.

This thesis presents the design of a disaggregated memory architecture for blade

servers that provides expanded memory capacity as well as dynamic capacity sharing

ix

across multiple servers. Unlike traditional architectures that co-locate compute and memory resources, the proposed design disaggregates a portion of the servers' memory, which is then assembled in separate memory blades optimized for both capacity and power usage. The servers access memory blades through a redesigned memory hierarchy that is extended to include a remote level that augments local memory. Through the shared interconnect of blade enclosures, multiple compute blades can connect to a single memory blade and dynamically share its capacity. This sharing increases resource efficiency by taking advantage of the differing memory utilization patterns of the compute blades. In this thesis, two system architectures are evaluated that provide operating system-transparent access to the memory blade; one uses virtualization and a commodity-based interconnect, and the other uses minor hardware additions and a highspeed interconnect. Both are able to offer up to ten times higher performance over memory-constrained environments. Finally, by extending the principles of disaggregation to both compute and memory resources, new server architectures are proposed that provide substantial performance-per-cost benefits for large-scale data centers over traditional servers.

## **Chapter 1**

#### Introduction

Current hardware and software trends indicate an impending memory capacity wall that is hindering the full utilization of per-server compute resources. Compute capacity is growing at a fast rate due to the increasing number of central processing unit (CPU) cores per chip. Designs from AMD and Intel will have as many as 8 CPU cores per chip in the near future, and these numbers are expected to continue to increase [9]. To effectively utilize this growing compute capacity, there needs to be a matching increase of memory capacity. Further increasing the pressure on capacity, memory requirements of applications and operating systems are rising, with examples including in-memory databases, search engine indices, OS footprint growth, and virtual machine consolidation [15]. These combined trends require increased scaling in memory capacity in order to meet hardware and software demands. However, aggregate projections of memory capacity growth per CPU socket show that capacity is unable to keep up with these demands [86]. Memory is already one of the most important resources in servers, and left unchecked, the impending memory capacity wall will lead to future systems being underutilized due to lack of memory capacity.

Concurrently, the memory system is becoming a larger contributor to total server power and costs [29] due to the high operating speeds of memory and large memory

capacities that must be provisioned for expected workload requirements. This problem is magnified by the many servers in large scale data centers. In recent years, data centers have grown in size and importance to the computer industry [11, 68]. One of the primary factors of their growth is the emergence of the internet sector, especially in large-scale applications such as web search. These sectors have data centers that scale up to thousands of servers, as evidenced by companies such as Google and Microsoft having hundreds of thousands of servers spread across several globally distributed locations [35]. At this scale, the power and cost efficiency of servers is closely linked to total operating costs. The large contribution of memory system to both power and costs therefore makes it critical to have highly efficient and well utilized memory resources in servers across the entire data center.

This thesis examines the dual needs of addressing the memory capacity wall and having power and cost-efficient memory resources in large-scale environments. Given these needs, it is apparent that new memory architectures are required that can provide expanded memory capacity and more efficient memory resources. Due to their targeted use in large-scale environments, these architectures must be designed to exploit the economies of scale, taking advantage of the lower costs of high-volume components while minimizing the use of custom components. At the same time, when designing these memory systems, there are new opportunities to significantly improve their effectiveness. One such opportunity is optimizing for the *ensemble*, which refers to a group of closely located servers. When viewed at an ensemble level, there is time-varying, differing memory usage across servers due to different applications and workload inputs. This variability can be leveraged to provision resources for the expected sum of memory usage

across the ensemble, as opposed to the current standard practice of provisioning each server for the expected worst case memory usage. Additionally, the increased prevalence of blade servers – with their fast, shared interconnection networks – and virtualization software – with its support for hardware indirection – offer unique opportunities for efficient memory architectures that provide shared, expanded capacity in an operating system and application-transparent fashion.

In this thesis, these unique opportunities are explored in order to design a new, disaggregated memory architecture. The concept of disaggregation is used to refer to the separation of a resource from its traditional location within a compute server, and the assembly and use of that resource in such a way that promotes utilization and cost efficiency across the ensemble. Specifically I consider, separating a portion of the memory resources from compute servers, and organizing that memory in a cost and power-efficient manner that allows their utilization to be maximized across all of the servers. These memory resources are assembled in a specially designed memory blade that provides remote, expanded capacity to compute blades within an enclosure. The memory blade's capacity is dynamically allocated among the connected compute blades. The memory blade and two system architecture designs to access the blade are evaluated and are shown to effectively meet the goals of expanding capacity along with improving cost and power efficiency. Finally the principles of disaggregation are applied at a broader scale, and new server architectures are proposed for large-scale data centers that offer substantial performance and cost benefits over conventional servers.

Before discussing the disaggregated architectures in detail, a closer examination of the current memory capacity and power trends, new opportunities for memory system efficiency, and current work must be considered.

## 1.1 Memory Capacity Trends

In recent years, memory capacity has become a crucial yet limited resource in commodity systems. On the capacity demand side, current studies project an increased number of cores per socket, with some studies predicting a two-fold increase every two years [9]. As the number of cores per socket increases, the memory requirement to effectively utilize all of those cores also scales. Applications are requiring increasing amounts of memory capacity to deal with demands from web 2.0 applications, inmemory databases, and virtual machines [15]. Furthermore, operating systems are growing in memory footprint, with each successive generation of Windows requiring more memory [54]. However, from a *supply* point of view, memory capacity growth is unable to keep up. The International Technology Roadmap for Semiconductors (ITRS) estimates that the pin count at a socket level is likely to remain constant [86]. As a result, the number of channels per socket is expected to be near-constant. In addition, the rate of growth in dual in-line memory module (DIMM) density is starting to wane, growing at a rate of two-fold every three years versus the previous rate of two-fold every two years. Additionally the DIMM count per channel is declining (e.g., two DIMMs per channel on Double Data Rate 3 (DDR3) interfaces versus eight for DDR1 interfaces) [42]. Figure 1 aggregates these trends to show historical and extrapolated increases in processor computation and associated memory capacity. The processor line shows the projected trend of cores per socket, while the dynamic random access memory (DRAM) line shows

Figure 1: Projected annual growth in number of cores and memory capacity.

The expected number of cores per socket (blue line) is growing at a faster rate than the expected DRAM capacity (orange line). On average, memory capacity per processor core is extrapolated to decrease 30% every two years.

the projected trend of capacity per socket given DRAM density growth and DIMM per channel decline. If these trends continue, the growing imbalance between supply and demand may lead to commodity memory capacity per core dropping by 30% every two years. If not addressed, future systems are likely to be performance-limited by inadequate memory capacity.

At the same time, several studies show the contribution of memory to the total cost and power consumption of future systems increasing from its current value of about 25% [56, 67, 61]. A survey of memory costs of differing technology types and capacities, discussed in greater detail in Chapter 6, shows that the costs of higher speed, higher capacity memory can easily rival the cost of the processor. New generations of memory reduce power consumption, but these reductions are offset by the faster operating frequencies and the larger memory capacities that are being used. Furthermore, certain

Figure 2: Intra- and inter-server variations in memory utilization.

(a) The amount of granted memory for TPC-H queries can vary by orders of magnitude. Note the memory usage is on a log sacle. (b) "Ensemble" memory usage trends over one month across 11 servers from a cluster used for animation rendering. Note the variability in utilization across the servers at any given time point.

recent memory technologies such as Fully-Buffered DIMMs (FB-DIMM) require additional hardware that increases power consumption [36]. As memory power trends higher, it will increase ownership costs as more energy will be required to adequately cool the servers.

There are new technologies emerging to improve memory capacity, including the use of alternative memory technologies such as Flash [94] or Phase Change Memory [57] as main memory, 3D stacked DRAM [51], and buffers [4] or ASICs [20] to increase the allowable DIMMs per memory channel. These technologies are all promising in increasing memory capacity, but each has different drawbacks, including asynchronous

read/write performance, lifetime wear-out concerns, configuration flexibility, and non-commodity costs. Despite these alternatives, DRAM currently remains the primary option for main memory capacity.

## 1.2 Heterogeneity Opportunities in Enterprise Workloads

These challenges in memory capacity and power present a unique opportunity for research and development. Recent studies have pointed to a new possibility to address these challenges—namely that of optimizing for the ensemble [75], referring to a group servers physically located near each other. For example, several studies have shown that there is significant temporal variation in the usage of resources like CPU time or power, both across and within applications. There are analogous trends in memory usage based on variations across application types, workload inputs, data characteristics, and traffic patterns. Figure 2(a) shows how the memory allocated for queries by a standard transaction processing benchmark, TPC-H, can vary widely. There are several orders of magnitude difference in memory allocated between the smallest and largest queries, demonstrating the large memory variations within an application. Figure 2(b) presents a high-level illustration of the time-varying memory usage of 11 randomly-chosen servers from a 1,000-CPU cluster used to render a recent animated feature film [1]. Each line illustrates a server's memory usage varying from a low baseline when idle to the peak memory usage of the application. As can be seen, there is variation in the memory usage across all servers at any time. These results point to the opportunity for a solution that provisions server memory for the typical usage, with the ability to dynamically add memory capacity across the ensemble. This solution can reduce costs and power by

avoiding the over provisioning that results from allocating each system for its worst-case memory usage.

#### 1.3 Blade Servers

One solution for addressing resource efficiency for servers has been the blade server environment. In such an environment, individual servers are in a "blade" form-factor, which is smaller than its 1U or 2U counterparts by excluding components such as fans, power supplies, and I/O devices. Instead these blades plug into an enclosure which provides shared resources for those excluded components and other features such as network switches. By sharing resources, blade systems are able to be more efficient than traditional servers; for example, fans and power supplies can be sized for and operate in more efficient ranges. Because they are targeted towards enterprise environments, blade servers typically have support for management processors that allow remote control over server hardware and power settings. Additionally, blade vendors often include or support virtualization software to provide greater flexibility and control over the operating systems being run. By offering improved resource efficiency through sharing resources, blade servers offer unique possibilities for new memory system designs that address the previously discussed power and capacity concerns.

#### 1.4 Thesis Statement

To address the issues arising from memory capacity and power trends, this thesis explores new memory architectures that utilize the opportunities presented by ensemble-level optimizations and blade server infrastructures. Specifically this thesis presents the design and evaluation of a *disaggregated* memory architecture that is inspired by

reassessing traditional memory systems which co-locate compute and memory resources. Instead, a portion of memory resources are separated from servers and are organized in a shared, remote memory pool, and the servers' memory hierarchies are extended to include a remote memory level. This pool, provided through a capacity-optimized *memory blade*, is shared among compute servers within an enclosure to provide dynamic memory capacity allocation. Compared to the state of the art, the memory blade is unique in enabling both capacity expansion as well as dynamic capacity sharing. Importantly, the disaggregated architecture leverages both the shared, high-speed interconnects found in blade systems, as well as the dynamic variations in workload memory requirements. Through memory blade-specific power optimizations, and by right-provisioning memory capacity at an ensemble level, disaggregated memory can address the power and cost problems that plague current servers. By amortizing the memory blade costs across multiple servers in addition to its other benefits, the architecture offers significant cost advantages over state of the art techniques that only expand capacity for a single server.

This thesis evaluates two system architectures that provide access to the memory blade and provide operating system-transparent capacity expansion. The first design requires changes only in hardware, while the second design limits changes to only the software layer. The memory blade and these two architectures are evaluated through simulation across a range of workloads, as well as on utilization traces across multiple live-data centers, and are shown to provide on average a 10 fold performance improvement compared to a memory constrained baseline. To further elucidate the software requirements, a software-based prototype of disaggregated memory is developed by modifying the Xen hypervisor, an open-source software project. This prototype is used to

validate some of the previous simulation findings, and its development leads to several interesting insights into the software-aspects of disaggregated memory.

Finally, disaggregated memory is used as a cornerstone for a more advanced server architecture which uses compute disaggregation, optimized cooling and packaging, and low-power storage alternatives. These new server architectures are designed and evaluated for large-scale data centers, specifically warehouse-computing environments, and are found to provide significantly higher performance per cost efficiency compared to traditional servers.

#### 1.5 Contributions

This thesis makes the following contributions:

- Identification of memory capacity and power as system-limiting factors in future servers

- Design of a disaggregated memory architecture for blade systems, providing an expanded and shared remote memory capacity

- Evaluation using simulation of two implementations of disaggregated memory that focus on either hardware or software changes

- Development and evaluation of a software-based prototype of disaggregated memory using the Xen hypervisor

- Design of new disaggregation-based server architectures that leverage low power components, redesigned packaging, and disaggregated memory

- Evaluations demonstrating the effectiveness of the server architectures on novel,

warehouse-computing oriented workloads

## 1.6 Organization

The rest of the thesis is organized as follows: Chapter 2 contains background on many of the key concepts that are central to this work, including current memory architectures, servers, and blade systems. Chapter 3 discusses the disaggregated memory architecture, covering the design of the memory blade, and two system architectures that are used to access the memory blade. This architecture is evaluated, primarily through simulation, in Chapter 4. The development of the software-based prototype of disaggregated memory is covered in Chapter 5. Chapter 6 explores the evolution of disaggregated memory to disaggregated server architectures and evaluates these architectures on novel, data center-oriented workloads. Chapter 7 discusses related work in the memory and server architecture space. Chapter 8 presents future work and Chapter 9 concludes the thesis.

#### Chapter 2

### **Background**

This chapter presents the background for several key topics, including main memory architectures, server designs and blade servers, and data centers. The motivation for this thesis is driven by the current limitations of main memory architectures in providing adequate memory capacity in the future, and rising demands for that memory capacity. At the same time, inefficiencies in server architectures and the emergence of the blade infrastructure offer new opportunities for improving the resource efficiency of both memory architectures and servers. Finally background on data centers and their growing importance to the computer industry is discussed. Based on growth of large-scale data centers, they will likely be a driver of server-class computer design in the near future.

## **2.1 Current Main Memory Architectures**

#### 2.1.1 Main Memory Architecture and DRAM

Commodity-class x86-based servers typically have one or two CPU sockets connected to a northbridge chipset, or memory controller hub. The northbridge is connected to several banks of dual in-line memory module (DIMMs) slots, and provides the communication between the CPU and the dynamic random access memory (DRAM) that is placed into the DIMM slots. In more recent processors, such as the AMD Opteron and

Phenom, and the Intel Core i7 and latest Xeon, the northbridge is integrated onto the processor die, thereby directly connecting the processor to the DIMM slots. The on-die northbridge configuration provides lower latency, faster access to the DRAM, but is conceptually very similar to the traditional design with a discrete northbridge. In these commodity x86 servers, the main memory consists solely of DRAM, which comes in several interfaces including double dynamic rate (DDR), DDR2, DDR3, and Fully-Buffered DIMM (FB-DIMM). Each successive DDR generation offers higher speed and all DDR types assume a parallel bus interconnect, while FB-DIMM assumes a serial point-to-point link. In addition, the successive DDR generations have supported increased DRAM densities and lower operating voltages, thereby reducing the power generated.

DDR interfaces use a parallel bus architecture that requires the processor's memory controller to be connected to all of the memory slots. Because of the electrical complexity involved in the parallel bus wiring, the bus architecture is a limiting factor in the total number of DRAM devices that can be connected, the density of those memories, and the transfer speed of the interconnect. Achieving higher memory capacity and faster speeds thus leads to expensive and complex electrical signaling. This electrical complexity is one factor why server-class motherboards — which typically offer a large memory capacity — cost a significant amount higher than traditional desktop-class motherboards.

#### 2.1.2 Recent Designs for Increased Capacity

The emergence of FB-DIMM was driven largely by the limitations of the traditional parallel bus memory architecture. FB-DIMM instead uses a serial, point-to-point link, requiring far fewer wires that run at a higher frequency. The high-speed serial interface allows more DIMMs to be connected to the processor and higher overall bandwidths. FB-

DIMM modules use DDR2-based DRAM devices to provide memory capacity, but have an additional chip on each module called an Advanced Memory Buffer (AMB). The AMB is responsible for reading the data from the DDR2 memory devices and converting it to the serial interface. However, there are drawbacks to FB-DIMM primarily due to the AMB chip, which is located on every DIMM. The first drawback is increased memory access latency due to converting the parallel DDR memory interface to the FB-DIMM serial interface. Because there is a large performance difference in memory speed and processor speed, for many applications memory latency can be one of the main factors in overall performance. The extra latency from FB-DIMM can thus result in slower performance compared to architectures using DDR interfaces. The second drawback is that the AMB draws a large amount of power [36]. Especially in servers with large memory capacities, where memory power can be quite high and even comparable to overall processor power, the power required for the AMB exacerbates the situation. Higher power consumption affects cost in terms of both higher power costs to run the systems, as well as higher cooling costs for the extra heat that is generated. Finally, the AMB itself adds to the cost of each of the DIMMs, resulting in higher prices than DDR DIMMs of comparable speed and capacity. The added costs reduce the usefulness of FB-DIMM for high-volume markets, such as large-scale data centers. Furthermore, the costs, high power, and increased latencies point to the inadequacies of FB-DIMM to fully address the memory capacity needs faced by current memory architectures.

Although FB-DIMM is unlikely to become a ubiquitous solution – for example, AMD announced it has no future plans to use FB-DIMM [23] – it does highlight several key needs for future memory architectures. First, memory latency is an important component

for overall performance, and new architectures should avoid increasing latency in the common or most frequent access paths. Second, new technologies are needed to expand memory capacity beyond the current limitations faced by the parallel bus architecture. As will be described in the next section, it is necessary to have more memory capacity to match the compute capacity that is increasing with the growth of multi-core processors. Finally, memory power is an important consideration, especially for server-class computers. Resources must be efficiently utilized to maximize the amount of work done per watt.

Beyond FB-DIMM, there have been several newly proposed memory technologies to attempt to increase memory capacity. AMD has announced a product called G3MX [4], which is similar to FB-DIMM, but instead places the buffer chip on the motherboard. This configuration avoids the cost and power overheads that are incurred by an AMB being on every FB-DIMM. However, this technology has not been introduced into the market as of 2010. It is unclear if there will be a high-volume market that will drive commoditization costs. Furthermore, including the buffers on the motherboard will increase motherboard costs.

Cisco has released an Extended Memory Blade server [20] which utilizes an ASIC plugged into a separate CPU socket to provide expanded capacity. The ASIC allows multiple DIMMs to be mapped into a single DIMM slot, surpassing the normal electrical limitations of standard processor memory channels. However, this architecture imposes non-commodity costs on all servers that require large memory, requires custom hardware and motherboard from Cisco, and is unlikely to reach high-volume markets.

Another technology is 3D stacked memory [51], which incorporates DRAM chips directly onto the processor die. This stacking can likely provide greater densities than is available with current DRAM, but like the other solutions incurs significant non-commodity costs. Additionally, the 3D stacked memory architecture could be more limiting in the possible memory configurations available if the only processor can only access the 3D stacked DRAM as main memory. This architecture would require a new processor model in order to obtain greater memory capacity, which would discourage high-volume markets that may have wide variety of memory capacity needs.

Although each of these solutions offer potential memory capacity increases, most offer only a one-time increase. In addition, they suffer from not being applicable to high-volume markets, making them inappropriate for cost-effective designs. The memory blade, on the other hand, minimizes the non-commodity parts and amortizes their costs across multiple servers, enabling cost-effective capacity expansion. Additional benefits are gained through dynamically sharing the memory blade capacity. Lastly, most of these technologies are orthogonal to the memory blade design, and can be utilized by the memory blade if commoditization drives their costs down.

#### 2.1.3 Distributed Shared Memory Architecture

A processor's memory controller is typically connected directly to the accessible DIMM slots. However, in a distributed shared memory (DSM) system, multiple processors are connected to each other using a coherent interconnect, and processors can address other processors' memory in a single global, unified address space. Server-class processors such as the AMD Opteron and Intel Xeon support DSM through a multi-socket architecture, in which a single motherboard has two or more processor sockets

connected by a coherent interconnect. These configurations are known as symmetric multiprocessing (SMP), where several identical processors share main memory. Most systems are limited to 4 sockets [23], but with additional circuitry and logic, much larger systems can be created, such as those historically offered by SGI [55]. In a DSM system, when a processor must access another processor's memory, the original processor generates a memory request. The memory request is sent to the processor connected to the memory, which completes the request on behalf of the original processor and returns the data. Memory contents across the different memories, as well as the caches of the processors, are kept up-to-date using a coherency protocol.

Distributed shared memory systems can provide a larger memory capacity than is possible with a single processor socket by sharing the memory of several processors. However, there are several drawbacks to increasing capacity by using a DSM system. First, latency to access another processor's memory is higher than accessing local memory because the request must traverse sockets to the other processor, and must take part in the coherency protocol to get the proper data. The increased latency has motivated the development of multiple schemes that utilize either hardware or software to minimize the latency. Second, multi-processor motherboards cost more than single-processor motherboards due to their extra materials, complex electrical wiring required, and lower-volume market. Thus DSM systems can be a costly way to obtain greater memory capacity. Lastly, although DSM systems increase the total memory capacity, the capacity-per-socket ratio, or compute-to-memory ratio, is not changed. Because the compute-to-memory ratio is unchanged, although DSM systems will alleviate situations where the performance is memory capacity-bound, they will not address situations where each of

the processors requires more capacity. Such situations will continue to have underutilized compute resources.

### 2.2 Software Needs for Memory Capacity

To understand the needs for large memory capacities, current software resource demands must be examined. Due to the large gap between processor performance and disk performance, applications rely on main memory capacity to store and retrieve data with high performance. The reliance on main memory is especially true with the rise of latency-sensitive applications specifically in the internet sector. There has been an emergence of data-rich, highly interactive "web 2.0" applications where low latency, on the millisecond timescale for user response, is extremely important to overall user experience, and thus crucial to end metrics such as total number of visitors to a website, or total number of order transactions. To support these applications – which are as widely varied as web search, social networking, blogs, and real-time chat – there has been significant effort to ensure they maximize the use of main memory and minimize the accessing of data from disk. These performance optimizations are evidenced by efforts of Google and Yahoo! to specifically make their web search indexes fit into main memory, and the wide-spread use of a main memory based caching layer, memcached [32], in infrastructures such as Facebook or LiveJournal. In particular, memcached works by having a distributed cache that utilizes the main memory of servers to cache objects, such as the results of a database query or a page rendering. The servers running memcached can be standard servers running applications such as web search, or can be dedicated caching servers. In large-scale infrastructures, there may be hundreds of computers dedicated to being memcached servers to provide high performance, and more

importantly, fast response times. As web 2.0 infrastructures continue to grow and scale out, they will be one of the largest driving factors behind the need for greater memory capacity.

Similarly, there is also a growth in memory capacity demand in the database segment. Database management systems (DBMS) are seeing an increase in in-memory database systems (IMDS), which store an entire database in main memory [48]. This configuration is contrary to traditional DBMS, which store databases on disk. Significantly higher performance can be achieved by having the entire database in main memory because memory is an order of magnitude faster to access than disk both in terms of latency and bandwidth. This performance improvement is beyond what is achievable by caching a traditional disk-based DBMS in memory. Caching can speed up accesses to read objects by storing them in memory, but writing objects still pays the performance overhead of accessing the disk. Furthermore, IMDS are optimized to operate within memory, and avoid some of the overheads that disk-based DBMS have in maintaining data on disk.

Another key driver of memory capacity needs is virtualization software. Virtualization is increasingly being used to provide consolidation of servers in data centers. Virtualization enables software implementations of full-machines, called virtual machines (VM), to be used in place of individual servers. Virtualization provides each VM the appearance of being its own machine through the use of a virtual machine monitor (VMM), or hypervisor. The hypervisor is a small layer of software that abstracts the underlying system's physical hardware in a manner that enables the VMs to be agnostic to actual hardware. This abstraction allows VMs to run (in the ideal case) on any hardware that is supported by the hypervisor without needing reconfiguration. Moreover,

it allows multiple VMs to share a single machine by multiplexing the hardware at the hypervisor level. Operating systems typically expect to have full and sole control of the server's hardware, and thus servers normally only run a single operating system. Through the support and indirection of the hypervisor, virtualization can surpass this limitation and allow multiple operating systems to run simultaneously; for example, one VM can be running Windows XP, another VM can be running Debian Linux, and yet another could be running Red Hat Linux, all at the same time.

This ability to run multiple operating systems is especially useful for servers in data centers. Often times such servers are utilized only lightly, but cannot be consolidated because they are running applications that require separate servers. This limitation may be either due to compatibility reasons (e.g., one application needs Windows Server, and another needs Linux), application requirements, or security reasons (e.g., isolation). Without virtualization, each instance of these applications would require their own server, which comes with the costs of purchasing, running, and managing that server. With virtual machines, each of those applications can be run in a separate VM, and those VMs can be consolidated onto a single server, assuming it has enough compute, memory, and storage resources. Virtual machine consolidation can greatly reduce the amount of running servers required in a data center, especially when the servers are not consistently under heavy utilization. Furthermore, the appearance of VMs as full systems can help ease implementation of services. For example, in Amazon's Elastic Compute Cloud [84], VMs give the users "full" systems which can be used for individual purposes. Unfortunately, when consolidating virtual machines, memory capacity can be a bottleneck preventing further consolidation, especially for virtual machines with low

levels of processor utilization. Consolidated VMs require the server have memory capacity to hold the entirety of their memory; thereby the consolidation of multiple VMs onto a single server greatly increases the memory resource pressure on that server. Thus in these VM environments, it is very important to have a large memory capacity to support the high levels of consolidation.

As discussed in this section, there are multiple software trends driving the need for increased memory resources – specifically memory capacity. Applications and software such as web 2.0, in-memory databases, and virtualization all require large memory capacities to achieve high overall system performance. As applications with large main memory requirements continue to become more prevalent, it will be important that new memory architectures are able to supply them with adequate capacity and resources.

### 2.3 Servers and Blade Systems

Server infrastructures are undergoing a design evolution that seeks to increase their efficiency and reduce costs, while also providing maximum flexibility. Blade servers are a prime example of such an evolution. To understand the need behind the design evolution, some background information on commodity-class servers must be reviewed. Servers found in data centers typically come in form-factors of 1U or 2U, which refers to their vertical height being 1.75" or 3.5", respectively. These servers are rack mounted, in which they are connected to a standardized chassis that measures 19" wide. Typical racks are 42U tall, allowing twenty-one to forty-two servers per standard rack. There are more advanced designs that allow mounting of servers on both the front and back of the rack, thereby doubling the number of servers per rack. A 1U or 2U server contains all traditional computer components, including motherboard, processor, RAM, I/O devices

such as Ethernet network interface cards (NICs), and typically one or more hard drives. Also included are one or more power supplies (if more are needed for redundancy) and cooling fans to pull cold air from outside of the server, pass the air over the components, and exhaust the air out the other side. 1U servers are traditionally single or dual-socket systems, and are often the mainstay of large-scale data centers for their combination of cost, size, compute power, and flexibility. 2U servers offer more capacity for components, such as quad-socket systems, or multiple disk drives.

Blade systems are intended to improve upon the design of servers by offering greater flexibility in form-factor and configuration, and reducing the redundant resources among groups of servers. Instead of requiring servers to be a 1U or 2U form-factor, individual blade servers, or compute blades, plug into a rack-mounted enclosure, allowing a greater flexibility in form-factor and arrangement. The flexibility allows blade servers to better match the configurations and arrangements needed by applications while requiring less real estate than traditional 1U servers. For example, the HP c-Class blade system has an enclosure that has a 10U form factor and can support up to 16 servers per enclosure. Blade infrastructures that are focused on server density, such as the HP Blade PC, can have up to 20 blade servers per 3U. Blade systems often provide modularity in the type of blades that can be used. The server, or compute blade, is the most common form, but there can also be storage blades that contain disks, and I/O blades that contain I/O adapter cards such as graphics cards or networking cards. The blade enclosure contains a backplane that has electrical connectors that the blades physically plug into. Additionally the backplane provides resources such as power and interconnect (e.g., Ethernet and PCI Express). Blade servers are an important market segment for major companies such as

HP, Dell, IBM, and Sun. Because they are targeted towards enterprises, they often include advanced manageability features such as on-board management processors and power and cooling control, as well as reliability features such as redundant power supplies, fans, and networking.

Beyond having a more flexible form-factor, one of the key improvements of blade systems over traditional servers is having a shared infrastructure. Traditional rack-mounted servers are isolated and each one has its own individual components. For example, each server has a power supply, cooling fans, and networking hardware. However, this isolation and redundancy can be wasteful – the power supplies are often forced to run in less efficient ranges of operation if servers are lightly utilized; cooling fans are forced to be smaller, less efficient form-factors to fit in a 1U or 2U case, and may be underutilized depending on the activity level of the servers. Blade systems address these inefficiencies by providing power, cooling, and integrated networking resources at the enclosure level. This resource sharing allows for cooling fans to be larger and more efficient and the power supplies to be run at more efficient operating ranges (i.e., high utilization) by taking advantage of the varying utilization profiles of the compute blades [58]. Additionally, the cost of the components is amortized across all of the compute blades that populate the enclosure.

#### 2.4 Data Centers

Companies use data centers to house and run their large collections of servers. These data centers are buildings that have dedicated capacity to house, power, cool, and manage the servers. There has been significant growth in the data center segment, driven by the internet sector and cloud computing. Internet companies such as Microsoft, Google, and

Yahoo! have invested millions of dollars in purchasing land, building, and running data centers, and continue to expand their capacity [93]. Similarly, there has been an emergence of *cloud computing*, in which third-party companies manage servers and infrastructure, and sell compute time and capacity to end users. The actual details of the infrastructure and management can be abstracted away from the end users, allowing them to focus only on the actual workloads being run. Cloud computing benefits the end users by allowing them to use as much compute power as necessary; as the users' applications require more processing power, more compute resources can be utilized from the cloud on an on-demand basis. With the emergence of cloud computing companies such as Amazon have dedicated large amounts of compute resources and are continually expanding their data centers. The large scale internet sector and cloud computing data centers all have unique requirements compared to smaller deployments, and house thousands of servers running a variety of core applications or services such as web servers, web search, e-mail, and job schedulers. Due to this massive scale, efficiency at all levels of operation is very important. For example, millions of dollars have been invested in the development of power-efficient data centers that are optimized to maximize cooling effectiveness and minimize power losses. Some recent data centers are being built in colder climates to take advantage of ambient external air cooling; other data centers have been built near power sources such as dams to provide cheap electricity [63].

Because of the enormous scale of these data centers, for the design of domain-specific architectures can be feasible and cost-effective. Both Google and Yahoo! have their own optimized server enclosures [85]. Furthermore, companies have put millions of dollars

into designing unique cooling infrastructures. There have also been efforts by Microsoft and Google in using shipping containers to house servers, providing a flexible and cost-effective building unit for data centers [35]. Based on the millions of dollars being put forth towards these efforts, and the sheer scale of these data centers, domain-specific architectures that offer significant power or cost advantages can be quite feasible.

## Chapter 3

# **Disaggregated Memory Architecture**

In order to address the memory capacity and power problems discussed previously, new architectural solutions are needed that can provide both transparent memory capacity expansion to match computational scaling, and transparent memory sharing at the ensemble level. In addition, given the large-scale data centers that these architectural solutions are targeted towards, it is important for these approaches to require at most minor changes to ensure that their costs do not outweigh their benefits. When considering the design of new memory architectures, blades servers offer an interesting platform due to their fast, shared interconnection networks and support of virtualization software. The increased market adoption of blade servers helps make them a viable platform for new memory architectures.

This thesis proposes a new architectural building block, a *memory blade*, which provides transparent memory expansion and sharing for commodity-based designs. The design of the memory blade is discussed in this chapter, and the memory blade is used to propose two new *disaggregated memory* architectures. Both architectures augment the memory hierarchy with a remote memory level whose capacity is provided by the memory blade. The first solution requires no changes to existing system hardware, using support at the virtualization layer to provide page-level access to a memory blade across a

commodity interconnect. My second solution proposes minimal hardware support on every compute blade, but provides finer-grained access to a memory blade across a coherent network fabric for commodity software stacks.

## 3.1 Disaggregated Memory Concept

There are four key observations that motivate the development of disaggregated memory:

- (1) The emergence of blade servers with fast shared communication fabrics in the enclosure enables separate blades to share resources across the ensemble.

- (2) Virtualization provides a level of indirection that can enable OS- and application-transparent memory capacity changes on demand.

- (3) Market trends towards commodity-based solutions require special-purpose support to be limited to the non-volume components of the solution.

- (4) The footprints of enterprise workloads vary across applications and over time; but current approaches to memory system design fail to leverage these variations, resorting instead to worst-case provisioning.

Based on these observations, this thesis argues for a re-examination of conventional designs that co-locate memory DIMMs in conjunction with computation resources. These designs connect DIMMs through conventional memory interfaces and the processor controls them through on-chip memory controllers. Instead, this thesis proposes a *disaggregated multi-level design* which provisions a separate memory blade, connected at the I/O or communication bus. The concept of disaggregation refers to the separation of memory from its location within the compute blade, and the use of that memory in a way

that promotes resource and cost efficiency across the ensemble. In this design, a portion of the memory resources are separated from the compute blades within an enclosure, and this memory is organized on a memory blade to maximize the efficiency across the whole ensemble. Thus the memory blade comprises arrays of commodity memory modules assembled to maximize density and cost-effectiveness. Importantly, the memory blade provides an extra, remote memory capacity to the compute blades. The memory hierarchy is reorganized to support this remote level in an operating system-transparent fashion through either modifications at the hypervisor level, or minor hardware changes. Furthermore, the memory blade takes advantage of varying memory requirements by allocating capacity on-demand to individual compute blades, allowing for more efficient overall utilization of memory.

# 3.2 Memory Blade Architecture

#### 3.2.1 Memory Blade Design

The design of the memory blade is illustrated in Figure 3(a). The memory blade consists of a protocol engine, an interface bridge, a custom memory-controller ASIC (or a light-weight CPU), and one or more channels of commodity DIMM modules. The protocol engine and interface bridge are used to interface with the blade enclosure's I/O backplane interconnect, providing connectivity to multiple compute blades. The custom memory-controller handles requests from client blades to read and write memory, using standard virtual memory techniques to translate the requested memory addresses to their actual locations on the memory blade. Additionally the controller manages capacity allocation and address mapping across the connected compute blades. The memory blade's channels of DIMM modules use either on-board repeater buffers or alternate fan-

out techniques to allow each memory channel to support a high capacity. Optional memory-side accelerators can be added for functions like compression and encryption. The memory blade can either be designed as another blade in the system – supporting the same form factor as the compute blades – or could alternatively be designed to fit into the I/O bays typically found in blade enclosures. The former design would provide more physical space for DIMMs, while the latter design would avoid replacing any compute blades. In this thesis I assume the latter design, where the memory blade is situated in the I/O bay to maximize the amount of compute capacity per enclosure.

The memory blade requires some custom hardware, including the memory-controller ASIC, the memory channels, and the motherboard. Although this custom hardware is contrary to the goal of avoiding non-commodity components, the memory blade requires no changes to volume blade-server designs, as it connects through standard I/O interfaces. In this thesis PCI Express® (PCIe®) or HyperTransport<sup>TM</sup> (HT<sup>TM</sup>) are used as the I/O interconnect. Additionally, because the memory blade's capacity is available to all servers in the enclosure, its total costs are amortized over the entire server ensemble. Furthermore, the memory blade design is straightforward compared to a typical server blade, as it does not have the cooling challenges of a high-performance CPU and does not require local disk, Ethernet capability, or other elements (e.g., management processor, SuperIO, etc.). The simple design should minimize the cost of the custom hardware. To further offset hardware costs, the memory blade's DRAM subsystem is optimized for power and capacity efficiency. Because client access latency is dominated by the enclosure interconnect, resource efficiency optimizations are possible at the minor cost of performance. For example, the controller can aggressively place DRAM pages into active

Figure 3: Design of the memory blade.

(a) The memory blade architecture is shown in detail. The memory blade connects to the compute blades via the enclosure backplane. (b) The address mapping data structures that support memory access and allocation/revocation operations.

power-down mode, which reduces memory power by almost 90%, but takes an extra 6 DRAM cycles to transition into standby mode [64]. The controller can also map consecutive cache blocks into a single memory bank to minimize the number of active devices at the expense of reduced single-client bandwidth.

The design of the memory blade reflects deliberate choices to make a straightforward design that would fit well in the commodity-based markets, but is by no means the only feasible way a memory blade could be designed. The memory blade could possibly have greater compute power than an ASIC, making it closer to a large-memory server. This design was not pursued in favor of simplicity as it would require greater complexity in

the programming of the memory blade and its interactions with the compute blades. Although the memory blade uses either PCIe or HT, nothing precludes it from using other interconnects such as Infiniband® or QuickPath Interconnect. A memory blade could also serve as a vehicle for integrating alternative memory technologies, such as Flash or phase-change memory, possibly in a heterogeneous combination with DRAM, without requiring modification to the compute blades. This configuration would need more logic at the memory controller to communicate with the different memory types, as well as policies for using one memory technology versus another, but the added design complexity may be outweighed by the benefits from alternative memory technologies. Many of these alternative designs are discussed in Chapter 8.

#### 3.2.2 Memory Blade Mapping

The memory blade is designed to be shared by multiple compute blades. To provide protection and isolation among shared clients, the memory controller translates each memory address accessed by a client blade into an address local to the memory blade, called the Remote Machine Memory Address (RMMA). In the proposed design, each client manages both local and remote physical memory within a single System Memory Address (SMA) space. Local physical memory resides at the bottom of this space, with remote memory mapped at higher addresses. For example, if a blade has 2 GB of local DRAM and has been assigned 6 GB of remote capacity, its total SMA space extends from 0 to 8 GB. Each blade's remote SMA space is mapped to a disjoint portion of the RMMA space. This process is illustrated in Figure 3(b). The blade's memory is managed in large chunks (e.g., 16 MB) so that the entire mapping table can be kept in SRAM on the memory blade's controller. For example, a 512 GB memory blade managed in 16 MB

chunks requires only a 32,000 entry mapping table. Using these "superpage" mappings avoids complex, high-latency DRAM page table data structures and custom translation lookaside buffer (TLB) hardware. This architecture does not preclude shared-memory communication among client blades, but in favor of a simplistic solution, it is not included in this initial design. The implications of supporting distributed shared memory are discussed in Chapter 8.

## 3.2.3 Remote Memory Allocation and Revocation

The memory blade's total capacity is partitioned among the connected clients through the cooperation of the virtual machine monitors (VMMs) running on the client servers, in conjunction with enclosure-, rack-, or datacenter-level management software. The VMMs in turn are responsible for allocating remote memory among the virtual machine(s) (VMs) running on each client system. The selection of capacity allocation policies, both among blades in an enclosure and among VMs on a blade, is a broad topic that deserves separate study. Here the discussion is restricted to designing the mechanisms for allocation and revocation.

Allocation is straightforward: privileged management software on the memory blade assigns one or more unused memory blade superpages to a client, and sets up a mapping from the chosen blade ID and SMA range to the appropriate RMMA range. Revocation is required when there are no unused superpages, and some existing mapping must be revoked so that memory can be reallocated. Capacity reallocation is a rare event compared to the frequency of accessing memory using reads and writes. Consequently, the design focuses primarily on correctness and transparency and not performance.

When a client is allocated memory on a fully subscribed memory blade, management software first decides which other clients must give up capacity, then notifies the VMMs on those clients of the amount of remote memory they must release. There are two possible approaches for freeing pages. First, most VMMs already provide paging support to allow a set of VMs to oversubscribe local memory. This paging mechanism can be invoked to evict local or remote pages. When a remote page is to be swapped out, it is first transferred temporarily to an empty local frame and then paged to disk. The remote page freed by this transfer is released for reassignment. Alternatively, many VMMs provide a "balloon driver" [95] within the guest OS to allocate and pin memory pages, which are then returned to the VMM. The balloon driver increases memory pressure within the guest OS by requesting memory, forcing the OS to select pages for eviction to satisfy the driver's request. This approach generally provides better results than the VMM's paging mechanisms, as the guest OS can make a more informed decision about which pages to page out to disk and may simply discard clean pages without writing them to disk. Because the newly freed physical pages can be dispersed across both the local and remote SMA ranges, the VMM may need to relocate pages within the SMA space to free a contiguous 16 MB remote superpage.

Once the VMMs have released their remote pages, the memory blade mapping tables may be updated to reflect the new allocation. It is assumed that the VMMs can generally be trusted to release memory on request; the unlikely failure of a VMM to release memory promptly indicates a serious error and can be resolved by rebooting the client blade.

## 3.3 System Architecture with Memory Blades

While the memory-blade design enables several alternative disaggregated memory architectures, two specific designs are discussed here, one based on making changes only at the software stack, and another based on requiring only minor hardware changes. Based on their implementation differences, the first design uses page swapping on remote access, while the second design provides fine-grained remote access. In addition to providing more detailed examples of possible disaggregated memory architectures, these designs also illustrate some of the tradeoffs in the multi-dimensional design space for memory blades. Most importantly, they compare the method and granularity of access to the remote blade (page-based versus block-based) and the interconnect fabric used for communication (PCI Express versus HyperTransport).

## 3.3.1 Page-Swapping Remote Memory (PS)

The first design avoids any hardware changes to the high-volume compute blades or enclosure; the memory blade itself is the only non-standard component. This constraint implies a conventional I/O backplane interconnect, typically PCIe. This basic design is illustrated in Figure 4(a).

Because CPUs in a conventional system cannot access cacheable memory across a PCIe connection, the system must bring locations into the client blade's local physical memory before they can be accessed. The Page-Swapping (PS) design leverages standard virtual memory mechanisms to detect accesses to remote memory and relocate the targeted locations to local memory on a page granularity. In addition to enabling the use of virtual memory support, page-based transfers exploit locality in the client's access stream and amortize the overhead of PCIe memory transfers. To avoid modifications to

Figure 4: Page-Swapping (PS) Remote Memory Design.

(a) Disaggregated architecture that connects the compute and memory blades using a commodity interconnect. No changes are required to compute servers and networking on existing blade designs. Minor modules (shaded block) are added to the virtualization layer. (b) The address mapping design places the extended capacity at the top of the address space. In this example 2-8GB are remote memory.

application and OS software, this page management is implemented in the hypervisor or VMM. The VMM detects accesses to remote data pages and swaps those data pages to local memory before allowing a load or store to proceed.

The new page management scheme is illustrated in Figure 4(b). As mentioned previously, when remote memory capacity is assigned to a specific blade, the SMA (machine physical address) space is extended at that blade to provide local addresses for the additional memory. The VMM assigns pages from this additional address space to

guest VMs, where they will in turn be assigned to the guest OS or to the applications. However, because these pages cannot be accessed directly by the CPU, the VMM cannot set up valid page-table entries for these addresses. It instead tracks the pages by using "poisoned" page table entries without their valid bits set or by tracking the mappings outside of the page tables (similar techniques have been used to prototype hybrid memory in VMWare [98]). In either case, a direct CPU access to remote memory will cause a page fault and trap into the VMM. On such a trap, the VMM initiates a page swap operation. This simple OS-transparent memory-to-memory page swap should not be confused with OS-based virtual memory swapping (paging to swap space), which is orders of magnitude slower and involves an entirely different set of sophisticated data structures and algorithms.

The PS design assumes page swapping is performed on a 4 KB granularity, a common page size used by operating systems. Page swaps logically appear to the VMM as a swap from high SMA addresses (beyond the end of local memory) to low addresses (within local memory). To decouple the swap of a remote page to local memory and eviction of a local page to remote memory, a pool of free local pages is maintained for incoming swaps. The software fault handler thus allocates a page from the local free list and initiates a DMA transfer over the PCIe channel from the remote memory blade. The transfer is performed synchronously (i.e., the execution thread is stalled during the transfer, but other threads may execute). Once the transfer is complete, the fault handler updates the page table entry to point to the new, local SMA address and puts the prior remote SMA address into a pool of remote addresses that are currently unused.

# App OS Compute Blade CPUs Backpan Memory blade HyperTransport

Figure 5: Fine-Grained Remote Memory Access (FGRA) Design.

This design assumes minor coherence hardware support in every compute blade. The added coherence filter hardware, CF, is shown.

To maintain an adequate supply of free local pages, the VMM must occasionally evict local pages to remote memory, effectively performing the second half of the logical swap operation. The VMM selects a high SMA address from the remote page free list and initiates a DMA transfer from a local page to the remote memory blade. When complete, the local page is unmapped and placed on the local free list. Eviction operations are performed asynchronously, and do not stall the CPU unless a conflicting access to the inflight page occurs during eviction.

#### 3.3.2 Fine-Grained Remote Memory Access (FGRA)

The previous solution avoids any hardware changes to the commodity compute blade, but at the expense of trapping to the VMM and transferring full pages on every remote memory access. The second design examines the effect of a few minimal hardware changes to the high-volume compute blade to enable an alternate design that has higher performance potential. In particular, this design allows CPUs on the compute blade to access remote memory directly at cache-block granularity.

This approach leverages the glueless SMP support found in current processors. For example, AMD Opteron<sup>TM</sup> processors have up to three coherent HyperTransport<sup>TM</sup> links

coming out of the socket. The Fine-Grained Remote Memory Access (FGRA) design, shown in Figure 5, uses custom hardware on the compute blade to redirect cache fill requests to the remote memory blade. Although it does require custom hardware, the changes to enable the FGRA design are relatively straightforward adaptations of current coherent memory controller designs.

This additional hardware, labeled "Coherence filter" in Figure 5, serves two purposes. First, it selectively forwards only necessary coherence protocol requests to the remote memory blade. For example, the coherence filter can respond immediately to invalidation requests because the remote blade does not contain any caches. Only memory read and write requests require processing at the remote memory blade. In the terminology of glueless x86 multiprocessors, the filter ensures that the memory blade is a home agent but not a cache agent. Second, the filter can optionally translate coherence messages destined for the memory blade into an alternate format. For example, HyperTransport-protocol read and write requests can be translated into generic PCIe commands, allowing the use of commodity backplanes and decoupling the memory blade from specific cache-coherence protocols and processor technologies.

Because FGRA allows the remote SMA space to be accessed directly by CPUs, VMM support is not required; an unmodified OS can treat both local and remote addresses uniformly. However, a VMM or additional OS support is required to enable dynamic allocation or revocation of remote memory. Performance can also potentially be improved by migrating the most frequently accessed remote pages into local memory, swapping them with infrequently used local pages—a task that could be performed by a VMM or by extending the non-uniform memory access support available in many OSes.

# **Chapter 4**

# **Evaluation of Disaggregated Memory**

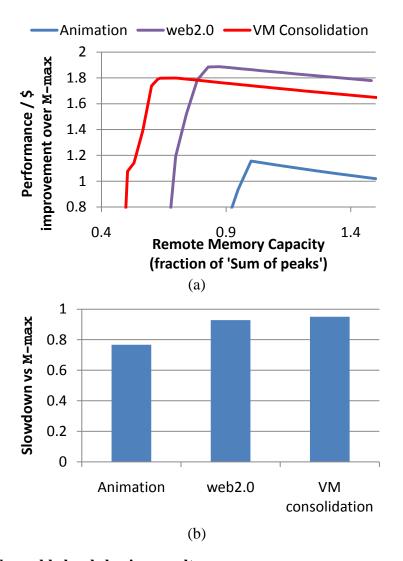

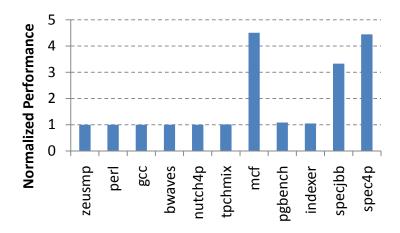

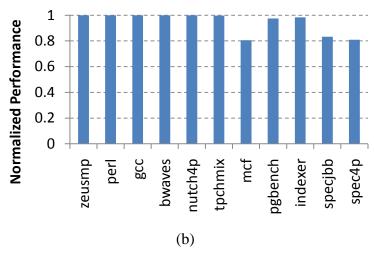

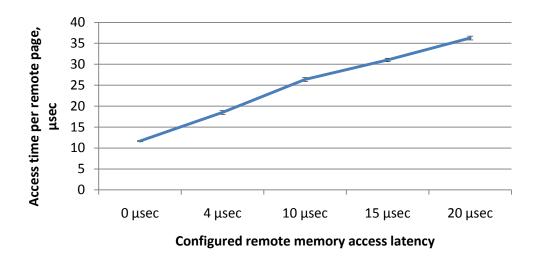

This chapter evaluates the proposed disaggregated memory architectures, specifically examining the ability of the remote memory blade to effectively provide expanded capacity and shared capacity. The two system architectures for accessing the memory blade, PS and FGRA, are evaluated through simulation, and it is found that they are both able to provide high performance, but there are interesting trade-offs and some counter-intuitive results. The results show that memory disaggregation can provide significant performance benefits (on average 10X) in memory-constrained environments. Additionally, the sharing enabled by these solutions can enable large improvements in performance-per-dollar (up to 87%) and greater levels of consolidation (3X) when optimizing memory provisioning across multiple servers. Based on the results, some alternative designs are explored, specifically for the FGRA solution.

# 4.1 Methodology

## 4.1.1 Simulation Methodology

In this work, the performance of the memory blade designs is measured primarily via memory trace-based simulation because it makes it practical to process the billions of main-memory references needed to exercise a multi-gigabyte memory system. The

simulations are accomplished through a newly developed disaggregated memory simulator that uses detailed traces of main-memory accesses to estimate the memory blade's performance. These traces have information such as the address being accessed and the cycle of access. The simulator processes the traces and upon seeing a unique page, places that page in the first memory hierarchy level with free space (either local memory, remote memory, or disk, in that order). On subsequent access to the page, the simulator first determines the location in the hierarchy of the memory being accessed, and then simulates how long it would take to access the address based on any actions that must be taken (e.g., a remote page being accessed must first be swapped to local memory under the PS design). The simulator has multiple configurable parameters including: size, latency, and bandwidth of local memory, remote memory and disk; latency and bandwidth of the interconnect; hypervisor trap time; and packet processing time. The final output of the simulator includes a variety of statistics, such as peak bandwidth used, and the total cycles taken to complete the memory trace, which is the main performance indicator. Other possible alternatives to trace-based simulation are discussed in Section 4.7.1.

Memory reference traces were collected from the COTSon simulator, a detailed full-system simulator, used and validated in prior studies [8]. COTSon was modified to record the physical address, CPU ID, timestamp and read/write status of all main-memory accesses. To make it feasible to run the workloads to completion, a lightweight CPU model was used for this simulation. (Each simulation still took between 1 to 2 weeks to complete.) The simulated system has four 2.2 GHz cores, with per-core dedicated 64KB L1 and 512 KB L2 caches, and a 2 MB L3 shared cache.

| Memory blade parameters |          |                    |      |                            |       |  |

|-------------------------|----------|--------------------|------|----------------------------|-------|--|

| DRAM Latency            | 120 ns   | Map table access   | 5 ns | Request packet processing  | 60 ns |  |

| DRAM<br>Bandwidth       | 6.4 GB/s | Transfer page size | 4KB  | Response packet processing | 60 ns |  |

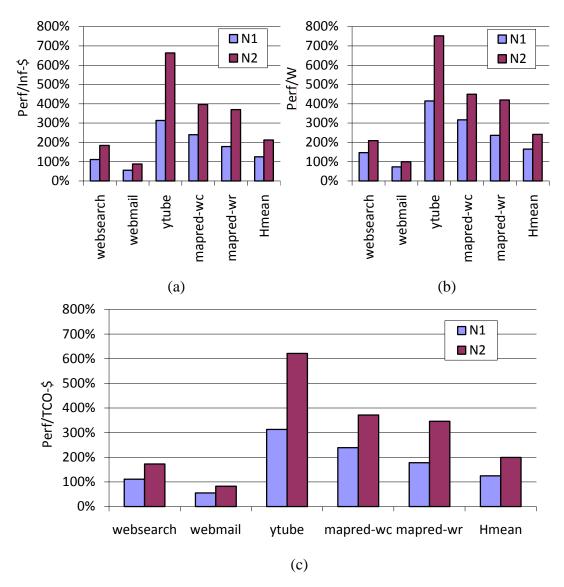

(a)