# ENHANCING THE INSTRUCTION FETCHING MECHANISM USING DATA COMPRESSION

by

**I-Cheng Chen**

A dissertation submitted in partial fulfillment of the requirement for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 1997

Doctoral Committee:

Professor Trevor Mudge, Chair Professor Richard B. Brown Professor Peter M. Chen Professor Edward S. Davidson Professor Ronald J. Lomax

© I-Cheng Chen All Rights Reserved

\_ 1997

This dissertation is dedicated to my parents, Dr. Chih-Hsien Chen and Mrs. Ching-Mei Chen.

#### ACKNOWLEDGEMENTS

First and foremost, I would like to thank my advisor, Professor Trevor Mudge, for giving me his precious advice and guidance. He, by setting an example himself, also showed the importance of working smart and being well-rounded.

I also want to thank my dissertation committee. I would like to thank Professor Richard Brown who leads the PUMA project with dedication and provides us with an excellent research environment. Professor Edward Davidson brought me into the field of computer architecture with his solid and intellectually stimulating lectures. I would also like to thank Professor Ronald Lomax and Professor Peter Chen for their helpful comments on this dissertation.

I am deeply indebted to my parents for their continuous support throughout my life. Without their caring encouragement, I would never have been able to complete my Ph.D. program. And I would also like to thank my brother I-Hong Chen for his assistance.

I would like to acknowledge Professor Sean Coffey and Professor Peter Bird for giving me new perspectives and advice on different research directions.

I also wish to thank Chih-Chieh Lee, who has been a classmate of mine since high school, for his great partnership. Through numerous night-long discussions, he has helped me create and implement various research ideas. I really cherish the opportunity to have him as my academic as well as social partner.

I gratefully thank my group members, Brian Davis, Charles Lefurgy and Bruce Jacob for their patient assistance on my English. They are the best tutors one can ever find. I would also like to thank other group members, Jim Dundas, Matt Postiff, Kristian Flautner, Mike Riepe, David Van Campenhout, Victor Kravets, Todd Basso, Spencer

iii

Gold, Tim Strong, Sean Stetson, Phiroze Parakh, Claude Gauthier, Keith Kraver, Mini Nanua, and Mike Kelly, for creating a pleasant and productive working environment. In addition, I like to thank my colleagues, Jude Rivers and Wee Teck Ng, for their assistance.

Finally, I would like to thank Hong-Yi Wei for her company and kind support.

## TABLE OF CONTENTS

| DED  | DICATI                            | ÖNii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACŀ  | KNOW                              | LEDGEMENTS iii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| LIST | <b>F OF F</b>                     | IGURES viii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| LIST | Г OF Т                            | ABLESx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CHA  | APTER<br>INT                      | <b>DGEMENTS</b> iii <b>URES</b> viii <b>BLES</b> x <b>DDUCTION</b> 1         for fast instruction fetching       1         apression as a solution       2         tion of this dissertation       3 <b>YSIS OF BRANCH PREDICTION VIA DATA COMPRESSION</b> 6         ion       6         nodel and overview of branch prediction       7         general conceptual system model for branch prediction       8         2.1.1       Source       8         2.1.2       Information processor       9         2.2.1.2.1       Selector       9         2.2.1.2.1       Selector       10         2.1.3       Predictor       10         2.1.3       Predictor       10         2.1.4       Selector       10         2.1.5       Compatcher       10         2.1.1       Markov predictor schemes       10         3.1.1       Markov predictors       13         3.1.2       Combining Markov predictors to perform PPM       13         3.1.2       Combining Markov predictor       15         escription of two-level predictor       15         wo-level branch pre |

| 1.1  | The ne                            | ed for fast instruction fetching1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.2  | Data c                            | ompression as a solution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.3  | Organi                            | zation of this dissertation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CHA  | APTER<br>ANA                      | 2<br>ALYSIS OF BRANCH PREDICTION VIA DATA COMPRESSION 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.1  | Introdu                           | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.2  | System 2.2.1                      | 2.2.1.2       Information processor       9         2.2.1.2.1       Selector       9         2.2.1.2.2       Dispatcher       10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.3  | Data c<br>2.3.1                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.4  | Two-le<br>2.4.1<br>2.4.2<br>2.4.3 | evel branch prediction as an approximation of PPM15Description of two-level predictor15Two-level branch predictors as Markov predictors16Approximation to optimal predictors18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.5 | Impact of optimal predictors and further improvement192.5.1Implication of optimal predictors192.5.2Assumptions for optimal predictors192.5.3Illustration of modest improvements using PPM techniques20 |                            |  |  |  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|--|--|

| 2.6 | Cost-effectiveness of PPM                                                                                                                                                                              | 26                         |  |  |  |

| 2.7 | Discussion of further improvement                                                                                                                                                                      | 30<br>31<br>32<br>32<br>32 |  |  |  |

| 2.8 | Conclusions and further work                                                                                                                                                                           | 33                         |  |  |  |

| CH  | APTER 3<br>FURTHER EXAMINATION WITH OPTIMAL ALGORITHM AND<br>EXACT ANALYSIS                                                                                                                            | 35                         |  |  |  |

| 3.1 | Description of Lempel-Ziv predictor                                                                                                                                                                    | 35                         |  |  |  |

| 3.2 | Implementation details and consideration                                                                                                                                                               | 39                         |  |  |  |

| 3.3 | Simulation results                                                                                                                                                                                     | 40                         |  |  |  |

| 3.4 | Verification with an exactly analyzable program—Quicksort3.4.1Description of Quicksort                                                                                                                 |                            |  |  |  |

| 3.5 | Predictability of branches in Quicksort                                                                                                                                                                | 43                         |  |  |  |

| 3.6 | Simulation results                                                                                                                                                                                     | 45                         |  |  |  |

| 3.7 | Summary                                                                                                                                                                                                | 47                         |  |  |  |

| CH  | APTER 4<br>DESIGN OPTIMIZATION FOR HIGH-SPEED PER-ADDRESS TWO<br>LEVEL BRANCH PREDICTORS                                                                                                               |                            |  |  |  |

| 4.1 | Introduction                                                                                                                                                                                           | 48                         |  |  |  |

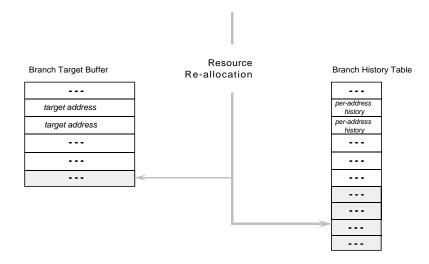

| 4.2 | Per-address two-level branch predictors4.2.1Tagless implementation                                                                                                                                     |                            |  |  |  |

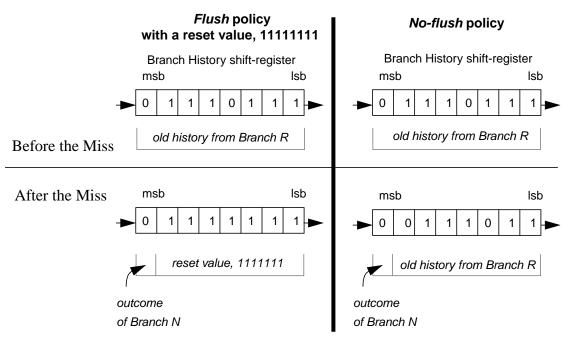

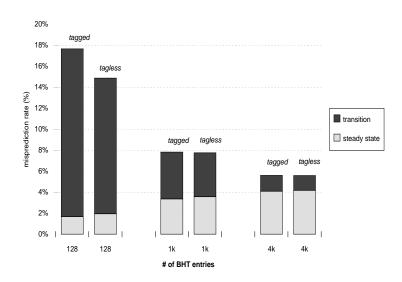

| 4.3 | Performance analysis for tagless predictors4.3.1Miss handling policies4.3.2Simulation methodology4.3.3Simulation results4.3.4Analysis using transitional-state and steady-state error                  | 53<br>54<br>55             |  |  |  |

| 4.4 | Cost-benefit analysis for tagless predictors4.4.1Cost/performance analysis4.4.2Design principles                                                                                                       | 62                         |  |  |  |

| 4.5 | Conclusion                                                                                                                                                |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHA | APTER 5<br>IMPROVING INSTRUCTION FETCH BANDWIDTH AND I-CACHE<br>PERFORMANCE USING DATA COMPRESSION                                                        |

| 5.1 | Introduction                                                                                                                                              |

| 5.2 | Intrinsic compressibility (redundancy) in programs725.2.1 Patterns725.2.2 Instruction fetch bottleneck74                                                  |

| 5.3 | Description of the compression technique                                                                                                                  |

| 5.4 | Simulation results                                                                                                                                        |

| 5.5 | Discussion of implementation issues                                                                                                                       |

| 5.6 | Related research                                                                                                                                          |

| 5.7 | Conclusion and future research                                                                                                                            |

| CHA | APTER 6<br>PREFETCHING USING BRANCH PREDICTION INFORMATION90                                                                                              |

| 6.1 | Introduction                                                                                                                                              |

| 6.2 | Description of prefetching schemes916.2.1Related prefetching schemes916.2.2Branch prediction-based prefetching92                                          |

| 6.3 | Simulation environment956.3.1Simulation of speculative execution956.3.2Description of benchmarks966.3.3Hardware assumption976.3.4Bus arbitration policy98 |

| 6.4 | Simulation results and analysis                                                                                                                           |

| 6.5 | Discussion of implementation issues                                                                                                                       |

|     | APTER 7<br>CONCLUSIONS116                                                                                                                                 |

| BIB | LIOGRAPHY                                                                                                                                                 |

## LIST OF FIGURES

| Figure 2.1:  | A conceptual system model for branch prediction                                  |

|--------------|----------------------------------------------------------------------------------|

| Figure 2.2:  | A two-step model for data compression12                                          |

| Figure 2.3:  | Example of a Markov predictor of order 214                                       |

| Figure 2.4:  | Prediction flowchart of a PPM predictor of order m                               |

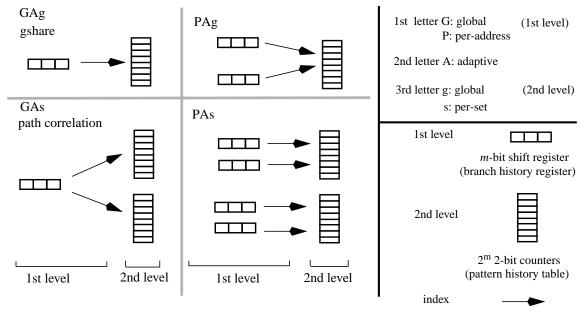

| Figure 2.5:  | Popular variations of two-level predictors                                       |

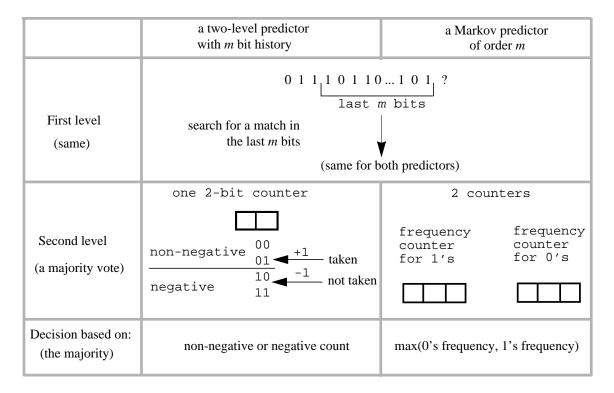

| Figure 2.6:  | A two-level branch predictor vs. a Markov predictor                              |

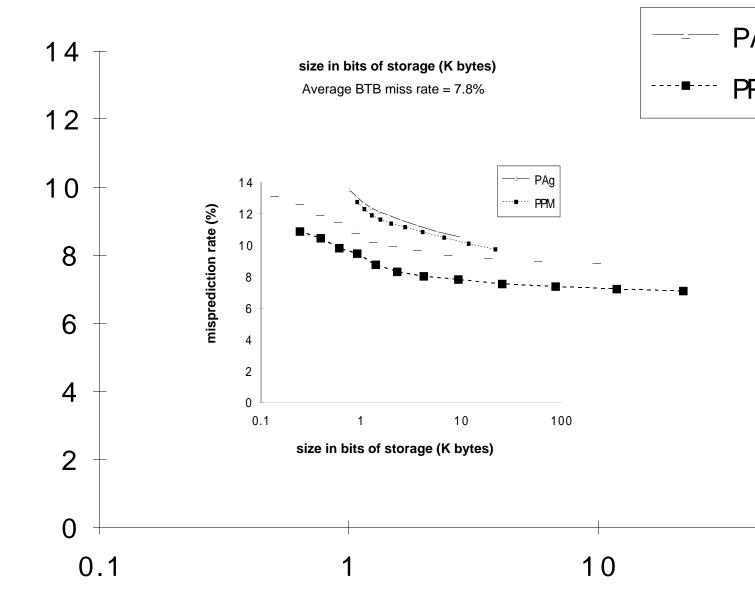

| Figure 2.7:  | Misprediction rate for direct-mapped BTB with 1024 entries                       |

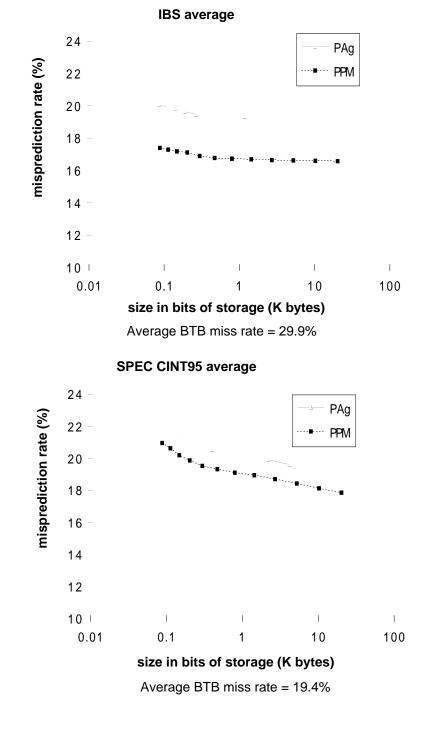

| Figure 2.8:  | Improved accuracy of PPM predictor with a direct-mappedBTB wit 128 entries.25    |

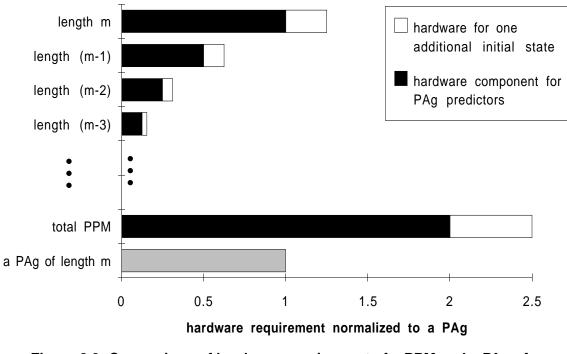

| Figure 2.9:  | Comparison of hardware requirement of a PPM and a PAg of the same history length |

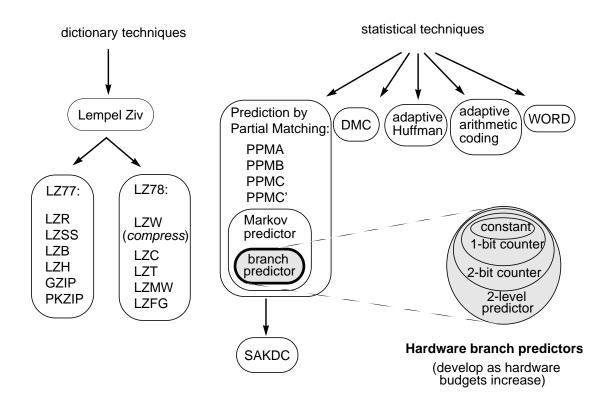

| Figure 2.10: | Branch predictors as a subset of predictors used in data compression31           |

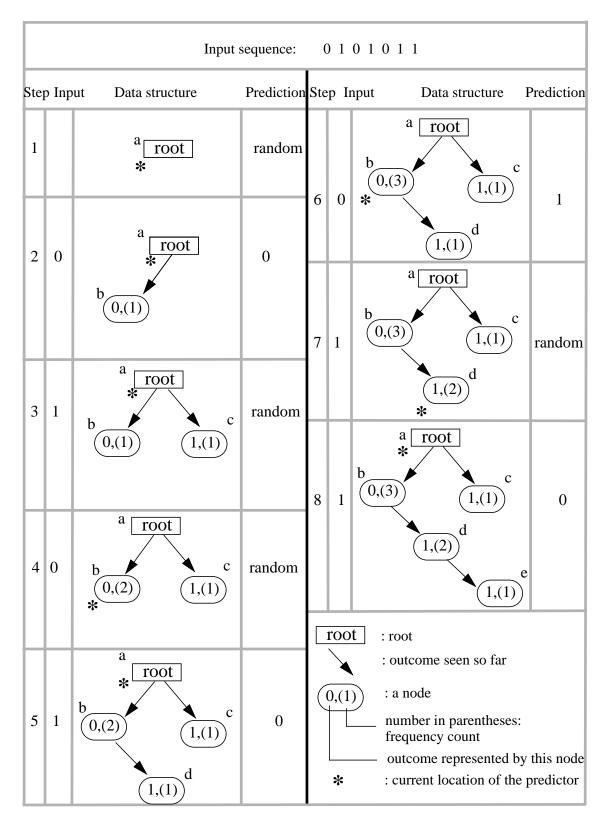

| Figure 3.1:  | Example of a Lempel-Ziv predictor                                                |

| Figure 3.2:  | A Quicksort program and its two comparison branches                              |

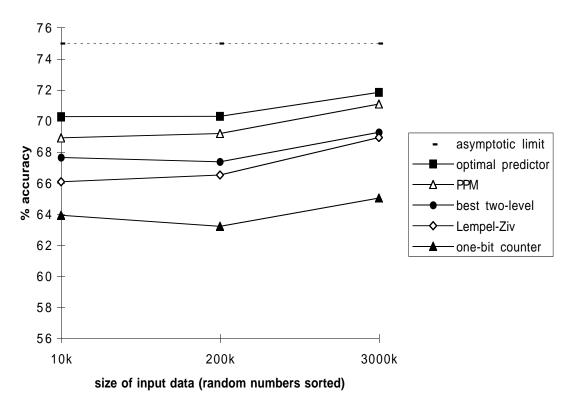

| Figure 3.3:  | Comparison of prediction accuracy for Quicksort                                  |

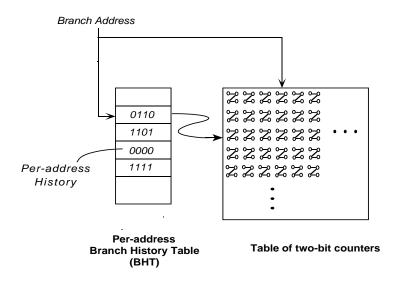

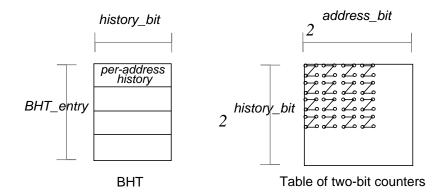

| Figure 4.1:  | Schematic for a per-address two-level branch predictor                           |

| Figure 4.2:  | Tagged per-address two-level branch predictor                                    |

| Figure 4.3:  | Tagless per-address two-level branch predictor                                   |

| Figure 4.4:  | An example comparing the flush and no-flush policies                             |

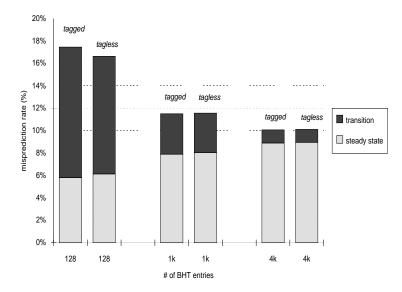

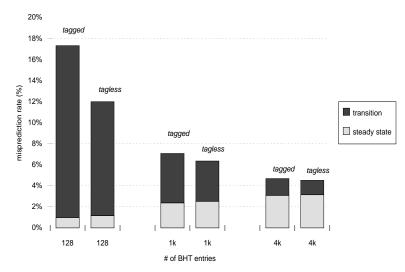

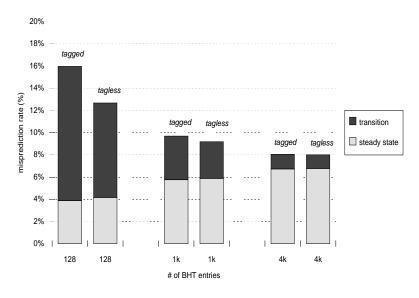

| Figure 4.5:  | Misprediction rate of PAg with 8-bit history length for IBS                      |

| Figure 4.6:  | Misprediction rate of PAg with 8-bit history length for SPEC CINT95 . 56         |

| Figure 4.7:  | Misprediction rate of PAg with 14-bit history length for IBS 57                  |

| Figure 4.8:  | Misprediction rate of PAg with 14-bit history length for<br>SPEC CINT9557        |

| Figure 4.9:  | Illustration for the three parameters of per-address scheme cost function        |

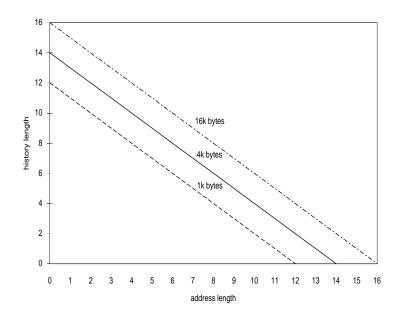

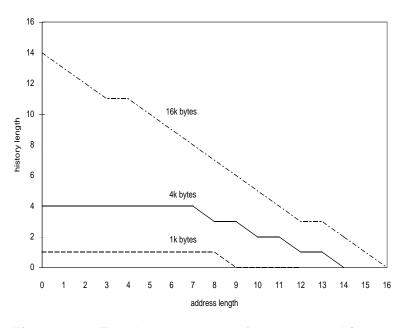

| Figure 4.10: | Equal-cost contours for 128 branch history entries                               |

| Figure 4.11: | Equal-cost contours for 8k branch history entries                                |

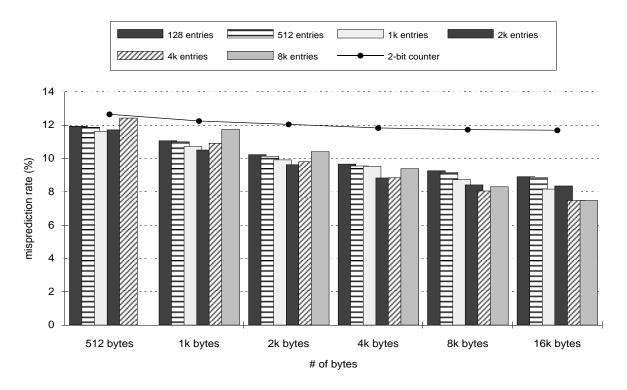

| Figure 4.12: | Misprediction rate vs. budget for SPEC CINT9564                                  |

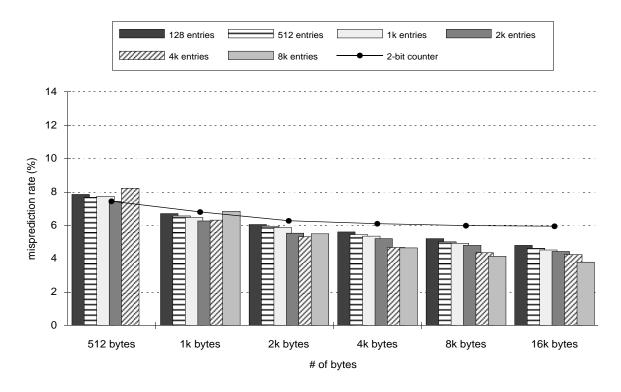

| Figure 4.13: | Misprediction rate vs.budget for IBS                                                                      |

|--------------|-----------------------------------------------------------------------------------------------------------|

| Figure 4.14: | The optimal configuration for each budget in SPEC CINT9566                                                |

| Figure 4.15: | The optimal configuration for each budget in IBS67                                                        |

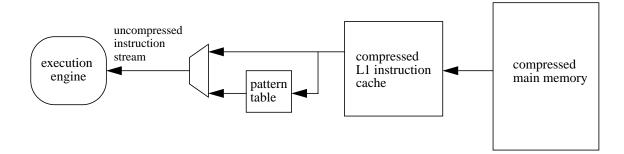

| Figure 5.1:  | Organization of the compression scheme75                                                                  |

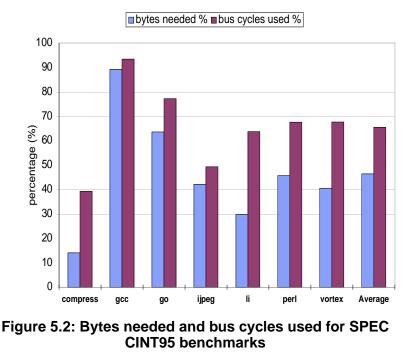

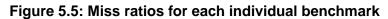

| Figure 5.2:  | Bytes needed and bus cycles used for SPEC CINT95 benchmarks 78                                            |

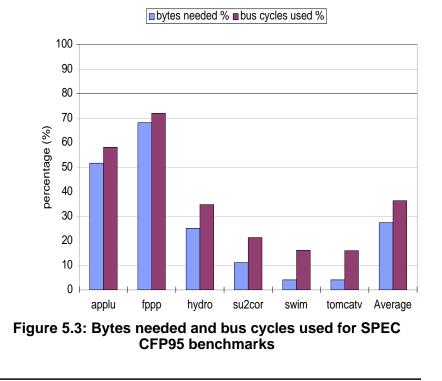

| Figure 5.3:  | Bytes needed and bus cycles used for SPEC CFP95 benchmarks 79                                             |

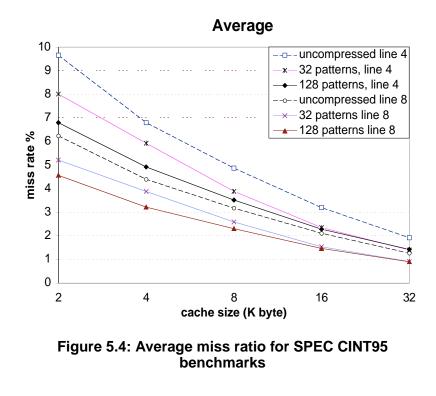

| Figure 5.4:  | Average miss ratio for SPEC CINT95 benchmarks                                                             |

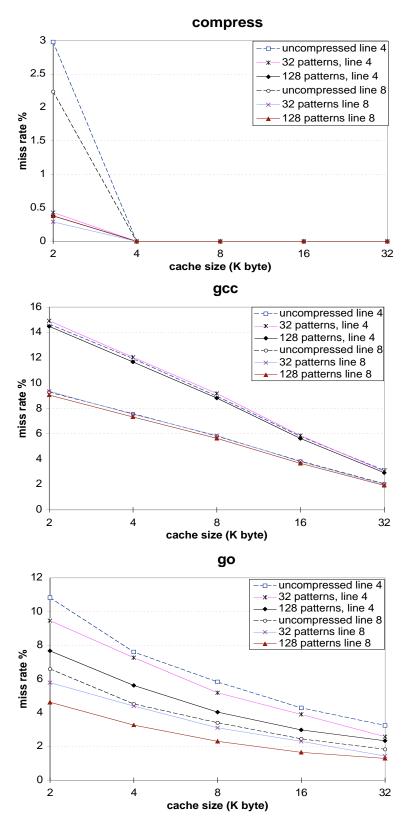

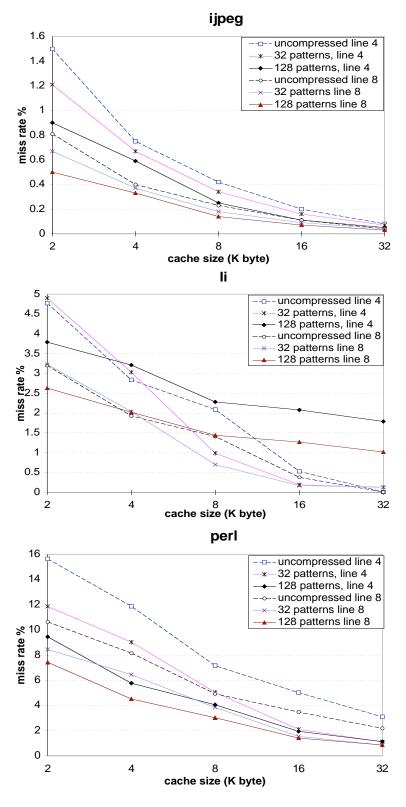

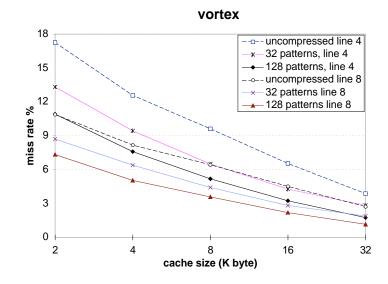

| Figure 5.5:  | miss ratios for each individual benchmark                                                                 |

| Figure 5.6:  | Comparison of the compression effects with 32 patterns and 128 patterns                                   |

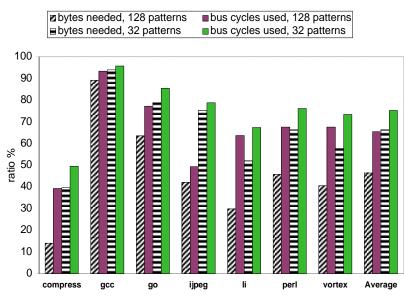

| Figure 5.7:  | A five-stage pipeline using predecoded information to reduce the delay of decompression lookup            |

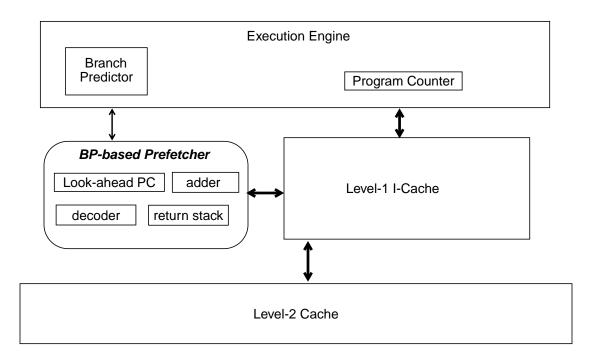

| Figure 6.1:  | Conceptual organization of BP-based prefetching scheme                                                    |

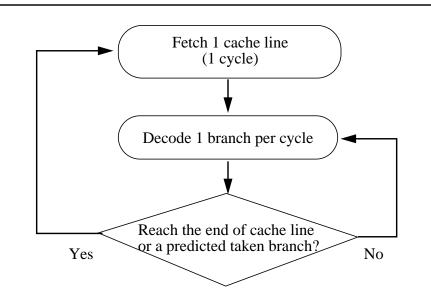

| Figure 6.2:  | Flowchart of BP-based prefetching                                                                         |

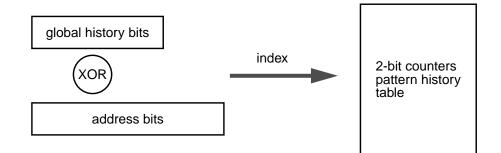

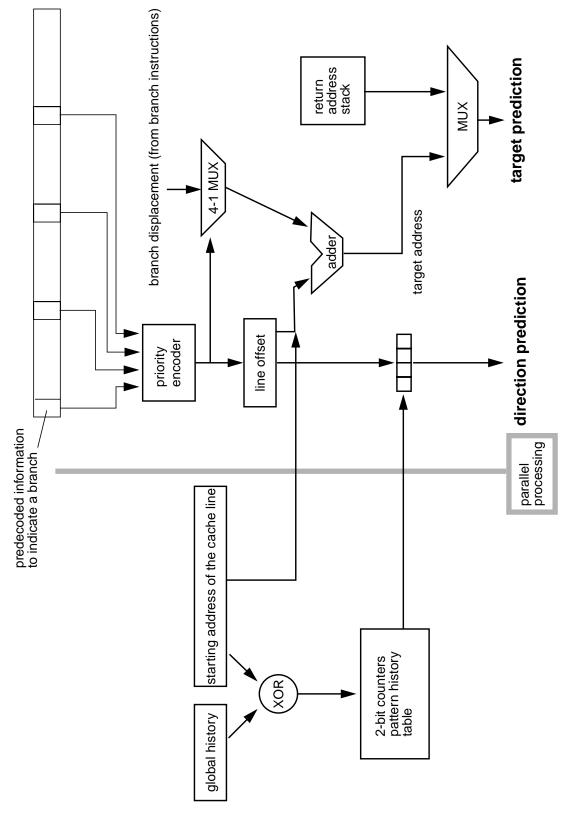

| Figure 6.3:  | A gshare branch predictor                                                                                 |

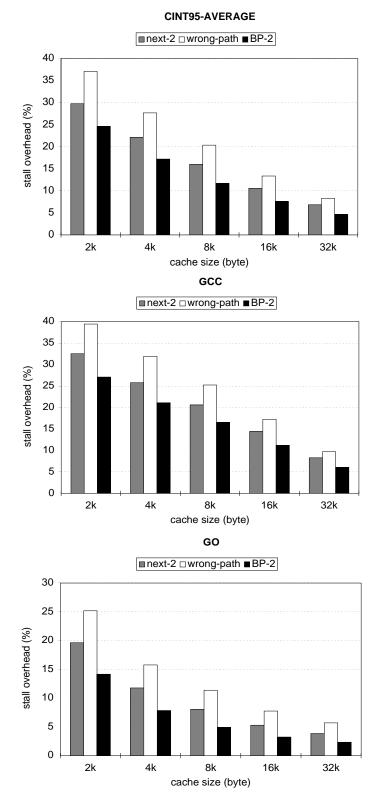

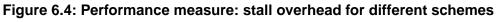

| Figure 6.4:  | Performance measure: stall overhead for different schemes 100                                             |

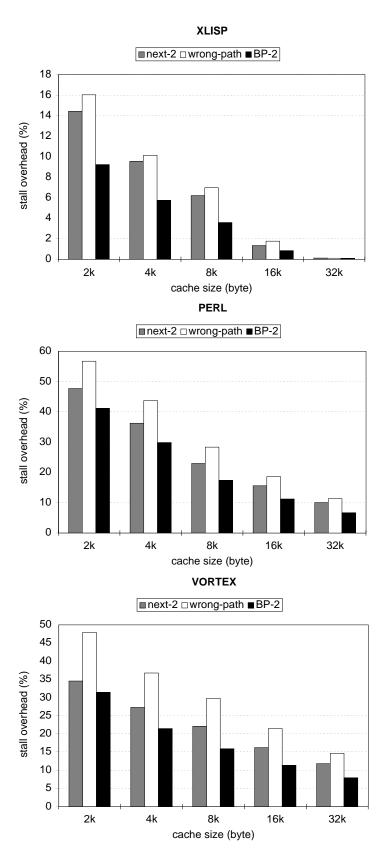

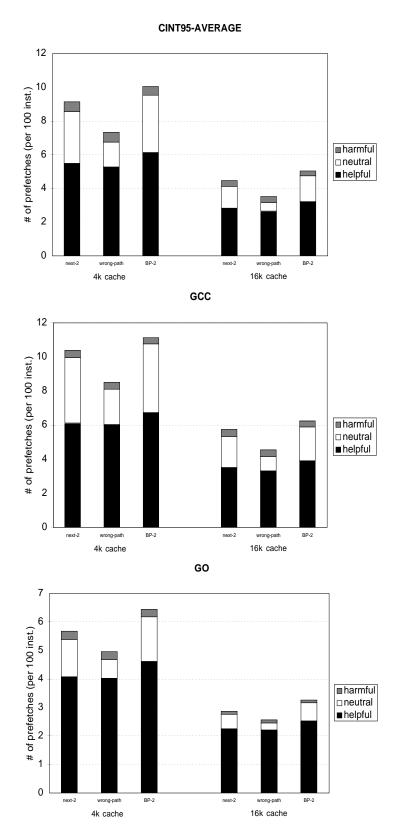

| Figure 6.5:  | Total prefetches generated in each scheme and the classification of these prefetches                      |

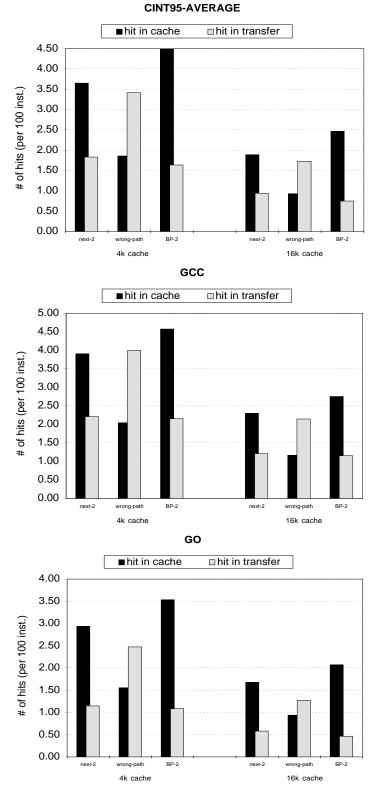

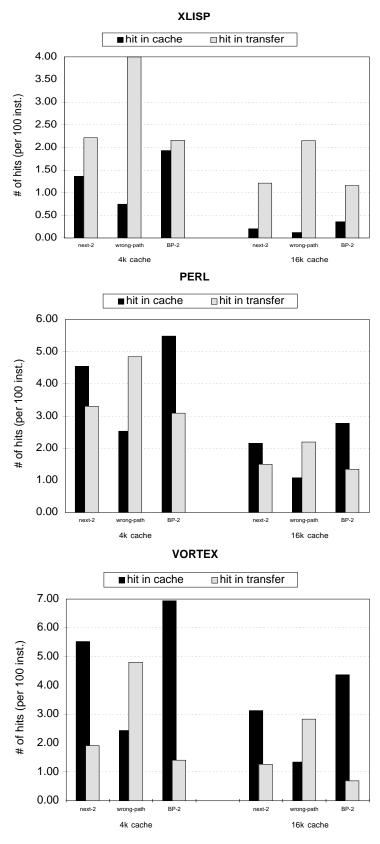

| Figure 6.6:  | Further classification of useful prefetches                                                               |

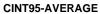

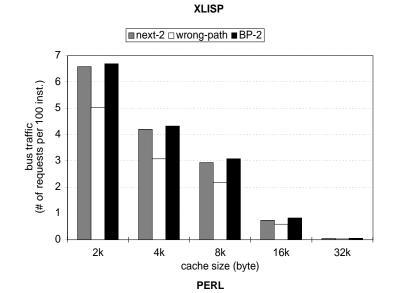

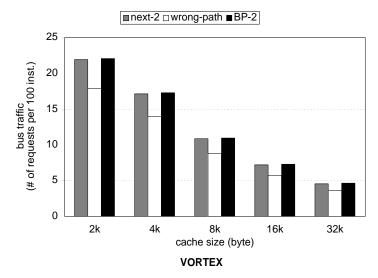

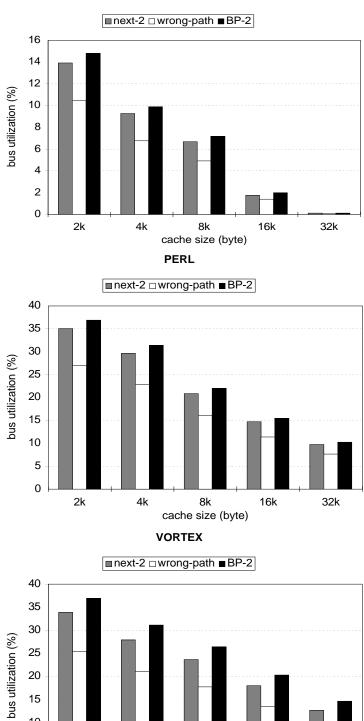

| Figure 6.7:  | Bus traffic for different schemes                                                                         |

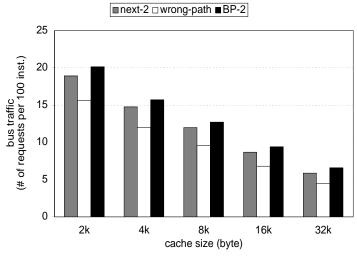

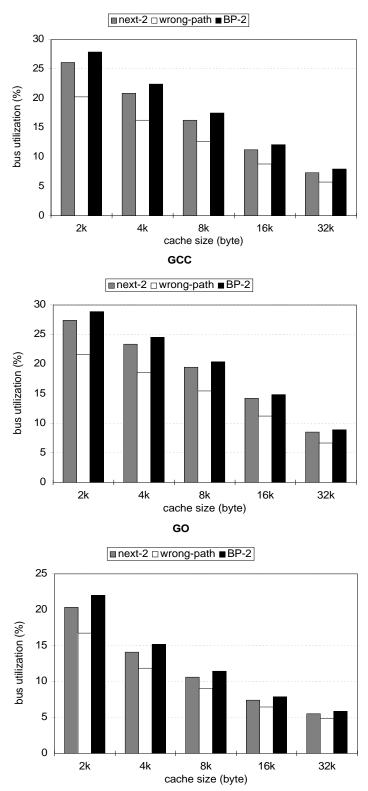

| Figure 6.8:  | Percentage of utilization for the bus to level-2 cache for different schemes                              |

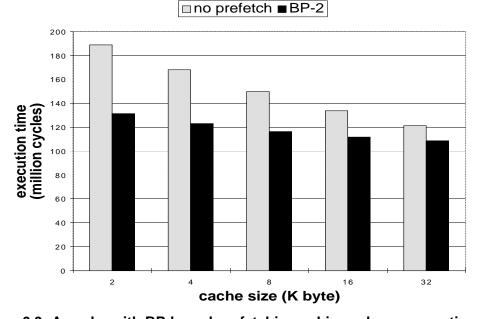

| Figure 6.9:  | A cache with BP-based prefetching achieves lower execution time<br>than a plain cache of 4 times the size |

| Figure 6.10: | A possible implementation of branch prediction-based prefetching 115                                      |

## LIST OF TABLES

| Table 2.1: | Summary of current popular prediction schemes11                                              |

|------------|----------------------------------------------------------------------------------------------|

| Table 2.2: | Description of Instruction Benchmark Suite (IBS) workloads $\dots \dots 21$                  |

| Table 2.3: | Input data set used for SPEC CINT 95 benchmarks                                              |

| Table 2.4: | Static and dynamic conditional branch counts in the IBS and SPEC CINT95 programs             |

| Table 3.1: | Prediction accuracy of GAg style of two-level predictor and Lempel-Ziv on SPECInt92 programs |

| Table 4.1: | Detail misprediction rates for tagged and tagless predictors58                               |

| Table 5.1: | Instruction counts                                                                           |

| Table 5.2: | Pattern table sizes in bytes                                                                 |

| Table 6.1: | Statistics of the benchmarks used                                                            |

## CHAPTER 1 INTRODUCTION

#### **1.1** The need for fast instruction fetching

The speed of current microprocessors continues to increase due to advanced technology and aggressive designs. This high speed mainly results from increasingly higher clock rate, more functional units, wider instruction issuing and deeper speculative execution.

However, the increasing speed of microprocessors also stresses the need for ever faster instruction fetching rate. To sustain the full speed of microprocessors, the instruction fetching rate must increase proportionally to supply the instructions required. Fast instruction fetching rate heavily depends on the solution to these critical issues: accurate branch prediction, high instruction cache hit rate, and high bandwidth for fast transfer rate.

To enable aggressive speculative execution and issuing beyond one basic block per cycle, accurate branch prediction is necessary. This is because conditional branch instructions depend on values produced by previous instructions, but, in current deep-pipelined designs, those previous instructions generally take several cycles to complete. Therefore, to execute at least one branch every cycle, we need accurate branch prediction to predict the direction of branches and to speculatively execute beyond one basic block.

Since memory speeds can not keep up with microprocessor speeds, multiple levels of cache structures are designed to reduce this gap. Consequently, high hit rates in caches become critical for fast and steady instruction supply. In addition, high-bandwidth buses are needed for fetching instructions into the cache. This may be a problem because microprocessors usually have limited pin counts, which limit the widths of buses.

Furthermore, to increase cache hit rates and to hide the transfer latency among various levels of cache structures, efficient prefetching is needed. Prefetching can reduce misses in the cache by anticipating the instructions needed in the future and fetching these instructions into the cache before they are requested. By fetching in advance, prefetching also hides the transfer latency by overlapping it with regular microprocessor execution.

#### **1.2** Data compression as a solution

Data compression is a mature and well established field that has been studied for decades. However, there is little attempt to borrow techniques from data compression to solve critical issues in microprocessor design. In this dissertation, I will show opportunities to apply data compression to improve various important aspects for fast instruction fetching: branch prediction, instruction fetch bandwidth, and instruction cache performance.

I will first show that data compression is closely related to branch prediction and can be applied to improve prediction accuracy. Then, using techniques in data compression, I will establish a theoretical basis for current branch predictors as well as point out directions for future improvements. Data compression can even provide us optimal predictors, yet the design of branch predictors still remains a cost-effective optimization problem due to implementation and budget constraints. In addition, I will demonstrate that, by compressing instruction streams, data compression offers an excellent way to improve the cache hit rate and instruction fetch bandwidth. When carefully designed, compression algorithms can be implemented efficiently in hardware to be incorporated into microprocessors. Then using these techniques as basic building blocks, I design an effective prefetching algorithm using branch prediction information to further improve the instruction fetching rate.

#### **1.3** Organization of this dissertation

This dissertation is based on work described in [Chen96a, Chen96b, Mudge96, Chen97a, Chen97b, Chen97c] and is organized into five chapters. Chapter 2 first demonstrates the correspondence between branch prediction and data compression. Then we establish a theoretical basis for current branch predictors by showing that "two-level" or correlation based predictors are, in fact, simplifications of an optimal predictor in data compression, Prediction by Partial Matching (PPM). If the information provided to the predictor remains the same, it is unlikely that significant improvements can be expected (asymptotically) from two-level predictors, since PPM is optimal. However, there is a rich set of predictors available from data compression, several of which can still yield some improvement in cases where resources are limited. To illustrate this, we conduct tracedriven simulation running the Instruction Benchmark Suite and the SPEC CINT95 benchmarks. The results show that PPM can outperform a two-level predictor for modest sized branch target buffers.

After showing that PPM can be successfully applied to branch prediction, Chapter 3 further examines the performance of another optimal algorithm from data compression: Lempel-Ziv algorithm (found in Unix *compress*). Moreover, we will show that, for some programs, the theoretical limit of predictability can be derived using exact analysis. We have chosen Quicksort algorithm to illustrate this point and then use this limit to calibrate the performance of various branch prediction schemes.

Although optimal predictors can be derived using techniques from data compression, the actual design of branch predictors still remains a cost-effective optimization problem due to implementation and budget constraints. In particular, optimal designs vary with target technology and hardware budget. To identify optimal designs, we need to consider all parameters in a branch predictor and evaluate their interaction.

Chapter 4 shows how the design style of optimal predictors changes due to high

clock rate, and how a comprehensive analysis can be done to determine the best design configuration. We choose per-address two-level branch predictors for illustration, because they have been shown to be among the best predictors and have been implemented in current microprocessors.

Chapter 5 introduces a simple and efficient data compression technique to improve instruction cache hit rates and to increase instruction fetch bandwidth. After code generation, a program is executed and profiled to find frequently used instruction sequences. By mapping these instruction sequences into single byte opcodes, we can effectively compress multiple-instruction, multi-byte operations onto a single byte. When these compressed opcodes are detected in program execution, they are dynamically expanded within the CPU into the original instruction sequences. By restricting the instruction sequence within a basic block (excluding branches), branch instructions and their targets are unaffected by this technique allowing compression to be decoupled from compilation.

Although the compiler was not optimized to exploit our instruction compression technique, we effectively reduced both the I-cache byte fetch requirements and the I-cache miss rates for the SPEC95 benchmarks. The average bytes needed from level-1 cache were reduced by 50% for integer benchmarks, and 70% for floating point benchmarks. The average bus cycles needed to fetch instructions from level-1 cache were reduced by 35% for integer benchmarks, and 65% for floating point benchmarks. In addition, a compression enhanced cache has a lower miss rate than a plain cache twice the size for integer benchmarks.

Using branch prediction as a basic building block, Chapter 6 presents a novel instruction prefetching algorithm to further increase instruction fetching rate. Instruction prefetching can effectively reduce instruction cache misses and hide transfer latency, thus improving the performance. We propose a prefetching scheme, which employs a branch predictor to run ahead of the execution unit and to prefetch potentially useful instructions.

Branch prediction-based (BP-based) prefetching has a separate small fetching unit, allowing it to compute and predict targets autonomously. Our simulations show that a 4-issue machine with BP-based prefetching achieves higher performance than a plain cache 4 times the size. In addition, BP-based prefetching outperforms other hardware instruction fetching schemes, such as next-n line prefetching and wrong-path prefetching, by a factor of 17-44% in stall overhead.

Finally, Chapter 7 presents summaries of previous chapters and some concluding remarks.

#### **CHAPTER 2**

#### ANALYSIS OF BRANCH PREDICTION VIA DATA COMPRESSION

#### 2.1 Introduction

As the design trends of modern superscalar microprocessors move toward wider instruction issue and deeper super-pipelines, effective branch prediction becomes essential to exploring the full performance of microprocessors. A good branch prediction scheme can increase the performance of a microprocessor by eliminating instruction fetch stalls in the pipelines. As a result, numerous branch prediction schemes have been proposed and implemented on new microprocessors [MReport95b, MReport95c, MReport96].

Many researchers focus on designing new branch prediction schemes based solely on comparing simulation results. However, very few studies address the theoretical basis behind these prediction schemes. Knowing the theoretical basis helps us to assess how good a prediction scheme is, as well as how much more we can improve the existing predictors.

To establish a theoretical basis, we first introduce a conceptual system model to characterize components in a branch prediction process (this work has also been published in [Chen96a]). Using this model, we notice that many of the best prediction schemes [Pan92, Yeh92b, Yeh93, McFarling93, Chang94, Nair95b] use predictors similar to a "two-level" adaptive branch predictor [Yeh91]. Then, we demonstrate that these "two-level like" predictors are, in fact, simplified implementations of an optimal predictor in data compression, Prediction by Partial Matching (PPM) [Cleary84, Moffat90]. This establishes a theoretical basis for current two-level predictors that can draw on the

relatively mature field of data compression.

In particular, the potential benefit of applying data compression techniques to branch prediction is readily apparent in the similarity of predictors used in both methods. In practice, the predictors used in branch prediction are only a very small subset of the predictors developed in data compression. To illustrate the potential improvement using data compression techniques, we have conducted trace-driven simulations. The results show that PPM outperforms an equivalent two-level predictor on the Instruction Benchmark Suite (IBS) [Uhlig95a] and the SPEC CINT95 [SPEC95] benchmarks. The improvement is not great, because two-level predictors are near optimal. However, in the case of modest size systems, the improvement is more significant.

This chapter is organized into seven sections. In Section 2.2 we introduce a conceptual system model to describe the process and components of branch prediction. We then use this model to summarize current popular branch prediction schemes. In Section 2.3, we show that data compression is relevant to branch prediction because it also requires prediction.

In Section 2.4, we develop a theoretical basis for two-level predictors by demonstrating that they are simplified versions of an optimal predictor, PPM. Section 2.5 considers the implications of the availability of optimal predictors, and shows that, in some cases, branch prediction can still benefit from data compression. We verify this with trace-driven simulation again running the IBS and the SPEC CINT95 benchmarks. Section 2.7 discusses the potential benefits from data compression and further improvement in each component of our conceptual prediction model. Finally, we present conclusions and further work in Section 2.8.

#### 2.2 System model and overview of branch prediction

To explain branch prediction schemes, a conceptual view of a branch prediction scheme is introduced. This conceptual view allows us to compare various branch

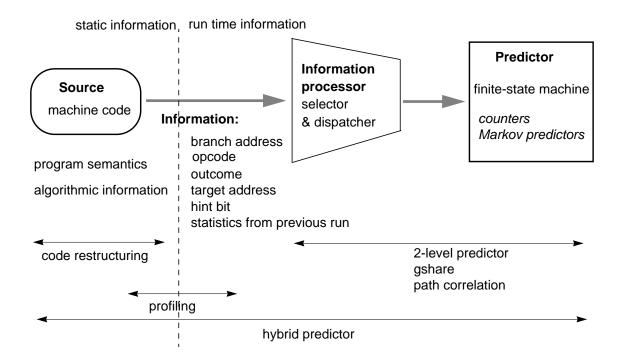

Figure 2.1: A conceptual system model for branch prediction

prediction schemes. It also enables us to focus and improve each component by clearly defining its function. This conceptual model elaborates on the one in [Young95]. Our model extends it to accommodate most popular branch prediction schemes.

#### 2.2.1 A general conceptual system model for branch prediction

The general conceptual model we introduce for branch prediction consists of three major components: a source, an information processor, and a predictor, as illustrated in Figure 2.1. Although some components are often combined in a hardware implementation, this three-part model is useful in explaining the principles behind different prediction schemes.

#### 2.2.1.1 Source

The source is simply the machine code of the programs we are running. The source contains program semantics and algorithmic information. To aid branch prediction, this

information can be explored and extracted during the compile-time. It can be stored and passed on to be used during execution. A hint bit in branch instructions is one means of passing this information. In addition, the source can be modified to produce more predictable branches using statistics from previous test-runs. This is how code restructuring and code profiling work.

#### 2.2.1.2 Information processor

In a hardware implementation, the information processor is often combined with predictors and, hence, overlooked. However, the information processor plays a key role in the prediction process and thus deserves a close study. Conceptually, it can be subdivided into two components: selector and dispatcher.

#### 2.2.1.2.1 Selector

The selector selects which run-time information should be used for branch prediction and encode it. This information can include branch address, operation code, branch outcome, target address, hint bits, or statistics from test-runs. Prediction accuracy depends heavily on the mix of run-time information that is employed. Indeed, significant improvement in future branch prediction schemes are likely to come from providing new prediction information.

Once the information is determined, the selector decides how to represent the information. For example, suppose branch outcomes and branch addresses are selected as information upon which predictions are to be made, then the selector can combine the outcomes with addresses into one single stream or keep outcomes as individual streams classified by branch addresses. A good encoding can result in a concise and efficient representation that helps prediction.

#### 2.2.1.2.2 Dispatcher

The dispatcher determines how the information is mapped (fed) to the various predictors, since multiple information streams and predictors may exist in a prediction scheme. The mapping can be one-to-one, many-to-one, one-to-many, dedicated, or multiplexed (time-shared). Different mappings often have great influence on the final prediction accuracy.

#### 2.2.1.3 Predictor

A predictor is simply a finite-state machine that takes input and produces a prediction. It does not need to know the meaning of the input. Common examples are a constant or static predictor, a 1-bit counter, a 2-bit up-down saturating counter [Smith81], and a Markov predictor. A Markov predictor forms the basis of recent two-level prediction schemes and is discussed in detail in Section 2.3 For the moment, a Markov predictor is simply a finite-state machine that generates predictions based on a finite number of previous inputs.

#### 2.2.2 Overview of current branch prediction schemes

Using the conceptual model just introduced, we can summarize current popular branch prediction schemes in Table 2.1. This table describes the basic components used in each prediction scheme. It lists whether source modification or profiling are used for each prediction scheme. For the information processor, it describes both the information used by the selector and the way dispatcher maps information. Finally, the predictor used in each prediction scheme is also listed. From this table, we notice that many of the best prediction schemes [Pan92, Yeh92b, Yeh93, McFarling93, Chang94, Nair95b] use Markov predictors. We will explain this further in Section 2.4.

| Prediction                                          | Source mod-               | Information processor                   |                                         |                              |

|-----------------------------------------------------|---------------------------|-----------------------------------------|-----------------------------------------|------------------------------|

| scheme                                              | ification or<br>profiling | selector                                | dispatcher                              | predictor                    |

| forward not-<br>taken,<br>backward taken<br>(FNTBT) | no                        | (address - target)                      | many-to-one                             | constant                     |

| 2-bit counter                                       | no                        | outcome, classified by<br>address       | one-to-one,<br>mapped with<br>address   | 2-bit counters               |

| path correlation                                    | no                        | target, in execution<br>order           | one-to-many,<br>mapped with<br>address  | several Markov<br>predictors |

| gshare                                              | no                        | address, outcome,<br>XOR together       | one-to-one                              | a Markov predictor           |

| GAg                                                 | no                        | outcome, in execution order             | one-to-one                              | a Markov predictor           |

| GAs                                                 | no                        | outcome,<br>in execution order          | one-to-many,<br>mapped with<br>address  | several Markov<br>predictors |

| PAg                                                 | no                        | outcome, classified by address          | many-to-one,<br>multiplexed             | a Markov predictor           |

| PAs                                                 | no                        | outcome, classified by address          | many-to-many,<br>mapped with<br>address | several Markov<br>predictors |

| PSg                                                 | no                        | outcome, classified by address          | many-to-one,<br>multiplexed             | constant                     |

| branch<br>correlation                               | yes                       | statistics from previous runs, hint bit | one-to-one,<br>mapped with<br>address   | constant                     |

| hybrid predictor                                    | yes                       | combinations of above                   | combinations of above                   | combinations of above        |

#### Table 2.1: Summary of current popular prediction schemes

### 2.3 Data compression and prediction

Like branch prediction, data compression relies on prediction. In data compression, the goal is to represent the original data with fewer bits. The basic principle of data compression is to use fewer bits to represent frequent symbols, while using more

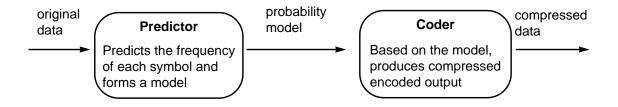

Figure 2.2: A two-step model for data compression

bits to represent infrequent symbols. Thus, the net effect is to reduce the overall number of bits needed to represent the original data. In order to perform this compression effectively, a compression algorithm has to predict future data accurately to build a good probabilistic model for the next symbol [Bell90]. Then, as shown in Figure 2.2, the algorithm encodes the next symbol with a coder tuned to the probability distribution. Current coders can encode data so effectively that the number of bits used is very close to optimal and, consequently, the design of good compression relies on an accurate predictor. The problem of designing efficient and general universal compressors/predictors has been extensively examined. In our experiments we draw on these techniques, adapting them to the new context of branch prediction.

#### 2.3.1 Prediction by Partial Matching

Prediction by partial matching (PPM) is a universal compression/prediction algorithm that has been theoretically proven optimal and has been applied in data compression and prefetching [Cleary84, Krishnan94, Kroeger96, Moffat90, Vitter91]. Indeed, it usually outperforms the Lempel-Ziv algorithm (found in Unix *compress*) due to implementation considerations and a faster convergence rate [Curewitz93, Bell90, Witten94]. As described above, the PPM algorithm for text compression consists of a predictor to estimate probabilities for characters and an arithmetic coder. We only make use of the predictor. We encode the outcomes of a branch, taken or not taken, as 1 or 0 respectively. Then the PPM predictor is used to predict the value of the next bit given the prior sequence of bits that have already been observed.

#### 2.3.1.1 Markov predictors

The basis of the PPM algorithm of order *m* is a set of (m + 1) Markov predictors. A Markov predictor of order *j* predicts the next bit based upon the *j* immediately preceding bits—it is a simple Markov chain [Ross85]. The states are the 2<sup>*j*</sup> possible patterns of *j* bits. The transition probabilities are proportional to the observed frequencies of a 1 or a 0 that occur given that the predictor is in a particular state (has seen the bit pattern associated with that state). The predictor builds the transition frequency by recording the number of times a 1 or a 0 occurs in the (*j* + 1)-th bit that follows the *j*-bit pattern. The chain is built at the same time that it is used for prediction and thus parts of the chain are often incomplete. To predict a branch outcome the predictor simply uses the *j* immediately preceding bits (outcomes of branches) to index a state and predicts the next bit to correspond to the most frequent transition out of that state.

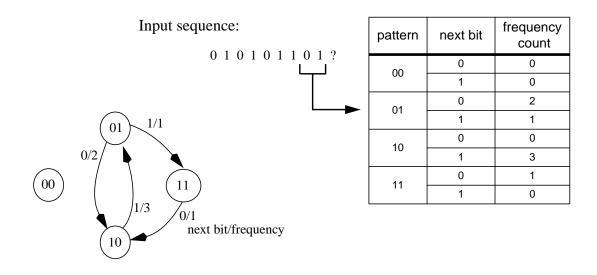

Figure 2.3 illustrates how a Markov predictor works. Let the input sequence seen so far be 010101101, and the order of Markov predictor be 2. The next bit is predicted based on the two immediately preceding bits, that is, 01. The pattern 01 occurs 3 times previously in the input sequence. The frequency counts of the bit following 01 are: 0 follows 01 twice, and 1 follows 01 once. Therefore, the predictor predicts the next bit to be 0 with a probability of 2/3. The (incomplete) 4-state Markov chain is shown at the left of the figure. Note that a 0-th order Markov predictor simply predicts the next bit based on its relative frequency in the input sequence.

#### 2.3.1.2 Combining Markov predictors to perform PPM

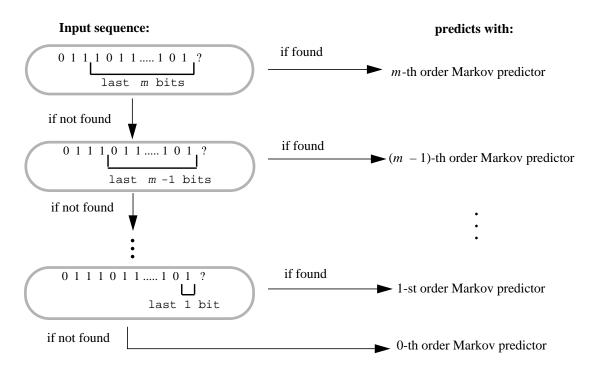

We noted earlier that the basis of a PPM algorithm of order m is a set of (m + 1)Markov predictors. The algorithm is illustrated in Figure 2.4. PPM uses the m

#### Figure 2.3: Example of a Markov predictor of order 2

The Markov chain at left corresponds to the information collected from the input sequence in the table at right. Note that the chain is incomplete, because of 0 frequency count transitions.

immediately preceding bits to search a pattern in the highest order Markov model, in this case *m*. If the search succeeds, which means the pattern appears in the input sequence seen so far (the pattern has a non-zero frequency count), PPM predicts the next bit using this *m*th-order Markov predictor as described in the previous subsection. However, if the pattern is not found, PPM uses the (m - 1) immediately preceding bits to search the next lower order (m - 1)-th order Markov predictor. Whenever a search misses, PPM reduces the pattern by one bit and uses it to search in the next lower order Markov predictor. This process continues until a match is found and the corresponding prediction can be made.

There are a number of variations on how the frequency information in the individual Markov predictors can be updated as the PPM process proceeds. In our experiments we use *update exclusion*. This means that we only update the frequency counters for the predictor that makes the prediction and the predictors with higher order. Lower order predictors are not updated.

Figure 2.4: Prediction flowchart of a PPM predictor of order m

#### 2.4 Two-level branch prediction as an approximation of PPM

In this section, we show that recently proposed two-level or correlation based predictors are approximations of, PPM, an optimal prediction algorithm.

#### 2.4.1 Description of two-level predictor

Among the various branch prediction schemes, two-level or correlation based predictors are among the best. In addition, these predictors all share very similar hardware components. As Figure 2.5 shows, they have one or more shift-registers (branch history registers) to store history information in the first level and have one or more tables of 2-bit counters (pattern history tables) in their second level [Yeh91]. The contents of the first level shift-registers are typically used to select a 2-bit counter in one of the second-level tables. Predictions are made based on the value of the 2-bit counter selected.

Figure 2.5: Popular variations of two-level predictors

#### 2.4.2 Two-level branch predictors as Markov predictors

From the above discussion on two-level adaptive branch predictors and the one on Markov predictors in Section 2.3.1.1, it can be seen that there are strong similarities. Though different schemes of two-level branch predictors exist, they differ only in what information is used for history and what subsets of branch outcomes are used to index and update the counters. As a result, there exists a corresponding Markov predictor for each scheme.

Figure 2.6 shows the similarity between a two-level predictor and a Markov predictor. Both predictors behave exactly the same in the first level. They both use the last m bits of branch outcome to search the corresponding data structure. Note that an m-bit shift register serves two functions: first, it limits the information used for prediction to m previous outcomes and, second, it uniquely defines a finite-state machine in which each state has exactly two predefined next states. In the second level, the Markov predictor uses a frequency counter for each outcome, while the two-level predictor uses a saturating up-

Figure 2.6: A two-level branch predictor vs. a Markov predictor

down 2-bit counter [Smith81]. Whenever a branch is taken/not taken, the 2-bit counter increments/decrements. The decision for a two-level predictor depends on whether the value of the counter falls in the non-negative half or the negative half. Similarly, a Markov predictor simply predicts the next branch to be the most frequent outcome based on two frequency counters. Both predictors are utilizing a majority vote via different implementations. The saturating counter is an approximation to this that can be realized in hardware efficiently.

An interesting illustration is to see how a two-level predictor, the per-address branch history register with global pattern history table (PAg), corresponds to a Markov predictor. This per-address scheme uses one table of 2-bit counters and multiple shift registers where each register records only outcomes of a particular branch. Although multiple shift registers exist, all shift registers operate the same and correspond to the same transition rule for a finite-state machine (state diagram). In addition, all shift registers share the same global table of 2-bit counters and, hence, share the same value (counter) in each state. Therefore, this per-address scheme uses one Markov predictor that is time-shared and updated among various branches.

#### 2.4.3 Approximation to optimal predictors

Given the arguments in the previous sections, we now show that a two-level predictor is an approximation of an optimal predictor. As mentioned in Section 2.3.1, PPM is a theoretically proven optimal predictor consisting of a set of Markov predictors. Though performance is inferior at the beginning, a single Markov predictor can approach the performance of PPM in the long run (asymptotically) [Bell90]. Furthermore, we have shown that a two-level predictor is a simplified Markov predictor. Therefore, we can see that a two-level predictor is an approximation of an optimal predictor, PPM.

Under hardware implementation constraints, a two-level predictor is a reasonable simplification of PPM. The complete PPM predictor can be viewed as a set of two-level predictors, having not one size of predictor (m) but a set that spans m down to 0 (a simple two-bit counter—equivalent to a per-address predictor with zero history length). These extra small predictors help to reduce "cold starts," i.e., lack of information at the training period. Although two-level predictors do not include small predictors, they still can perform well since cold starts are far less severe in branch prediction than in text compression. To see how cold starts differ in the two fields, we consider the number of all possible combinations of m outcomes. In branch prediction, there are  $2^m$  possible combinations where 128 is the number of printable ASCII symbols. Compared to the large number of branches executed in typical programs, these  $2^m$  cold starts are negligibly small and hardly decrease the overall prediction accuracy. Another simplification made by two-level predictors is the use of a 2-bit counter instead of an n-bit counter. This is a cost-effective choice, since two

bits is the minimal number needed so that the direction of the predictor is not changed by the single exit in a loop statement [Lee84, Smith81].

As an aside, note that it is not coincidental that a 2-bit saturating up-down counter is the best among 4-state predictors [Nair95a]. This is because, with four states, one 2-bit saturating up-down counter is the best way to mimic the majority vote used in the Markov predictor. In the original Markov predictor, this voting prediction is done with two frequency counters (one for each outcome).

#### 2.5 Impact of optimal predictors and further improvement

#### **2.5.1 Implication of optimal predictors**

Having shown that a two-level predictor is an approximation of an optimal predictor, we have established a theoretical basis for this type of branch predictor. Rather than just comparing simulation results, which does not tell us how well these predictors perform in general, we can now have a reasonable degree of confidence in the performance of two-level predictors. It is unlikely that, by improving the predictor component alone, we can generate significant improvement in predictor accuracy excepting in special cases discussed below. This is because two-level predictors already perform close to optimal under the constraints imposed by the information they are given. Of course, the inclusion of more information (e.g., knowledge about the program executing) can always be used to improve the prediction accuracy.

#### 2.5.2 Assumptions for optimal predictors

It is important to clarify just what we mean by "optimal." The optimality of PPM assumes that the source of data (branch outcomes in our case) is a stationary and ergodic random process; in other words, outcomes are time invariant and future outcomes can be predicted with samples drawn from present ones. This type of source modeling has been

successfully applied to a broad range of applications including English text [Bell90]. In our work, we have assumed this source model applies to branch outcomes. It seems reasonable to assume that the statistics of branches is not influenced by the point in execution time when one starts to observe them, because we consider our branch outcomes to be drawn from a sequence created by the ordered execution of all wellformed programs. With these assumptions, a source model that is ergodic and stationary is a reasonable choice. However, there are some concerns that limit the extent to which the optimality claims which follow from the model apply. The most obvious is that optimality, in the sense used here, only implies that a scheme will perform as well as any other scheme in the long run. However, nothing is guaranteed about the rate of convergence, or the time before a scheme reaches its best performance. Therefore, though an optimal scheme will perform well eventually, in practice, it may take a long time to reach that state. In addition, the implementation of an optimal scheme may need a large memory and other resources.

From the above statement we cannot conclude whether an optimal predictor will perform well if a program ends quickly, or if the time between context switches is short. Fortunately, a typical time frame between context switches is relatively long and may contain anywhere from about 10 thousand to 100 thousand branches. Furthermore, empirical evidence described in the next section and reported in [Bell90, Witten94] suggests PPM has a fast convergence rate.

#### 2.5.3 Illustration of modest improvements using PPM techniques

In this section, we illustrate that techniques from data compression can still, in some cases, yield modest improvements to branch prediction. To assess and confirm the potential improvement, we conduct trace-driven simulations. As input for the simulation, we use the Instruction Benchmark Suite (IBS) benchmarks [Uhlig95a] and the SPEC CINT95 benchmark suite [SPEC95] for our simulation.

| IBS benchmarks                                                                                                                                     |                                                                                   |                                                              |                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------|

| Benchmarks                                                                                                                                         | Description                                                                       |                                                              |                                                 |

| groff                                                                                                                                              | GNU C++ implementation of the Unix 'nroff' text formatting program. Version 1.09. |                                                              |                                                 |

| gs                                                                                                                                                 | 'Ghostscript' version 2.4.1. Displays single page of text and graphics.           |                                                              |                                                 |

| mpeg_play'mpeg_play' version 2.0. Displays 85 frames.nroffUnix text formatting program whipped with Ultrix 3.1.real_gccGNU C compiler version 2.6. |                                                                                   |                                                              |                                                 |

|                                                                                                                                                    |                                                                                   | sdet                                                         | Multiprocess benchmark from the SPEC SDM suite. |

|                                                                                                                                                    |                                                                                   | verilog Verilog-XL version 1.6b. Simulates a microprocessor. |                                                 |

| video_play                                                                                                                                         | Modified 'mpeg_play.' Displays 610 frames.                                        |                                                              |                                                 |

Table 2.2: Description of Instruction Benchmark Suite (IBS) workloads

The IBS benchmarks are a set of applications designed to reflect realistic workloads. A brief description of benchmarks in IBS is listed in Table 2.2. The traces of these benchmarks are generated through hardware monitoring of a MIPS R2000-based workstation. We use the traces collected under the operating system Ultrix 3.1, which include both kernel-level and user-level instructions.

For the SPEC CINT95 benchmark suite, we used ATOM [Eustace95], a code instrumentation interface from Digital Equipment Corporation, to collect our traces. The benchmarks are first instrumented with ATOM, then executed on a DEC 21064-based workstation running the OSF/1 3.0 operating system to generate traces. These traces contain only user-level instructions. The input data set used for generating traces is summarized in Table 2.3.

The statistics of traces from the IBS and the SPEC CINT95 are summarized in Table 2.4. All traces are identical in format and are used as input to our simulator.

By using a set of small predictors, PPM can predict relatively well in situations where little history information is available, such as conflict misses or cold starts. In particular, this occurs in per-address prediction schemes where a finite branch-target

| SPEC CINT 95 benchmarks                     |                                                                                                              |  |  |  |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|

| Benchmarks                                  | input data set                                                                                               |  |  |  |

| compress                                    | reduced version of <i>bigtest.in</i> (reference data), reduced to 30,000 elements (instead of 14,000,000)    |  |  |  |

| gcc jump.i (one of the reference data sets) |                                                                                                              |  |  |  |

| go                                          | <i>2stone9.in</i> (training data), reduced the game_level to 19 (instead of 50)                              |  |  |  |

| ijpeg                                       | specmun.ppm (test data)                                                                                      |  |  |  |

| li                                          | train.lsp (training data)                                                                                    |  |  |  |

| perl                                        | reduced version of <i>scrabbl.in</i> (reference data), reduced to the first 5 items (instead of 7)           |  |  |  |

| vortex                                      | reduced version of training data, reduce iteration counts<br>and data to the first 10 items (instead of 250) |  |  |  |

#### Table 2.3: Input data set used for SPEC CINT 95 benchmarks

Input to the SPEC CINT95 benchmarks was a reduced input data set; each benchmark was run to completion.

buffer is used to record individual branch history, since the history of a particular branch may be overwritten by that of other branches due to contention in the finite buffer (conflict misses). For these cases, PPM can be used to alleviate the problem.

To illustrate potential improvement, we compare the PAg two-level predictor scheme and PPM. PAg means that the inputs are divided into per-address branch outcome streams, and then they are fed into one global predictor. Compared to global schemes, the advantage of PAg, and other per-address schemes, is that aliasing that may arise by mixing streams from different branch histories is reduced. However, conflict misses in the branch target buffer (BTB) become a more significant problem because only finite records of distinct branches can be maintained. This is due to limited buffer size; consequently, the history will be replaced and lost from time to time. The conflict miss problem gets worse as the number of distinct branches increases, since more individual branch outcome streams must be recorded.

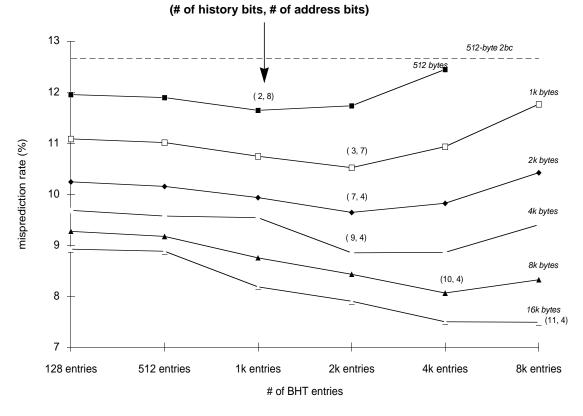

Figure 2.7 shows the misprediction results for a direct-mapped BTB with 1024

| Benchmarks  |            | static<br>conditional<br>branches | dynamic<br>conditional<br>branches |

|-------------|------------|-----------------------------------|------------------------------------|

|             | compress   | 95                                | 10,216,264                         |

| 95          | gcc        | 15,647                            | 24,048,361                         |

| SPEC CINT95 | go         | 4,742                             | 18,168,554                         |

| CI          | ijpeg      | 902                               | 40,854,598                         |

| ЪЕ          | li         | 345                               | 24,977,690                         |

| S           | perl       | 1,576                             | 31,309,305                         |

|             | vortex     | 5,963                             | 24,979,201                         |

|             | groff      | 6,333                             | 11,901,481                         |

|             | gs         | 12,852                            | 16,307,247                         |

|             | mpeg_play  | 5,598                             | 9,566,290                          |

| IBS         | nroff      | 5,249                             | 22,574,884                         |

| B           | real_gcc   | 17,361                            | 14,309,867                         |

|             | sdet       | 5,310                             | 5,514,439                          |

|             | verilog    | 4,636                             | 6,212,381                          |

|             | video_play | 4,606                             | 5,759,231                          |

Table 2.4: Static and dynamic conditional branch counts in the IBS andSPEC CINT95 programs

entries. The vertical axis indicates branch misprediction rate, and the horizontal axis indicates the size of predictors in term of the storage bits needed. The top graph is the average of the IBS benchmarks, while the bottom graph is the average of the SPEC CINT95 benchmarks. As indicated by the relatively lower misprediction curve, PPM outperforms PAg, and the improvement of PPM is greater in IBS than in the SPEC CINT95. The small improvement in SPEC is due to its small miss rate (4.8%) in the BTB. This is because small miss rate implies little history information loss (occurred during misses); however, PPM is better than PAg only in cases when history information is not available, such as conflict misses and cold misses. The small BTB miss rate in the SPEC is because only a small number of distinct branches contribute to the vast majority of branch instances for most benchmarks [Sechrest96].

SPEC CINT95 average

Average BTB miss rate = 4.8%

### Figure 2.7: Misprediction rate for direct-mapped BTB with 1024 entries

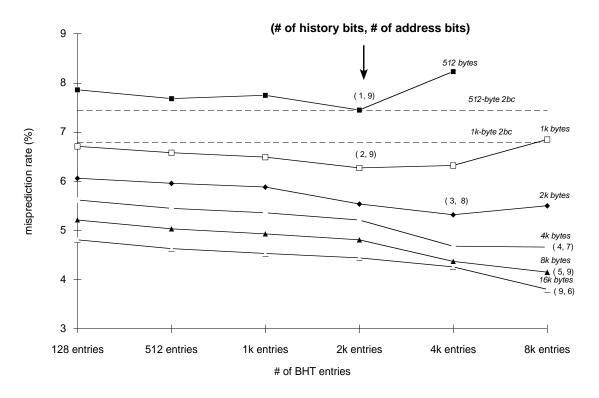

To see the effect of a small BTB, we reduce the number of entries from 1024 to 128. As shown in Figure 2.8, PPM again performs better than the PAg scheme for both

Adobe's PostScript Language Reference Manual, 2nd Edition, section H.2.4 says your EPS file is not valid, as it calls setpagedevice

# **IBS** average

Figure 2.8: Improved accuracy of PPM predictor with a direct-mapped BTB wit 128 entries

benchmarks. Notice that, with a smaller BTB, the improvement of PPM over PAg is more pronounced. Also, as in the previous case, the improvement of PPM is greater in IBS than

in the SPEC CINT95. The improvement of PPM is more significant when the BTB miss rate (history information lost) is high.

As the results show, PPM performs better than two-level predictors. The improvement comes from a better mechanism for dealing with conflict (and cold) misses in which a set of Markov predictors rather than just the largest one are employed, as PAg does. If PPM cannot find a complete length of the branch history information, it reduces the length and search in the lower predictors. In the same situation two-level predictors use incorrect history information, which can lead them to index to the wrong counters. The accuracy decreases because not only is the wrong counter selected for prediction, but it is also incorrectly trained. PPM solves the conflict miss problem more gracefully than two-level predictors. This is why PPM performs better when the miss rate is pronounced.

To conclude this section, we briefly describe the implementation cost, and more details will be discussed in the next section. The PPM in our simulation uses 2-bit counters as the PAg does. The PPM implementation is essentially a set of PAg systems with history registers of length m, m-1, m-2, etc. Thus, the second-level table in the PPM implementation requires ( $2^m + 2^{m-1} + 2^{m-2} + ... + 2^0 = 2^{m+1} - 1$ ) 2-bit counters. All together, this adds to about twice the number of bits required in the PAg system. This is reflected in Figure 2.7 and Figure 2.8.

#### 2.6 Cost-effectiveness of PPM

Though a PPM needs more hardware than a PAg of the same history length, a PPM is still more cost-effective. We can see this by understanding the relationship of performance improvement to additional hardware requirement for both PPM and PAg. To enable a straightforward comparison of the hardware requirements of both predictors, the PPM in our simulator uses the same counters, 2-bit, as a PAg does. In this prototype, the hardware requirement of our PPM is about 2.5 times that of a PAg of the same history length. As shown in Figure 2.9, the additional hardware requirement comes from (1) the

Figure 2.9: Comparison of hardware requirement of a PPM and a PAg of the same history length