# A BASEBAND PROCESSOR FOR SOFTWARE DEFINED RADIO TERMINALS

by

Hyunseok Lee

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering and Computer Science) in The University of Michigan 2007

Doctoral Committee:

Professor Trevor N. Mudge, Chair Professor Chaitali Chakrabarti, Arizona State University Associate Professor Scott Mahlke Professor Marios C. Papaefthymiou Professor Wayne E. Stark

### ABSTRACT

#### A BASEBAND PROCESSOR FOR SOFTWARE DEFINED RADIO TERMINALS

by Hyunseok Lee

Chair: Trevor N. Mudge

Software defined radio (SDR) is a technical effort to use programmable hardware in wireless communication systems so that various protocols can be easily supported by software. However, using programmable hardware for SDR terminals has been unachievable because of their tight power budget and high demand on computation capability. The main theme of this thesis is to design a power efficient programmable baseband processor for the SDR.

This thesis analyzed most contemporary wireless communication protocols both in system and algorithm levels. System level analysis is to see the interactions between algorithms and the algorithm level analysis is to investigate the computation patterns of the algorithms comprising baseband operations.

Based on the characterization results, this thesis proposes chip multiprocessor architecture, whose PEs have both parallel and scalar datapaths. Multiprocessor architecture is proposed to exploit the algorithm level parallelism. Both the parallel and scalar datapaths are used because baseband processing is a combination of parallelizable and scalar computations. For additional enhancements, three novel schemes are applied to the SIMD style parallel datapath: macro instructions, macro pipelining, and the staggered execution of computation units.

Macro instruction is to combine several primitive instructions into one. It reduces system power by eliminating unnecessary register accesses. The macro pipelining is to form a pipeline by cascading hardware blocks for common macro operations. It enhances system throughput by concurrently executing the macro operations. The staggered execution is to shift the operation timing of computation units of the parallel datapath. It improves system throughput and power efficiency by replacing complex  $N \times N$  crossbar switches with simple  $N \times 1$  switches.

The power efficiency of the proposed architecture is evaluated through a Verilog model and commercial tools. The proposed architecture consumes only 150 mW while providing W-CDMA 2Mbps packet data service.

The contributions of this thesis are to analyze the characteristics of baseband operations from the perspective of architecture and to adapt the three novel schemes for system enhancement. ©

Hyunseok Lee 2007

All Rights Reserved

To min, claire, and chloe

## TABLE OF CONTENTS

| DEDICATIO   | Ν                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ii |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| LIST OF FIG | URES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | vi |

| LIST OF TAI | BLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | х  |

| CHAPTER     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

| I. INTR     | ODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1  |

| II. PREI    | IMINARY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6  |

| 2.1         | Types of Wireless Communication Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6  |

| 2.2         | Evolution of Wireless Communication Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9  |

| 2.3         | Wireless Protocol Stack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11 |

| 2.4         | Skeleton of a Wireless Terminal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12 |

| 2.5         | Software Defined Radio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14 |

| III. ALGO   | ORITHM LEVEL WORKLOAD CHARACTERIZATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 16 |

| 3.1         | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 16 |

| 3.2         | Digital Baseband Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 16 |

| 3.3         | Major Computation Kernels of Baseband Workload                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 19 |

| 3.4         | Characteristics of Parallelizable Computation Kernels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 19 |

| 3.5         | Types of Macro Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 22 |

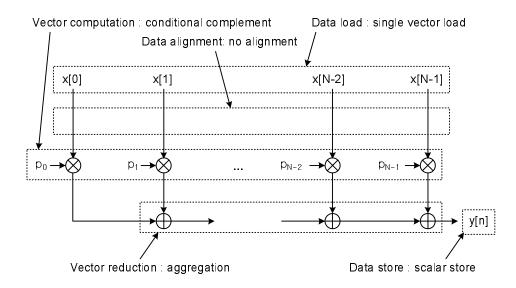

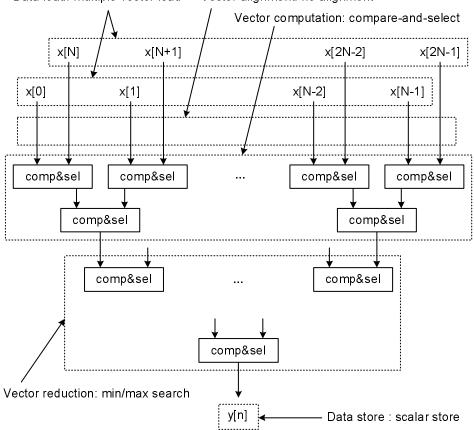

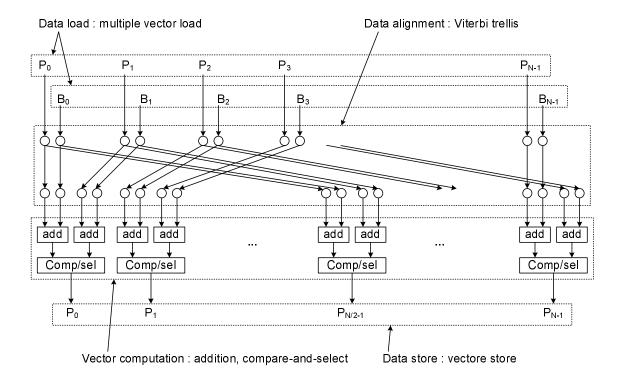

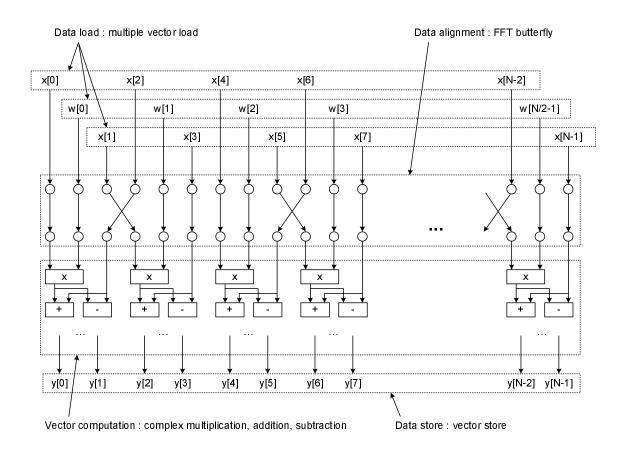

|             | 3.5.1 Data Load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 22 |

|             | 3.5.2 Data Alignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 23 |

|             | 3.5.3 Vector Computation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 27 |

|             | 3.5.4 Vector Reduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 27 |

|             | 3.5.5 Data Store                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 28 |

| IV SVST     | EM LEVEL WORKLOAD CHARACTERIZATION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|             | DMA     DMA <td>29</td> | 29 |

| 4.1         | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 29 |

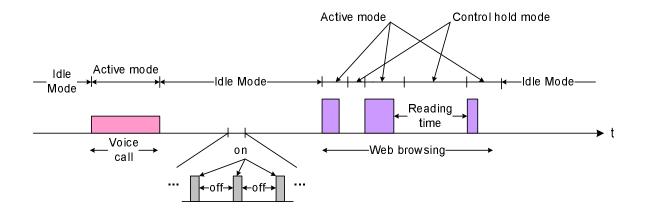

| 4.2      | Operation Modes of Wireless Terminal                      | 29 |

|----------|-----------------------------------------------------------|----|

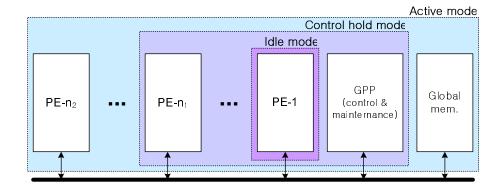

|          | 4.2.1 Characteristics of Active and Control Hold Modes    |    |

|          | Operations                                                | 30 |

|          | 4.2.2 Characteristics of Idle Mode Operations             | 31 |

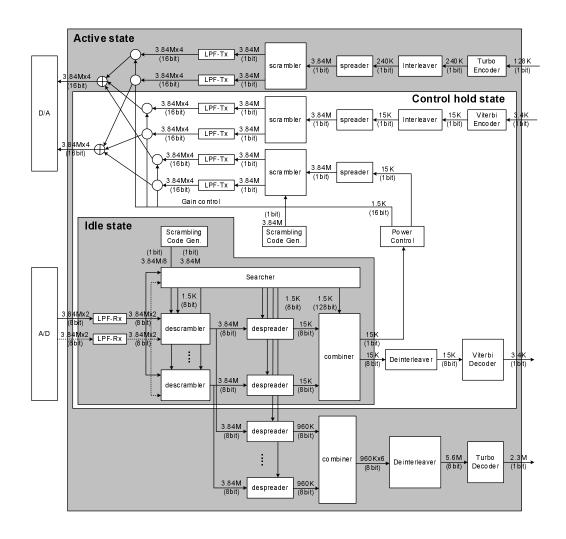

| 4.3      | A Case Study: W-CDMA Terminal                             | 32 |

|          | 4.3.1 Terminal Operation Condition                        | 33 |

|          | 4.3.2 System Block Diagram                                | 34 |

|          | 4.3.3 Processing Time                                     | 37 |

|          | 4.3.4 Peak Workload Profile                               | 38 |

|          | 4.3.5 Parallelism                                         | 39 |

|          | 4.3.6 Memory Requirement                                  | 40 |

|          |                                                           |    |

|          | I LEVEL ARCHITECTURE OF THE BASEBAND                      | 10 |

| PRO      | CESSOR FOR SDR                                            | 43 |

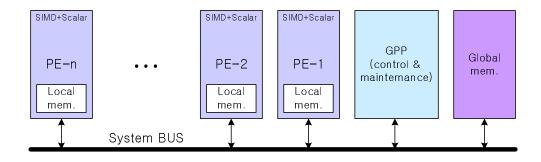

| 5.1      | Chip Multiprocessor                                       | 43 |

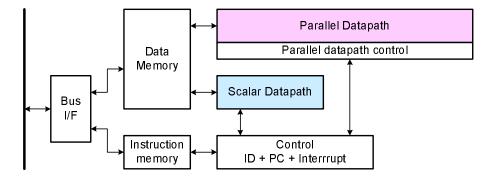

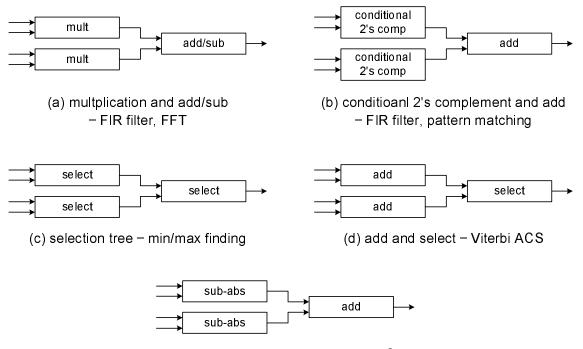

| 5.2      | Coarse Grain PE                                           | 45 |

| 5.3      | Homogeneous PE                                            | 46 |

| 5.4      | Low Speed BUS                                             | 46 |

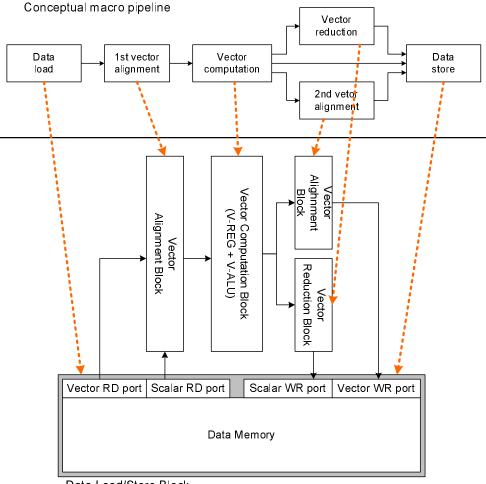

| 5.5      | Memory Hierarchy                                          | 47 |

|          | 5.5.1 Scratch Pad Memory                                  | 47 |

|          | 5.5.2 Hierarchical Memory                                 | 48 |

| 5.6      | SIMD+Scalar                                               | 49 |

| 5.7      | Support Wide Workload Variation                           | 51 |

|          |                                                           |    |

| VI. THE  | ARCHITECTURE OF PROCESSING ELEMENT                        | 53 |

| 6.1      | Previous Works                                            | 53 |

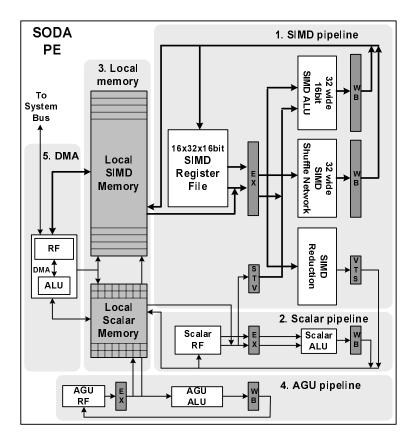

| 6.2      | SODA Architecture                                         | 57 |

| 6.3      | Motivations                                               | 58 |

| 6.4      | Novel Schemes for Power Reduction and Higher Throughput . | 60 |

|          | 6.4.1 Macro Instruction                                   | 60 |

|          | 6.4.2 Macro Pipelining                                    | 64 |

|          | 6.4.3 Staggered Execution of Computation Units            | 68 |

| 6.5      | Processing Element Design                                 | 72 |

|          | 6.5.1 High Level Architecture of Processing Element       | 72 |

|          | 6.5.2 Execution Examples in Two Operation Modes           | 79 |

|          | 6.5.3 Computation Units                                   | 83 |

|          | 6.5.4 Vector Reduction Unit                               | 84 |

|          | 6.5.5 Address Generators                                  | 86 |

|          | 6.5.6 Interconnection Networks                            | 86 |

| 6.6      | Programming Model                                         | 89 |

| 0.0      | 6 6 m · · · · · · · · · · · · · · · · ·                   |    |

| VII. POW | ER AND THROUGHPUT ANALYSIS                                | 92 |

| 7.1       | Experim  | ent Environment and Methodology         | 92  |

|-----------|----------|-----------------------------------------|-----|

|           | 7.1.1    | Component Level Evaluation Environment  | 92  |

|           | 7.1.2    | Kernel Level Evaluation Environment     | 93  |

|           | 7.1.3    | System Level Evaluation Environment     | 93  |

| 7.2       | Kernel L | evel Analysis                           | 94  |

|           | 7.2.1    | FIR filter                              | 94  |

|           | 7.2.2    | Pattern Matching                        | 95  |

|           | 7.2.3    | Minimum/Maximum Finding                 | 96  |

|           | 7.2.4    | Viterbi-BMC/ACS                         | 97  |

|           | 7.2.5    | FFT                                     | 98  |

| 7.3       | System I | Level Analysis: W-CDMA 2Mbps Workload   | 98  |

|           | 7.3.1    | Optimal Active Mode Operation Frequency | 98  |

|           | 7.3.2    | Idle Mode Support                       | 00  |

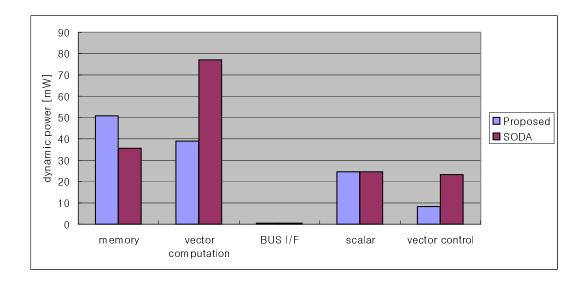

|           | 7.3.3    | Component Level Breakdown               | 02  |

|           | 7.3.4    | Comparison with SODA                    | 03  |

| 7.4       | Future S | DR Solution                             | .05 |

| VIII. CON | CLUSIO   | <b>N</b>                                | .08 |

| APPENDICE | S        |                                         | 14  |

| BIBLIOGRA | PHY      |                                         | 49  |

# LIST OF FIGURES

# Figure

| 2.1 | Types of wireless communication networks: WPAN, WLAN, WMAN, and WWAN                                                | 7  |

|-----|---------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Evolution history of WWAN systems                                                                                   | 9  |

| 2.3 | A simplified protocol stack of a wireless terminal                                                                  | 11 |

| 2.4 | Skeleton of a wireless terminal (3G cellular phone)                                                                 | 13 |

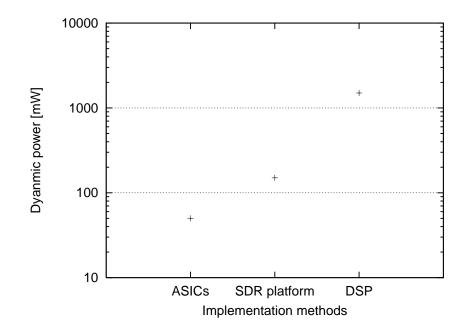

| 2.5 | Comparison of dynamic power consumption of ASICs, SDR plat-<br>form, and DSP                                        | 15 |

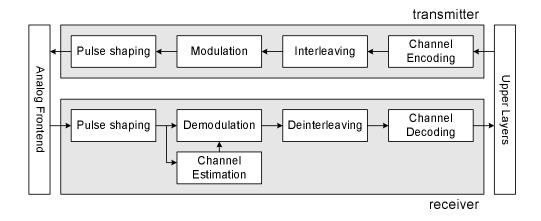

| 3.1 | Generalized block diagram of wireless terminal's digital baseband $\$ .                                             | 17 |

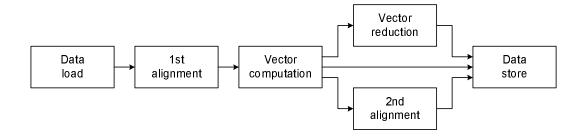

| 3.2 | A conceptual macro pipeline model which can describe the operation of all parallelizable kernels                    | 21 |

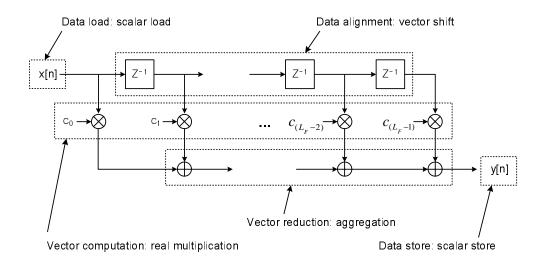

| 3.3 | Interpretation of the FIR filter kernel into the macro pipeline                                                     | 22 |

| 3.4 | Interpretation of the pattern matching kernel into the macro pipeline                                               | 23 |

| 3.5 | Interpretation of the min/max finding kernel into the macro pipeline                                                | 24 |

| 3.6 | Interpretation of the Viterbi-ACS kernel into the macro pipeline $\ .$ .                                            | 25 |

| 3.7 | Interpretation of the FFT kernel into the macro pipeline $\ldots$ .                                                 | 26 |

| 4.1 | The active, control hold, and idle modes of wireless terminals                                                      | 30 |

| 4.2 | Detailed block diagram of the W-CDMA physical layer when it provides the packet data service described in Table 4.1 | 35 |

| 5.1 | The high level architecture of the proposed baseband processor for<br>the SDR                                       | 44 |

| 5.2  | The skeleton of a PE, which has both scalar datapath and SIMD datapath                                                                              | 49 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.3  | The controlling of the number of active PEs according to terminal's operation state change                                                          | 51 |

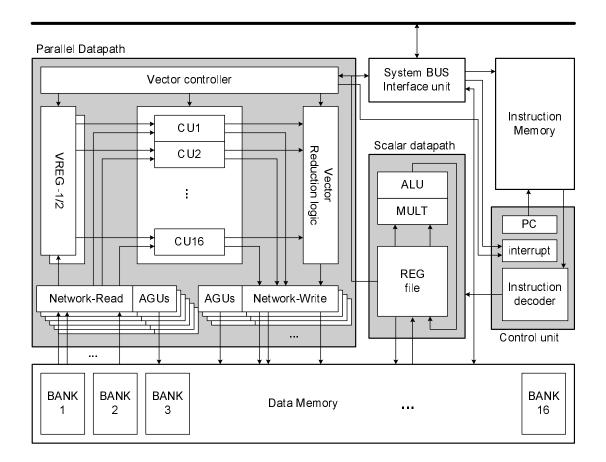

| 6.1  | Architecture of the SODA PE                                                                                                                         | 56 |

| 6.2  | Operation of major parallelizable kernels which can be represented<br>by macro instructions through concatenating arithmetic units                  | 62 |

| 6.3  | Conceptual macro pipeline and its mapping on real hardware, which consists of macro hardware blocks                                                 | 65 |

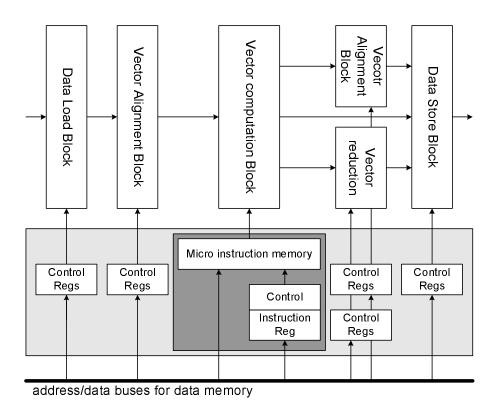

| 6.4  | The control scheme of the macro pipeline, which uses both control registers and CISC instructions                                                   | 66 |

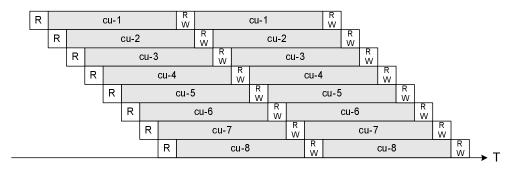

| 6.5  | The difference on the execution timing of CUs in (a) the synchronous operation mode and (b) the staggered operation mode $\ldots$ $\ldots$ $\ldots$ | 69 |

| 6.6  | Comparison of the effect on the staggering of workload having (a) short computations (b) long computations                                          | 70 |

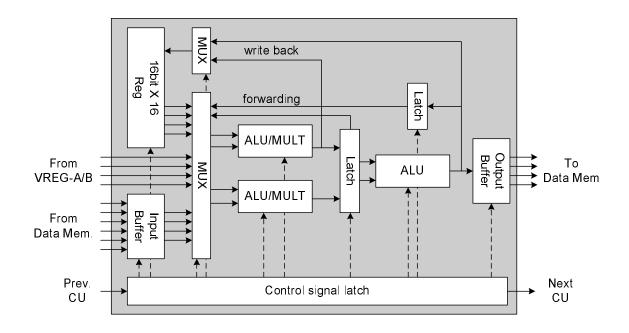

| 6.7  | High level architecture of PE                                                                                                                       | 72 |

| 6.8  | An example which shows the relation between the amount workload and the amount of input/output data                                                 | 74 |

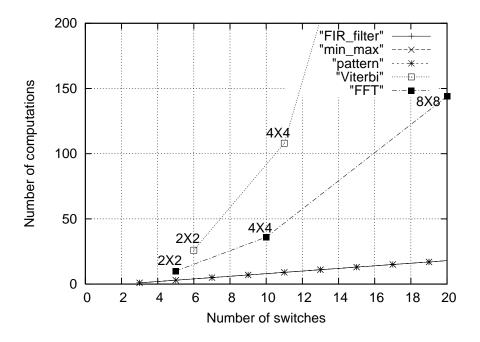

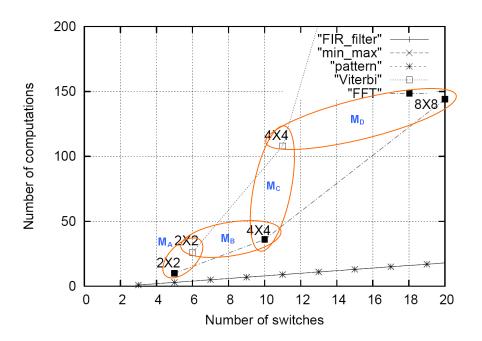

| 6.9  | The relation between the number of required switches for parallel data load/store and the number of computations done in a CU                       | 75 |

| 6.10 | Four possible workload mapping schemes                                                                                                              | 76 |

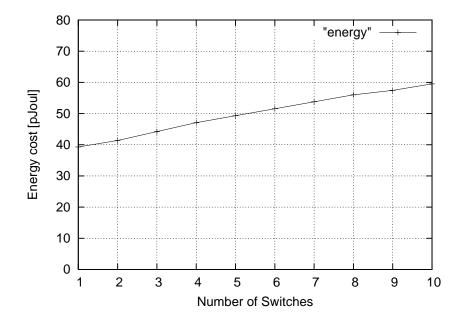

| 6.11 | The relation between the number of switches for parallel data load/store and the energy cost of switches                                            | 77 |

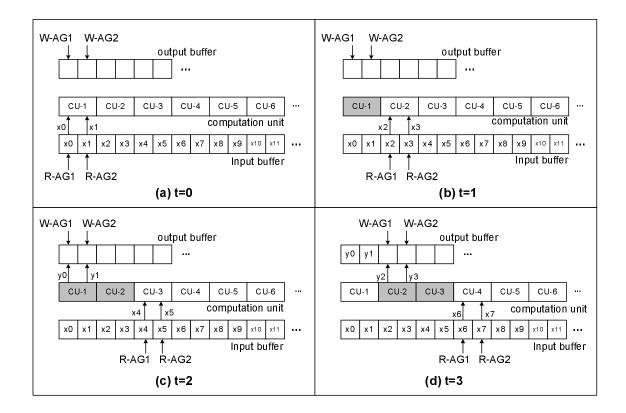

| 6.12 | The operation of PE in the staggered operation mode when it per-<br>forms the first stage of the radix-2 FFT operation                              | 79 |

| 6.13 | An example of the synchronous execution of PE when it performs 32-tap FIR filter operation                                                          | 82 |

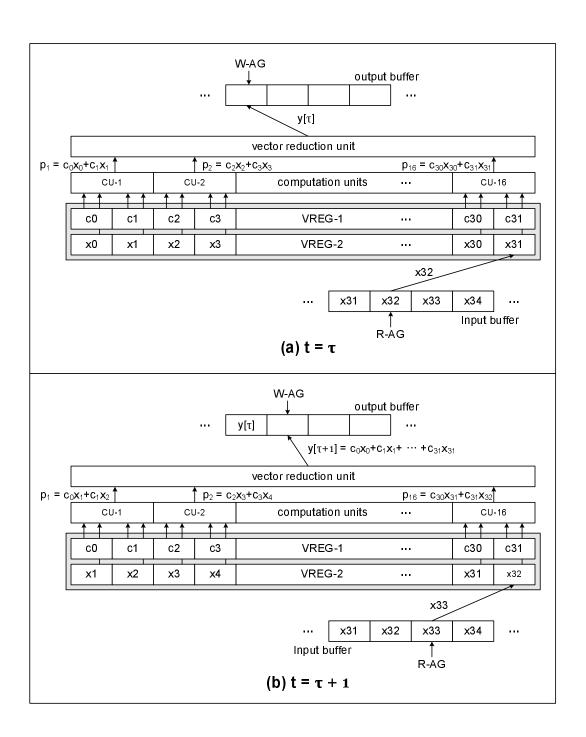

| 6.14 | The detailed architecture of the CU                                                                                                                 | 83 |

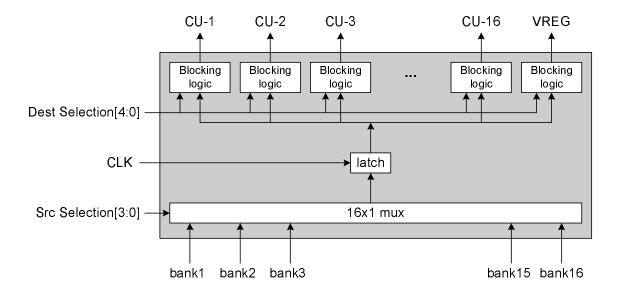

| 6.15 | Detailed architecture of the interconnection network for data load $% \mathcal{A}_{\mathrm{rel}}$ .                                                                        | 87  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

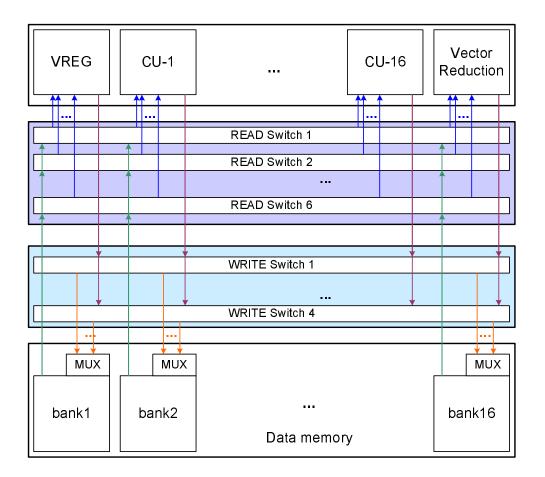

| 6.16 | Relation between the data memory, switches, and CUs $\ldots$ .                                                                                                             | 88  |

| 6.17 | An example of an application program for FIR filtering $\ldots$ .                                                                                                          | 90  |

| 6.18 | An example of a library routine for the FIR filtering                                                                                                                      | 91  |

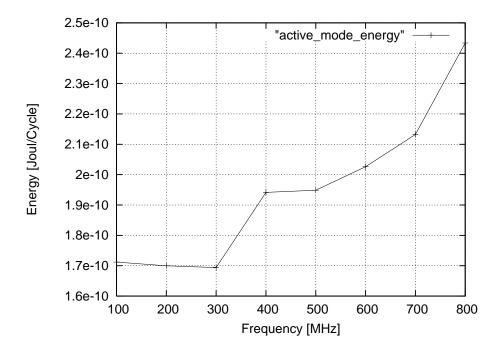

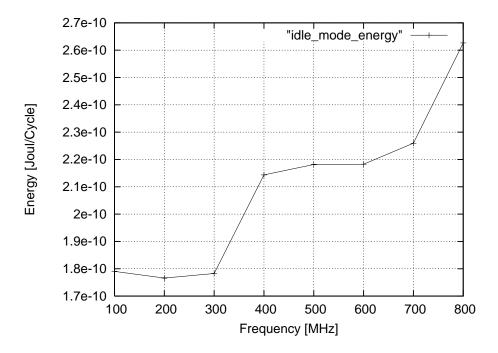

| 7.1  | The relation between the operation frequency and the system energy<br>per cycle, when the system provides the W-CDMA 2Mbps packet<br>data service                          | 99  |

| 7.2  | The relation between the operation frequency and the system energy per cycle, when the system is in the W-CDMA idle mode                                                   | 101 |

| 7.3  | Power comparison between the SODA and the proposed new architecture when they support W-CDMA 2Mbps packet data service                                                     | 104 |

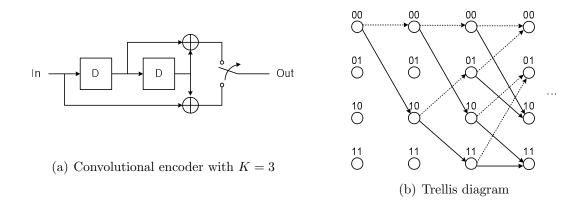

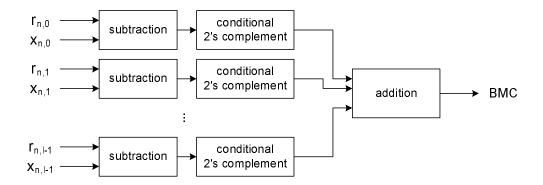

| A.1  | An example of the (a) a convolutional encoder with $K = 3$ and (b) corresponding trellis diagram                                                                           | 116 |

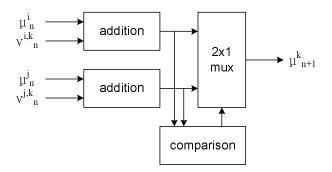

| A.2  | A representation of BMC operation as a combination of elementary arithmetic operations                                                                                     | 118 |

| A.3  | ACS operation in a trellis diagram                                                                                                                                         | 120 |

| A.4  | An implementation of the ACS operation with primitive arithmetic operations                                                                                                | 120 |

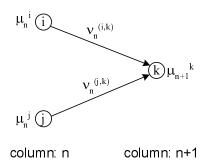

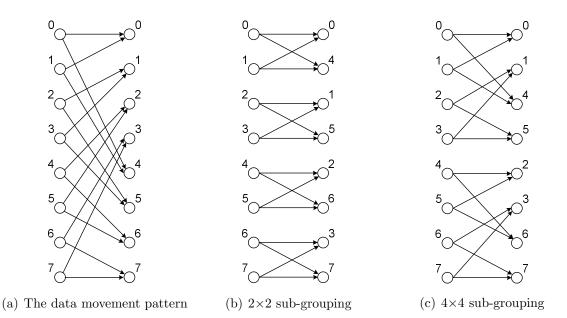

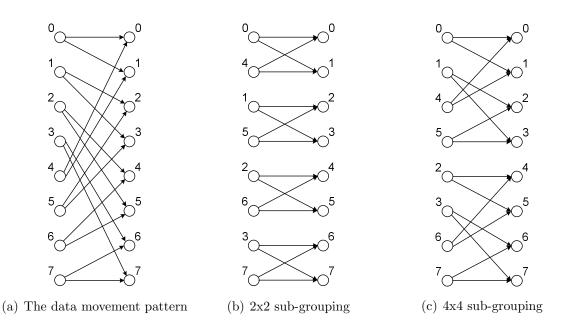

| A.5  | The data movement pattern of ACS operation when K=4 and sub-<br>grouping of ACS operation into smaller groups                                                              | 121 |

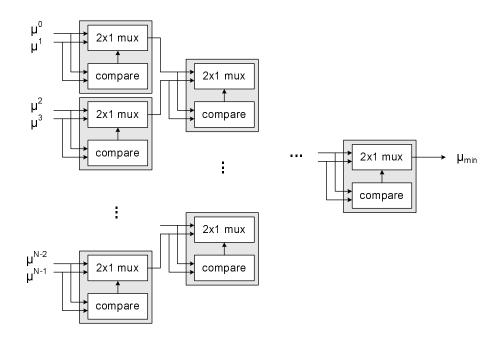

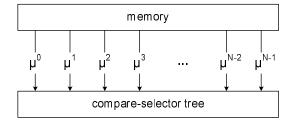

| A.6  | A compare-selector tree for the minimum value searching function of the ACS normalization procedure                                                                        | 123 |

| A.7  | The data movement pattern appearing in the minimum value search-<br>ing function of the ACS normalization procedure, after parallelizing<br>with the compare-selector tree | 124 |

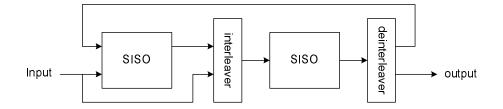

| A.8  | The structure of Turbo decoder                                                                                                                                             | 125 |

| A.9  | The data movement pattern of backward ACS operation when $K=4$ and sub-grouping of ACS operation into smaller groups $\ldots \ldots \ldots$                                | 128 |

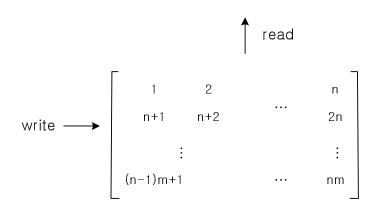

| A.10 | The operation of the block interleaver                                                                                                                                                                                                                             |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

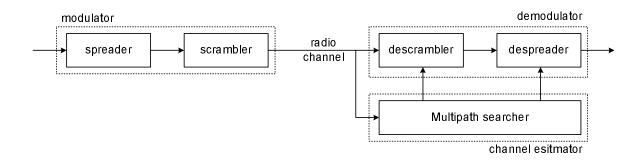

| A.11 | The structure of modulator and demodulator of CDMA based system130                                                                                                                                                                                                 |

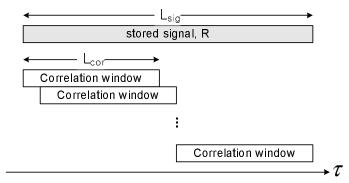

| A.12 | The correlation computation procedure of the multipath searcher .<br>. $134$                                                                                                                                                                                       |

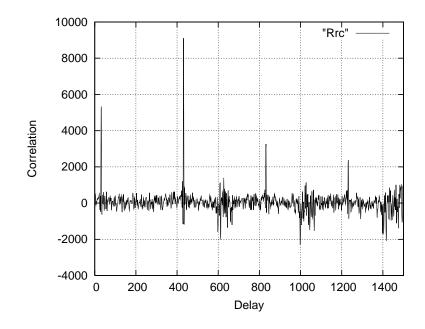

| A.13 | An example of the correlation results which shows four peaks 135                                                                                                                                                                                                   |

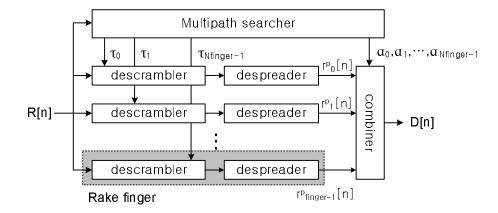

| A.14 | The structure of the rake receiver                                                                                                                                                                                                                                 |

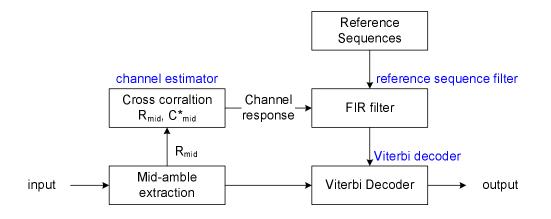

| A.15 | The structure of the MLSE equalizer for TDMA systems $\ . \ . \ . \ . \ 139$                                                                                                                                                                                       |

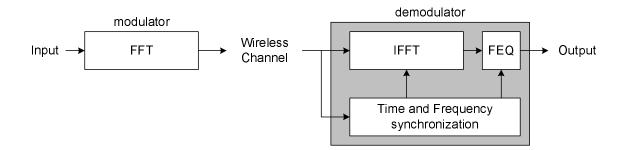

| A.16 | The outline of modulator and demodulator of an OFDMA based system                                                                                                                                                                                                  |

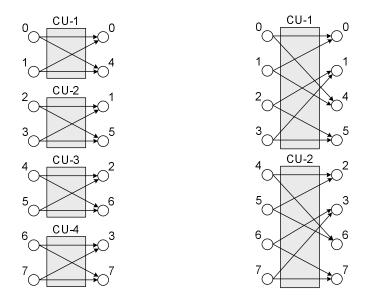

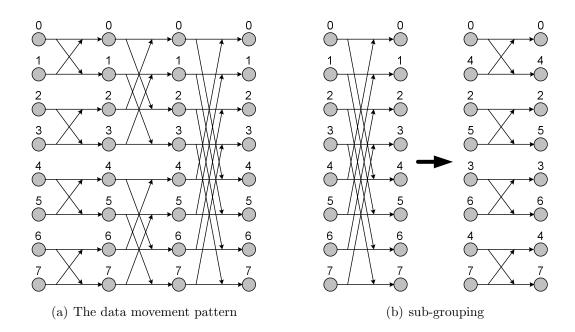

| A.17 | The data movement pattern of 8 points FFT operation and sub-<br>grouping of FFT operations into smaller groups                                                                                                                                                     |

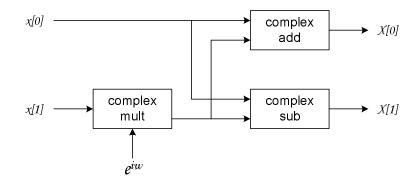

| A.18 | Computation pattern of radix-2 FFT operation                                                                                                                                                                                                                       |

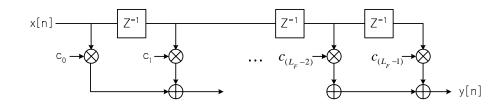

| A.19 | Two implementation ways of the FIR filter                                                                                                                                                                                                                          |

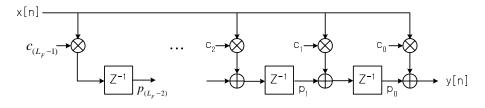

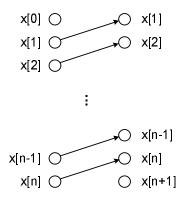

| A.20 | Data movement pattern of the FIR filter. $x[0], \ldots, x[n]$ are the stored<br>input data and $x[n+1]$ is a new input data $\ldots \ldots \ldots$ |

# LIST OF TABLES

### <u>Table</u>

| 3.1 | Major computation kernels comprising the baseband processing work-<br>load                                                                      | 20 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Characteristics of the parallelizable vector kernels in the baseband processing workload                                                        | 20 |

| 4.1 | Operation conditions of a W-CDMA terminal which are assumed for system level workload analysis                                                  | 33 |

| 4.2 | Processing time requirements of the W-CDMA physical layer                                                                                       | 36 |

| 4.3 | Peak workload profile of the W-CDMA physical layer and its varia-<br>tion according to the operation mode change                                | 38 |

| 4.4 | Parallelism available in the algorithms of the W-CDMA physical layer                                                                            | 39 |

| 4.5 | Memory requirements of the algorithms of the W-CDMA physical layer                                                                              | 41 |

| 6.1 | Power consumption of 16 bit datapath components which are implemented by 130 nm technology and run at 700 MHz                                   | 58 |

| 6.2 | Operation power profile of the SODA PE when it performs Viterbi decoder with K=7 and R= $1/3$ , and 64-wide FFT operation                       | 58 |

| 6.3 | Operation cycle profile of SIMD based architecture when it performs Viterbi decoder with $K=7$ and 64-wide FFT operation $\ldots \ldots \ldots$ | 59 |

| 6.4 | Operation cycle count comparison between the datapath with macro instructions and without macro instructions                                    | 63 |

| 6.5 | Macro and primitive instructions of the CU                                                                                                      | 85 |

| 7.1 | Comparison of the throughput and energy consumption of the pro-<br>posed architecture with the SODA, when they perform the FIR filter<br>kernel                | 95 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 7.2 | Comparison of the throughput and energy consumption of the pro-<br>posed architecture with the SODA, when they perform the pattern<br>matching kernel          | 96 |

| 7.3 | Comparison of the throughput and energy consumption of the pro-<br>posed architecture with the SODA, when they perform the mini-<br>mum/maximum finding kernel | 96 |

| 7.4 | Comparison of the throughput and energy consumption of the proposed architecture with the SODA, when they perform the Viterbi-BMC/ACS kernel                   | 97 |

| 7.5 | Comparison of the throughput and energy consumption of the pro-<br>posed architecture with the SODA, when they perform the FFT kernel                          | 98 |

| 7.6 | Dynamic power consumption of the proposed architecture when it provides W-CDMA 2Mbps packet data service                                                       | 02 |

### CHAPTER I

# INTRODUCTION

In the near future, we will use intelligent devices that include the functionalities of most hand held devices such as tablet computers, cellular phones, MP3 players, game consoles, etc [1][2]. In order to maximize the efficacy of this future device, it is crucial to provide a seamless wireless connection without any spatial or time limitation. However, in reality, it is not easy to provide such seamless wireless connection because there have been no wireless networks that cover the entire world.

A key technology that enables seamless wireless inter-connectivity is software defined radio (SDR). SDR is a wireless communication system whose function blocks are implemented by flexible software routines instead of fixed hardware, so various wireless protocols can be easily supported on the same platform [3]. An SDR terminal adaptively changes its operation mode according to the type of available wireless network. The concept of the SDR originated in the military, but now it is emerging as important commercial technology. For instance, 4G, the next generation of cellular phone networks, requires that multiple wireless protocols be supported within a single terminal [4].

Although the concept of the SDR is very attractive, there exist many obstacles on the way to its commercialization. High computation capability, tight power budget, and high degree of programmability are quite difficult goals to achieve simultaneously. The amount of computation required for a wireless terminal to perform baseband signal processing is above several tens giga operations per second (GOPS) level. The power allowed for baseband signal processing must be lower than several hundred mW in order to be used for commercial purposes [5]. Furthermore, the programmability needed for the execution of various wireless protocols tends to undermine the power efficiency of a hardware system.

There have been many architectures for SDR. The SandBluster [6] of SandBridge is a chip multiprocessor system which supports multi-threading in the hardware level and its core has a narrow single instruction multiple data (SIMD) datapath. The PicoArray [7] of PicoChip is a multiple instruction multiple data (MIMD) style processor array. It is only suitable for base stations with loose power constraints because of its high power consumption caused by having individual control logics in each core. There are two architectures based on wide-SIMD datapath, SODA from Michigan [8] and the EVP from Phillips [9]. However, the throughput and power performance of these architectures are not sufficient to meet the requirements of emerging high speed wireless networks, such as WiMax and W-CDMA high speed downlink packet access (HSDPA).

The main topic of this thesis is to design a programmable digital hardware system that can support all the major wireless protocols while satisfying the three requirements of the SDR: high computation capability, low power consumption, and programmability. For this purpose, this thesis fulfils the design of an SDR platform with two underlying guidelines. One is to fully exploit all available parallelism existing in the baseband signal processing in order for both high computation capability and low power consumption. Another is to limit the programmability of the hardware system, such that it minimally satisfies the flexibility requirement, in order to minimize power burden induced by allowing programmability. However, these design guidelines are reasonable only when the workload characteristics of the applications are properly analyzed. Thus, as a first step, this thesis analyzes the characteristics of major signal processing algorithms which comprise the baseband operation of most contemporary wireless communication networks [10][11][12][13][14][15].

Workload characterization was done at two levels, the system and individual algorithms. System level characterization helps high level design decisions such as the granularity of processing elements (PE), number of PEs, memory hierarchy, and interprocess communication mechanism. As a representative system, this thesis models the physical layer of the W-CDMA and derives many design data, such as dominant computation kernels, peak workload, the range of workload variation, and communication pattern between computation kernels. The results from the algorithm level characterization is used to determine the design of the PE. This thesis analyzed the operation of major algorithms that dominate the baseband processing workload, such as Viterbi decoder, Turbo decoder, and modulation/demodulation schemes, of time division multiple access (TDMA), code division multiple access (CDMA), and orthogonal frequency division multiple access (OFDMA) systems.

On top of these workload characterization results, this thesis proposes a coarse gain chip multiprocessor architecture whose one PE contains both a parallel and scalar datapath. All PEs are interconnected by a low speed bus. A chip multiprocessor architecture allows the utilization of the algorithm level parallelism of the baseband operation. Coarse grain PEs minimize power expensive global communication. Thus, low speed buses are sufficient to cover the communication traffic between PEs. Having both parallel and scalar datapaths within each PE allows a power efficient operation by minimizing the number of data copies for the communication between the parallel and scalar datapath.

For the parallel datapath of a PE, this thesis applies three novel schemes to improve its throughput and power efficiency: macro instructions, macro pipelining, and staggered execution of computation units (CU). Macro instructions combine several instructions into one. The use of macro instructions is power efficient due to the minimizing of the number of power consuming register file accesses. Macro pipelining cascades macro hardware blocks of data load/store, data alignment, and computations. As we will show in the chapter for the algorithm level workload characterization, major parallelizable computation kernels can be modeled as the combination of data load/store, data alignment, and computations. Thus, macro pipelining allows us to exploit the macro operation level parallelism which was not utilized by previous SDR solutions based on the thread, instruction, and data level parallelism (DLP). Staggered execution shifts the operation timing of computation units in the parallel datapath. Because only one CU needs input data at a time, it is possible to use an  $N \times 1$  network for feeding input data to an N wide parallel datapath instead of complex and power consuming  $N \times N$  network. These three novel schemes result in good power and throughput performance compared to previous architectures. Experimental results show that the proposed architecture consumes about 150 mW while supporting W-CDMA 2Mbps packet data service.

For component level power information, this thesis builds a hardware model with Verilog and synthesizes the hardware model with Synopsys' Physical Compiler using the TSMC-13 standard cell library which is based on 0.13 micron technology. Additionally, this thesis uses Artisan's memory compiler for the generation of storage components, such as register files and data memory. Synopsys' PrimePower tool is also used for the power evaluation in the gate level. This thesis also builds a system level power evaluation tool that uses component level power information and executable code as input for system level power evaluation.

The organization of this thesis is as follows. In Chapter II, this thesis discusses preliminary topics, which are required to explain the detail operation of wireless terminals. In Chapter III, the physical layer operations of wireless communication systems are broken down into the algorithmic level. In Chapter IV, this thesis analyzes the characteristics of physical layer operations in the system level. Based on workload analysis results, this thesis proposes an architecture for a baseband processor in Chapter V and VI. In Chapter VII, this thesis shows power and throughput evaluation results. Finally, Chapter VIII concludes this thesis. In Appendix, it is possible to see detail discussion on the characteristics of baseband processing algorithms.

### CHAPTER II

# PRELIMINARY

Prior to detailed discussion, several preliminary issues are explained in this chapter. The explanation will include the evolution history, types, and protocol stack hierarchies of wireless networks. In addition, a generalized model of physical layer operations is also explained. Understanding of these issues is important to validate the design decisions made on the proposed architecture for SDR application.

### 2.1 Types of Wireless Communication Networks

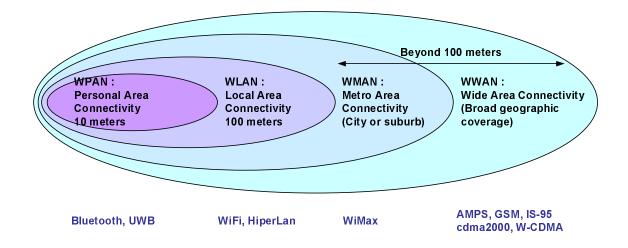

According to the required range of network coverage, it is possible to classify wireless communication networks into four types as shown in Figure 2.1 [16]: wireless personal area networks (WPAN), wireless local area networks (WLAN), wireless metro area network (WMAN), and wireless wide area networks (WWAN). The operation procedure of these networks differ greatly because of application specific optimization.

The WPAN enables users to connect to various personal devices over short distances without wires. An application might be synchronizing data between a personal data assistant and a desktop computer. Bluetooth is the most popular system at the moment [17]. Ultra wide band is one emerging technology which is applicable

Figure 2.1: Types of wireless communication networks: WPAN, WLAN, WMAN, and WWAN

for the WPAN [18]. One unique characteristic of the WPAN is its simple operation scenario compared to other wireless networks. This characteristic is a result of an effort to minimize production cost. Because the WPAN needs to be built on any kind of consumer electronic device, low production cost is crucial. Because of such a low implementation cost, even single mode wireless terminals have WPAN interfaces as a default feature.

WLAN originated from wired local area network (LAN). It aims to replace existing wired LAN by high speed wireless channels. A typical terminal of this type of wireless networks is a laptop computer having wireless access. IEEE 802.11/a/b/g, usually called as WiFi, are the most popular WLAN systems [19]. HiperLan is the European standard for the WLAN. However, it become a minor standard supported by very limited companies. The characteristics of the WLAN are its high data rate and limited terminal mobility support. The narrow network coverage of the WLAN results in higher data rate (up to 100 Mbps) compared to other types of wireless networks having wider coverage. Because there are no organizations who manage inter-operability of WLAN access points, the control procedure for mobility support defined in WLAN specification has no significant meaning in practice. Thus, one fundamental shortcoming of WLAN is limited coverage.

In metro areas, WMAN could be optimal. Originally this network was designed to replace roughly one mile range optical cables between end users and network router, last mile problem [20]. Installing optical link to all subscribers is economically inefficient because of the low utilization of optical links. WMAN can provide a similar level of network throughput with lower cost by replacing expensive optical cables with wireless link. IEEE 802.16 is the most common WMAN system. It has been evolved to support even mobile terminals in addition to fixed terminals [15].

WWAN evolved from telephone networks. The early generations of WWAN such as AMPS, GSM, and IS-95 provide voice service. The 3rd generation systems, called 3G, provide multimedia services such as video telephony on wireless channels. The CDMA-2000 [21] and W-CDMA [12] systems are typical examples. One characteristic of the WWAN is the support of relatively lower data rate but better terminal mobility. Usually the WWAN covers an entire country or continent. For complete mobility support with low equipment cost, a cell of this network covers wider area and consequently the allowed maximum data rate is usually lower than other networks.

Because network coverage and available maximum data rate are different, the optimal network varies according to operation environment. In building environments such as an office, the WLAN may be optimal for data service. In rural area, the WWAN may be optimal because of its wide coverage. At the street of metro area, the WMAN can be optimal. As we mentioned before, in the near future, end users will need terminals that can support above protocols to seamless span WPANs,

Figure 2.2: Evolution history of WWAN systems

WLANs, WMANs, WWANs, plus their future derivatives. Such a variety of network types lead us to develop a flexible hardware system that can run many wireless protocols.

### 2.2 Evolution of Wireless Communication Networks

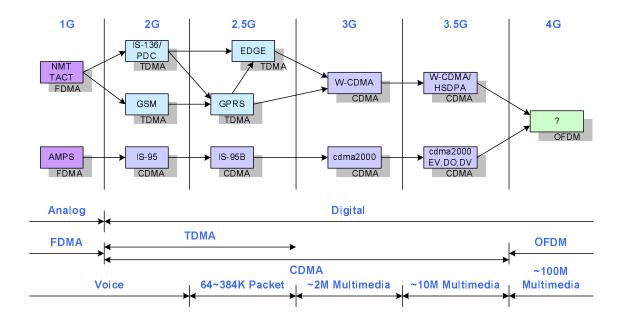

In the previous subsection, we saw that there exist many different types of wireless networks. However, even for the same type of wireless network, there exist different generations because wireless networks continuously evolve in order to provide better service by adapting new technologies. As an example, Figure 2.2 depicts the evolution history of the WWAN.

The first generation of the WWAN provides voice service. The system of this generation relied on analog communication technology and consequently its network

capacity is much lower than that of successors. The second generation WWAN increases its network capacity by adapting more advanced digital communication technologies such as TDMA and CDMA. The goal of the 2.5th generation WWAN was to provide packet data service in addition to voice service. Furthermore, the 3rd generation WWAN targets 2 Mbps multimedia service including voice service, video telephony, and high speed internet access over wireless channel. From this generation, the CDMA technology is adapted for all kinds of WWANs. The 3.5 generation WWANs additionally define 10 Mbps level high speed packet channels on the existing 3G systems. The high speed channels are designed to compete with the WMAN and WLAN that can provide high speed link in building environment. Until now, there is no specification for the 4th generation WWAN. However, it is commonly predicted that OFDMA and multiple input multiple output (MIMO) technologies will be key ingredient of the 4th generation WWAN.

From the evolution history of the WWAN, we can see that, even for a same service such as voice, there exist many different network generations, and within the same network generation, there exist many specifications based on different communication technologies. Such diversity limits the coverage of the WWAN and a similar situation also exists at other type of networks. For example, most European countries use the GSM system but in USA both GSM and IS-95 systems are used for voice service. Thus, the subscriber of IS-95 system in USA can not be served in Europe with the same phone. Therefore, the evolution of wireless network also leads us to develop a flexible wireless terminal that can support all network generations and communication technologies.

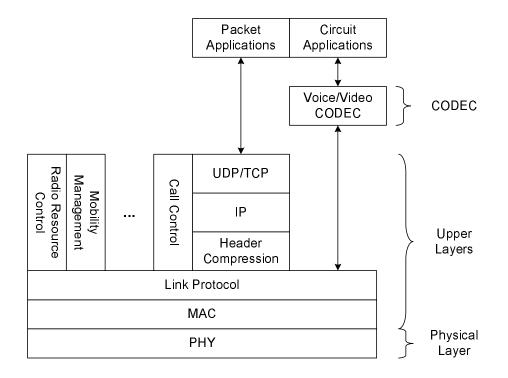

Figure 2.3: A simplified protocol stack of a wireless terminal

#### 2.3 Wireless Protocol Stack

As shown in Figure 2.3, we can divide the protocol stack of a wireless terminal into two categories according to workload characteristics: the physical layer and the upper layers. The operation of the physical layer is related to overcoming unreliable wireless channel characteristics and maximizing the efficiency of expensive wireless spectrum. The physical layer consists of computationally intensive signal processing algorithms.

In contrast, the upper layer protocols consist of control intensive operations. Medium access control (MAC) resolves contention between terminals who share wireless channels. The link protocol performs control actions required to retransmit corrupted frames. In addition to data transmission and reception, many control actions are performed in the upper layers. Radio resource control dynamically assigns and releases radio resource for terminals according to their operation state. Mobility management performs control actions for terminal handover procedure between basestations. Call control covers call generation and termination procedures.

According to application types, different protocol paths are used. For packet data applications such as web browsing, TCP/IP protocols are used for end to end data transmission over an IP network. In circuit applications, after the link layer, frames are directly forwarded to coder/decoder (CODEC) because no retransmission is allowed in the circuit application due to tight time budget. Between user applications and link protocol, video or voice CODEC can be placed. The function of CODEC is to minimize the amount of transmitted information by removing redundancy and to recover original information. MPEG coding/decoding is an example of the CODEC operation.

#### 2.4 Skeleton of a Wireless Terminal

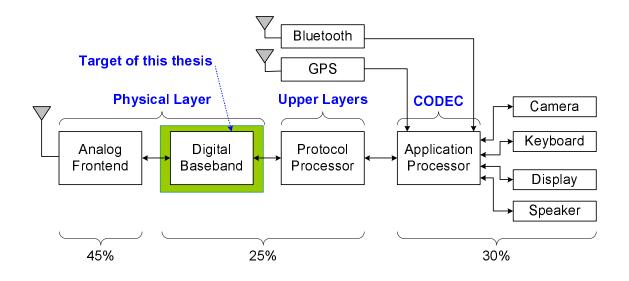

As shown in Figure 2.4, a wireless terminal can be implemented with four major blocks: analog frontend, digital baseband, protocol processor, and application processor. The physical layer of wireless protocol is mapped on both the analog frontend and digital baseband. The upper layers of wireless protocol are mapped on the protocol processor. Application processor covers the CODECs.

The operation of the analog frontend is to place a baseband signal on the carrier frequency band and vice versa. Because state-of-art digital circuit can not process a GHz level signal with reasonable power consumption, it is common to implement this block with analog ASICs. The digital baseband block performs the remaining physical layer operations. Due to the tight power budget and high computation

Figure 2.4: Skeleton of a wireless terminal (3G cellular phone)

requirements, it is common to implement the digital baseband in digital ASICs. Meanwhile, the operation of upper layer protocols can be represented as a finite state machine whose state transitions are initiated by external control messages or internal events. Thus, the protocol processor block is implemented in a form of general purpose processor (GPP) except for some hard realtime operations such as MAC response generation and encryption/decryption. The application processor also requires many computations. In order to achieve flexibility and high performance at the same time, a GPP with accelerators is a common implement method.

As shown in Figure 2.4, the analog frontend circuits is a primary power dissipator in wireless terminal. The analog frontend, application processor with other user interface units, and baseband processor correspondingly consume about 45, 30, and 25% of 3G cellular phone power [22].

Among the four major blocks in Figure 2.4, the ASIC based analog frontend and

digital baseband are within the scope of the SDR. However, this thesis only focuses on the architecture of digital baseband processor.

#### 2.5 Software Defined Radio

The SDR is to implement all functional blocks of wireless communication systems with software routines and programmable hardware instead of inflexible ASICs. It enables the support of many wireless protocols without specialized hardware because a simple software routine change is enough for switching to other wireless protocols.

Because wireless communication systems consist of basestations and wireless terminals, the physical layer of both sides can be implemented in the form of the SDR. Battery powered terminals have more strict power constraint compared to AC powered basestations. So, the realization of SDR concept on wireless terminals is more difficult.

The SDR is advantageous to all bodies related to wireless communication systems. At first, it reduces the development time and cost of manufacturers. By reusing identical hardware platform for many terminals with different protocols, it is possible to reduce the time to market and development cost. Second, the SDR allows service providers to upgrade infrastructure without substantial cost. Most wireless protocols continuously upgrade to provide better services. So, if a system was not designed with SDR concept, service providers need to change the hardware of infrastructure to cope with such protocol evolution. A typical example is the addition of HSDPA channel on W-CDMA protocol. By adding this channel, the maximum data rate of W-CDMA protocol is increased from 2 Mbps to 14 Mbps. Third, the SDR provides seamless wireless connections to end users with one wireless terminal. This service is one of key features of 4G wireless communication systems.

Figure 2.5: Comparison of dynamic power consumption of ASICs, SDR platform, and DSP

A fundamental challenge in a hardware system for the SDR is to overcome the inefficiencies in power and throughput caused by increasing the flexibility required for supporting multiple protocols. Thus, special purpose circuits for single protocol exhibit the best power and throughput performance, whereas fully programmable hardware such as DSP shows the worst performance. The performance of SDR platforms is placed between these two extremes. This relation is depicted in Figure 2.5. In this graph, we compare the dynamic power consumption of ASICs, SDR platforms, and DSP under identical workload<sup>1</sup>

<sup>&</sup>lt;sup>1</sup>We assume 2Mbps turbo decoder workload where code rate R=3. the power data of ASICs is from [23], that of SDR platform is from the experiment results shown in Chapter VII, and that of DSP is from [24][25].

### CHAPTER III

# ALGORITHM LEVEL WORKLOAD CHARACTERIZATION

#### 3.1 Introduction

In this chapter, this thesis analyzes the characteristics of signal processing algorithms comprising baseband processing workload. From the view point of computer architecture, this thesis identifies the computation and data movement patterns of major signal processing algorithms because these patterns have directly impacts processor architecture. Although detailed characterization was done, this chapter only contains analysis results to avoid distracting from the main topic of this thesis, the design of baseband processor architecture. Detailed analysis results can be found in Appendix.

#### 3.2 Digital Baseband Operations

The detail operation of the digital baseband is quite different according to the type of communication technologies. However, according to their role, it is possible to model the operation of the digital baseband into the combination of five function blocks as shown in Figure 3.1: channel coding/decoding, block interleaving/deinterleaving, modulation/demodulation, channel estimation, and pulse shap-

Figure 3.1: Generalized block diagram of wireless terminal's digital baseband

ing.

The function of a channel coding/decoding block is forward error correction. Because wireless channels are very unreliable, some of a received signal is corrupted while propagating through wireless channel. The channel coding/decoding makes it possible to correct the corrupted signal at the receiver without retransmission. The channel coder in the transmitter adds systematic redundancy on the transmitting information and the channel decoder in receiver exploits this redundant information to correct the corrupted signal. Among many existing channel coding schemes, Convolutional code and Turbo code are widely used at most wireless communication networks [26]. For the decoding of these codes, Viterbi algorithm is most widely used [27]. Recently low density parity check (LDPC) codes have begun to be adapted in wireless communication networks [28].

Interleaving/deinterleaving is used to overcome burst errors occurring within short time interval. In wireless channel, abrupt changes of channel quality are frequently observed and the channel decoder shows bad performance at such burst error patterns. Block interleaving/deinterleaving minimizes the effect of burst errors by scattering error signal over longer time interval.

Modulation<sup>1</sup> is a procedure to map input information bit sequence on specially designed signal waveforms. Demodulation is a procedure to estimate transmitted information bit sequence from received signal waveform. Because the transmitted signal is distorted by a wireless channel, it is required to estimate wireless channel characteristic for better demodulation performance. Popular modulation/demodulation schemes are TDMA, CDMA, and OFDMA.

The channel estimator in receiver measures the characteristics of wireless channel and provides the estimation result to the demodulator. Because a wireless channel is a time varying random function, channel estimators need to measure channel characteristics periodically. In CDMA systems, multipath searcher is used for channel estimation [29]. In TDMA systems, although various estimation algorithms are used for this purpose, maximum likely sequence estimation (MLSE) algorithm is most popular among them [30]. However, in OFDMA systems, a simple channel estimator is enough in receiver because OFDM symbol is inherently robust to the signal distortion caused by the wireless channel.

Pulse shaping is required to convert binary digital information into a frequency limited signal [31]. A binary impulse train, which is used in the digital baseband, is a signal with infinite frequency bandwidth. However, the frequency band, which is allowed for practical communication networks, is limited. In transmitters, the pulse shaping suppresses signal terms out of the allowed frequency band such that the interference to other channels is minimized. However, at receiver, the pulse shaping filter suppresses nose signal power through matched filtering<sup>2</sup>.

<sup>&</sup>lt;sup>1</sup>Modulation and demodulation discussed in this section are not the operations performed in analog frontend, that place signal from baseband to carrier band and vice versa.

$<sup>^{2}</sup>$ It is to compute a convolution between the received signal and the complex conjugate of the signal waveform used for the pulse shaping at the transmitter.

#### 3.3 Major Computation Kernels of Baseband Workload

As a first work, this thesis identifies major computation kernels of baseband workload, and the results are summarized in Table 3.1. From this table, it is possible to observe two important characteristics of the baseband workload. First, the baseband operation is the mixture of parallelizable and sequential workloads. Second, the number computation kernels is limited. Table 3.1 shows there exist only 6 parallelizable vector kernels and 8 scalar kernels. Detailed explanations on all kernels can be found Appendix.

At the case of parallelizable vector kernels, their computation pattern and data movement patterns are almost deterministic. However, some scalar kernels can be implemented with many different ways. In other word, the scalar kernels demand higher level of flexibility than the parallelizable vector kernels.

Thus, it is possible to conclude that either pure parallel architecture or pure scalar architecture is not appropriate for the baseband processing. Defining two datapaths, one for parallelizable vector kernels and the other for scalar kernels, will be useful for improving the power efficiency and throughput of system.

#### 3.4 Characteristics of Parallelizable Computation Kernels

In this subsection, we further discuss the characteristics of parallelizable kernels in order to derive hardware design information. As we will see in next chapter, the parallelizable kernels dominate the baseband workload. So, more intensive analysis is required for efficient system design.

We found that the operation of all parallelizable kernels can be described as a combination of the following macro operations: data load, data alignment, vector computation, vector reduction to scalar, and data store.

| Key Kernels        | Vector/Scalar | Vector Width | System Type                         | Function Block                                                |

|--------------------|---------------|--------------|-------------------------------------|---------------------------------------------------------------|

| FIR filter         | vector        | 6-320        | TDMA,CDMA,OFDMA                     | TDMA,CDMA,OFDMA   pulse shaper, channel estimator             |

| Pattern matching   | vector        | 16           | CDMA                                | synchronization                                               |

| min/max finding    | vector        | 32-10248     | TDMA, CDMA, OFDMA channel decoder   | channel decoder                                               |

| Viterbi-ACS        | vector        | 64-256       | TDMA,CDMA,OFDMA                     | TDMA,CDMA,OFDMA channel decoder, channel estimator            |

| Viterbi-BMC        | vector        | 64-256       | TDMA,CDMA,OFDMA                     | TDMA, CDMA, OFDMA channel decoder, channel estimator          |

| FFT                | vector        | 64-2048      | OFDMA                               | demodulation                                                  |

| Viterbi-TB         | scalar        | I            | TDMA,CDMA,OFDMA                     | TDMA,CDMA,OFDMA   channel decoder, channel estimator          |

| Interleaving       | scalar        | I            | TDMA,CDMA,OFDMA                     | TDMA,CDMA,OFDMA   interleaver, deinterleaver, channel decoder |

| Symbol mapping     | scalar        | I            | TDMA,CDMA,OFDMA                     | TDMA,CDMA,OFDMA modulator, demodulator                        |

| Channel encoding   | scalar        | I            | TDMA,CDMA,OFDMA channel encoder     | channel encoder                                               |

| Sliding window     | scalar        | I            | TDMA, CDMA, OFDMA   frame detection | frame detection                                               |

| Code generation    | scalar        | I            | CDMA                                | modulator/demodulator                                         |

| Interpolation      | scalar        | I            | OFDMA                               | demodulator                                                   |

| Frequency tracking | scalar        | I            | OFDMA                               | demodulator                                                   |

|                    |               |              |                                     |                                                               |

|   | oad                          |

|---|------------------------------|

|   | ğ                            |

| - |                              |

| - | sing workl                   |

|   | OL                           |

|   | ¥.                           |

|   |                              |

|   | 60                           |

|   | Ц                            |

| • | $\mathbf{S}$                 |

|   |                              |

|   | ຽ.                           |

|   | õ                            |

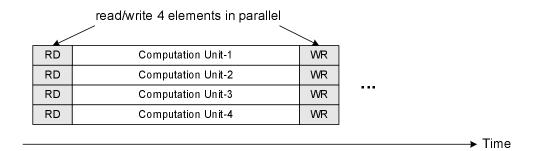

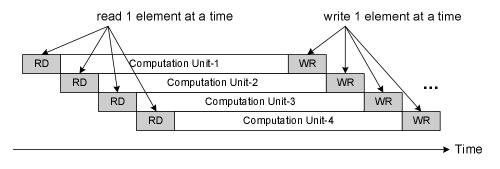

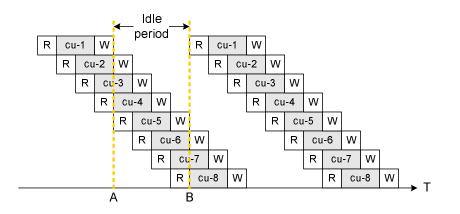

|   | OIO                          |