### FUNCTIONAL DESIGN VERIFICATION FOR MICROPROCESSORS BY ERROR MODELING

by

**David Van Campenhout**

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 1999

**Doctoral Committee:**

Professor Trevor Mudge, Chair Professor Richard B. Brown Professor John P. Hayes Professor Karem A. Sakallah

© David Van Campenhout 1999 All Rights Reserved To my parents.

### ACKNOWLEDGEMENTS

I would like to express my sincere appreciation to my advisor Trevor Mudge for his mentoring and guidance. Trevor has also given me broad freedom in my research and has been much more than just a research advisor. My appreciation and thanks also goes to John Hayes. Working with John has been a great learning experience. I would like to thank Karem Sakallah and Richard Brown for serving on my committee.

I would like to thank those who volunteered their time and effort to participate in our error collection effort: Hussain Al-Asaad, Todd Basso, Mary Brown, Juan Antonio Carballo, Subhachandra Chandra, Robert Chappell, Jim Dundas, David Greene, Jonathan Hauke, Rohini Krishna Kaza, Michael Kelley, Matt Postiff, and Steve Raasch.

I thank my friends and colleagues in ACAL: Hussain Al-Alsaad, Jeff Bell, I-Cheng Chen, Brian Davis, Jim Dundas, Jonathan Hauke, Tom Huff, Jim Huggins, Hyungwon Kim, Keith Kraver, Victor Kravets, Chih-Chieh Lee, Charles Lefurgy, João Paulo Marques da Silva, Phiroze Parakh, Steeve Raasch, Mike Riepe, Mike Upton, and Hakan Yalcin. These individuals together with the faculty provided an intellectually stimulating environment where it was also fun to work. I will never forget Tim Stanley who left us much too early. I am grateful for several close friends I met during my years in Michigan and hope that they will continue to be part of my life.

My deepest appreciation goes to my parents for their unconditional love and encouragement. I am grateful to my brothers for their understanding.

I would like to acknowledge the Belgian American Educational Foundation for having given me the opportunity to study in the US and supporting my first year of study.

## **TABLE OF CONTENTS**

| DEDICATION         | ii   |

|--------------------|------|

| ACKNOWLEDGEMENTS   | iii  |

| LIST OF FIGURES    | vi   |

| LIST OF TABLES     | viii |

| LIST OF APPENDICES | ix   |

| CHAPTER            |      |

| 1. |     | Introduction                                           | 1  |

|----|-----|--------------------------------------------------------|----|

|    | 1.1 | Microprocessor design                                  | 2  |

|    | 1.2 | Functional verification                                | 5  |

|    | 1.3 | Test generation for FDV                                | 8  |

|    | 1.4 | Checking the outcome of a simulation                   | 11 |

|    | 1.5 | Measuring and predicting functional quality            | 13 |

|    | 1.6 | Related area: physical fault testing                   | 18 |

|    | 1.7 | Related area: software testing                         | 20 |

|    | 1.8 | Thesis outline                                         | 23 |

| 2. |     | Design error data                                      | 26 |

|    | 2.1 | Published error data                                   | 26 |

|    | 2.2 | Collection method                                      | 28 |

|    | 2.3 | Collected error data                                   | 30 |

|    | 2.4 | Guidelines for implementing an error collection system | 37 |

|    | 2.5 | Discussion                                             | 39 |

| 3. |     | Design error models                                    | 41 |

|    | 3.1 | Error model requirements                               | 41 |

|    | 3.2 | Design error models                                    | 42 |

|    | 3.3 | Number of error instances defined by error model       | 45 |

|    | 3.4 | Test generation                                        | 47 |

|    | 3.5 | Error simulation                                       | 48 |

|    | 3.6 | Analytical coverage evaluation of CSSL1                | 60 |

|    | 3.7 | Coverage evaluation using error simulation             | 64 |

|    | 3.8 | Coverage evaluation by analysis of actual errors       |    |

|    | 3.9 | Conclusions                                            |    |

| 4.     | High-level test generation for design verification of |

|--------|-------------------------------------------------------|

|        | pipelined microprocessors                             |

| 4      | .1 Related work                                       |

| 4      | .2 Pipelined processor model 83                       |

| 4      | .3 Pipeframe model                                    |

| 4      | .4 Test generation algorithm                          |

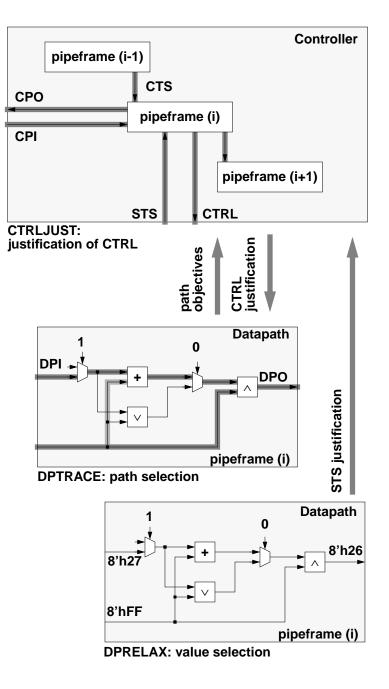

| 4      | .5 DPTRACE: path selection in datapath                |

| 4      | .6 DPRELAX: value selection in datapath               |

| 4      | .7 CTRLJUST: CTRL line value justification            |

| 4      | .8 Experiments                                        |

| 4      | 9 Conclusions                                         |

| 5.     | Conclusions                                           |

| 5      | .1 Contributions                                      |

| 5      | .2 Future work                                        |

|        |                                                       |

| APPENI | DICES                                                 |

| BIBLIO | GRAPHY                                                |

## **LIST OF FIGURES**

### <u>Figure</u>

| 1.1  | Relationship between physical design verification and physical           |    |

|------|--------------------------------------------------------------------------|----|

|      | fault testing                                                            | 23 |

| 1.2  | Deployment of the proposed verification system                           | 24 |

| 2.1  | Example of instruction sequence that exposes an error                    | 27 |

| 2.2  | Bug report example                                                       | 29 |

| 2.3  | Error collection system                                                  | 31 |

| 2.4  | Difference between two successive revisions                              | 33 |

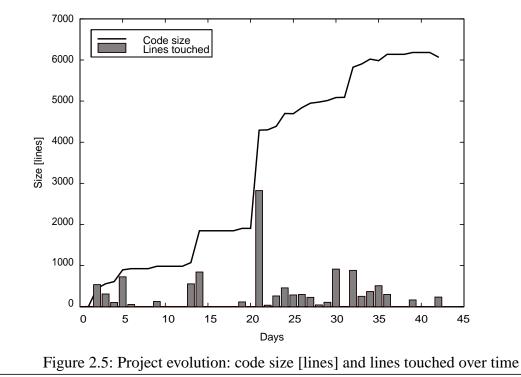

| 2.5  | Project evolution: code size [lines] and lines touched over time         | 34 |

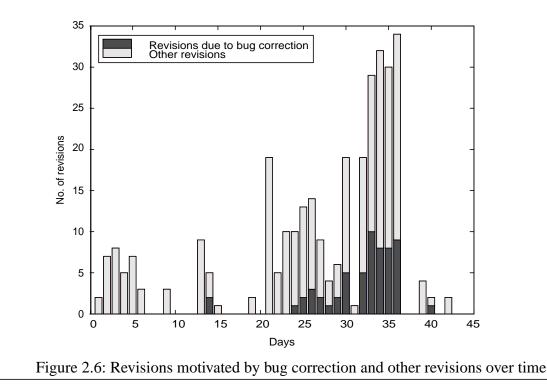

| 2.6  | Revisions motivated by bug correction and other revisions over time      | 35 |

| 2.7  | Design errors: time to discovery [days] vs. error size [lines]           | 36 |

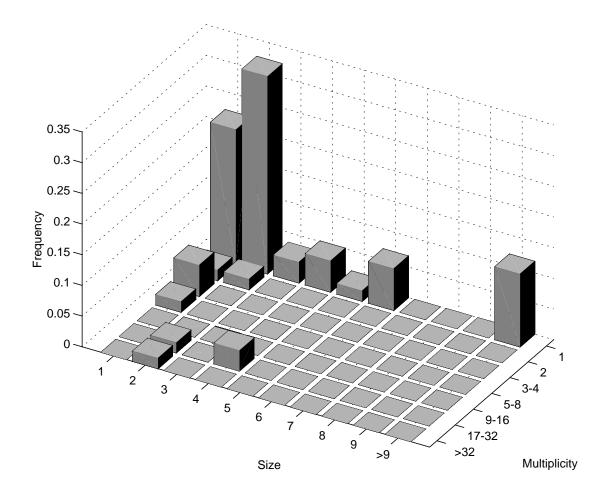

| 2.8  | Frequency of design errors in function of their size and multiplicity    | 37 |

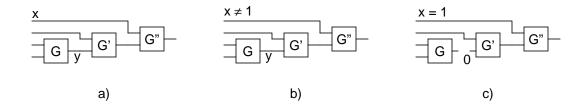

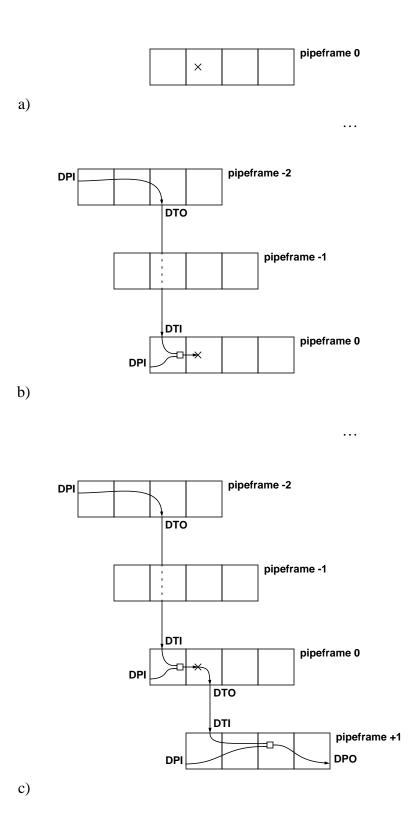

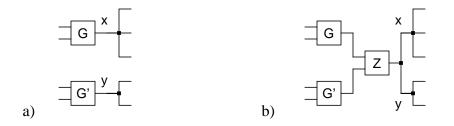

| 3.1  | CSSL1 error (x = 1, y / 0): a) error-free design; b) erroneous design    |    |

|      | with $x \neq 1$ ; c) erroneous design with $x = 1$                       | 45 |

| 3.2  | PROOFS' error simulation algorithm                                       | 51 |

| 3.3  | CESIM error simulation algorithm for conditional errors                  | 53 |

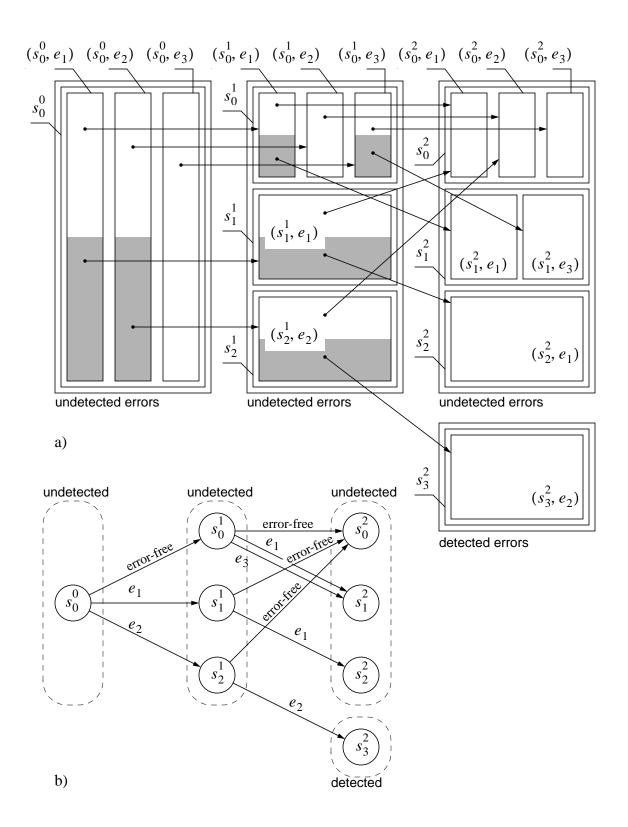

| 3.4  | Example execution of CESIM for a 3-vector test sequence:                 |    |

|      | a) PS- and PSBE-partitions of errors, b) corresponding state transitions | 55 |

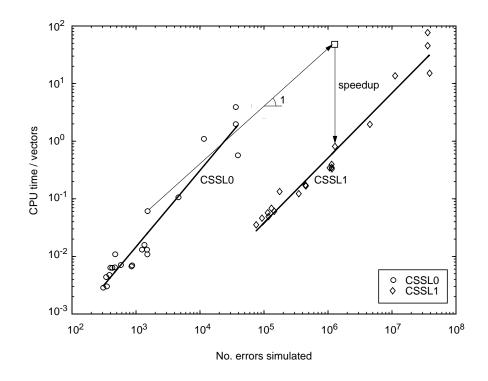

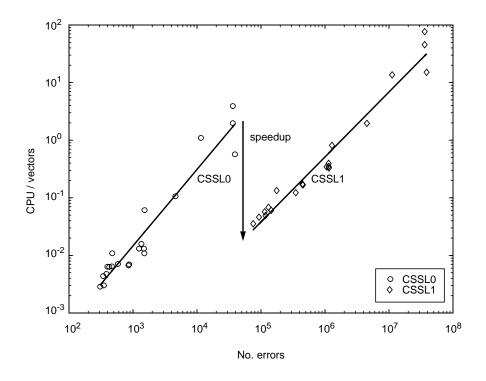

| 3.5  | Run-time analysis of CESIM on the ISCAS'89 benchmarks                    | 57 |

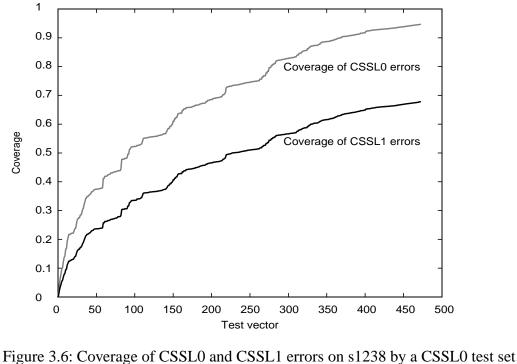

| 3.6  | Coverage of CSSL0 and CSSL1 errors on s1238 by a CSSL0 test set          |    |

|      | generated by HITEC                                                       | 58 |

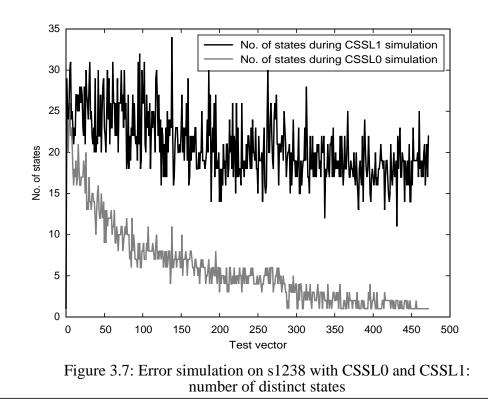

| 3.7  | Error simulation on s1238 with CSSL0 and CSSL1: number of                |    |

|      | distinct states                                                          | 59 |

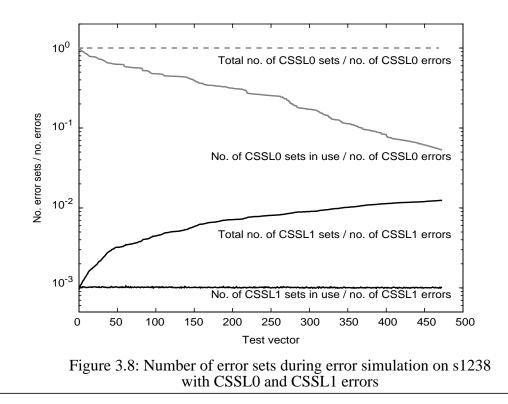

| 3.8  | Number of error sets during error simulation on s1238 with CSSL0         |    |

|      | and CSSL1 errors                                                         | 60 |

| 3.9  | Some basic error types [AA95]                                            | 61 |

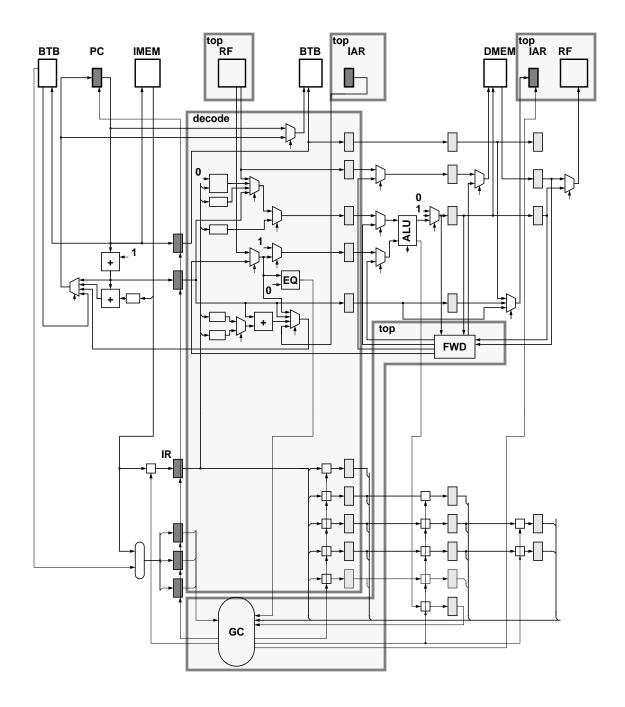

| 3.10 | i e                                                                      |    |

|      | decode and top                                                           | 66 |

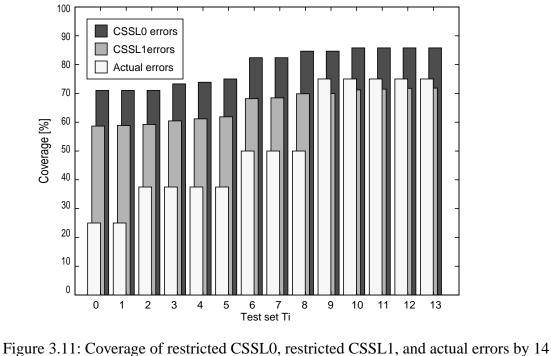

| 3.11 | Coverage of restricted CSSL0, restricted CSSL1, and actual errors        |    |

|      | by 14 biased random test sets T0-T13 for top                             | 68 |

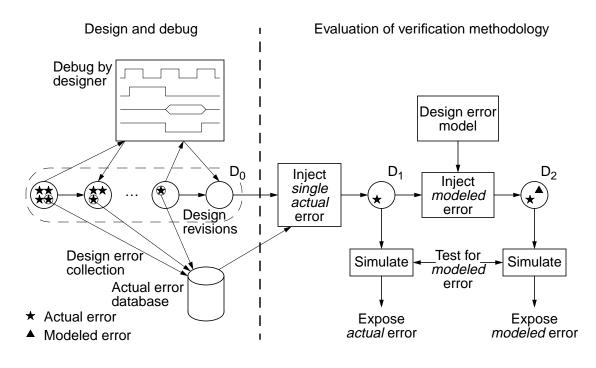

|      | Experiment to evaluate the proposed design verification methodology      | 70 |

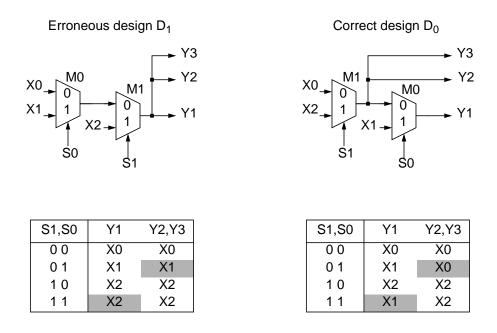

| 3.13 | Example of an actual design error in our DLX implementation              | 71 |

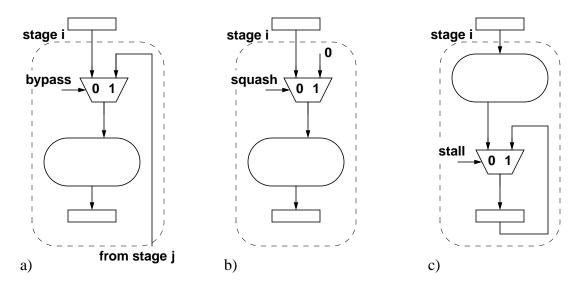

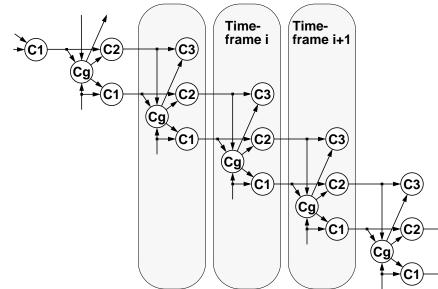

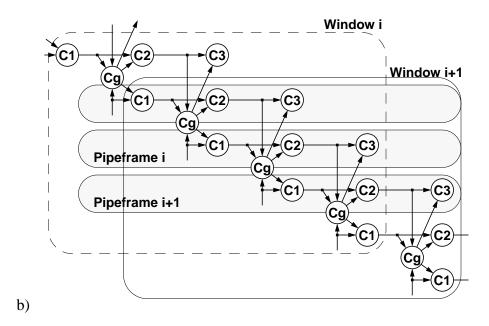

| 4.1  | Instruction interaction mechanisms: a) bypassing, b) squashing,          |    |

|      | c) stalling                                                              | 84 |

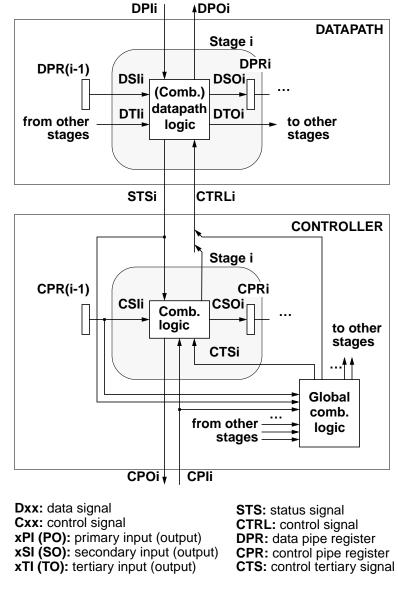

| 4.2  | Pipelined microprocessor model                                           | 85 |

| 4.3  | Pipelined controller                                                     | 87 |

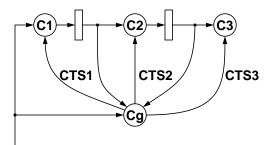

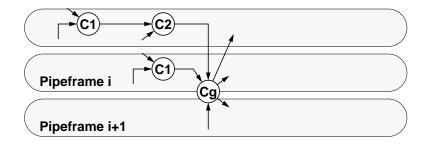

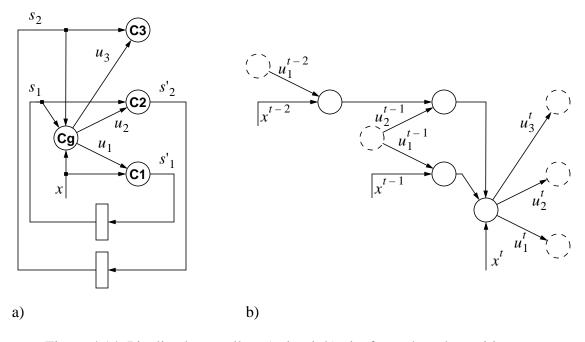

| 4.4         | Iterative array of pipelined controller: a) conventional organization;  |     |

|-------------|-------------------------------------------------------------------------|-----|

|             | b) alternative organization                                             | 88  |

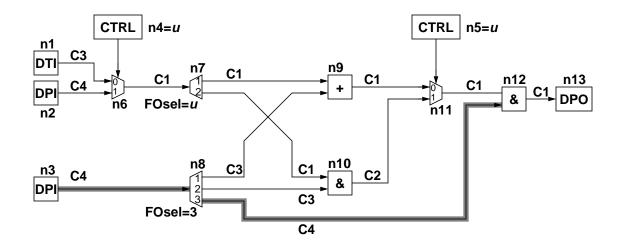

| 4.5         | Composite circuit dealt with in pipeframe organization                  | 89  |

| 4.6         | The three parts of the test generation algorithm and their interactions | 91  |

| 4.7         | Flowchart of overall test generation algorithm                          | 92  |

| 4.8         | Overall iterative organization of path selection                        | 94  |

| 4.9         | C- and O-propagation tables                                             | 99  |

| 4.10        | Path selection using C-values                                           | 100 |

| 4.11        | Directed search PODEM                                                   | 101 |

| 4.12        | Backtrace rules for path selection: add, and                            | 102 |

| 4.13        | Backtrace rules for path selection: fan, mux                            | 103 |

| 4.14        | Pipelined controller: a) circuit b) pipeframe-based transition system   | 110 |

| 4.15        | Overall test generation algorithm                                       | 111 |

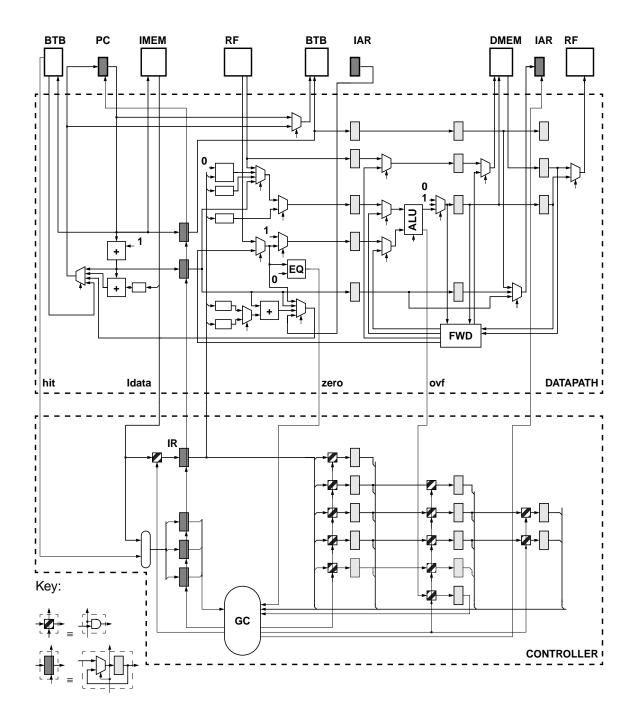

| 4.16        | Simplified schematic of DLX implementation                              | 113 |

| A.1         | BF (x, y): a) Fault-free circuit, b) faulty circuit                     | 122 |

| <b>B</b> .1 | Run time analysis of CESIM on ISCAS'89 benchmarks                       | 128 |

## LIST OF TABLES

### Table:

| 1.1                      | Phases in the design of a microprocessor                                                                                                                                                                                                                                                               | 3                 |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 2.1<br>2.2<br>2.3<br>2.4 | Design projects for which error data was collected<br>Design files written for the X86 project<br>Error distribution in X86<br>Design error distributions [%]                                                                                                                                          | 33<br>34          |

| 3.1                      | Characteristics of two modules of the DLX microprocessor implementation                                                                                                                                                                                                                                | 65                |

| 3.2                      | Coverage of synthetic and actual errors by biased random tests<br>T0-T13                                                                                                                                                                                                                               | 67                |

| 3.3                      | Actual design errors and the corresponding dominated modeled errors for DLX                                                                                                                                                                                                                            | 72                |

| 3.4                      | Actual design errors and the corresponding dominated modeled errors for LC2                                                                                                                                                                                                                            |                   |

| 3.5                      | Comparison of practical design error models                                                                                                                                                                                                                                                            | 76                |

| 4.1<br>4.2               | Initial C- and O- values<br>Computation of controllability and observability measures for a node                                                                                                                                                                                                       | 98                |

| 4.3<br>4.4<br>4.5<br>4.6 | with incoming edges $x_1x_m$ and outgoing edges $y_1y_n$<br>Model parameters of DLX design<br>High-level test generation for bus-SSL errors in DLX implementation<br>Gate-level test generation for standard SSL errors using HITEC<br>Comparison of high-level and gate-level test generation for DLX | 115<br>115<br>115 |

| A.1                      | Bridging functions Z(x, y)                                                                                                                                                                                                                                                                             | 123               |

| <b>B</b> .1              | Test generation and fault simulation of ISCAS'89 circuits using<br>HITEC                                                                                                                                                                                                                               | 126               |

| B.2                      | Error simulation of ISCAS'89 circuits using CESIM                                                                                                                                                                                                                                                      | 127               |

## LIST OF APPENDICES

### **Appendix**

| A. | Relationship between CSSL1 errors and bridging faults | 122 |

|----|-------------------------------------------------------|-----|

| B. | Conditional error simulation on ISCAS 89 benchmarks   | 124 |

# CHAPTER 1 Introduction

Information technology is drastically changing our world. Economies are shifting from the industrial age of steel and cars to the information age of computer networks and ideas [Eco96]. In 1998, the gross domestic product (GDP) in the US due to computers, semiconductors, and electronics reached that of the automobile industry: 3.5% [Baum98]. The microprocessor, which saw its birth in 1971 with the Intel 4004, plays a central role in this information revolution. Indeed, Intel now dominates the hardware side of the computer industry. It is the largest (by dollar volume) chipmaker in the world. Microprocessors have become commodity products and are essential parts, not just of computers, but also of cars, cellular phones, personal digital assistants, and video games, to name just a few. Continuous technological improvements have led to integrated circuits becoming smaller, faster and cheaper. Simultaneously, people have continued to find new uses of microchips and computers. The Internet, with its explosive growth, is just the latest example.

The markets for microprocessors demand low cost and high performance, and are changing rapidly. To meet these demands, microprocessor design houses have to overcome great technological challenges: Circuits need to be designed that operate at very high speed. New design methodologies to deal with signal integrity and timing issues are becoming necessary now that the minimum feature size has dropped well into the deep sub-micron regime. The number of transistors integrated on a single chip is doubling every 18 months. This has led to an enormous growth in functional complexity. Furthermore, the pressure put on the design cycle by time-to-market is enormous.

Functional verification, which is concerned with ensuring that the design implements the intended functional behavior, is considered one of microprocessor design's major bottlenecks. A verification team today is the size of what an entire microprocessor design team was 10 years ago [Wolf98b]. The technology and knowledge required to do verification 'right' is expected to become a differentiator among companies [Wolf98b]. Successful companies will have to put together a complete set of complementing technologies to ensure their designs' functional quality. Also, microprocessors are increasingly being used in (safety-) critical applications, which directly influence the need for better design verification.

The cost of doing verification 'wrong' can be very high. Manufacturing an extra silicon revision of a chip is becoming increasingly expensive [Wils99]. Far more severe can be the loss in expected sales and margin due to the delay in planned shipping date when an unplanned silicon revision is required. Finally, production volumes are ramping up so rapidly, that letting the first customers do the debugging is no longer an option. To cover the replacement of faulty chips containing the infamous FDIV bug, Intel announced a charge against earnings of \$475 million [Beiz95].

The subject of this thesis is a new methodology for functional design verification of microprocessors. To put functional design verification into perspective, we first examine the design process. We then define functional design verification in Section 1.2. The next three sections discuss some important issues in functional design verification: test generation (Section 1.3), correctness checking (Section 1.4), and quality measurement (Section 1.5). We examine related work in the areas of physical fault testing and software testing in Sections 1.6 and 1.7, respectively. We conclude this introduction with an outline of the thesis.

#### **1.1** Microprocessor design

To put functional design verification into perspective, we first examine the design process of microprocessors. Our discussion is based on an article by Bose and Conte [Bose98]. Referring to Table 1.1, four major phases can be identified: 1) architectural exploration, 2) microarchitecture definition, 3) design implementation, and 4) post tape-out.

| Phase                        | Synthesis activities                                                        | Analysis (verification) activities                                                                                 | Design representations                                                       |

|------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| Architectural exploration    | Application selection<br>Workload selection<br>Trace generation             | Validation of traces                                                                                               | Performance,<br>cost, and power<br>goals                                     |

| Microarchitecture definition | Development of<br>trace-driven simulator<br>Microarchitecture<br>definition | Performance<br>verification                                                                                        | ISA<br>Trace-driven<br>simulation<br>model (µarch.)                          |

| Design<br>implementation     | Logic design<br>Circuit design<br>Physical design                           | Func. design verif.<br>Func. impl. verif.<br>Timing verification<br>Electrical verification<br>Layout verification | Behavioral RTL<br>Structural RTL<br>Transistor-level<br>schematics<br>Layout |

| Post tape-out                | Machine-specific compiler tuning                                            | Functional testing<br>Electrical charact.<br>Performance charact.                                                  | First silicon                                                                |

Table 1.1: Phases in the design of a microprocessor

#### **Architectural exploration**

Both economical and technological forces set the design targets for a new microprocessor. The specifications include performance goals for certain applications, cost and power consumption constraints.

One of the first tasks of the architects is to select representative applications, generate corresponding workloads, and reduce these to *benchmarks* that are small enough for microarchitectural simulation. Other activities include the analysis of the dataflow of key applications and the development of a crude model to evaluate the performance of the architecture. Architects bound the design space based on technological considerations.

#### **Microarchitecture definition**

The second phase is concerned with the definition of the microarchitecture. Architects work on microarchitectural innovations, determine which microarchitectural features need to be considered, and build simulation models for them. These models are the building blocks of a simulation model for the complete microarchitecture. The purpose of the

microarchitectural simulator, also referred to as a *timer* or a *performance simulator*, is to compute an accurate estimate of the execution time, in number of clock cycles, of a given benchmark on a given concrete microarchitecture [Burg97, John91]. As the number of design points is very large and the size of the benchmarks is very large as well, simulation speed is important. A popular simulation technique is trace-driven simulation [John91]. A concrete microarchitecture is defined by a set of parameters that further specify the features used, such as the number and latency of integer execution units, or the size of a cache. Also associated with each microarchitectural feature is its cost in terms of hardware, but also in terms of design and verification effort. To accurately estimate the cost some floorplanning and circuit design studies may be required.

The design problem is that of finding the microarchitecture that meets all the constraints and provides the best trade-off between performance and cost. Verification at this stage of the design is mainly concerned with the correctness of the microarchitectural simulator; the systematic study of this problem, also referred to as performance verification, has only recently gained interest [Bose98].

#### **Design implementation**

In the third phase the microarchitecture is implemented. The microarchitectural specification is typically not formal, and consists of textual descriptions, block diagrams, and parameter values. The first step in this phase is to design the first register-transfer level (RTL) description. Standardized hardware description languages (HDL's), such as Verilog [IEEE96] and VHDL [IEEE88], or C/C++ are commonly used to describe the RTL model. This activity is sometimes referred to as *control design*. Logic designers refine this behavioral RTL description to a structural RTL description. Circuit designers generate transistor-level netlists that implement the structural RTL. Layout designers generate layouts for the transistor-level schematics. The refinement from behavioral RTL to layout differs significantly among industrial design methodologies.

There are numerous verification problems at this stage. They include functional (logic) verification, timing verification, electrical verification, physical design rule verification. In functional verification we distinguish between design verification, which is concerned

with the functional correctness of the initial RTL description, and implementation verification, which is concerned with checking the functional equivalence between two versions of the implementation. The latter includes comparing the RTL view against the structural view, the structural RTL view vs. transistor level schematics, and the schematics vs. the layout.

#### Post tape-out

Functional design verification continues after the design has been taped out. Once first silicon is available, extensive functional testing can begin. The main difference with presilicon design verification is the vast increase in test throughput. Diagnosing the root cause of a discrepancy can be difficult. Functional test suites are complemented with test suites aimed at measuring performance. Other activities in this phase include electrical characterization, and physical fault testing and diagnosis.

Software activities that critically depend on the hardware, such as machine-specific compiler tuning, and post-hardware measurements, can start as soon as the silicon has been found sufficiently functional. This may involve engineering workarounds for remaining functional bugs, or fabrication of corrected versions of the chip.

#### **1.2 Functional verification**

Functional verification has gained a lot of interest in recent years as evidenced by the surge in publications detailing industrial experience with the topic:

- AMD's K5: [Gana96]

- DEC's Alpha: [Kant96, Tayl98]

- HP's PA RISC: [Alex96, Bass95, Mang97, Weir97]

- IBM's S/390: [Shep97, Wile97]

- Metaflow's Sparc: [Pope96]

- Motorola/IBM's PowerPC: [Mall95, Mona96]

- SGS Thomson's Chameleon: [Casa96]

Although concrete methodologies differ from company to company, some common themes can be identified as we shall see.

**Functional implementation verification.** Functional *implementation* verification refers to checking the functional equivalence between two versions of the design. The two versions may be representations of the design at a different level of abstraction (below the microarchitectural level), such as behavioral and structural RTL. Alternatively they may be different versions of the design at the same level of abstraction; for example, one may be a retimed version of the other.

Efficient methods have been developed to formally check the boolean equivalence of large combinational circuits [Kuel97], and have recently become available commercially [Goer95]. For library-based logic design methodologies these tools are readily applicable. In custom methodologies a significant effort may be involved in automatically extracting an accurate gate-level view from the transistor level netlist. Nevertheless, these methods are becoming a favorable alternative for regression verification using a (switch-level) simulator.

Combinational equivalence checkers can be used to check the equivalence of two sequential circuits if there is a one-to-one mapping between the state registers. If such a mapping does not exist, the complexity of the problem greatly increases. For the special case of circuits whose state registers differ because of retiming, more specialized methods have been developed [Bisc97, Hosk95].

**Functional design verification.** Functional *design* verification (FDV) is concerned with verifying the functional correctness of the first RTL model of the design. For microprocessor design correctness, this means conformance to the instruction set architecture (ISA) and to some (incomplete) microarchitectural specification.

Functional design verification undergoes several phases as the project progresses. The complete effort can be divided into a pre-silicon and a post-silicon phase. The former phase is further divided into unit verification and system verification.

During *unit* verification a portion of the design is verified in isolation. For larger units, another (lower) level of integration (designer macros) may be appropriate. Basically the

same verification techniques as those at the system level are applicable. The advantages of this bottom-up approach are as follows. Functional bugs that are confined to a single unit are usually easier to detect and diagnose when that unit is exercised in isolation than in the system. Furthermore, verification does not have to wait until every unit is completed. A disadvantage is the overhead required to set-up testbenches for all of the units. This may require abstract models to mimic other units interfacing with the one being verified. Once functional quality criteria for the units have been met, *system* verification can be started.

The aim of *pre-silicon* functional verification is not to eliminate every functional design error, but to raise the functional quality of the design to a level that facilitates swift hardware bring-up and test. Consequently the system has to be able to perform most functions perfectly, but a small number of remaining errors can be tolerated. Wile et al. [Wile97] report three key elements in achieving this goal: 1) The strengths and weaknesses of verification methods used need to be understood. 2) The priorities of hardware bring-up need to be understood and verified. 3) Work-around mechanisms, which allow for avoidance of failing aspects of the system behavior, need to be understood and fully functional. If these conditions are met, a much higher confidence in the functional quality of the design can be obtained in a given amount of time by fabricating the chip and performing extensive functional testing than by any of the pre-silicon verification techniques. This is essential for meeting time-to-market. The throughput of test cases during *post-silicon* verification is typically 3 to 5 orders of magnitude greater than that during pre-silicon verification. On the other hand, diagnosing an error may take significantly more time. The first step is usually to try to reconstruct the conditions that led to the discrepancy in the RTL simulation model. The observability offered by the RTL model can then be used to diagnose the error to its root cause.

#### Approaches to functional design verification

There are two broad approaches to functional hardware design verification: formal and simulation-based. Formal methods try to verify the correctness of a system by using mathematical proofs [Clar96, Kurs97, McFa93, McMi94, Yoel90]. Such methods implicitly consider all possible behaviors of the models representing the system and its

specification, whereas simulation-based methods can only consider a limited range of behaviors. The accuracy and completeness of the system and specification models is a fundamental limitation for any formal method. The spectrum of formal methods for FDV is broad. At one end there are methods that are highly automated, but address only a very restricted problem space [Beer96, EET94, Goer97, Hard96, Kuel97, McMi93]. Methods at the opposite end, such as theorem proving, use formalisms to address a richer class of problems, and have mechanisms to use hierarchy and abstraction, but require a great amount of expertise to apply them [Cohn87, Cohn89, Owre96, Wind95].

Simulation-based design verification tries to uncover design errors by detecting a circuit's faulty behavior when deterministic or pseudo-random tests (simulation vectors) are applied. All of the microprocessor manufacturers mentioned in the beginning of Section 1.2 report that they still rely heavily on simulation-based methods to verify their products. Simulation-based methods are readily applicable as typical design flows use HDL descriptions that can be simulated using standard logic simulation tools, or C/C++ descriptions in conjunction with a proprietary (cycle-based) simulator. Also, logic simulation is an area hardware designers are very familiar with.

In the following sections we examine some important issues in simulation-based functional design verification: test generation, checking correctness, and measuring functional quality.

#### **1.3** Test generation for FDV

**Manual test generation.** Hand-written tests have been used with great success in the early days of computer design. With an intimate understanding of the design, a designer can write a very powerful and yet small set of verification tests that are very effective in exercising the design. Hand-written tests also have the advantage of being easier to debug. However, as the size and complexity of designs have dramatically increased, it becomes harder for one person to comprehend the complete design at a detailed level. Moreover, modern simulation technology, such as cycle-based simulation [McGe95], is able to simulate millions of clock cycles per day on a single workstation, even for the biggest

designs. To take advantage of this simulation capability, automated test generation methods are needed.

**Pseudo-random test generation.** In the area of physical fault testing, it has long ago been recognized that test patterns can easily be generated randomly. The method requires very little effort, but its efficiency and effectiveness, are rather low compared to algorithmic approaches. Furthermore, the effectiveness and efficiency decrease with increasing design size [Abra90]. Nevertheless, random test pattern generation can be very useful to complement manual test generation in the absence of better methods. Sophisticated pseudo-random exercisers have been used very successfully to validate complex microprocessor designs [Ahar91, Kant96]. Taylor et al. [Tayl98] report that 79% of the functional bugs in the DEC Alpha 21264 microprocessor were found by pseudorandom tests. To achieve this high effectiveness such pseudo-random test generators incorporate knowledge about the instruction set architecture and the concrete microarchitecture. They typically have many parameters that allow the verification engineer to bias test generation towards "interesting behaviors," such as corner cases. A strength of random test generators is that they can generate test cases that verification engineers might have never thought of. On the other hand, most random test generators have so-called *holes*: these are areas in the space of valid test sequences that are covered only with an extremely low probability, or even are not covered at all. Random tests are more difficult to debug than hand-written tests.

**Template-based test generation.** Certain aspects of designs are difficult to cover with biased random tests. This may be the case if the space of valid input sequences is highly constrained. Specialized tools have been developed to help automate the generation of such focused tests. One example is a code generator described in [Chan94, Chan95]. The user provides so-called symbolic instruction graphs that compactly describe a set of instruction sequences that exhibit certain properties. The tool generates actual instruction sequences that satisfy all the properties by using constraint solving techniques. One property might be that the third instruction is a load-class instruction, which causes a cache miss, and that the fourth instruction is an arithmetic instruction using the result produced by the load instruction. Free variables, such as the register that serves as the load

target, are chosen in a biased random manner. The tool incorporates knowledge about the micro-architecture, in the form of implicit constraints and biasing functions. A similar tool is described in [Hoss96].

**Operating system (OS) and application code.** Other sources of verification tests are operating system code and application code. However, booting an OS requires on the order of ten billion cycles [Kuma97], therefore the use of this type of verification has only recently become feasible through hardware emulation [Gana96, Bass95, Kuma97]. Demonstrating that the design correctly boots several OS's is a great confidence builder. Furthermore, for architectures that are not very well documented, such as the Intel x86 architecture [Wolf98a], successfully running application software with the OS in place is a common practice [Gana96]. In spite of the fact that the x86 architecture dominates the industry, there are some subtle features [X86] which are not officially documented and can cause compatibility problems. Ultimately application and OS software are the yardsticks for compatibility. In-circuit emulation is one step closer towards real system operation. The emulator is hooked up to a (modified) system board and hence receives real external events from other devices on the system bus.

**Coverage-directed test generation.** Pseudo-random test generators are typically deployed in conjunction with extensive coverage measurements. Coverage is a measure of the completeness of a test suite for a design. A discussion of prevalent coverage metrics is given in Section 1.5. Coverage data is analyzed to identify regions of the behavior that are not (well) covered. Usually, verification engineers manually tune the pseudo-random test generators, or write a focussed test to cover the verification hole.

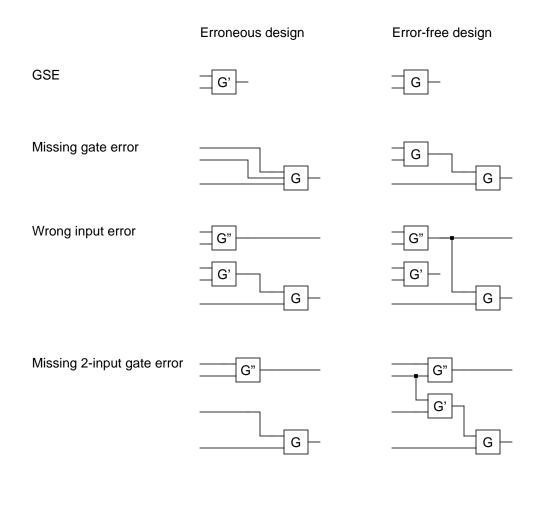

**Error-oriented test generation.** A different approach is to use synthetic design error models to guide test generation. This exploits the similarity between hardware design verification and physical fault testing. For example, Al-Asaad and Hayes [AA95] define a class of design error models for gate-level combinational circuits. They describe how each of these errors can be mapped onto single-stuck line (SSL) faults that can be targeted with standard automated test pattern generation (ATPG) tools. This provides a method to generate tests with a provably high coverage for certain classes of modeled errors.

A second method in this class stems from mutation testing, which is an error-oriented structural approach to software testing. Mutation testing will be discussed in greater detail in Section 1.7. Recently, Al Hayek and Robach [AH96] have successfully applied mutation testing to hardware design verification in the case of small VHDL modules.

#### **1.4** Checking the outcome of a simulation

A nontrivial task in simulation-based FDV is to determine the outcome of simulating a verification test, i.e., did the verification test detect an error?

**Manual inspection.** Manual inspection of the simulation output is still a commonly used method, especially in the early stages of the verification effort. The engineer, typically the designer, inspects the simulation output through an interface similar to that of a logic analyzer. This method is very flexible way for tracking down an error to its source. The interface allows the designer to explore the entire design. Every signal in the circuit can be examined. Once the outcome of a simulation run has been validated, it can be stored together with the test for later use (regression testing). Although manual inspection is error-prone and impractical for large test sets, it is still necessary to diagnose the root cause of discrepancies detected by the methods discussed below.

**Self-checking tests.** A first approach to automated correctness checking is to make the tests self-checking. The tests start by setting up the system's initial state. This is followed by the bulk of the verification test. At the end, part of the system's final state is compared to a precomputed final state included with the test. If the test was generated manually, it is not uncommon that the test writer computes the expected final state himself. For larger tests, and for tests that were generated with tool assistance or even completely automatically, the final state is usually computed by running the test through a suitable high-level simulation model of the system, such as an interpreter for the ISA. The outcome of a self-checking test is basically pass or fail. In case of failure, the test needs to be simulated again, this time with full visibility. Tracking down the error (error diagnosis) can be very tedious and time consuming. Another complication of the approach is the problem of *error masking*. At some point in the simulation, a verification test may uncover

a design error (make it observable in the visible part of the machine state), but the error effect might get annihilated in the remaining part of the simulation. To overcome this difficulty, tests are usually restricted in length. An advantage of self-checking tests is that only the implementation needs to be simulated. The absence of a suitable simulatable reference model (specification) makes it the only choice for correctness checking. The use of self-checking tests has been reported in [Chan94, Ho96a]. Kantrowitz and Noack [Kant96] worked on the functional verification of a commercial superscalar microprocessor. They reported some of these difficulties associated with self-checking tests, and mainly used the *co-simulation* approach to correctness checking.

**Co-simulation.** The second approach for automated checking is to simulate the implementation and the specification together and to compare the states of both machine constantly. This approach has been referred to as co-simulation [Ho96a]. A discrepancy between implementation and specification states indicates either an error in the implementation (a design error), or an error in the reference model. Provided that the reference model and the implementation are developed independently, it is very unlikely that both models exhibit exactly the same error and hence that an error would pass unnoticed. The main difficulty with this approach is that the reference model and the implementation are usually at different levels of abstraction. Synchronizing the simulation of both models, and providing an appropriate mapping (both in time and in space) between the state of the reference model and the implementation may require a significant amount of effort. A superscalar processor with out-of-order execution might be working on several tens of instructions at any given time, whereas the sequential reference model processes only a single instruction at a time. The benefits of this approach are as follows. Cosimulation allows large verification tests to be run without supervision. Changes in the implementation only require changing the state mapping. No individual verification tests need modification, as might be the case for self-checking tests. Co-simulation is typically used in verification methodologies that use pseudo-random test generation [Kant96, Tay198].

Assertion checkers. Assertion checkers, also referred to as *watchdogs* or *snoopers*, are agents that check certain properties about the design during the simulation. Checkers

increase observability, help diagnosis, and prevent wasted simulation cycles by aborting the simulation as soon as a violation occurs. They can be used in conjunction with selfchecking tests or co-simulation. A module that monitors the signals on a bus and checks these signals against the bus protocol is an example of a checker. Another example is a unit that monitors a finite-state machine and halts the execution as soon as the machine enters an illegal state.

#### **1.5** Measuring and predicting functional quality

Perhaps the most challenging problem in simulation-based FDV is to estimate the confidence in the functional quality of a design after a certain amount of verification. Bass et al. report the following acceptance criteria that were used in the verification effort of the HP PA 7100LC microprocessor [Bass95]:

- all failures are diagnosed to their root cause

- no chip failures exist

- all handwritten tests pass

- random code generators have run for a "long time" without finding any failures

- application software has run without any indication of hardware bugs

The problem can be stated informally as two questions: "How thoroughly has the design been verified?" and "When am I (going to be) done simulating?" The first question is concerned with *coverage*, the completeness of a verification test set. Given that exhaustive simulation is not practical, and that therefore any simulation-based verification method is incomplete, the second question is concerned with predicting the effort required to achieve a certain level of functional quality. Determining coverage and predicting the verification effort are closely related aspects. Both analysis of bug detection data, and analysis of coverage have been used to gauge the (expected) confidence in the functional quality of a design.

#### Analysis of bug detection data

Upton collected design error data from the Aurora GaAs microprocessor designs at the University of Michigan [Upto94, Upto97]. He observed error rates of one design error per every 100 to 200 lines of Verilog code. This figure has been confirmed by industrial sources [Bent97]. Upton also analyzed the cumulative number of detected bugs over time and suggested that the bug detection process can be modeled as a function exponentially tapering off in time.

Malka and Ziv apply techniques from software reliability engineering for statistical analysis of bug detection data from two industrial microprocessor design projects [Malk98]. They use trend analysis to gauge the effect of the introduction of a new test generation techniques on reliability growth. Modeling of the bug discovery process is used to make short term predictions, such as the mean time to the next failure, and long term predictions, such as when a certain level of reliability can be expected. They conclude that statistical analysis of bug detection data can provide very relevant information for determining tapeout dates.

The use of quality criteria based on analysis of bug detection data is widespread. However very little data of this type has been published [Mona96]. One reason might be that this data is highly dependent on the design and verification methodology, the nature of the design, and the designers themselves. Also, bug detection data is only meaningful to the extent that a detailed verification plan has been carefully designed and implemented, and that continuous efforts have been made to improve and extend techniques to exercise the design. Biased-random test generators can generate new tests indefinitely, but these tests tend to loose their effectiveness over time. Analysis of coverage provides another means to assess the functional quality of a design.

#### Analysis of coverage

Coverage is a measure of the completeness of a test suite for a design. Moundanos, Abraham and Hoskote [Moun98] give an idealized definition of coverage as the ratio of the exercised behaviors over the total number of specified behaviors. A behavior can be modeled as an execution trace of the design. Unfortunately, attempting to exercise all possible execution paths is an intractable problem. Practical coverage metrics are needed to expose shortcomings of test suites and to spur further directed test generation. They are also needed to complement the methods discussed above for evaluating the state of completion of the verification effort.

#### Code coverage metrics from software testing

Software design also poses the problem of measuring the effectiveness of testing [Beiz90]. Classical structural metrics such as *statement*, *branch* and *path coverage* also apply to hardware design, as designs are usually represented in hardware description languages today. It is well known that many design errors may still go undetected even though complete statement and branch coverage has been achieved. Full path coverage is an impractical goal as the number of paths can be exponential. An advantage of these metrics is that their computation imposes only a small overhead on logic simulation. A typical flow for code coverage measurement is as follows. First the original HDL description is instrumented. The instrumented code is then simulated for the given test suite using an standard logic simulator that is augmented with library functions provided by the coverage tool vendor. Part of the simulation outcome is coverage data that can be examined using a coverage analysis tool.

#### OCCOM

Although code coverage metrics such as statement coverage can be computed efficiently, they suffer from not taking into account observability. A verification test that activates a particular statement, but fails to propagate the effect of executing that statement to a part of the machine state that is truly observable (those signals that are also part of the specification), cannot be considered to have "covered" that statement. To address this shortcoming Devadas et al. [Deva96] propose a code coverage metric based on *tag propagation*, which was later refined in [Fall98a] and is called OCCOM, which stands for observability-based code coverage metric. Errors are associated with assignment statements in the code. The effect of an error is represented by a "tag" that can propagate

through the circuit according to a set of rules similar to the D-calculus [Abra90]. The metric measures the fraction of tags that have been propagated to the observable state over the number of tags injected. The major extension of [Fall98a] to the earlier work in [Deva96] is an efficient method for computing OCCOM coverage using a standard logic simulator. The efficiency of computation is closely related to the definition of the tag propagation rules. The propagation rules are defined so that, in essence, the erroneous machine stays on the same execution path as the error-free machine. Experimental results on small examples show a modest overhead factor of 1.5-4 over logic simulation, which is a much smaller overhead than that incurred by fault simulation.

#### FSM based metrics

Microprocessor designs typically have a natural partition: datapaths and controllers. Controllers have been found to be particularly prone to design errors [Ho96a]. An appropriate model for small controllers is that of a finite-state machine (FSM). Coverage can then be measured as the fraction of states or state transitions visited by a test sequence. FSM transition coverage is not a meaningful metric for microprocessors, which can easily contain thousands of state registers. Even if it were possible to compute the set of reachable states, any coverage measurement with respect to complete state graph would be negligibly small. However, most of the state registers are part of the datapath. Ho [Ho95] worked on the verification of the protocol processor in the FLASH project [Kusk94]. Even after abstracting the datapath, he was still faced with the state explosion problem. Control is usually distributed and consists of a number of interacting smaller FSM's. Ho proposed an incremental strategy in which coverage with respect to the individual state machines is attempted first. This type of coverage measurement is referred to as FSM coverage in industry [Hoss96, Kant96, Nels97, Paln94, SP92], and is also supported by EDA vendors [Clar98]. Next, larger composite state machines can be considered. To reduce the size of that state graph further, Ho defined an equivalence relation on states. All states that apply the same control signals to the datapath are considered equivalent. Provided that the machine has been partitioned in such a way that the datapath does not store any control state, this is a very reasonable assumption. Ho applied his methodology in combination

with hand-generated self-checking tests. He found that designers presented with state transitions that were not covered had great difficulty generating tests to exercise these transitions. An automated method for test generation would have helped a lot. This direction of research set in [Ho95] has gained considerable following: [Ho96b, Ho96a, Geis96, Gupt97, Lewi96, Moun98]. Of particular interest is a study of the relationship between reduced-FSM coverage and design error coverage by Gupta et al. [Gupt97]. However, theoretical results in this area tend to be weak and extensive experimental studies have not appeared in the literature.

#### Design-specific coverage analysis

The functional complexity of commercial microprocessors has been increasing continuously. Functional verification of these designs poses formidable challenges that verification teams tackle with very pragmatic approaches that are specific to the concrete design to be verified, and build on past experience. We list some of the coverage analysis techniques from the functional verification effort of the DEC Alpha processors [Dohm98, Kant96, Tayl98]:

- *State transition analysis.* State transitions coverage is measured on individual FSM's in the design. Some aspects of the design may not be directly implemented as a localized FSM, but may have a natural abstract FSM view that can then be used to measure transition coverage. The analysis may include checking for transitions that are not supposed to occur.

- *Sequence analysis.* A sequence of microarchitectural events in a particular window of time is measured. This type of analysis can be used, for example, to ensure that a behavioral model for an external device on the system bus is fully randomizing events.

- *Occurrence analysis.* Occurrence analysis refers to counting events without any time relationship. An example is checking that a carry-out has been generated for every stage of an adder.

Similar work appears in [Mona96, Pope96].

#### **Design error coverage**

A class of simulation-based verification approaches [Abad88, AA95, Kang94, VC98] use synthetic error models to guide test generation. Coverage is then defined as the ratio of detected synthetic errors to the total number synthetic errors. This is similar to a fault grade in physical fault testing [Abra90]. An advantage of design error coverage is that it addresses observability. A limitation is its high computational cost, as in fault simulation.

#### **1.6 Related area: physical fault testing**

Physical fault testing addresses the problem of detecting physical errors in digital systems. Physical faults may be introduced during the manufacturing process or may appear over time "in the field" due to wear, etc. Direct analysis of physical faults is a physical problem. Furthermore, a wide variety of technology-dependent physical faults exist. Logical fault models and delay fault models have been developed to model in a technology-independent way the physical faults that affect a system's function and operating speed, respectively [Abra90]. In the following we restrict the discussion to testing for logical faults. Logical fault models greatly simplify the testing problem by moving the problem from the physical domain to the Boolean domain.

A logical fault model together with the circuit under test, defines a set of faulty circuits. The test generation problem is to find tests that distinguish each of the faulty circuits from the fault-free circuit. Likewise, in error-directed FDV, tests need to be generated that distinguish the given design from a number of erroneous circuits defined by a design error model. Despite this close relationship, the problems have major differences concerning 1) the reference model, 2) the nature of the circuit: combinational vs. sequential, 3) fault/ error models, and 4) hierarchy.

**Reference model.** In physical fault testing the fault-free circuit is given and completely specified. In design verification, a design (implementation) that needs to be verified is given; the correct design is unknown. Instead, and at best, a complete model of the correct design at a higher abstraction level is given also. Often only a partial specification of the system's behavior is available.

**Combinational vs. sequential circuits.** Test generation for sequential circuits is a much harder problem than test generation for combinational circuits [Micz86, Chen96, Marc96]. Although several test generators are commercially available that are able to generate very high quality tests for very large combinational circuits, test generation for sequential circuits the size of modern microprocessor is well beyond the reach of any current automatic test pattern generation (ATPG) system. However, design for testability techniques (DFT) [Abra90] can greatly reduce the complexity. In full scan design, every register is replaced by a scan register and the registers are linked in a chain, thereby making every register observable and controllable. This effectively reduces the test generation problem to one for combinational circuits. Unfortunately these DFT techniques do not apply to design verification, since typically there is no one-to-one correspondence between the state elements of the design implementation and the reference model (specification).

**Fault/error models.** A third difference between the two areas is that physical fault testing has a proven and widely accepted logical fault model, the single-stuck line (SSL) model. The SSL combines simplicity with the property that it forces each line in the circuit to be exercised. A large body of research has been based on this model. Design verification, as yet, does not have such a fault model. The success of the SSL model provides a motivation to develop error models for design verification, which can potentially benefit from the work on SSL faults.

**Hierarchy.** Physical fault testing and FDV also differ in the role hierarchy plays. In physical fault testing the goal is always complete (SSL) fault coverage at the gate-level. Hierarchical test generation approaches have been proposed that carry the promise of being able to handle larger designs than purely gate-level methods. Typically, test sets are precomputed for gate-level descriptions of individual modules. System tests are then derived at the high-level representation that apply the test stimuli to the module under test, and propagate the error effects to the system's primary outputs [Murr90, Murr92]. FDV can be done in a bottom-up fashion. First, the units constituting the design are verified. Verification tests are applied to the unit in isolation during this phase. Next, the complete design is verified, shifting the focus towards the interaction of the units.

#### **1.7** Related area: software testing

Since the introduction of HDL's to mainstream design methodologies in the 80's, hardware design has started to resemble software design. HDL's, such as Verilog and VHDL, take after general-purpose programming languages, such as C/C++ and Ada. Complex mechanisms, such as dynamic memory allocation, recursion, arbitrary user defined data type and pointers, are readily supported by general-purpose programming languages and are commonly used in software design. In hardware designs, however, these mechanisms need to be implemented explicitly by the designers so that they readily map onto hardware. Functional verification of software is therefore substantially more complex than hardware verification.

The task of software testing is to ensure the reliability of software. A large number of methodologies and techniques have been proposed; an overview can be found in [Beiz90]. However, most of these techniques are not supported by tools that automate the testing process. This is in contrast to most areas of hardware testing and verification. One explanation is that software tends to be more complex and more diverse. Testing methods that are both practical and effective tend to rely on expert knowledge about the software under test that is very difficult to automate. Another explanation is that most testing methods crucially depend on a *specification*. Written specifications are now considered a cornerstone of any software development project [Post96b], but there has been a time when the software community stubbornly tried to avoid taking time to record a description of how software was supposed to behave.

Programmers obviously need specifications to write code, but these specifications should also be written down to facilitate making changes and repairs later. Testers need written specifications to determine whether an observed behavior conforms to the intended behavior.

Informal specifications, plain English descriptions of the requirements, have the benefit of being easy to read. Unfortunately they are a major obstacle to automation of software testing. Recently, formal languages that are still readable, such as Semantic Transfer Language (STL) that appears in [IEEE94], have been proposed to capture specifications. Such formal specifications can automatically be checked not only for syntax problems, but also for semantic inconsistencies. Formal specifications are essential to systematic test case generation and functional coverage measurement.

Beizer [Beiz90] distinguishes two major approaches to software testing: functional and structural. Functional methods are specification-directed and view the implementation as a black box. Structural methods are driven by the implementation. In the remainder of this section we discuss some of the few techniques that 1) are general, i.e., not specific to a particular application domain, and 2) have substantial support for automation.

**Control flowgraph path testing.** Path testing methods are based on the use of the control flowgraph of the program. In this graph nodes represent branching points or junction points in the programs. Arcs represent branch-free code with a single entry and exit. Path testing is the oldest of all structural test techniques. Beizer references work at IBM from 1964. Tests are targeted at bugs that make the program take a different path than intended. Completeness of test sets is measured in terms of their statement, branch, and path coverage. Statement coverage requires that all statements in the program be executed at least once. Branch coverage requires that each alternative at each branch in the program is exercised at least once. Branch coverage implies statement coverage. Path coverage requires that all control flow paths through the program are exercised. This is in general not practical to achieve as the number of paths can be exponential. Full statement and branch coverage are common targets during unit testing. Additional paths are selected by other test methods, such as dataflow testing, or logic-based testing. Coverage measurement is widely supported by software development tool vendors [Paxs98, SR].

**Mutation testing.** Mutation testing is an error-oriented structural approach to software testing introduced by DeMillo et al. in [DeMi78]. Mutation testing considers programs, termed mutants, that differ from the given program by only simple errors, such as replacing '<' by ' $\leq$ ' in one conditional expression. The task of the tester is to construct tests that distinguish the mutants from the given program. Mutation testing provides a metric, mutation coverage, to grade test sets. King and Offutt described in [King91] a system to automatically generate tests using constraint solving techniques.

Mutation testing is predicated on two hypotheses. The competent programmer hypothesis assumes that programmers write code that is very close to correct code. The coupling effect hypothesis states that a test that distinguishes all programs differing from a correct one by only simple errors (mutants), will also be sensitive for more complex errors.

Mutation testing has several high costs associated with it: 1) the large number of mutants that need to be considered, 2) the requirement to execute tests on all of the mutants still alive, and 3) the complexity of test generation. The first problem is addressed by selective mutation [Offu96]. Selective mutation considers only mutation operators, which generate a number of mutants which is linear in the size of the program. A careful experimental study indicates that tests having good coverage with respect to selective mutation provides a good coverage for (non-selective) mutation as well. The second source of the cost is addressed by weak mutation [Wood93]. In weak mutation only the activation of the error is considered, not the propagation. This makes weak mutation a much easier criterion to satisfy. In firm mutation [Wood93], the error is introduced in the program, during the execution, and it only persists for a limited duration of the execution, not till completion of the activation and that with respect to (strong) mutation has not been studied.

**Run-time debugging.** Errors involving dynamically allocated memory are notoriously difficult to debug because they are hard to analyze statically. Examples of such errors are leaking memory, using uninitialized variables, using freed memory, and reading or writing beyond array boundaries. The widely used Purify tool [Rat97] is designed for this type of errors. Purify instruments the object code of a program so that during program execution all code is checked for these run-time errors and memory leaks.

A common type of late-cycle error in hardware designs involves complex control interactions. A register leak occurs when a shared register latches corrupted data, or when it is overwritten before its data has been used. To combat this type of error, 0-In Design Automation [0In] proposes to automatically synthesize assertions that check for these errors. The instrumented design containing the assertions is then simulated with a standard HDL simulator.

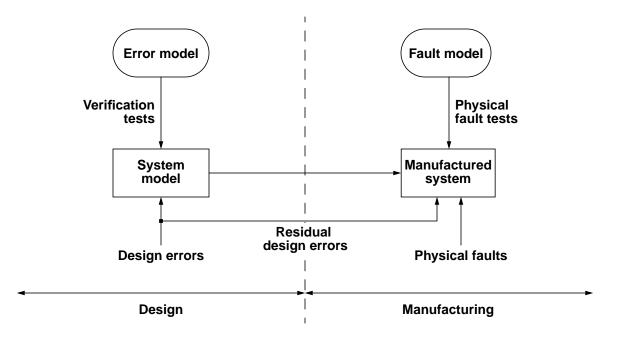

Figure 1.1: Relationship between physical design verification and physical fault testing

#### **1.8** Thesis outline

This thesis explores functional design verification by modeling design errors and generating functional vectors for modeled errors using methods adapted from physical fault testing techniques. The close relationship between physical fault testing and design verification is illustrated in Figure 1.1. The task of physical fault testing is to identify parts that are functionally defective due to imperfections in the manufacturing process. For this purpose, tests are generated that are targeted instances of logical fault models, such as SSL faults. Likewise, the task of FDV is to detect functional design errors. We develop design error models based on empirical error data.

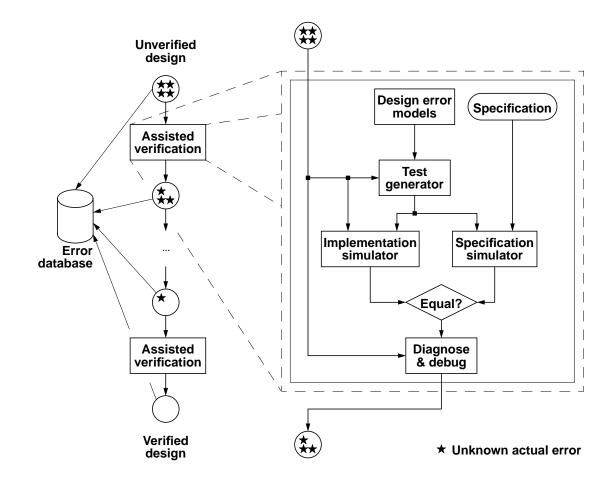

The deployment of our methodology is illustrated in Figure 1.2. An implementation to be verified and its specification are given. For microprocessors, the specification is typically the ISA, and the implementation is a description of the new design in an HDL, such as VHDL or Verilog. In this approach, synthetic error models are used to guide test generation. The tests are applied to simulated models of both the implementation and the

Figure 1.2: Deployment of the proposed verification system

specification. A discrepancy between the two simulation outcomes indicates an error, either in the implementation or in the specification. The figure also shows that throughout the verification process, actual errors are recorded. This information can be used to tune error models.

Chapter 2 examines design error data. Published design error data lack the detail needed to derive structural error models. We therefore devised a systematic method to collect error data. We present and analyze error data we collected from design projects at the University of Michigan. Chapter 3 develops synthetic error models based on the empirical data. We identify requirements that error models must satisfy to be useful for design verification. We show how well each of the proposed error models meets these requirements.

Chapter 4 considers the problem of generating verification tests for synthetic errors in microprocessors. As we will see, this problem is not unlike test generation for SSL faults in a very large sequential circuit. To cope with this complexity, we consider a limited, but important, class of pipelined microprocessors, and develop a test generation method specific to these designs. To this end, we introduce a model that captures high-level information about the structure of pipelined microprocessors. We then develop a high-level test generation method that exploits the high-level knowledge. We describe experiments to evaluate the effectiveness of this algorithm.

Chapter 5 summarizes our research contributions and presents some directions for future research.

# CHAPTER 2 Design error data

Our design verification approach uses design error models to direct test generation. Good design error models should result in test sets that detect many actual design errors. To construct such design error models a good understanding of the nature, frequency, and severity of actual design errors is required. Despite the abundance of design errors in large-scale projects, very little data has been published on these errors. It is common practice in industry to record design errors, but this information is considered proprietary and, perhaps, embarrassing, so it rarely appears in public. These considerations led us to collect error data from design projects at the university. Section 2.1 presents published errors. Section 2.3 presents the error data we collected. Section 2.4 offers some lessons learned. A summary and a discussion of our results is given in Section 2.5.

# 2.1 Published error data

Although design errors that make their way into final products are common, manufacturers have not always been forthcoming about them. This has changed since MIPS began to publish their bug list beginning with [MIP94]; the Pentium bug [Beiz95] also influenced this change. To give a feel for these errors, we present a few examples of design errors that appeared in major commercial microprocessors.

The errata list for the MIPS R4000PC and R4000SC microprocessors (revisions prior to revision 3.0) [MIP94] documents 55 bugs. Many of these require a rare combination of events before they become visible. The following is a representative bug: If an instruction sequence which contains a load causing a data cache miss is followed by a jump, and the jump instruction is the last instruction on the page and, further, the delay slot of the jump

| lw   | // data cache miss                                   |

|------|------------------------------------------------------|

| noop | // one or two noops                                  |

| jr   | <pre>// last instruction in the page</pre>           |

|      | // page boundary                                     |

| noop | <pre>// first instruction (delay slot of jump)</pre> |

|      | // on the next page                                  |

#### Figure 2.1: Example of instruction sequence that exposes an error

is not mapped at the time, then the (VM) exception vector is incorrectly overwritten by the jump address. The R4000 will use the jump address as the exception vector. The workaround suggested in [MIP94] is that jump and branch instructions should never be the last location in a page.

Early versions of the Intel 8086 were shipped with the following bug [Ham94]: The architecture specifies that for MOV and POP instructions to a segment register, interrupts are not to be sampled until completion of the *following* instruction [Int89]. This feature allows a 32-bit pointer to be loaded to the stack pointer registers SS and SP without the danger of an interrupt occurring between the two loads. However, early versions of the 8086 do not disable interrupts following a MOV to a segment register. This causes them to crash when an interrupt uses the stack between MOV SS, reg and MOV SP, op. A workaround is to insert instructions to temporarily disable the interrupts when reloading SS. An uncorrectable problem occurs when an unmaskable interrupt takes place while executing the instruction pair.

These published bug lists are inadequate for error model construction for two reasons: 1) Errata lists typically provide only a programmer's view on the errors. Our error models depend on the design implementation. Therefore, more detailed information about the errors is required, namely the concrete modification to the design implementation that fixes the error. 2) Errata lists only concern errors in the final product. Microprocessor companies go to great efforts to functionally validate their designs. Those design errors that remain undetected before the product is shipped to customers tend to be very subtle and difficult to detect. The majority of all design errors are detected before reaching the customer, and hence are not documented in errata lists. Consequently, errata lists are not representative for the overall population of design errors. These considerations led us to systematically collect design errors from design projects at the university.

# 2.2 Collection method

The most suitable point to collect design error data is immediately after the design error is discovered and corrected. At that point, all relevant information about the design error should be recorded. This record-keeping requirement conflicts with the interests of the designer. Overhead has to be reduced to a minimum in order to overcome designers' natural reluctance to cooperate.

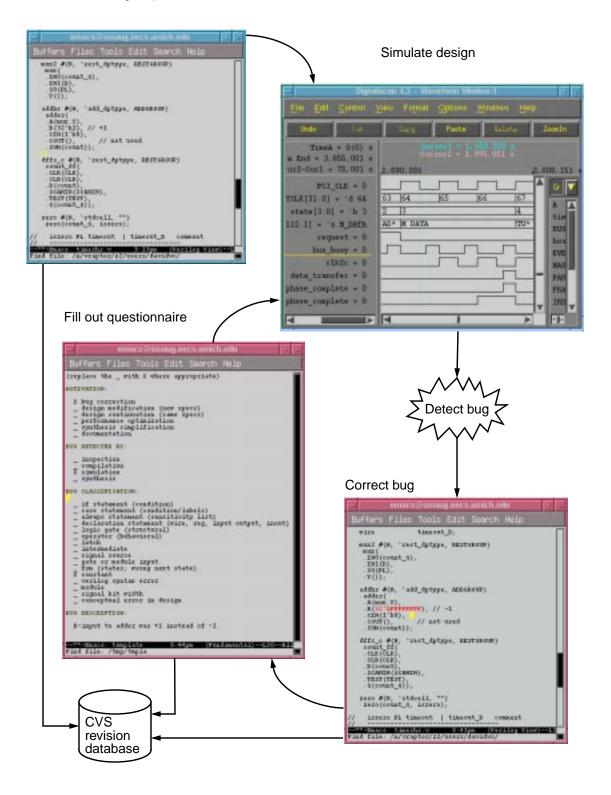

Our error collection method uses the revision management tool CVS [Cede93]. The revision management tool archives successive revisions of the design. Designers were asked to submit a new revision of their design whenever a design error was corrected and whenever they interrupted work on the design. Some designers resist the system because they see it as a way their work can be monitored. We defused this potential problem by providing designers with a handout [VC97] explaining the use of the revision management system, and by explaining our objectives to obtain the designers' cooperation.

Our first design error collection effort took place during the summer of 1996. Only the bare revision management system was in place. Experience with that project motivated the system described above. It was clear that a standardized form was needed to accompany each revision so that interesting revisions, i.e., those involving a design error correction, can be separated from other revisions. We therefore augmented the revision management system so that each time a new revision is submitted, the user is prompted to fill out a questionnaire. The questionnaire, in the form of a multiple choice form shown in Figure 2.2, gathers four pieces of information: 1) the motivation for revising the design; in the case of a bug, the following apply as well: 2) the method by which the bug was detected, 3) the class to which the bug belongs, 4) a short description of the bug. Design errors can be detected by reading the HDL code (inspection), by syntax checking performed by the HDL simulator (compilation) or a synthesis tool (synthesis), or by logic

(replace the \_ with X where appropriate) MOTIVATION: X bug correction \_ design modification \_ design continuation \_ performance optimization \_ synthesis simplification \_ documentation BUG DETECTED BY: \_ inspection \_ compilation X simulation \_ synthesis BUG CLASSIFICATION: Please try to identify the primary source of the error. If in doubt, check all categories that apply. X combinational logic: wrong signal source x missing input(s)

\_ unconnected (floating) input(s)

\_ unconnected (floating) output(s) \_ conflicting outputs \_ wrong gate/module type \_ missing instance of gate/module \_ sequential logic: \_ extra latch/flipflop

\_ missing latch/flipflop \_ extra state \_ missing state \_ statement: \_ if statement \_ case statement \_ always statement \_ declaration \_ port list of module declaration \_ expression (RHS of assignment): \_ missing term/factor \_ extra term/factor \_ missing inversion \_ extra inversion \_ wrong operator \_ wrong constant \_ completely wrong \_ buses: \_ wrong bus width \_ wrong bit order verilog syntax error \_ conceptual error \_ new category (describe below) BUG DESCRIPTION: Forgot to select NOP in case of stall

Figure 2.2: Bug report example

simulation. The operation of our error collection method within the design cycle is illustrated in Figure 2.3.

From the raw revision management data, we identified the design modifications to fix each error by computing the differences between successive revisions. The analysis of the design error data lead to a preliminary classification of design errors. This classification was used in our first major design error collection effort, which took place in the fall term of 1996. Analysis of this design error data lead us to revise our classification. The result is shown in Figure 2.2. The categories are not completely disjoint, so designers were asked to check all applicable categories.

## 2.3 Collected error data