# OS/Architecture Interactions and their Influence on Computer Architecture

by

#### David Nagle

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 1995

#### **Doctoral Committee:**

Professor Trevor Mudge, Chair

Professor Brice Carnahan

Professor Edward Davidson

Assistant Professor Stuart Sechrest

Joel Emer, Senior Consulting Engineer, Digital Equipment Corporation

UMI Number: 9542920

Copyright 1995 by Nagle, David Frederick All rights reserved.

UMI Microform 9542920 Copyright 1995, by UMI Company. All rights reserved. •

This microform edition is protected against unauthorized copying under Title 17, United States Code.

UMI

300 North Zeeb Road Ann Arbor, MI 48103

#### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

UMI

A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 313/761-4700 800/521-0600 · ...

© David Nagle

All Rights Reserved

and the agree of the con-

# **DEDICATION**

To mom and dad — for all of their love, encouragement, and support.

### **ACKNOWLEDGEMENTS**

A friend may well be reckoned the masterpiece of Nature.

Ralph Waldo Emerson

Today I find myself at the end of school. It's an amazing time — a new job with lots of people to meet and tasks to accomplish. It is also a time of reflection, a time to recognize the friends who have helped me through the years. My friends have given me so much, helped me to learn and to grow and have shared their lives with me. I thank each for their counsel, friendship and love.

Hugh Cooper helped me understand the art of teaching. He also taught me that, with a bit of creativity and a lot of hard work, there is always another way to attack a problem. It is a lesson I carry with me every day of my life.

Brice Carnahan and James Wilkes gave me the opportunity to teach some of the best and brightest students. It was in their Engineering 103 courses that I realized how rewarding it is to help people learn and grow.

Trevor Mudge is my good friend and advisor. His advice and experience allowed me to keep perspective while his patience and friendship guided me through graduate school. I look forward to many more lunches at Casey's.

Stuart Sechrest showed me how rewarding research can be and the importance of brainstorming. I will miss our impromptu conversations.

The graduate students who I worked with on the GaAs MIPS project were an amazing group of people. Tom Huff, Mike Upton, Tim Stanley and Mike Riepe all helped to make graduate school an interesting adventure.

Rob Novak was my roommate through most of graduate school. While that in itself is a noble feat, he also taught me the importance of taking time for myself and showed me the meaning of generosity.

Frank walked with me through one of the most amazing years in my life. His friendship and advice have been a unique gift that I value very much.

Julie Scherer helped me to understand the importance of sharing my love and friendship. Julie also taught me to have the courage to grab hold of life and not be afraid to follow my dreams.

Sean showed me the rewards of living life with a smile and good cheer. His strength, counsel and love are a continual inspiration to me.

David Grinnell's love and counsel gave me the strength to finish this work, to start my new career, and to share my life with him.

Rich Uhlig is my research partner and best friend. His example has been my teacher. His advise has been my guide. His support has been my strength. After years of working together, our paths have diverged for a while — each beginning a new life with new friends, each gaining new experiences and learning new things. I hope, however, that our partnership and friendship will continue to grow.

# **TABLE OF CONTENTS**

| DEDICAT                  | IONii                                                                                                                                                                                 |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACKNOW                   | LEDGEMENTSiii                                                                                                                                                                         |

| TABLE O                  | CONTENTSv                                                                                                                                                                             |

| LIST OF T                | ABLES viii                                                                                                                                                                            |

| LIST OF F                | IGURES ix                                                                                                                                                                             |

| CHAPTER                  | .1                                                                                                                                                                                    |

|                          | portance of<br>hitecture Interactions                                                                                                                                                 |

| 1.1<br>1.2<br>1.3<br>1.4 | Introduction1Why consider the operating system?2Where is the performance going?4Analyzing OS/architecture interactions7                                                               |

| CHAPTER                  | . 2                                                                                                                                                                                   |

| Measur                   | ing OS/Architecture Interactions                                                                                                                                                      |

| 2.1<br>2.2<br>2.3        | Introduction9How should we look at the problem?9Benchmarking for OS/architecture interactions132.3.1 Benchmarking 101162.3.1.1 How benchmarks are used162.3.1.2 Types of benchmarks17 |

|                          | 2.3.1.3 Evaluating the performance of a system                                                                                                                                        |

| 2.4                      | Tools and techniques for analyzing OS/architecture interactions                                                                                                                       |

|                          | 2.4.1.2 Other system utilities: vmstat. pstat                                                                                                                                         |

|         | 2.4.1.3 Profiling the kernel                                       | 00   |

|---------|--------------------------------------------------------------------|------|

|         | 2.4.1.3 Profiling the kernel                                       |      |

|         |                                                                    |      |

|         | 2.4.1.5 Summary of coarse-grained tools                            |      |

|         |                                                                    |      |

|         | •                                                                  |      |

|         | · · · · · · · · · · · · · · · · · · ·                              |      |

| 2.5     | 2.4.2.3 Summary of tools and techniques  Our approach              |      |

| 2.3     | 2.5.1 Workloads                                                    |      |

|         | 2.5.1 Workloads                                                    |      |

|         | 2.5.2.1 Monster traces                                             |      |

|         | 2.5.3 Tapeworm - a trap-driven simulation tool                     |      |

|         | 2.5.4 Verifying our measurements and results                       |      |

|         | 2.5.5 Exploring architectural trade-offs                           |      |

| 2.6     | • •                                                                |      |

| 2.0     | Summary                                                            | . 54 |

| CHAPTER | 3                                                                  | . 35 |

|         | nd their Interaction with the Operating System                     |      |

|         |                                                                    |      |

| 3.1     | OS impact on software-managed TLBs                                 |      |

| 3.2     | Page tables and translation hardware                               |      |

| 3.3     | OS influence on TLB performance                                    |      |

|         | 3.3.1 Mapping kernel data structures                               |      |

| 3.4     | Service migration                                                  |      |

| 3.5     | Operating system decomposition                                     |      |

| 3.6     | Additional OS functionality                                        |      |

| 3.7     | Improving TLB performance                                          |      |

| 3.8     | Additional TLB miss vectors                                        |      |

| 3.9     | Lower slots & partitioning the TLB                                 |      |

|         | Increasing TLB size                                                |      |

|         | TLB associativity                                                  |      |

| 3.12    | Summary                                                            | . 57 |

| СПУВТЕВ | 4                                                                  | ΞN   |

|         |                                                                    |      |

|         | ion Cache Performance and Design Trade-offs to Support Operating S | ys-  |

| tems    |                                                                    |      |

| 4.1     | Introduction                                                       |      |

| 4.2     | Reasons for increased I-cache misses                               |      |

| 4.3     | Instruction cache performance                                      |      |

| 4.4     | Cost and benefit analysis                                          |      |

|         | 4.4.1 Cost analysis                                                |      |

|         | 4.4.2 Performance-driven area allocation                           |      |

| 4.5     | Other techniques to improve I-cache performance                    |      |

|         | 4.5.1 Bandwidth                                                    |      |

|         | 4.5.2 Prefetching                                                  |      |

|         | 453 Rungeeing                                                      | 70   |

|           |        |            | ng                                      |     |

|-----------|--------|------------|-----------------------------------------|-----|

| 4.6       | Conclu | usions and | d future work                           | 80  |

| CHAPTER   | 25     |            | • • • • • • • • • • • • • • • • • • • • | 82  |

|           |        |            | for OS/architecture Analysis            |     |

| 5.1       | _      |            | • • • • • • • • • • • • • • • • • • • • | 82  |

| 5.2       |        |            | ency                                    |     |

|           | 5.2.1  |            | ····                                    |     |

|           | 5.2.2  |            |                                         |     |

|           | 5.2.3  |            | ardware issues                          |     |

|           | 5.2.4  |            | ry of hardware issues                   |     |

| 5.3       | Direct |            | e/software interactions                 |     |

|           | 5.3.1  |            | re management and policy                |     |

|           |        | 5.3.1.1    | TLB design and management               | 94  |

|           |        | 5.3.1.2    | Exception handling                      | 96  |

|           |        | 5.3.1.3    | Cache management                        | 97  |

|           | 5.3.2  |            | g costly hardware                       |     |

|           | 5.3.3  | OS strate  | egies to improve hardware performance   | 100 |

|           | 5.3.4  |            | у                                       |     |

| 5.4       | •      |            | e issues                                |     |

|           | 5.4.1  |            | ementation                              |     |

|           |        |            | Coding strategies and implementation    |     |

|           |        |            | Data movement                           |     |

|           | 5.4.2  |            | gn                                      |     |

|           |        |            | Example 1 - File cache design           |     |

|           | _      |            | Example 2 - VM management               |     |

| 5.5       | Summ   | ary        |                                         | 109 |

| CHAPTER   | 86     |            |                                         | 110 |

| Where     | We Hav | ve Been a  | and Where We are Going                  |     |

| 6.1       | Summ   | arv        |                                         | 110 |

| 6.2       |        |            | oing                                    |     |

| TERMINO   | LOGY   |            |                                         | 113 |

| DIDI IOCI |        |            |                                         | 115 |

|           |        |            |                                         |     |

# **LIST OF TABLES**

| Table 1.1 | Simulation vs. actual architectural performance                              |

|-----------|------------------------------------------------------------------------------|

| Table 1.2 | Architectural performance differences between Ultrix and Mach $3.0\ldots3$   |

| Table 2.1 | Relative performance of primitive OS functions                               |

| Table 2.2 | Number of cycles required to execute primitive OS functions                  |

| Table 2.3 | Workloads                                                                    |

| Table 2.4 | Operating systems                                                            |

| Table 3.1 | Total TLB misses across the benchmarks                                       |

| Table 3.2 | Costs for different TLB miss types                                           |

| Table 3.3 | Characteristics of the operating systems studied                             |

| Table 3.4 | Number of TLB misses (in thousands)41                                        |

| Table 3.5 | Time spent handling TLB misses (in seconds)41                                |

| Table 3.6 | Recomputed cost of TLB misses given additional miss vectors (Mach 3.0+AFSin) |

| Table 3.7 | Number of TLB slots for current processors                                   |

| Table 4.1 | On-chip memory in current generation microprocessors                         |

| Table 4.2 | TLB and cache configurations considered                                      |

| Table 4.3 | The ten best area allocations73                                              |

| Table 4.4 | Prefetching                                                                  |

| Table 4.5 | Bypassing                                                                    |

| Table 4.6 | Pipelined memory system with a stream buffer 80                              |

# **LIST OF FIGURES**

| Figure 1.1 | Stall breakdown by architectural component                                  |

|------------|-----------------------------------------------------------------------------|

| Figure 1.2 | Stall breakdown for workload suite                                          |

| Figure 2.1 | Complexity of OS/architecture studies                                       |

| Figure 2.2 | Monster monitoring system                                                   |

| Figure 2.3 | Logic analyzer buffer with timestamps                                       |

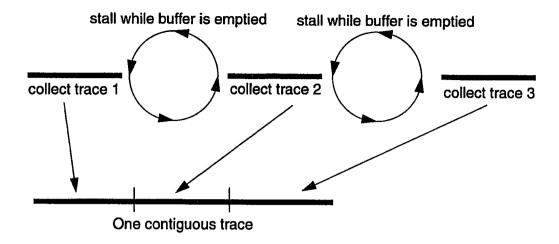

| Figure 2.4 | Capturing a contiguous trace                                                |

| Figure 2.5 | Tapeworm simulator                                                          |

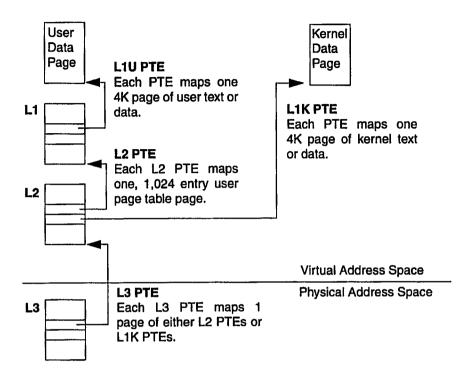

| Figure 3.1 | Page table structure in OSF/1 and Mach 3.0                                  |

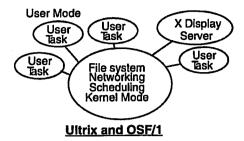

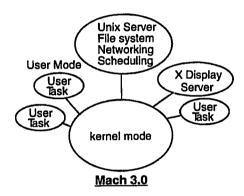

| Figure 3.2 | Monolithic and microkernel operating systems                                |

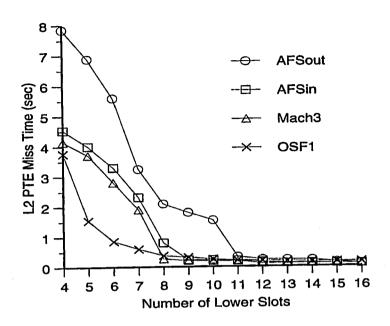

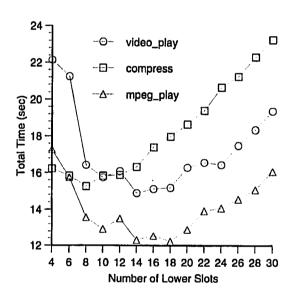

| Figure 3.3 | L2 PTE miss cost vs. number of lower slots                                  |

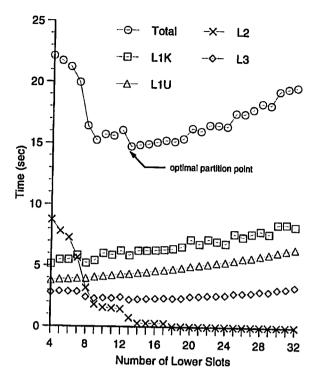

| Figure 3.4 | Total cost of TLB misses vs. number of lower TLB slots 49                   |

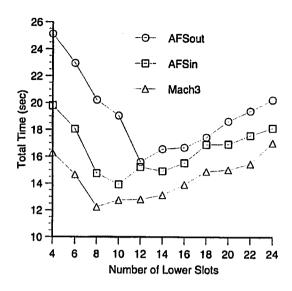

| Figure 3.5 | Optimal partition points for various operating systems and benchmarks 51    |

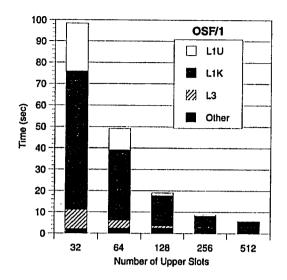

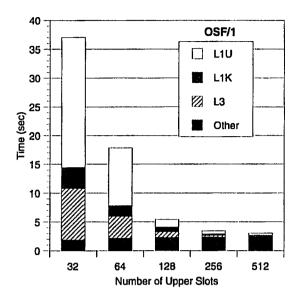

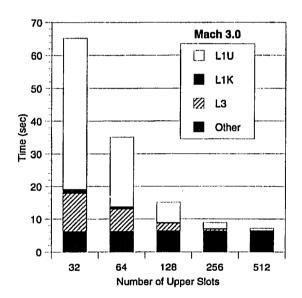

| Figure 3.6 | TLB service time vs. number of upper TLB slots                              |

| Figure 3.7 | Modified TLB service time vs. number of upper TLB slots54                   |

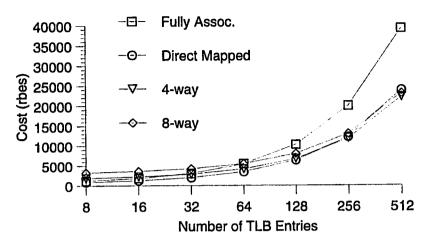

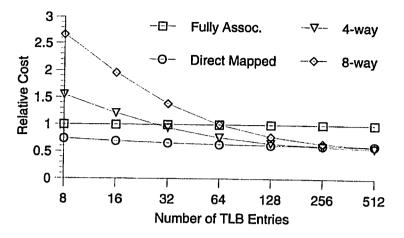

| Figure 3.8 | Total TLB service time for TLBs of different sizes and associativities . 56 |

| Figure 3.9 | Total TLB service time for compress under OSF/1                             |

| Figure 4.1 | Stall breakdown by architectural component                                  |

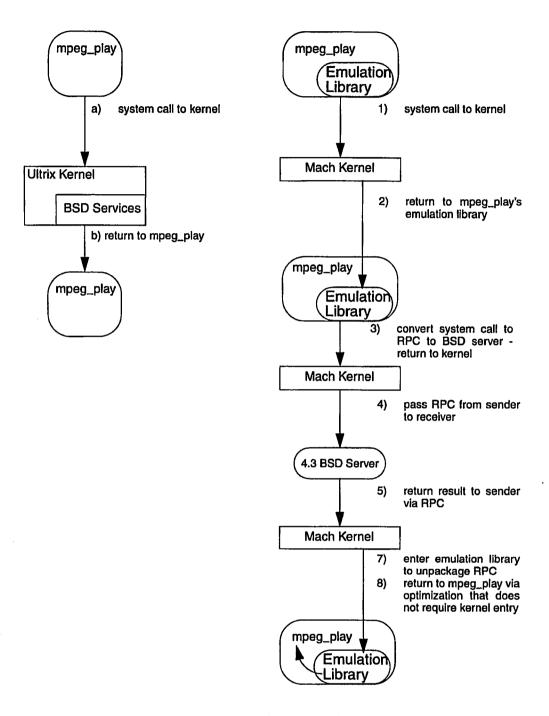

| Figure 4.2 | Service invocation paths in Ultrix and Mach 61                              |

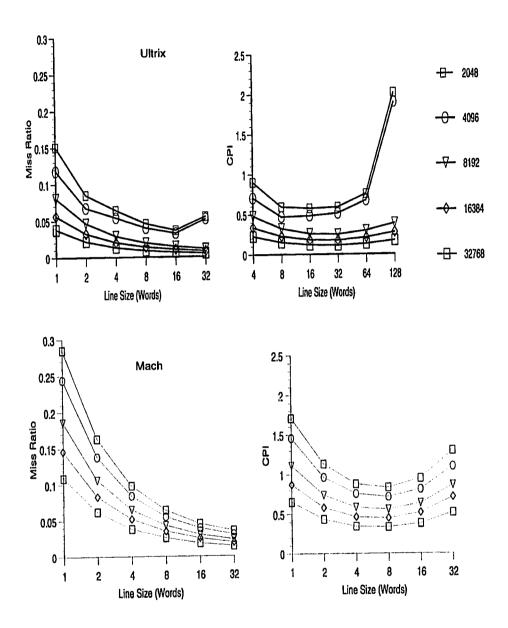

| Figure 4.3 | Instruction cache performance                                               |

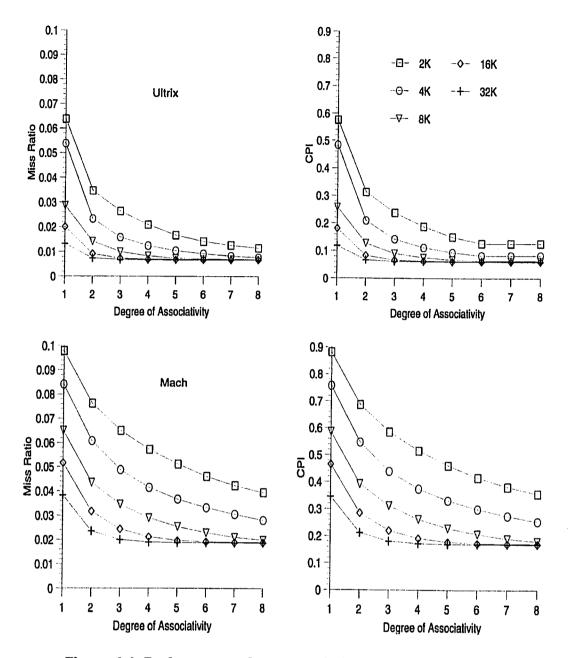

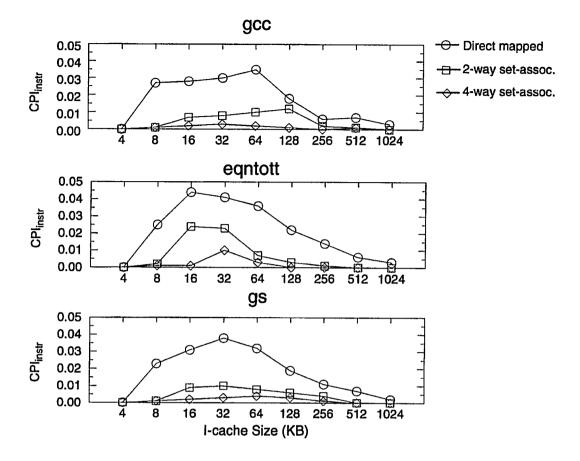

| Figure 4.4 | Performance of set-associative instruction caches                           |

| Figure 4.5 | Area cost for TLBs of different sizes and associativities                   |

| rigule 4.0 | Area cost of set-associative TLBs relative to fully-associative TLBs/(        |

|------------|-------------------------------------------------------------------------------|

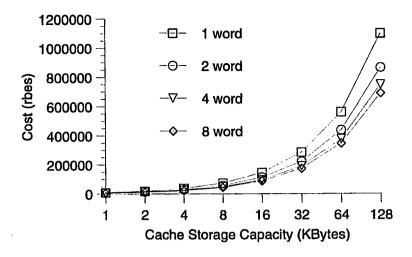

| Figure 4.7 | Area cost for caches of different capacity and line size                      |

| Figure 4.8 | Configurations that cost under 250,000 rbes                                   |

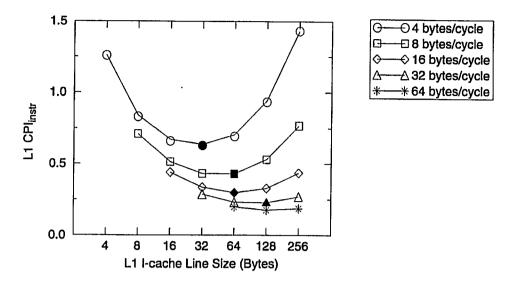

| Figure 4.9 | L1 CPI <sub>instr</sub> vs. line size                                         |

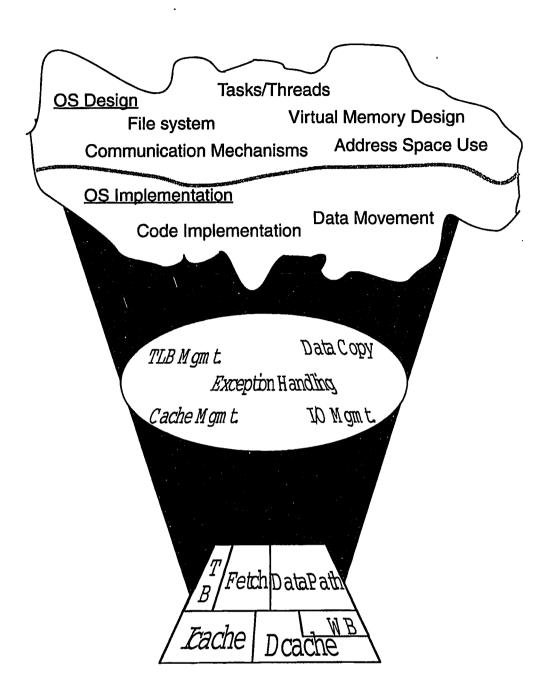

| Figure 5.1 | OS/architecture framework83                                                   |

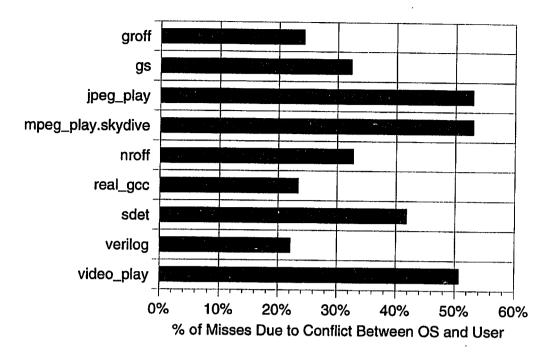

| Figure 5.2 | Variation in conflict misses 86                                               |

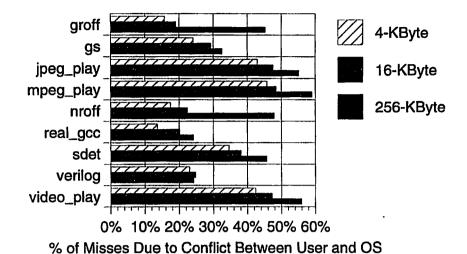

| Figure 5.3 | Variation in conflict misses across cache sizes                               |

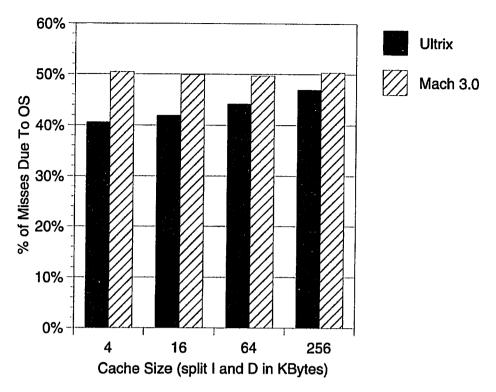

| Figure 5.4 | Percent of misses due to OS                                                   |

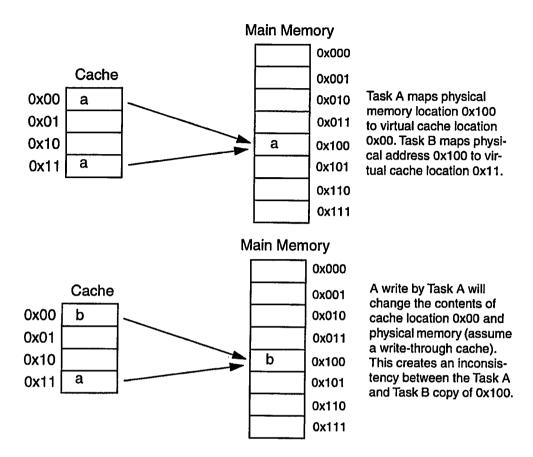

| Figure 5.5 | Illustration of inconsistency in virtually indexed caches                     |

| Figure 5.6 | Variability in CPI <sub>instr</sub> versus I-cache size and associativity 102 |

.

#### **CHAPTER 1**

# The Importance of OS/Architecture Interactions

#### 1.1 Introduction

Operating systems are important. Services provided by or accessed through the operating system (OS) are part of almost every application. Yet, most architectural studies have not considered OS effects. A lack of tools capable of capturing OS references, coupled with the complex behavior of the operating system, has forced most researchers either to qualitatively reason about the OS or to neglect the OS altogether.

This is in stark contrast to application/architecture research, which has developed a very good quantitative analysis methodology. Today, architects build accurate models that analyze interactions between hardware and application software, measuring the impact of various designs and helping to select architectural components that deliver the best performance within the constraints of a technology. The use of these results, however, is severely limited by their inability to account for the operating system's influence on architectural performance.

This dissertation addresses this problem by extending the quantitative approach to the study of the interactions between operating systems and architectures (OS/architecture interactions). Using a hybrid hardware/software monitoring system to gain access to all hardware and software activity, we measure the performance of real systems, analyze the interactions between the OS and architecture, and explore architectural design trade-offs that improve performance. Our goal is to provide designers with an understanding of how

| Benchmark  | Simulated Actua |      | % Difference Between<br>Simulated and Actual CPI | % of Run Time<br>Spent Outside<br>the Benchmark |  |

|------------|-----------------|------|--------------------------------------------------|-------------------------------------------------|--|

| fpppp      | 2.49            | 3.05 | 22.5%                                            | 0.7%                                            |  |

| gs         | 1.31            | 1.68 | 28.2%                                            | 48.6%                                           |  |

| jpeg_play  | 1.30            | 1.50 | 15.4%                                            | 12.8%                                           |  |

| mpeg_play  | 1.37            | 1.82 | 32.9%                                            | 25.6%                                           |  |

| small      | 1.01            | 1.27 | 25.7%                                            | 30.0%                                           |  |

| video_play | 1.17            | 2.44 | 108.6%                                           | 69.4%                                           |  |

Table 1.1 Simulation vs. actual architectural performance

Performance estimates obtained from simulation tools (e.g., cache2000 and pixstats) can be very inaccurate. The absolute error in cycles per instruction (CPI) varies from 15% (jpeg\_play to over 100% (video\_play). The "Actual CPI" does not include the CPI contribution due to TLB misses.

To produce the simulated CPI, each benchmark was annotated to produce an address trace of every instruction and data reference. The address trace was fed into a simulator, cache2000, which models a DECstation 3100 memory system. The results from cache2000 were combined with the static analysis results from the MIPS tool pixstats to compute the "Simulated CPI" values. Actual CPI was measured from a running workstation using our Monster monitoring system (see Chapter 2).

to analyze OS/architecture interactions and how architectures can overcome current performance problems.

## 1.2 Why consider the operating system?

Neglecting the OS would not be a serious problem if the OS did not adversely influence the behavior and performance of a system. However, the handful of works that have measured OS/architecture interactions consistently show a performance problem over a range of applications [Smith82, Clark84, Clark85, Clark88, Agarwal89, Torrellas92]. Consider the measurements in Table 1.1 (p. 2), a comparison of application-only simulation against actual machine performance, including all OS and system service

<sup>1.</sup> The exception is scientific applications, which typically utilize few OS services and can be accurately characterized without considering the operating system.

| Benchmark  | CPI<br>Ultrix | CPI<br>Mach 3.0 |  |

|------------|---------------|-----------------|--|

| fpppp      | 3.05          | 2.96            |  |

| gs         | 1.68          | 1.83            |  |

| jpeg_play  | 1.50          | 1.51            |  |

| kenbus     | 2.20          | 2.38            |  |

| mpeg_play  | 1.82          | 2.00            |  |

| real_gcc   | 1.68          | 1.83            |  |

| sdet       | 1.89          | 2.24            |  |

| video_play | 2.44          | 2.28            |  |

Table 1.2 Architectural performance differences between Ultrix and Mach 3.0

The data show that different operating systems can have very different architectural performance. Despite the fact that the same binaries were used under both operating systems, there are significant differences in architectural performance between Ultrix and Mach 3.0. Both measurements were taken from a DECstation 3100.

activity. In each case, the simulation tool's inability to account for OS activity' leads to a large gap between the predicted and actual performance.

Aggravating this problem are fundamental changes in OS and software technologies. Applications are increasing their use of OS services, operating systems are providing more functionality, and advances in OS technology are fundamentally changing the behavior of the operating system and its interaction with the processor and memory architecture. Table 1.2 (p. 3) compares the actual CPI measurements of two different operating systems: an old-style monolithic OS, Ultrix, and a newer microkernel based OS, Mach 3.0. The data show a large difference in CPI, even though both measurements are from the same machine running the same set of application and X server binaries.

Neglecting the operating system clearly results in an inaccurate characterization of performance. The data in Table 1.2 demonstrates that performance can differ between

<sup>1. &</sup>quot;OS activity" includes memory references from the OS kernel, OS servers (for Mach 3.0), system service references (such as an X display server) and multi-tasking effects.

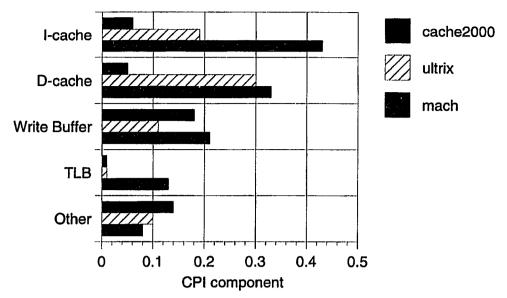

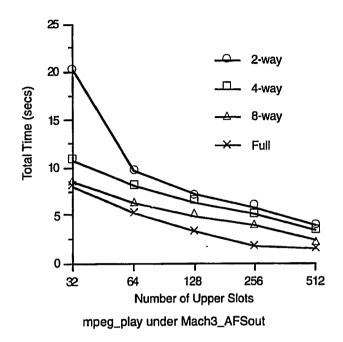

Figure 1.1 Stall breakdown by architectural component

The figure shows three different measurements of the mpeg\_play workload running on a DECstation 3100.

The DECstation 3100 is a MIPS R2000 based workstation with a 64-KByte instruction cache (I-cache), 64-KByte data cache (D-cache), a 4-entry write buffer, and a 64-entry fully-associative TLB (translation lookaside buffer). Processor stalls can be due to any of these hardware structures or *other* types of stalls including integer multiply/divide, interrupts, and floating point stalls.

operating systems and that architects may need to consider multiple operating systems in order to fully characterize OS/architecture interactions. The results, however, do not provide any insight into where performance is lost. We examine this question in the next section.

#### 1.3 Where is the performance going?

To answer this question, we used our system monitoring facilities (see Chapter 2) to measure the amount of time a workload spends stalling in each of the architectural components of a DECstation 3100. From these measurements, we can determine which hardware structures are the most important in terms of stall cycles. This information can

then be used to redesign the architecture to better support the software. Figure 1.1 (p. 4) shows the stall breakdown for an example workload, mpeg\_play.

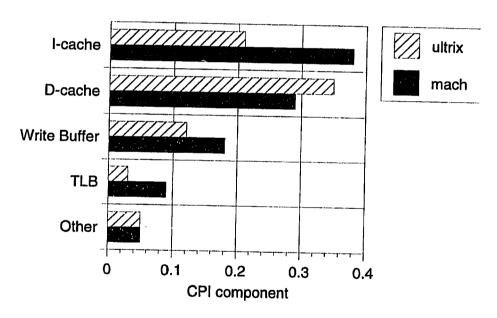

In the cache2000 simulations, which only consider application references, the two most important architectural components are the write buffer and "other", which include integer multiply/divide stalls, floating point stalls and exception stalls. Together, write buffer and other stalls account for over 75% of all stall cycles. Using this data, an architect would find the instruction cache (I-cache) and data cache (D-cache) performance acceptable and focus on improving the write buffer and "other" performance.

Real measurements under Ultrix reveal a very different performance picture. Here, the write buffer and "other" account for less than 30% of the total stall cycles. The biggest performance problem is the D-cache, which is responsible for over 40% of the stall cycles. Combined, the I- and D-caches account for 70% of the stall cycles. In contrast, cache2000 measurements suggest that caches account for less than 26% of the stall cycles.

The Mach 3.0 measurements portray yet another picture. Like Ultrix, the I- and D-caches are responsible for the largest portion of stalls. However, the total number of stall cycles has increased and the relative importance of I- and D-caches has switched, with the I-cache now responsible for over 40% of the total stall cycles. The graph also shows a significant increase in translation lookaside buffer (TLB) stalls, from 0.01 to 0.13 CPI. This shift between D- and I-cache and the increased importance of the TLB are important differences because they can influence architectural design trade-offs.

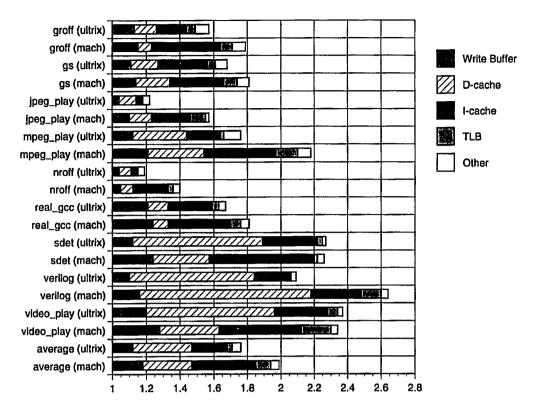

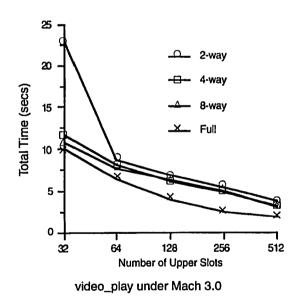

Measurements across a range of workloads show similar results (Figure 1.2, p. 6. - see Table 2.3, p. 27, for a description of the workloads). In almost every case, I-cache stalls are the largest source of stalls under Mach 3.0. Mach 3.0 also increases the number of TLB misses over Ultrix, by 300% in the average case.

<sup>1.</sup> mpeg\_play's performance characteristics are very similar to the performance characteristics averaged over our entire benchmark suite.

Figure 1.2 Stall breakdown for workload suite

Most of the workloads show a shift in the relative importance of D- and I-cache stalls and an increase in TLB stalls, between Ultrix and Mach.

This information is invaluable because it shows the extent to which architectural components contribute to performance loss, allowing designers to focus their attention on the important architectural issues. However, the results do not explain why there are significant differences between the operating systems; the results only provide a coarse-grained architectural view of the system's performance. Understanding "why" is far more important because it helps designers reason about how current and future software trends will impact the architecture. This, in turn, allows hardware designers to build architectures that meet the needs of current and future generations of software.

## 1.4 Analyzing OS/architecture interactions

The data in Figure 1.2 (p. 6) demonstrate that the OS can significantly impact performance. Identifying the hardware components responsible for lost performance is only the first problem. The more difficult problem is to determine what are the source(s) of the performance loss. In particular to understand if performance problems are due to:

- the architecture.

- the operating system,

- or some interaction(s) between the architecture and the operating system.

In the next chapter, we examine this question by analyzing the structure of the architecture, the operating system and the nature of their interactions. Our base architecture is a MIPS R2000 based DECstation 3100. The operating systems considered are three variants of UNIX with diverse internal structures: DEC Ultrix, OSF/1, and Mach 3.0.

After identifying several interactions between the operating system and architecture, we focus on OS interactions with the TLB and the I-cache. Analysis begins by identifying the reasons for TLB and I-cache performance problems. Using several different simulation techniques, we explore architectural design trade-offs to determine how much support the architecture can provide. Towards the end of our analysis, we propose a framework for studying OS/architecture interactions and use the framework to relate previous and concurrent research in the field.

The major contributions of this work are the following. First, we analyze OS/architecture interactions across several UNIX based operating systems with radically different internal organizations. Second, we explore architectural trade-offs to help alleviate the performance problems introduced by the operating system. Finally, we use

our results and the works of others to develop an OS/architecture framework that allows researchers to better analyze OS/architecture interactions.

Chapter 2 explores the performance problems and recent attempts to measure OS/architecture interactions. It also outlines our approach and applies the approach to diagnose the basic performance problems found in Ultrix, OSF/1 and Mach 3.0 running on a DECstation 3100. In Chapter 3, we begin our analysis, focusing on the translation lookaside buffer (TLB) and its interaction with the software. Chapter 4 explores caches and instruction fetching techniques. In Chapter 5, we review previous and concurrent work, describing what we have learned about OS/architecture interactions and outlining issues that remain unresolved. Conclusions and future work are presented in Chapter 6.

While we defer a full discussion of previous work to Chapter 5, we should mention that there have been other important contributions to the body of research in this area. Concurrent examples are Flanagan at Brigham Young University [Flanagan93] and Chen at Carnegie Mellon University [Chen94]. There are also several previous studies by Smith [Smith82], Clark et al. [Clark83, Clark85a, Clark85b], Agarwal [Agarwal88] and McRae [McRae93] which cover similar material. Chapter 5 will summarize both previous and concurrent work, placing issues into an OS/architecture framework that allows designers to understand how various components and design issues interact and affect performance.

# **CHAPTER 2**

# **Measuring OS/Architecture Interactions**

The art and science of computer performance boils down to characterizing the workload Domenico Ferrari

#### 2.1 Introduction

Why are OS/architecture interactions difficult to analyze? Probably the most common problem is the lack of tools capable of probing into the system. Even when the tools are available, there are a number of issues which are not usually encountered in standard application/architecture analysis. This chapter explores some of these issues. We begin by examining how recent works have attempted to analyze OS/architecture interactions, discussing some of the problems other works have encountered and the role benchmarks play in determining the results. We continue the discussion of benchmarks, examining issues that are unique to OS/architecture studies. Next, we outline a number of software and hardware tools that can be used to probe into the system. Finally, we discuss our tools and techniques, how they work and how we have applied them to the problem of analyzing OS/architecture interactions.

## 2.2 How should we look at the problem?

One of the major challenges in exploring the interactions between architectures and operating systems is understanding how to approach the problem. One approach is to treat the operating system as just one more piece of software. Several previous works have

adopted this *architecture-centric* viewpoint [Smith82, Clark83, Clark85a, Clark85b, Agarwal88]. Using either hardware monitoring facilities or complete address traces<sup>1</sup>, these works show that operating system code can significantly degrade the performance of hardware structures such as TLBs, write buffers, and caches.

A more *OS-centric* approach focuses on the performance of basic OS functions and associated architectural support. Two recent works, [Ousterhout89, Anderson91], use this approach, applying software methods and qualitative analysis techniques to analyze the performance of specific architectural structures. Their results suggest that current architectural trends cause OS performance to lag behind expected performance, creating a gap between application and OS performance.

Unfortunately, neither approach provides a complete picture of how OS/architecture interactions affect overall performance. By treating the OS as just another piece of code, the architecture-centric viewpoint is unable to determine how OS policy and implementation impact the architecture. This prevents architecture-centric studies from determining if the problem is best solved in hardware, software, or some combination of the two. Likewise, by focusing on specific architectural structures, the OS-centric approach cannot determine how the architecture, as a whole, impacts OS performance.

Worse, using a one-sided approach can sometimes lead to inaccurate results and misleading conclusions. For example, Ousterhout [Ousterhout89] and Anderson et al. [Anderson91] employed an OS-centric approach to show that "the performance of OS functions has not scaled in a commensurate way" with respect to application performance. Using a set of micro-benchmarks that implemented several operating system primitives such as context switching and exception handling, both works measured the micro-benchmark performance across a range of architectures, comparing the micro-benchmarks' relative performance increases against the performance increases of the

<sup>1.</sup> These complete address traces included OS references.

| Operation               | DEC<br>CVAX<br>(μsecs) | MIPS<br>R2000<br>(μsecs) | Relative Speed<br>(R2000/CVAX) |  |

|-------------------------|------------------------|--------------------------|--------------------------------|--|

| Null system call        | 15.8                   | 9.0                      | 1.8                            |  |

| Trap                    | 23.1                   | 15.4                     | 1.5                            |  |

| Page table entry change | 8.8                    | 3.1                      | 2.8                            |  |

| Context switch          | 28.3                   | 14.8                     | 1.9                            |  |

| Application Performance | _                      |                          | 4.2                            |  |

Table 2.1 Relative performance of primitive OS functions

This table, reproduced from Anderson et al. [Anderson91], compares the performance of the 11.1 MHz DEC CVAX with the 16.67 MHz MIPS R2000 processor. While the R2000's performance is better than the CVAX, the relative speed of R2000 to CVAX is significantly below that found by comparing the two machines' SPEC90 performance numbers.

SPEC90 application-based benchmark suite<sup>1</sup>. The data for one set of experiments is reproduced in Table 2.1<sup>2</sup> and was used to show how OS performance is lagging behind application performance. The implication was that architectural trends are not supporting operating system code as well as application code and that technologies such as RISC make it more difficult to implement efficient operating systems. To quote Ousterhout, "Operating systems are not getting faster as fast as hardware."

Unfortunately, the analysis did not consider important architectural issues, causing the researchers to draw several inaccurate conclusions. First, the comparison is based on the SPEC90 benchmark suite, which includes floating point and integer benchmarks. One source of significant improvement for SPEC90 is the superior floating point hardware found in many newer architectures<sup>3</sup>. This clearly will not benefit operating system code which executes almost no floating point operations. Second, the CVAX on-chip cache is

<sup>1.</sup> Ousterhout used the millions of instructions per second (MIPS) rating as the base for comparison. While this is different from Anderson, who uses SPEC90, architectural analysis of Ousterhout's workstations reveals similar problems in his analysis.

<sup>2.</sup> For the complete list of results, refer to Anderson et al., Table 1 [Anderson91].

too small to hold the working set of any of the SPEC90 benchmarks<sup>1</sup>. Therefore, we expect the R2000's large primary caches to give the SPEC90 benchmarks a significant performance improvement over the CVAX. The cache difference will not, however, provide any performance improvement for the micro-benchmarks because their working sets fit comfortably inside either the CVAX or MIPS primary cache.

With this architectural information, it becomes clear that this experiment provides little insight into OS/architecture interactions. It is true that the micro-benchmark performance did not scale at the same rate as the SPEC90 benchmarks. But, comparing the SPEC90 benchmark suite against the micro-benchmarks biased the experiment in favor of SPEC90 because it utilizes the floating point and cache improvements, while the micro-benchmarks do not.

Ironically, the data collected by Anderson can be used to answer an important question: "Are newer architectures improving the performance of OS primitives?" We answered this question by computing the number of cycles the CVAX and the MIPS architectures require to execute each primitive (Table 2.2). The results show that the MIPS architecture requires fewer cycles to execute each primitive OS function. So, while OS code may not be seeing the same rate of performance improvement as some user applications, architectural features are improving the performance of OS primitives. In other words, "operating systems are getting faster faster than hardware."

The fundamental limitation of most of the previous work has been its singular viewpoint. This is not to suggest that the previous work did not make a significant contribution. On the contrary. The VAX hardware measurement papers [Clark83, Emer84, Clark85, Clark88] clearly showed that OS code can significantly degrade the performance

<sup>3.</sup> For example, the R2000's floating point add, subtract and multiply algorithms are a full cycle faster than the CVAX.

<sup>1.</sup> The CVAX has a 1-KByte unified primary cache backed by a 64-KByte second level unified cache (2 cycle penalty on a primary cache miss that hits in the second level cache.

| Operation               | DEC<br>CVAX<br>(μsecs) | MIPS<br>R2000<br>(μsecs) | DEC<br>CVAX<br>(cycles) | MIPS<br>R2000<br>(cycles) |

|-------------------------|------------------------|--------------------------|-------------------------|---------------------------|

| Null system call        | 15.8                   | 9.0                      | 176                     | 150                       |

| Trap                    | 23.1                   | 15.4                     | 257                     | 257                       |

| Page table entry change | 8.8                    | 3.1                      | 98                      | 52                        |

| Context switch          | 28.3                   | 14.8                     | 314                     | 247                       |

Table 2.2 Number of cycles required to execute primitive OS functions

Using the data from Anderson et al. [Anderson91], this table shows the number of cycles required to execute each primitive OS function. The results show that the MIPS architecture actually requires fewer cycles to execute each primitive.

of hardware structures. Smith [Smith82] and Agarwal [Agarwal89] examined how OS code is affected by various cache design trade-offs and that neglecting OS references can result in optimistic performance simulations. Finally, while some of the quantitative analysis by Ousterhout [Ousterhout89] and Anderson et al. [Anderson91] misses the mark, their qualitative analysis of operating system and architectural trends was very insightful and has helped to guide much of the work that has been done over the last 4 years.

### 2.3 Benchmarking for OS/architecture interactions

Benchmarks are the basic ruler used to measure performance. However, choosing an appropriate benchmark is one of the most difficult aspects of designing a good experiment. A well-chosen set of benchmarks, carefully applied, will exercise appropriate system component(s), revealing valuable performance information. A poorly chosen set can overlook important components, focusing attention on issues of negligible importance.

Using benchmarks to construct a meaningful experiment requires a researcher to answer two basic questions.

What specific relationship is being examined?

Do the benchmarks exercise the system in such a way as to generate data that can elucidate this relationship?

While these questions may seem obvious, experimental work has often overlooked the second question, applying a "standard" benchmark suite without considering whether the benchmarks are appropriate for the performance issues being evaluated. For example, many published experiments only use the SPEC Floating Point and Integer Benchmark Suite to evaluate memory system designs. These benchmarks, however, do not exercise the instruction side of a memory system [SPEC91, Gee93, Uhlig95]. This limits the general applicability of the experimental results because the benchmarks are not an appropriate set of workloads for many studies. <sup>1,2</sup>

Researchers often overlook another important question, "Do the benchmarks bias the results of the experiment?" This is particularly true of experiments that use code fragment benchmarks (also known as micro-benchmarks) instead of real applications. Code fragments can rigorously exercise specific system component(s), but do not provide any information on the relative importance of the component(s). They can also remove the effects of hardware and/or software structures, creating artificially good or bad results [Bershad91].

Benchmarking issues become even more complex when studying OS/architecture interactions. Unlike experiments that only measure an application's interaction with the hardware, OS/architecture studies must consider how a workload exercises the hardware, the operating system, various software services, the interactions among these components,

The question of what is an appropriate workload has been widely debated by the research community for many years. The only conclusion is that there is no such thing as one appropriate set of workloads for all users. However, many studies have relied on a narrow range of workloads, neglecting to consider important software trends and their impact on design trade-offs.

Two reasons why researchers have been unable to consider a wider range of applications are the lack of application source code and tools capable of capturing the behavior of those applications.

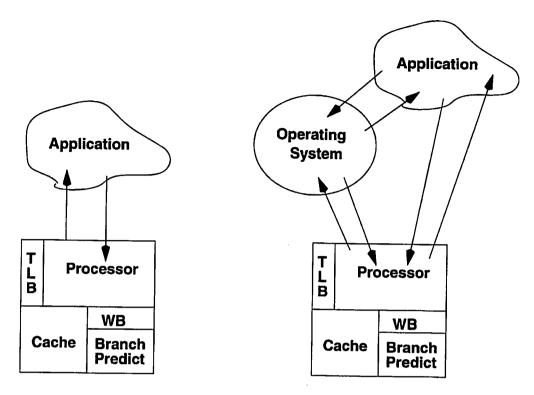

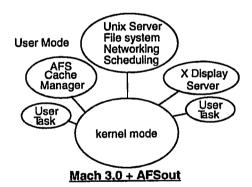

Figure 2.1 Complexity of OS/architecture studies

While traditional application/architecture studies consider only architecture and application interaction, OS/architecture studies must consider interactions among the operating system, application and architecture.

and the effects of competing workloads (Figure 2.3, p. 15). For example, decomposition of OS services can increase the amount of interprocess communication (IPC). It also can stress hardware components such as the TLB, but only when a significant number of services are concurrently used. Unfortunately, most OS-oriented benchmarks do not utilize a sufficient number of concurrent services, completely missing the interaction among OS, application and TLB (for a more detailed analysis, refer to Chapter 3).

Environmental issues must also be considered when measuring a system's performance. The number of tasks running, the task page allocation policy, and the size of physical memory play an important role in determining the experimental results. This is completely different from an application/architecture study, where the behavior of the

system is invariant between program runs. Our own measurements have shown that as Mach 3.0 ages, OS data structures can become scattered between the virtual and physical space, increasing the TLB miss rate. However, this type of phenomenon can only be observed after the system has been running for several hours or even several days.

Because these issues can have a pronounced effect on the results of an experiment, it is important that we examine how benchmarks should be used when studying OS/architecture interactions. The following sections summarize our findings. We begin by outlining basic benchmarking issues common to all types of performance research. This is followed by a discussion of benchmarking issues that are important to OS/architecture research. We conclude with a discussion of our benchmarks, why they were chosen, and some of their limitations.

#### 2.3.1 Benchmarking 101

#### 2.3.1.1 How benchmarks are used

Often, benchmarks are used to compare the speed or throughput of different systems. The speed measurement is like a race: each system runs the same set of benchmarks and the computer that finishes in the least amount of time is the winner. The throughput measurement is like a weightlifting contest. Each system runs a number of concurrent workloads and the one that can sustain the largest number of workloads per unit time is the winner. Benchmark suites such as SPEC Integer, SPEC Floating Point, SPEC SDM, SPEC SFS, and the Perfect Club are all designed to compare performance across various systems.

Benchmarks can also be used to determine the relative importance of various system components. For example, measurements of scientific applications show that they rely heavily on floating point computation and large data sets [Gee93] while measurements of video applications show a need for special integer computation.

Understanding the requirements of a user's workload allows designers to allocate system resources to deliver the best performance.

Finally, benchmarks are useful for studying the interactions between hardware and software components and for analyzing the impact of design trade-offs. Hardware structures such as caches or register windows have been implemented because workload studies showed that software could utilize these structures to improve performance.

#### 2.3.1.2 Types of benchmarks

Hennessy and Patterson outline four basic types of benchmarks [Hennessy91].

- Programs: applications that are used by computer users. The SPEC

Integer and Floating Point Benchmark Suites consist of real programs.

- Kernels: key fragments of code. The Livermore Loops are kernel benchmarks.

- Toy: real, but small programs such as quicksort or the 8-Queens game.

Stanford University has a collection of small benchmarks, called the

Small Benchmark Suite.

- Synthetic: programs designed to simulate some aspect of a workload's behavior, but not based on any real code. Whetstone and Drystone are synthetic benchmarks.

Any of these benchmark categories can be used to compare the performance of different systems. However, synthetic and toy benchmarks tend to be poor indicators of overall performance. Kernel benchmarks, also known as micro-benchmarks, are drawn from key fragments of code such as the computational loops in a matrix multiply routine or a system call to an OS service. These benchmarks can determine how well a machine performs a specific set of software operations. However, their narrow focus prevents kernels from providing information on the relative importance of various operations.

If well chosen, real program benchmarks can be the most useful because they provide a complete view of how the software utilizes the hardware. This allows designers to understand the relative importance of various hardware and software structures and to focus their attention on optimizations that will provide the greatest improvements in overall performance.

#### 2.3.1.3 Evaluating the performance of a system

There are two basic methods for evaluating the performance of a system. The first compares the performance of two or more machines. Metrics such as benchmark execution time, SPEC marks, or throughput are used to make the comparisons, providing quantitative comparisons that allows one to determine which machine is better for his or her set of workloads. The second method is to evaluate a system's performance against a bound. Here, measurements such as miss rate, CPI and the number of instructions executed are used to determine how close to "optimal" the performance is. This type of measurement is typically used by designers who try to find inefficiencies in various system structures.

## 2.3.2 Using benchmarks to study OS/architecture interactions

#### 2.3.2.1 What is a good set of benchmarks?

The answer to this question depends very heavily on the types of questions one is trying to answer. For example, a study focusing on the performance of file system design trade-offs would probably use workloads that exercised the file system. The benchmarks might be real programs such as compress and tar, or micro-benchmarks such as the Modified Andrew Benchmark [Ousterhout91]. In contrast, a study that is trying to determine the relative importance of the file system should use a wider range of benchmarks representative of the types of workloads a system would normally run.

For OS/architecture studies, both real applications and micro-benchmarks should be used. General performance trends should be measured using a large set of real applications. This prevents certain poorly performing components from dominating the results unless the components are critical to overall performance. Further, real applications determine the relative importance of various system components. Therefore, it is important to come as close as possible to real workloads when determining which hardware and software components are important to optimize. Once performance-critical hardware and software structures have been identified, micro-benchmarks can be used to examine the performance and interaction of specific components.

Neither type of benchmark is ideal. Micro-benchmarks suffer from several problems. First, they provide no understanding of the relative importance of various system components. This problem is best overcome by using representative applications to determine which hardware and/or software structures are important and then selecting micro-benchmarks that focus on the important structures. Second, micro-benchmarks can under or over emphasize certain hardware or software effects, such as cache misses, TLB faults and context switches. These changes in behavior can generate overly optimistic results or obscure the real cause of the performance problem.

Real applications do not suffer these drawbacks. They can, however, create very complex interactions among the hardware, the operating systems and system software services. While this is exactly the behavior a designer should measure, the complexity of the system can be overwhelming, making it difficult to isolate the source of specific performance problems.

#### 2.3.2.2 The system environment

Another important consideration is the system environment. Unlike application/architecture studies where the behavior of the software does not change from run to run, OS behavior can dramatically change between program runs. Policies such as

virtual to physical page mapping and scheduling, non-deterministic events such as interrupts, the locations of files in either the file cache or on disk, and the current state of OS data structures all influence the behavior of the system at a particular point in time.

Of course, the important question is, "Do changes in OS behavior significantly impact results?" The answer is most definitely yes. Sites, Kessler and Uhlig [Sites88, Kessler91, Uhlig95] have shown that page mapping within an address space can increase the cache miss rate enough to increase run time by several percent. It is also possible that random page mappings between address spaces will increase miss rates during some program runs. We have also observed that aging in kernel data structures can decrease performance. For example, the Mach 3.0 memory allocation algorithm for kernel data structures does not always distinguish between mapped and unmapped memory. As the system ages, this results in a higher reliance on mapped kernel memory. A workload executing on a system that has been alive for several days will incur up to 400% more TLB misses than the same workload run on a freshly booted machine.

These types of behavior have a number of ramifications. Studies that collect only one trace and then use the trace to drive many simulations may be relying on a trace that is particularly good or bad. This might cause the work to overlook important issues or focus attention on issues that occur very infrequently. For systems that process the trace on-the-fly, the variability between program runs may obscure the benefits of different implementations, making it difficult to evaluate design trade-offs where performance gains are only expected to be a few percent.

#### 2.3.2.3 Summary

Using benchmarks to study OS/architecture interactions is fundamentally different from benchmarking application/hardware interactions. Benchmarks must not only stress application/architecture interactions, but also OS/architecture interactions and application/OS interactions. This can create a very complex set of interactions, making it

difficult to isolate the cause(s) of performance problems. The irreproducable nature of the OS and environmental issues such as the system aging can cloud results, making system analysis even more difficult. But, all of these issues should be considered because they are all components of real system behavior.

# 2.4 Tools and techniques for analyzing OS/architecture interactions

There are a number of tools and techniques that can be used to analyze OS/architecture interactions. This section surveys these tools and how we have used them in our work. It is followed by a discussion of our monitoring system, Monster, and our simulation techniques.

## 2.4.1 Coarse-grain tools and measurement techniques

#### 2.4.1.1 Time and ps

Two of the most useful tools for evaluating the high-level behavior of a system are the Unix commands time and ps. time reports the estimated number of seconds a task spends in user mode, kernel mode, and the amount of idle time. ps reports the amount of time all living tasks have spent in user and system mode. By executing the ps command at the beginning and end of a benchmark, we are able to determine how much time a benchmark spends utilizing system services, such as the X display server, the AFS or NFS daemons, or the Mach BSD Unix server. We also use this information to verify that our Monster traces contain roughly the same proportion of benchmark and system service execution times as reported by ps.

Time and ps data are generated by sampling the state of the system at specific time intervals. This can create some error. For example, a benchmark that incurs a significant number of TLB misses will spend a lot of time in the kernel handling the TLB misses.

However, on our systems, some of the TLB handling code cannot be interrupted. While this code is executing, the system will not sample its state for time and ps statistics. Therefore, time and ps will underestimate the amount of time a task spends executing in kernel mode.

#### 2.4.1.2 Other system utilities: vmstat, pstat

The operating system keeps numerous statistics on its behavior and interaction with specific hardware components. Tools like vmstat and pstat provide information on virtual and physical memory requirements, I/O activity, paging and swapping, and the number of interrupts per second. We use this information to determine if the system's paging activity is dominating performance.

#### 2.4.1.3 Profiling the kernel

Operating systems can be profiled to measure the number of times and the amount of time spent in each OS function. OS designers use this information to identify which areas of the OS are most heavily used and to focus optimization techniques on those areas. For example, McRae [McRae91] has shown that the interface between the machine dependent and machine-independent virtual memory functions in Mach is one source of performance loss. Optimizing this interface could significantly reduce the cost of virtual memory management in Mach.

Profiling can also be used to determine the cost of primitive OS functions such as flushing the cache or memory-to-memory copy (bcopy). Architects can use this information to redesign specific aspects of the architecture, reducing the frequency and/or cost of expensive primitives.

#### 2.4.1.4 Software event counters

Software event counters embedded in the OS can be a very effective tool for measuring various performance problems. Usually incurring very low overhead (e.g., 3 or 4 instructions), counters can identify frequently used modules or objects. They can also identify a significant increase in the use of a module or object. This information can be invaluable to a designer tweaking a system's performance.

Software event counters, however, provide no information about the cost<sup>1</sup> of using a module or object. Therefore, one must be very careful when using counters to determine the importance of components because without knowing the cost, software counts can be misleading.

#### 2.4.1.5 Summary of coarse-grained tools

Understanding the system's behavior at the highest level is an important part of measuring OS/architecture interactions. Tools such as time, ps, and vmstat help to characterize a workload's interactions with various software and hardware components. The major limitation of coarse-grained tools is their inability to provide detailed, cycle-by-cycle information about how the software is interacting with the hardware. This information is crucial to understanding the performance and behavior of the architecture and its interaction with the software system.

#### 2.4.2 Fine-grained tools and measurement techniques

#### 2.4.2.1 Cycle and event counters

To measure and understand the behavior of the hardware, it is important to obtain fine-grained, cycle-by-cycle measurements. One approach is to use hardware and software

1. Cost as measured by the number of cycles.

counters to time and count specific events. One of the basic measurements this technique can obtain is the hardware efficiency measure, CPI.

-7;;-

## CPI = number of cycles/number of instructions

Using a cycle and an instruction counter that increments every instruction, we computed the CPI for each of our benchmarks (see Chapter 1).

Cycle counter's value at the entry and exit points of a code fragment, we can build a histogram of the code fragment's execution times, allowing us to compute the average execution time and the distribution of execution times. This method provides a much more accurate picture than the micro-benchmark technique, because the timing can be collected while real workloads execute, allowing the measurements to accurately capture the effects of hardware stalls such as TLB and cache misses.

More sophisticated counters can record hardware events such as cache and TLB misses, write buffer stalls, mis-predicted branches, floating point and integer muliply/divide stalls and superscalar issue rates<sup>1</sup>. Currently, several microprocessors, including the DEC Alpha and IBM RS/6000, provide these types of on-chip counters. A recent work by Cvetanovic et al. [Cvetanovic94] used the Alpha's hardware monitoring counters to measure its performance across a range of workloads.

Counters are very good at obtaining information about the performance of hardware and software structures. However, they cannot be used to evaluate the effectiveness of design trade-offs. For this, we must turn to tracing tools used in conjunction with trace-driven simulators.

<sup>1.</sup> For superscalar processors.

#### 2.4.2.2 Tracing tools

The most common example of software-based tracing tools are code annotation tools such as pixie and AE [Larus90, Smith91]. These tools annotate a program with extra instructions which generate a trace of all memory references. Recently, Chen [Chen93a] has extended the technique to include the operating system. By annotating every application, daemon, server and the operating system, Chen has been able to produce address traces which contain most of the system's activity. This is an important extension to the code annotation technique because it enables OS/architecture studies without additional hardware. Other researchers can use Chen's tools to annotate their operating systems and investigate OS/architecture interactions.

However, this approach suffers from several drawbacks. First, it is not possible to annotate the entire kernel, leaving some, perhaps important, portions of the operating system untraced. Second, it provides no information about the performance of the operating system on the hardware being traced. Hardware events such as cache misses and write buffer stalls are not reflected in the address trace. Detailed hardware models must be constructed in order to investigate performance problems. Third, the annotated code increases the run time of all software and changes the memory reference pattern. These changes can alter the behavior of the system and must be accounted for by the simulation tools.

A recently developed approach for tracing the operating system is called -driven simulation [Uhlig94c]. Using a hardware trap to expose events, such as cache or TLB misses, to the software, trap-driven simulation can be very fast because it relies on the hardware to process unimportant events such as cache hits. This reduces the time distortion caused by simulation. Further, because the hardware triggers the tracing mechanism, neither the application nor the operating system needs to be annotated. Hence,

there is almost no distortion in the memory system. We discuss Uhlig's prototype trapdriven simulator, Tapeworm, in Section 2.5.3 (p. 31).

A third type of tracing mechanism is a hardware monitoring system. Using a hardware monitor attached to the pins of the CPU, the monitor captures traces of all system activity, including address references and stall cycles. Because the monitor is autonomous from the processor, it can capture the traces without distorting the behavior of the system. However, when the hardware monitor's storage capacity fills, the processor must stall while the trace-buffer is processed. This creates distortion at regular intervals during a program run, using making outstanding asynchronous events such as disk I/Os appear almost instantaneous. We discuss our hybrid hardware/software monitoring system in Section 2.5.2 (p. 28).

#### 2.4.2.3 Summary of tools and techniques

As we have seen, a wide range of tools and techniques can be used to help in the study of OS/architecture interaction. Coarse-grained tools should be used first, to understand issues such as 1) which services an application uses and how much time is spent in each service; 2) which kernel routines are used the most; 3) whether an application creates activity, such as paging, that will dominate all other performance issues. Fine-grained tools can then focus on specific areas of concern, measuring the cycle-by-cycle interactions between the hardware and software, and identifying hardware and software components that cause performance loss.

#### 2.5 Our approach

The previous sections have outlined various issues that are important to consider when studying OS/architecture interactions. In this section, we present our approach and how it resolves some of the issues raised in the first part of this Chapter.

| Workload   | Description                                                                                                                                                          |  |  |  |  |  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| gcc        | The GNU C compiler (version 2.6)                                                                                                                                     |  |  |  |  |  |

| groff      | GNU C++ implementation of the UNIX nroff text formatting program (version 1.09).                                                                                     |  |  |  |  |  |

| gs         | Ghostscript (version 2.4.1) distributed by the Free Software Foundation. Renders and displays a single postscript page with text and graphics in an X display window |  |  |  |  |  |

| lOzone     | A sequential file I/O benchmark that writes and then reads a 10 Megabyte file. Written by Bill Norcott.                                                              |  |  |  |  |  |

| jpeg_play  | The xloadimage program written by Jim Frost. Displays four JPG images.                                                                                               |  |  |  |  |  |

| mab        | John Ousterhout's Modified Andrew Benchmark [Ousterhout89].                                                                                                          |  |  |  |  |  |

| mpeg_play  | mpeg_play V2.0 from the Berkeley Plateau Research roup. Displays 610 frames from a compressed video file [Patel92].                                                  |  |  |  |  |  |

| nroff      | Unix text formatting program shipped with Ultrix 3.1.                                                                                                                |  |  |  |  |  |

| ousterhout | John Ousterhout's benchmarks suite from [Ousterhout89].                                                                                                              |  |  |  |  |  |

| sdet       | A multiprocess, system performance benchmark which includes programs that test CPU, OS and I/O performance. From the SPEC SDM benchmark suite.                       |  |  |  |  |  |

| verilog    | Verilog-XL (version 1.6b) simulating the logic design of an experimental microprocessor.                                                                             |  |  |  |  |  |

| video_play | A modified version of mpeg_play that displays 610 frames of an uncompressed video file.                                                                              |  |  |  |  |  |

**Table 2.3 Workloads**

These are the workloads used throughout this dissertation. Some experiments use a subset of the entire suite or a single workload for illustration.

#### 2.5.1 Workloads

As discussed in Section 2.5.1 (p. 27), the choice of workloads can completely determine the outcome of an experiment. For example, to show bad TLB performance one should use the SPEC nasa7 program or the UNIX compress utility; to show bad D-cache performance, use Spice or compress. However, our goal is to understand OS/architecture interactions across a range of applications and to put various performance trends into perspective. Therefore, we used a wide range of applications described in Table 2.3 (p. 27). We also describe the operating systems in Table 2.4 (p. 28).

| Operating<br>System | Description                                                                                             |  |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------|--|--|--|--|

| Ultrix              | Version 3.1 from Digital Equipment Corporation                                                          |  |  |  |  |

| OSF/1               | OSF/1 1.0 is the Open Software Foundation's version of Mach 2.5                                         |  |  |  |  |

| Mach 3.0            | Carnegie Mellon University's version mk77 of the kernel and nk38 of the UNIX server                     |  |  |  |  |

| Mach3+AFSin         | Same as Mach 3.0, but with the AFS cache manager (CM) running in the UNIX server                        |  |  |  |  |

| Mach3+AFSout        | Same as Mach 3.0, but with the AFS cache manager running as a separate task outside of the UNIX server. |  |  |  |  |

**Table 2.4 Operating systems**

The basic operating systems were used in this dissertation: Ultrix, OSF/1 and Mach 3.0. In Chapter 3, we use all 3 plus to variants on Mach to explore TLB performance issues. In Chapter 4, we only use Ultrix and Mach 3.0.

Workloads like mab and ousterhout exercise specific aspects of the OS/architecture interface. jpeg\_play is CPU intensive. Most of the rest of the benchmarks are more general, representative of workloads like digital-media, simulation, text formatting, and multiprogramming. These are some of the most interesting workloads, revealing complex interactions between various hardware and software components.

#### 2.5.2 Monster - a hybrid hardware/software monitoring system

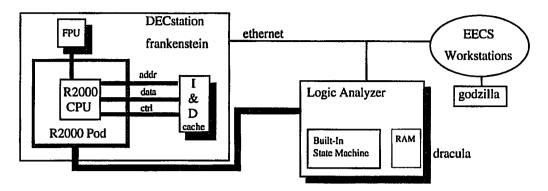

Monster is a hybrid hardware/software monitoring system which allows us to monitor a MIPS R2000 based DECstation 3100 (Figure 2.4, p. 29). Monster consists of: 1) a Tektronix DAS 9200 logic analyzer that is attached to the R2000's CPU pins and 2) custom software modules written to control the logic analyzer, its built-in state-machine and the traces captured by the logic analyzer. With access to the CPU pins, Monster can observe every processor event including floating point, write buffer and cache stalls. This allows Monster to accurately monitor the systems activity by either counting and timing specific events or by capturing traces of the hardware activity.

Figure 2.2 Monster monitoring system

Monster is attached to the CPU pins of a DECstation 3100. Because the caches are external to the R2000 processor, Monster can observe all system activity.

To count events, such as the number of instructions executed, we program the logic analyzer's built-in state machine and pattern matching hardware to watch for specific events. When the event occurs, a counter is incremented. This allows us to collect data measurements like CPI or miss rates without any distortion to the system under test. We also annotate the operating system with special markers that denote specific points in the software. This allows us to locate and time events, such as kernel crossing or TLB misses. These markers do introduce some distortion into the system. However, we have measured the amount of distortion introduced and it is usually under 2%. Further, most of the experiments can correct for the distortion.

It is also possible to gather fine-grained timings by using the logic analyzer's memory buffer to record timestamps. We use this technique to measure the average cost of a TLB miss. The TLB miss handler is annotated with markers at its entry and exit points. Every time the logic analyzer detects one of the markers, it write the current timestamp into its buffer memory (Figure 2.5, p. 30). Once the buffer is full, the timestamps are

<sup>1.</sup> The markers are implemented by performing an uncached load into register R0 from an address in the kernel's text segment. This technique was taken from Torrellas [Torrellas92].

| <u>Marker</u>  | Time (in nanoseconds) | <u>Delta</u> |

|----------------|-----------------------|--------------|

| tlb miss entry | 200                   |              |

| tlb miss exit  | 1400                  | 1200         |

| tlb miss entry | 20000                 |              |

| tlb miss exit  | 21400                 | 1400         |

| tlb miss entry | 42000                 |              |

| tlb miss exit  | 43000                 | 1000         |

Figure 2.3 Logic analyzer buffer with timestamps

The logic analyzer buffer can store timestamps for specific events detected by the state machine. Processing the data generates a histogram of timings that can be used to compute various statistics such as the average amount of time spent in a routine and the standard deviation.

processed and used to compute the average amount of time spent in each TLB miss routine.

#### 2.5.2.1 Monster traces

Probably the most important use of the logic analyzer is to gather traces of the system's activity. The traces include all instruction and data references as well as every stall cycle. We use the traces to drive various trace-driven simulators that model and analyze various system performance issues.

Because of the finite amount of space available in Monster's trace buffer (512-K entries or 256-K cycles), we adopt two different approaches to gathering traces. The first approach forces the system to stall while the trace buffer is emptied (Figure 2.6, p. 31). This is done by entering a stall loop in the kernel's clock interrupt handler. Using this method, we can gather contiguous traces of each workload. The second approach, called trace sampling, does not stall the processor when the buffer fills. Instead, the workload is executed multiple times and during each program run, a sample is captured from a different portion of the workload. Capturing 50 or more samples usually provides enough data to accurately characterize specific aspects of the system's behavior.

Figure 2.4 Capturing a contiguous trace