# Design, Implementation and Use of the MIRV Experimental Compiler for Computer Architecture Research

by

## David Anthony Greene

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 2003

Doctoral Committee:

Professor Trevor Mudge, Chair Assistant Professor Todd Austin Emeritus Professor Ronald Lomax Assistant Professor Gary Tyson Dr. Thomas Puzak, IBM Corporation

### ABSTRACT

# Design, Implementation and Use of the MIRV Experimental Compiler for Computer Architecture Research

by

David Anthony Greene

Chair: Trevor Mudge

This dissertation introduces MIRV, an experimental compiler developed for computer architecture research. We discuss the design and implementation of the compiler and use it to conduct studies of various techniques to tolerate memory latency. On the instruction side, a thorough examination of hardware and software prefetching techniques is performed to evaluate their utility on several modern computer designs. Various points of ambiguity in the literature are identified and the consequences of their specification are studied. A framework for describing software instruction prefetching algorithms is developed and extensions to current techniques are analyzed. Previous research has shown that larger data register sets than are currently available in modern microprocessors are desirable. Various extensions to this research are explored to further increase the utility of the register file.  $\begin{tabular}{c} \hline \end{tabular} \hline \end{tabular} \end{tabular} \begin{tabular}{c} \hline \end{tabular} \end{tabua$

To my family, with love and thanks.

## ACKNOWLEDGEMENTS

Many people contributed to the success of this work and while I would like to acknowledge individually each by name, I would inevitably leave out deserving friends and relatives. Even the short list contained in these paragraphs is likely incomplete. I apologize in advance for such omissions and convey my deepened respect and admiration to all who contributed to the extraordinary experiences I have been fortunate to enjoy.

First and foremost I thank God – Father, Son and Spirit - for His guidance, strength and unconditional love. It is only with His aid that I have been able to complete this task.

My family has been a tremendous source of love, encouragement and inspiration. The support from my parents, Tom and Joleen Greene, and my sisters Amy Greene, Cathy Greene and Nancy Germanson kept me going not only through this specific task but through my entire life. I love all of you *so much*!

I also wish to thank Trevor Mudge, my advisor, and the entire dissertation committee for their insight and guidance. Trevor in particular had the grace to gently push this sometimes stubborn student forward without creating unnecessary tension and stress. His experience and wisdom helped me out of more than one jam.

The students at the University of Michigan provide tremendous support and stress relief. I worked for many years with Matt Postiff on the MIRV project and consider him to be my first sounding board and source of ideas. Likewise, Kris Flautner, Charles Lefurgy, David Helder and Dave Oehmke contributed significant amounts of thought and effort to this project. Steve Raasch and I entered the program at the same time and have been great friends and collaborators since our first computer architecture course at UM. Troy Nolan also provided social outlets and humor at just the right times.

The spiritual support provided by St. Mary Student Parish in Ann Arbor, MI is invaluable. In particular I wish to thank Fr. Tom Firestone, Fr. Dennis Glasgow, S.J., Pat Waters, Anita Bohn, Gretchen Baumgardt, Anna Moreland and Mike Moreland for their individual attention to my spiritual direction and growth. I also wish to thank the many members of the St. Mary's Peace and Justice Commission and Rite of Christian Initiation of Adults (RCIA) program, in particular Derek Yip-Hoi, Arun D'Souza, Steve Coffman, Anita Chiappetta, O.P., Gene Poore, O.P. and Emily Malleis.

Most of my friends in Ann Arbor come from the St. Mary's Graduate Student/Young Professional Discussion Group. In addition to providing a wonderful intellectual and social environment, this group has taught me what it means to create friendships. Thank you so much to all of you wonderful people!

The REFRESH young adult diocesan retreat through the Catholic diocese of Lansing, MI filled a spiritual gap as I could never have imagined. I was fortunate enough to work with the planning team for three retreats. Thanks, guys, for all of your encouragement, patience and understanding.

Special thanks goes to Ken Laberteaux for graciously and judiciously providing guidance through his own experience of finishing his doctoral degree. Even more importantly, Ken has been a good friend.

My full-time job in Ann Arbor has been in the music scene (I was a graduate student in my spare time) and I owe much of that to that wonderfully wacky group known as The Johnstown Cats swing band. The fabulous blend of Mike Sasena and trumpet, J. Dylan Clyne and Brody DeYoung on sax, Jeff Balcerski on trombone, Rob Felty on drums, Mark stock on guitar, Pete Klimecky on bass and the bang-up vox trio of Joe Mancuso, Chris Milas and Debbie Schooler provided just enough cover for this wayward tickler to keep the missed notes sufficiently hidden. Kudos also go out to former Cats Paul Forti, Hyatt Ford, Markus Nee, Scott Iekel-Johnson and Jeremy Welland. I have learned copious amounts of music theory through their pushing for more and better charts and I treasure every moment of it. Thanks guys for a wonderful, wonderful time!

Last but hardly least I must acknowledge my good and dear friends Mike and Jolene Sasena. Mike made the trek with me from the University of Notre Dame into enemy territory and our shared experiences in the ND marching band, The Johnstown Cats and at St. Mary's forged a bond like none other. Though I've only known Jolene a few years I feel like we are family. Both provided more support and encouragement than I could possibly catalog. You are very dear to me and I love you both!

# TABLE OF CONTENTS

| DEDICATION                                                                                                                                                   | ii |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| ACKNOWLEDGEMENTS i                                                                                                                                           | ii |

| LIST OF TABLES                                                                                                                                               | x  |

| LIST OF FIGURES                                                                                                                                              | ci |

| LIST OF APPENDICES                                                                                                                                           | 7i |

| CHAPTERS                                                                                                                                                     |    |

| 1 Introduction                                                                                                                                               | 1  |

| 1.1 The Thesis $\ldots$                                                                                                                                      | 1  |

| 1.1.1 MIRV: An Experimental $C/C++$ Compiler                                                                                                                 | 1  |

| 1.1.2 Instruction Prefetching $\ldots$                                                                                                                       | 4  |

| 1.1.3 Register Allocation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                            | 6  |

| 1.2 Benchmarks                                                                                                                                               | 7  |

| 1.3 Simulation Environment                                                                                                                                   | 8  |

| 2 The MIRV C/C++ Experimental Research Compiler                                                                                                              | 0  |

| 2.1 Introduction $\ldots$ 1                                                                                                                                  | 0  |

| 2.2 Compilation Model $\ldots \ldots \ldots$ | 1  |

| $2.2.1  \text{Filters}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                     | 4  |

| 2.2.2 Attributes and the Compilation Process                                                                                                                 | 5  |

| 2.3 Intermediate Representation Language                                                                                                                     | 6  |

| 2.3.1 Future Improvements                                                                                                                                    | 4  |

| 2.4 Intermediate Representation API                                                                                                                          | 7  |

| 2.5 Back-end Design                                                                                                                                          | 2  |

|                                                                                                                                                              | 3  |

|                                                                                                                                                              | 5  |

|                                                                                                                                                              | 9  |

| 2.6 Language Support                                                                                                                                         | -  |

| $2.6.1$ C Support $\ldots$ $4$                                                                                                                               |    |

| $2.6.2  C++ \text{ Support } \dots $                   | -  |

| 2.7 Previous Work                                                                                                                                            |    |

| 3 | MIRV   | Dataflow Model                                                                                                                                 |

|---|--------|------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 3.1    | Introduction                                                                                                                                   |

|   | 3.2    | Dataflow Architecture Requirements                                                                                                             |

|   |        | 3.2.1 An Example: Reaching Definition Analysis                                                                                                 |

|   |        | 3.2.2 The Visitor Pattern                                                                                                                      |

|   |        | 3.2.3 The MIRV Dataflow Framework                                                                                                              |

|   |        | 3.2.4 Dataflow Analysis Abstraction Using Attributes                                                                                           |

|   |        | 3.2.5 The Attribute Flow Pattern                                                                                                               |

|   | 3.3    | Whole-Program Analysis and Transformation                                                                                                      |

|   | 3.4    | Conclusion                                                                                                                                     |

|   |        | 3.4.1 Future Directions                                                                                                                        |

|   |        |                                                                                                                                                |

| 4 |        | Transformation Model                                                                                                                           |

|   | 4.1    | Introduction                                                                                                                                   |

|   | 4.2    | Transformation Overview                                                                                                                        |

|   | 4.3    | Transformation Architecture                                                                                                                    |

|   |        | 4.3.1 IR Visitation $\ldots \ldots 125$                    |

|   |        | 4.3.2 Performing Transformations                                                                                                               |

|   |        | 4.3.3 Dataflow Patching 137                                                                                                                    |

|   | 4.4    | An Example: Dead Code Elimination                                                                                                              |

|   | 4.5    | Dataflow Patching                                                                                                                              |

|   | 4.6    | Conclusion                                                                                                                                     |

| 5 | Autor  | natic Debugging Tools for Experimental Compiler Developers 150                                                                                 |

| 0 | 5.1    | Introduction                                                                                                                                   |

|   | 5.2    | Regression Testing                                                                                                                             |

|   | 0.2    | 5.2.1         Regression Suite         152                                                                                                     |

|   |        | 5.2.2 Portability                                                                                                                              |

|   |        | 5.2.3 Larger Benchmarks                                                                                                                        |

|   |        | 5.2.4 Stress Testing                                                                                                                           |

|   |        | 5.2.5 Development Policy                                                                                                                       |

|   | 5.3    | Compiler Debugging                                                                                                                             |

|   | 0.0    | 5.3.1 Bug Categorization                                                                                                                       |

|   |        | 5.3.2 Bug Characterization Techniques                                                                                                          |

|   |        |                                                                                                                                                |

|   |        | 0                                                                                                                                              |

|   |        | 5.3.4Tool Categorization1665.3.5The MIRV Architecture168                                                                                       |

|   | E 4    |                                                                                                                                                |

|   | 5.4    | Experiment Methodology                                                                                                                         |

|   | F F    | 5.4.1 Other Compiler Toolchains                                                                                                                |

|   | 5.5    | Results                                                                                                                                        |

|   |        | 5.5.1 General Results $\dots$ 171                                                                                                              |

|   | F 0    | 5.5.2 A Case Study: newlib $\dots \dots \dots$ |

|   | 5.6    | Previous Work                                                                                                                                  |

|   | 5.7    | Conclusion                                                                                                                                     |

| 6 | Instru | ction Prefetching                                                                                                                              |

| - | 6.1    | Introduction                                                                                                                                   |

|   | 6.2    | Overview                                                                                                                                       |

|   |        |                                                                                                                                                |

|   |       | 6.2.1  | Sequential Prefetching                         | <br>. 182  |

|---|-------|--------|------------------------------------------------|------------|

|   |       | 6.2.2  | Branch History Guided Prefetching              | <br>. 183  |

|   |       | 6.2.3  | Call Graph Prefetching                         |            |

|   |       | 6.2.4  | Cooperative Prefetching                        |            |

|   |       | 6.2.5  | Compiler Hint Guided Prefetching               |            |

|   | 6.3   |        | ch Architecture $\ldots$                       |            |

|   | 0.0   | 6.3.1  | Literature Overview                            |            |

|   |       | 6.3.2  | Design Variation Points                        |            |

|   | 6.4   |        | are Algorithms                                 |            |

|   | 0     | 6.4.1  | A Software Instruction Prefetching Framework   |            |

|   | 6.5   |        | odology                                        |            |

|   |       | 6.5.1  | Prefetch Architecture                          |            |

|   |       | 6.5.2  | Software Prefetch Filters                      |            |

|   |       | 6.5.3  | Simulation Environment                         |            |

|   |       | 6.5.4  | Experiment Design                              |            |

|   | 6.6   |        | 8                                              |            |

|   | 0.0   | 6.6.1  | Baseline Results                               |            |

|   |       | 6.6.2  | Cooperative Prefetching Results                |            |

|   |       | 6.6.3  | BHGP Results                                   |            |

|   |       | 6.6.4  | CHGP Results                                   |            |

|   |       | 6.6.5  | Cooperative CHGP Results                       |            |

|   | 6.7   |        | bus Work                                       |            |

|   | 6.8   |        | ision                                          |            |

|   | 0.0   | 6.8.1  | Summary                                        |            |

|   |       | 6.8.2  | Future Work                                    |            |

|   | ~ -   |        |                                                |            |

| 7 | -     |        | egister Promotion on Modern Microarchitectures |            |

|   | 7.1   |        | uction                                         |            |

|   | 7.2   | -      | lative Register Promotion                      |            |

|   | 7.3   |        | Compiler Impact                                |            |

|   | 7.4   |        | tore Load Address Table                        |            |

|   | 7.5   |        | Architectural Impact                           |            |

|   | 7.6   |        | totype SLAT ABI                                |            |

|   |       |        | Register Save/Restore Enhancements             |            |

|   | 7.7   |        | dology                                         |            |

|   | 7.8   |        | 8                                              |            |

|   | 7.9   |        | ous Work                                       |            |

|   |       | 7.9.1  | Compiler Transformations                       |            |

|   |       | 7.9.2  | Architectural Structures                       |            |

|   |       | 7.9.3  | Cooperative Techniques                         |            |

|   |       | 7.9.4  | Other Related Work                             |            |

|   | 7.10  | Conclu | 1sion                                          | <br>. 310  |

| 8 | Expan | ded SL | AT Architectures                               | <br>. 311  |

| 0 | 8.1   |        | uction                                         |            |

|   | 8.2   |        | roblem                                         |            |

|   | 0.2   | 8.2.1  | The Problem                                    |            |

|   |       | 8.2.2  | A Bird's-Eye View                              |            |

|   |       | 0.2.2  |                                                | <br>· 01-1 |

| 8.3       | Design $\ldots \ldots 315$ |

|-----------|---------------------------------------------------------------------------------------------------------|

|           | 8.3.1 The Logical Rename Table                                                                          |

|           | 8.3.2 ABI Impacts                                                                                       |

| 8.4       | Further Enhancements                                                                                    |

|           | 8.4.1 Architectural Impact                                                                              |

|           | 8.4.2 Compiler Impact 324                                                                               |

| 8.5       | Methodology                                                                                             |

|           | 8.5.1 Simulation Environment                                                                            |

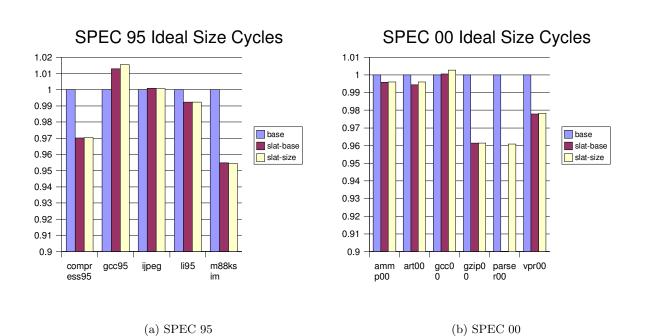

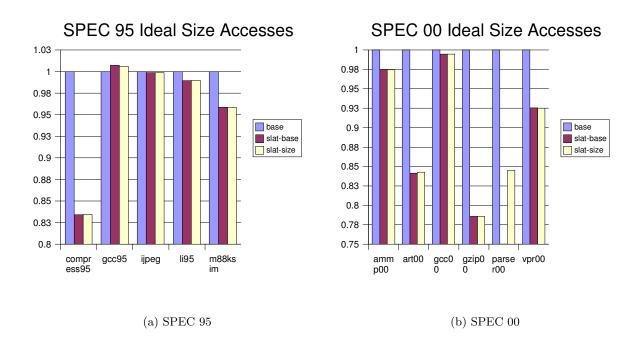

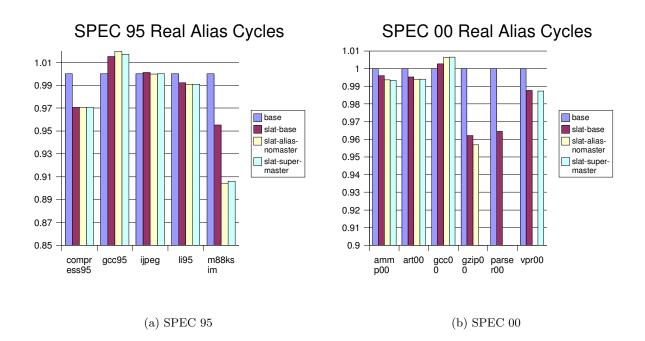

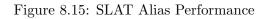

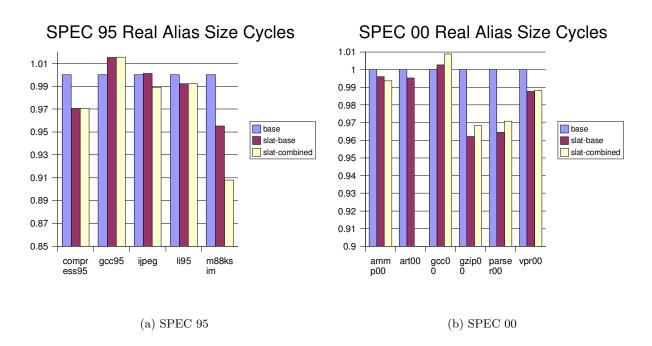

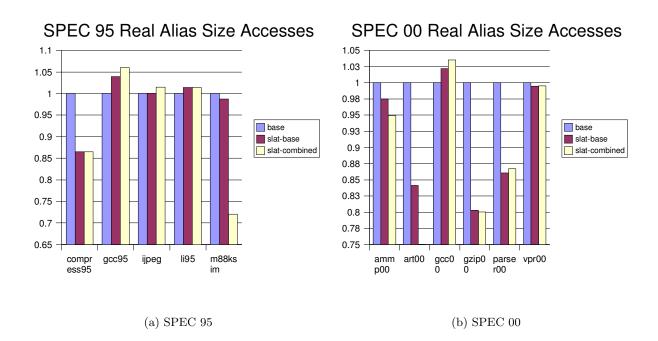

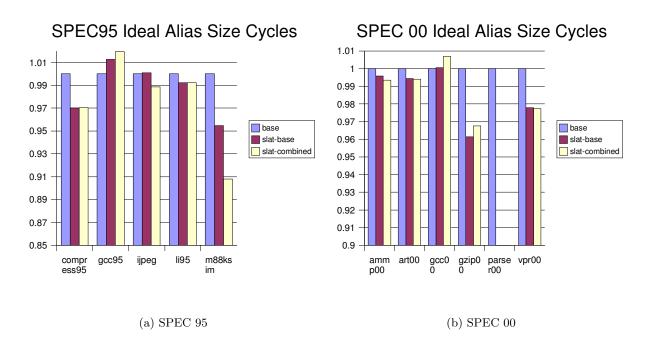

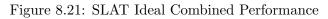

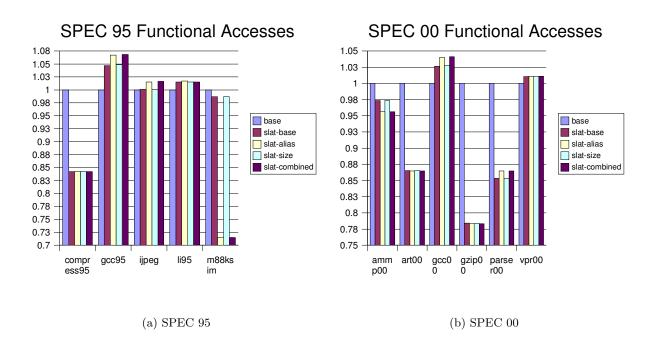

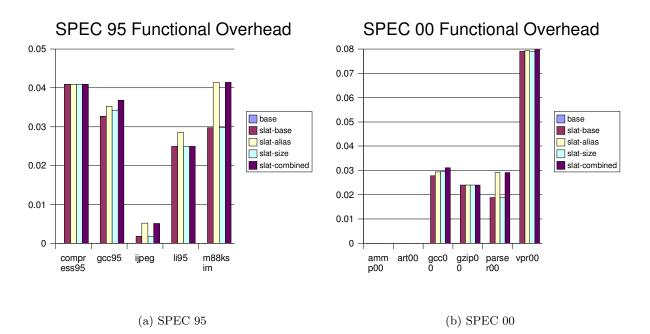

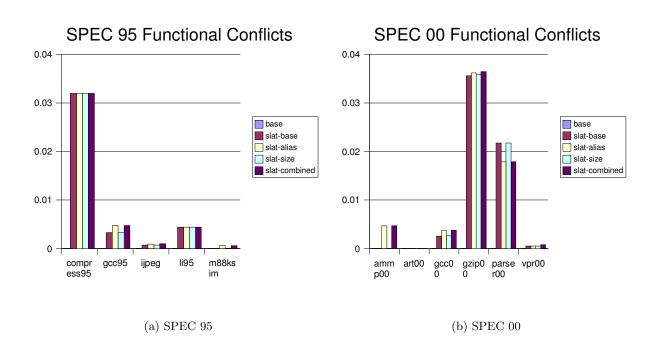

| 8.6       | Experimental Results                                                                                    |

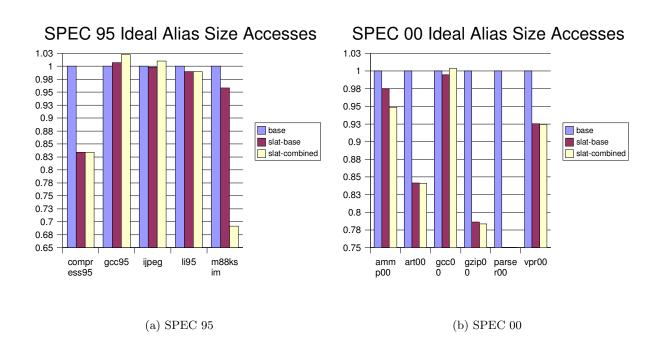

|           | 8.6.1 Size                                                                                              |

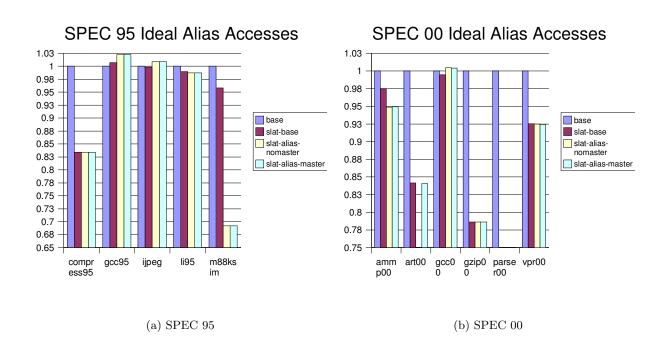

|           | 8.6.2 Aliases                                                                                           |

|           | 8.6.3 Alias and Size                                                                                    |

|           | 8.6.4 Overhead                                                                                          |

| 8.7       | Conclusion                                                                                              |

| APPENDICE | $\mathbf{S}$                                                                                            |

| BIBLIOGRA | <b>PHY</b>                                                                                              |

# LIST OF TABLES

## Table

| 1.1 | SPEC Reduced Datasets                    | 9   |

|-----|------------------------------------------|-----|

| 2.1 | MIRV Expressions                         | 17  |

| 2.2 | MIRV Statements                          | 20  |

| 2.3 | Branch Context Rules                     | 50  |

| 3.1 | Forward Dataflow Analysis Equations      | 68  |

| 3.2 | Backward Dataflow Analysis Equations     | 69  |

| 3.3 | Live Variable Expression Equations       | 72  |

| 3.4 | Live Variable Reference Equations        | 73  |

| 4.1 | Code Transformation Implementations      | 127 |

| 5.1 | Bug Isolation Tool Categorization        | 166 |

| 5.2 | Failure Category Descriptions            | 171 |

| 5.3 | lcc Failure Categorization               | 172 |

| 5.4 | MachSUIF Failure Categorization          | 179 |

| 6.1 | Simulation Parameters                    | 220 |

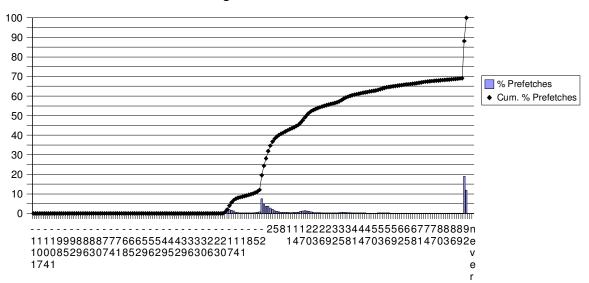

| 6.2 | Average BHGP Prefetch Lengths            | 256 |

| 7.1 | Simulation Parameters                    | 298 |

| 8.1 | Simulation Parameters                    | 330 |

| A.1 | MIRV Front-end Filters                   | 344 |

| A.2 | MIRV Back-end Filters                    | 345 |

| A.3 | Phase Ordering for O1 Optimization Level | 345 |

| A.4 | Phase Ordering for O2 Optimization Level | 346 |

| A.5 | Phase Ordering for O3 Optimization Level | 347 |

# LIST OF FIGURES

# Figure

| 2.1  | MIRV Compilation Flow                         | 12 |

|------|-----------------------------------------------|----|

| 2.2  | MIRV Compilation Model                        | 13 |

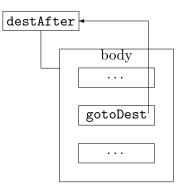

| 2.3  | gotoDest Structure                            | 22 |

| 2.4  | C Control with gotoDest                       | 23 |

| 2.5  | Attribute Representation in the MIRV IR       | 24 |

| 2.6  | The mirvCode Base Class                       | 28 |

| 2.7  | The mirvCode Attribute API                    | 28 |

| 2.8  | The mirvCode Structure and Transformation API | 29 |

| 2.9  | Common Linearizeable Attribute Tags           | 31 |

| 2.10 | The mirvSymbol Class                          | 32 |

| 2.11 | The mirvTypedSymbol Class                     | 32 |

| 2.12 | The mirvTypedSymbol Class                     | 33 |

| 2.13 | MIRV Type Classification Classes              | 33 |

| 2.14 | The mirvExpression class                      | 35 |

| 2.15 | Unary/Binary Expression Subclasses            | 36 |

| 2.16 | Array Expression Subclass                     | 37 |

| 2.17 | Field Expression Subclass                     | 38 |

| 2.18 | Function Call Expression Subclass             | 39 |

| 2.19 | Expression Leaf Classes                       | 39 |

| 2.20 | Expression Classifications                    | 40 |

| 2.21 | Backend Code Generation Flow                  | 43 |

| 2.22 | Quad Structure                                | 46 |

| 2.23 | Data Descriptor Structure                     | 47 |

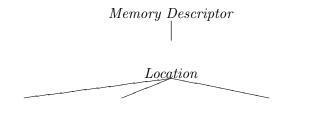

| 2.24 | Memory Descriptor Structure                   | 48 |

| 2.25 | Short Circuiting YACC Grammar                 | 51 |

| 2.26 | Short-Circuiting Example                      | 53 |

| 3.1  | Reaching Definition Example                   | 59 |

| 3.2  | The mirvVisitor Base Class                    | 63 |

| 3.3  | The mirvArrayToPointerVisitor Class           | 64 |

| 3.4  | The mirvAddExpression accept Member           | 64 |

| 3.5  | Forward Attribute Flow                        | 75 |

| 3.6  | Attribute Flow Objects                                              |

|------|---------------------------------------------------------------------|

| 3.7  | The mirvFlow Base Class                                             |

| 3.8  | Add Expression Flow    78                                           |

| 3.9  | Visiting Binary Tree Nodes                                          |

| 3.10 | Dataflow Attribute Manager Base Class                               |

| 3.11 | Dataflow Attribute Manager Class    80                              |

| 3.12 | Child Inherited Attribute Context Method Operation                  |

| 3.13 | Action Class                                                        |

| 3.14 | mirvVisitorAction Class                                             |

| 3.15 | mirvActionVisitor Class                                             |

| 3.16 | Templatized visitDouble 86                                          |

| 3.17 | mirvForwardFlow::visitDouble                                        |

| 3.18 | <pre>mirvForwardFlow::visit(mirvIfElseStatement *) 88</pre>         |

| 3.19 | <pre>mirvForwardFlow::visit(mirvWhileStatement *), Part 1</pre>     |

| 3.20 | <pre>mirvForwardFlow::visit(mirvWhileStatement *), Part 2</pre>     |

| 3.21 | mirvBackwardFlow::visitDouble                                       |

|      | <pre>mirvBackwardFlow::visit(mirvIfElseStatement *)</pre>           |

| 3.23 | <pre>mirvBackwardFlow::visit(mirvWhileStatement *), Part 1 94</pre> |

|      | <pre>mirvBackwardFlow::visit(mirvWhileStatement *), Part 2 95</pre> |

|      | Dataflow Class Hierarchy                                            |

|      | Backward Attribute Flow                                             |

|      | Attribute Stack State for Backward Flow                             |

|      | Live Variable Dataflow Attribute                                    |

|      | Live Variable addLive Implementation                                |

|      | Live Variable eraseLive Implementation 102                          |

|      | Live Variable getLiveSet Implementation                             |

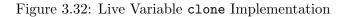

|      | Live Variable clone Implementation 105                              |

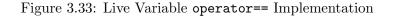

|      | Live Variable operator== Implementation                             |

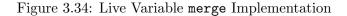

|      | Live Variable merge Implementation 105                              |

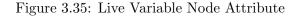

|      | Live Variable Node Attribute                                        |

|      | Live Variable Pre-Action                                            |

|      | Live Variable Post-Action                                           |

|      | Live Variable Pre-Visitor Function Visit                            |

|      | Live Variable Pre-Visitor Statement Visit                           |

|      | Live Variable Post-Visitor Statement Visit                          |

|      | Live Variable Post-Visitor Reference Visit                          |

|      | Live Variable Plugin                                                |

|      | Live Variable activate Method                                       |

|      | MIRV Alias Analysis Initialization Rules                            |

|      | MIRV Alias Analysis Expression Rules                                |

|      | MIRV Alias Analysis Statement Rules                                 |

|      | An Anonymous struct Type                                            |

|      | A Recursive struct Type                                             |

|      | Block Splitting                                                     |

| 0.43 |                                                                     |

| 4.1  | <pre>mirvTreeFlow::visit(mirvWhileStatement *) Implementation</pre> | 125 |

|------|---------------------------------------------------------------------|-----|

| 4.2  | Replacement Attribute Model                                         | 128 |

| 4.3  | Replacement Action Model                                            | 129 |

| 4.4  | Direct Replacement Action Model                                     | 130 |

| 4.5  | Direct Replacement execute                                          | 130 |

| 4.6  | Direct Replacement insertBefore                                     | 131 |

| 4.7  | Direct Replacement insertAfter                                      | 131 |

| 4.8  | Direct Statement Replacement Action Model                           | 132 |

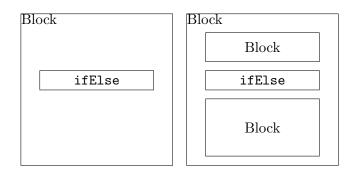

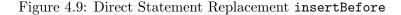

| 4.9  | Direct Statement Replacement insertBefore                           | 132 |

| 4.10 | Direct Statement Replacement insertAfter                            | 132 |

| 4.11 | Indirect Replacement Action Model                                   | 133 |

| 4.12 | Indirect Replacement execute Implementation                         | 134 |

| 4.13 | Indirect Statement Replacement Action Model                         | 135 |

| 4.14 | Indirect Statement Replacement insertBefore Implementation          | 135 |

| 4.15 | Setting while Statement Replacement Attributes                      | 136 |

| 4.16 | Setting Block Statement Replacement Attributes                      | 136 |

| 4.17 | Replacement Filter Helpers                                          | 137 |

| 4.18 | Backward IR Tree Traversal                                          | 138 |

| 4.19 | Dead Code Action Class                                              | 140 |

| 4.20 | Dead Code Assignment Action, Part 1                                 | 141 |

| 4.21 | Dead Code Assignment Action, Part 2                                 | 142 |

|      | mirvCode::replaceWith Implementation                                | 144 |

| 4.23 | Dead Code ifElse Action                                             | 146 |

| 4.24 | Dead Code Plugin                                                    | 147 |

| 4.25 | Dead Code activate Routine                                          | 147 |

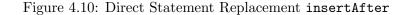

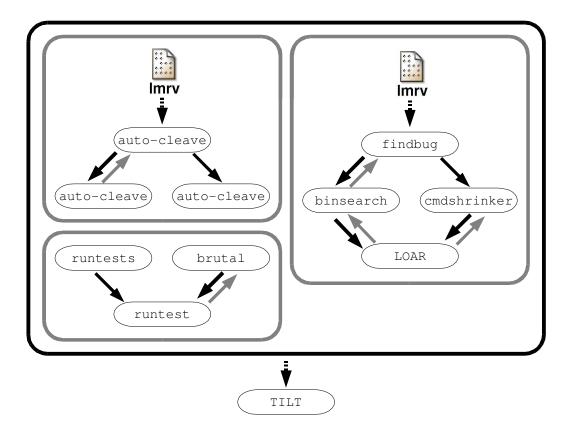

| 5.1  | MIRV Debug Flow                                                     | 167 |

| 6.1  | Software CGP Algorithm                                              | 184 |

| 6.2  | Cooperative Prefetching Algorithm                                   | 185 |

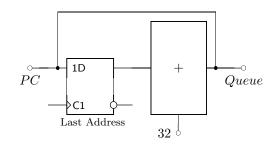

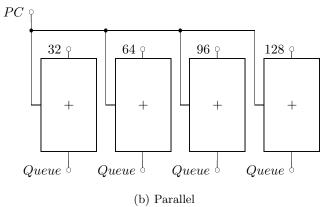

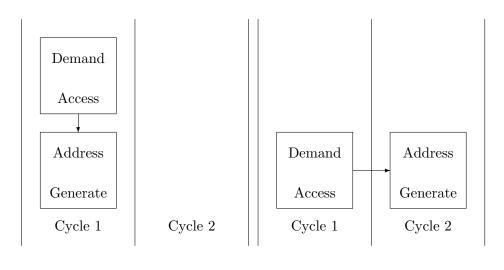

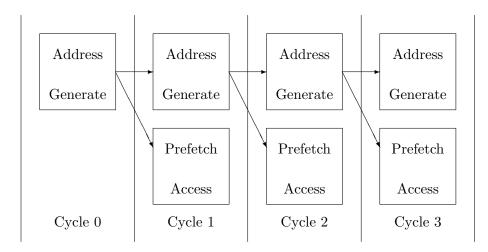

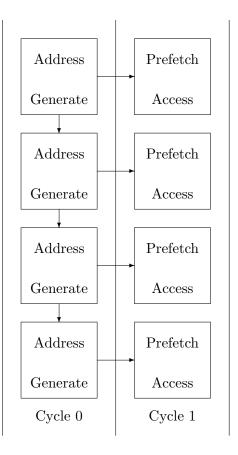

| 6.3  | Request Generation                                                  | 197 |

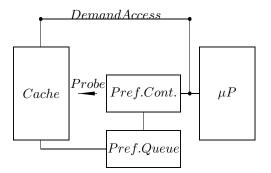

| 6.4  | Prefetch Architecture                                               | 200 |

| 6.5  | Generalized Prefetching Driver Algorithm                            | 201 |

| 6.6  | Generalized Prefetching Algorithm                                   | 202 |

| 6.7  | placeInPredecessors Algorithm                                       | 203 |

| 6.8  | placePrefetchesInCallers Algorithm                                  | 204 |

| 6.9  | countInstructions Algorithm                                         | 205 |

| 6.10 | countFunction Algorithm                                             | 206 |

| 6.11 | placePrefetchesInCallees Algorithm                                  | 207 |

| 6.12 | Prefetch Algorithm Step Policy                                      | 210 |

| 6.13 | Prefetch Initiation Architectures                                   | 216 |

| 6.14 | Prefetch Generation Timing                                          | 218 |

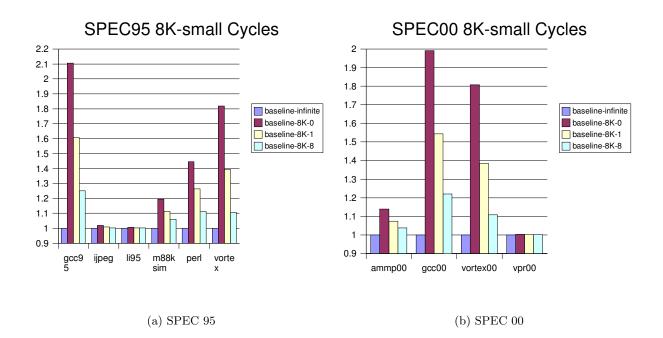

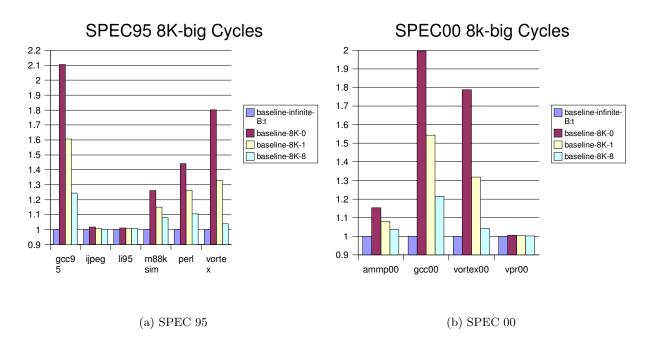

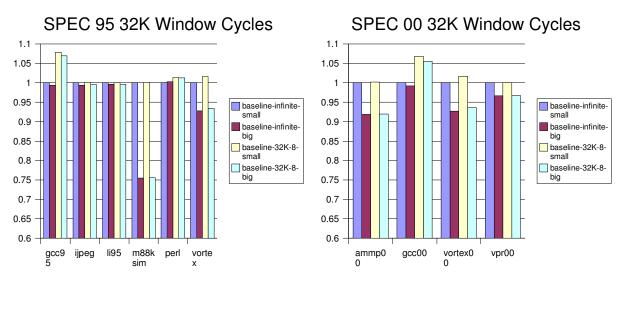

| 6.15 | Baseline 8K Sequential Prefetching, Small Window                    | 223 |

| 6.16 | Baseline 8K Sequential Prefetching, Large Window                    | 223 |

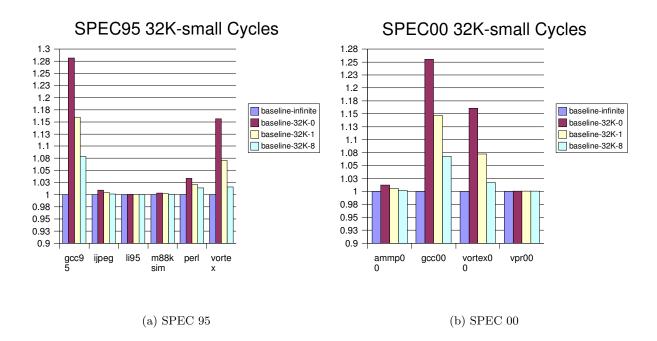

| 6.17 | Baseline 32K Sequential Prefetching, Small Window                   | 224 |

| 6.18 | Baseline 32K Sequential Prefetching, Large Window                   | 224 |

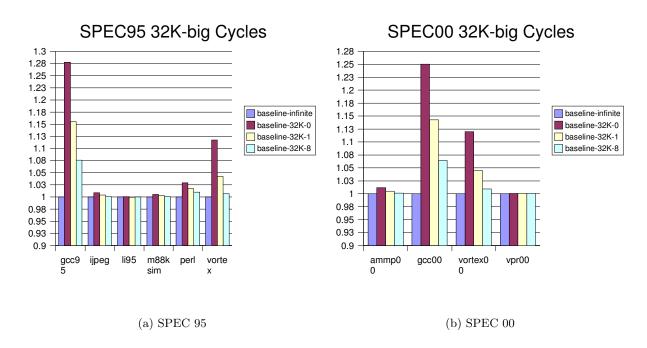

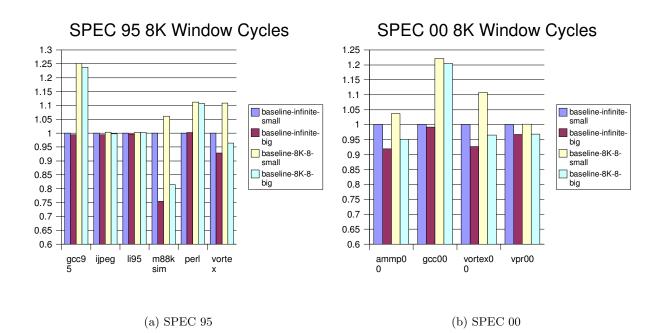

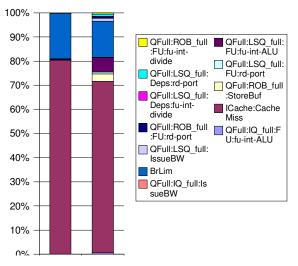

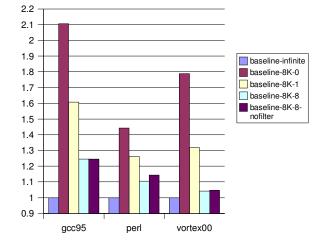

| 6.19 | Baseline 8K Window Performance                            | 226 |

|------|-----------------------------------------------------------|-----|

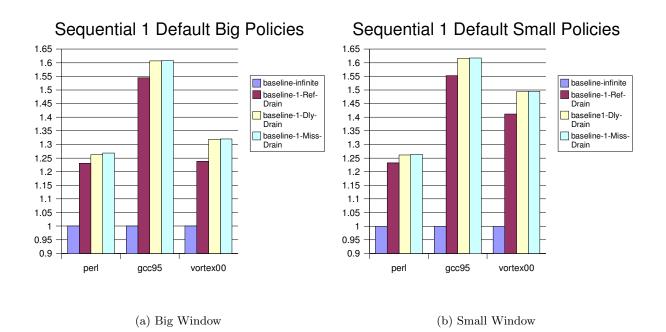

| 6.20 | Baseline 32K Window Performance                           | 227 |

| 6.21 | Fetch Loss Reasons                                        | 228 |

| 6.22 | Prefetch Filter Impact                                    | 230 |

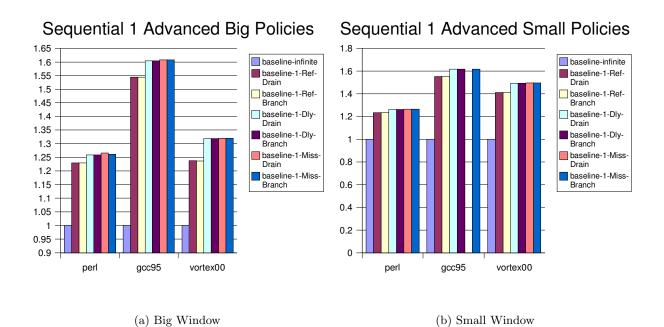

| 6.23 | Baseline Sequential-1 Default Queue Policies Performance  | 231 |

| 6.24 | Baseline Sequential-1 Advanced Queue Policies Performance | 231 |

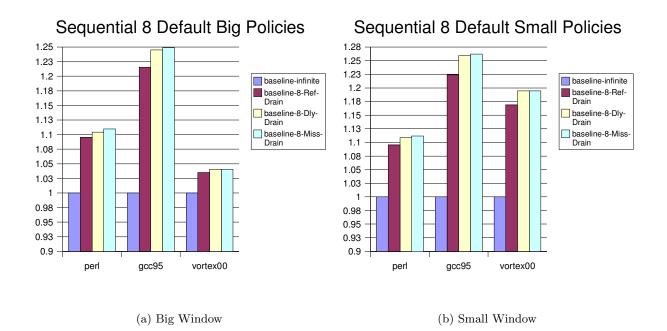

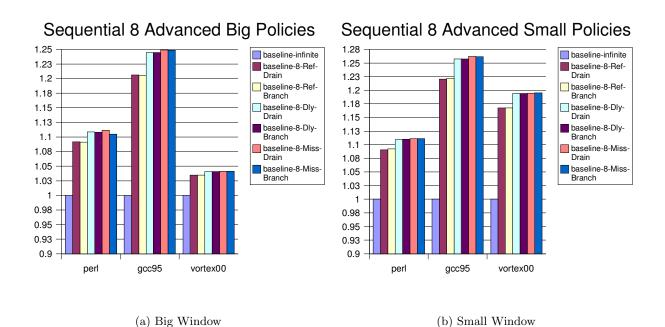

| 6.25 | Baseline Sequential-8 Default Queue Policies Performance  | 232 |

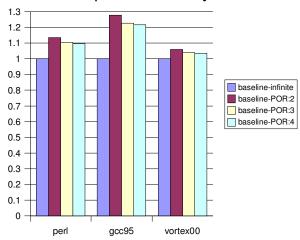

| 6.26 | Baseline Sequential-8 Advanced Queue Policies Performance | 232 |

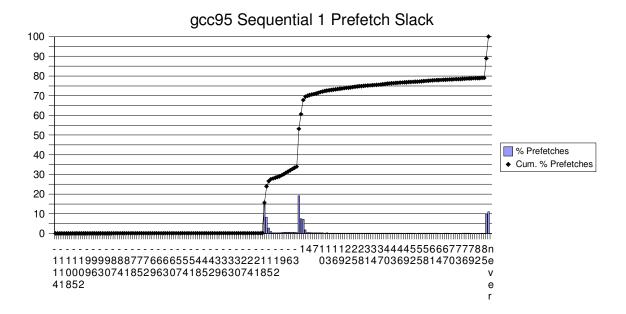

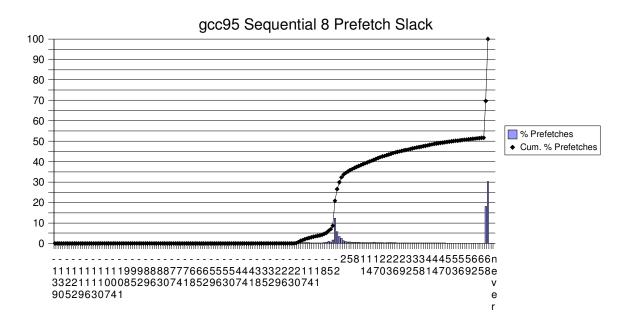

| 6.27 | Sequential Prefetching Slack                              | 234 |

| 6.28 | Baseline Sequential-8 Ports Performance                   | 236 |

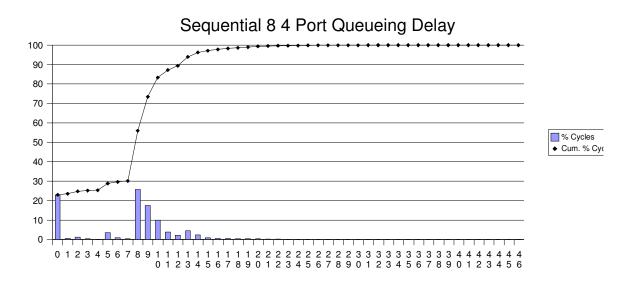

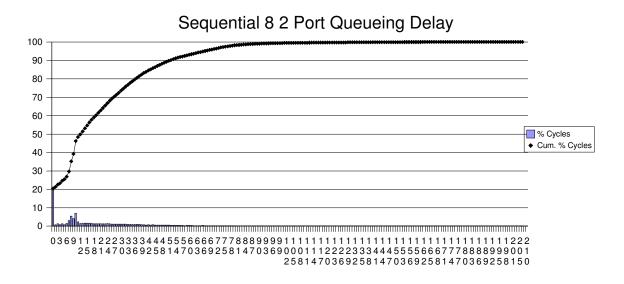

| 6.29 | Baseline Sequential-8 Ports Default Queueing Delay        | 237 |

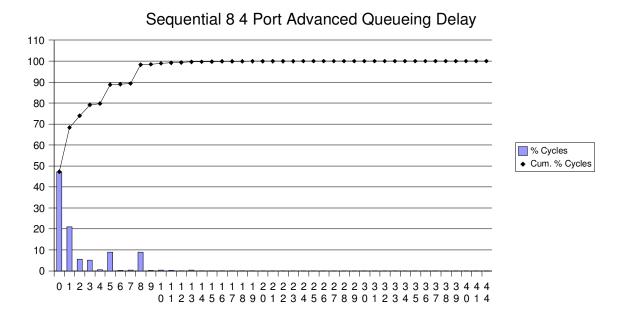

| 6.30 | Baseline Sequential-8 Ports Advanced Queueing Delay       | 238 |

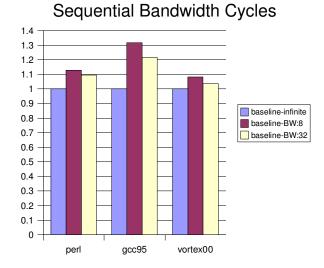

| 6.31 | Baseline Sequential-8 Bandwidth Performance               | 239 |

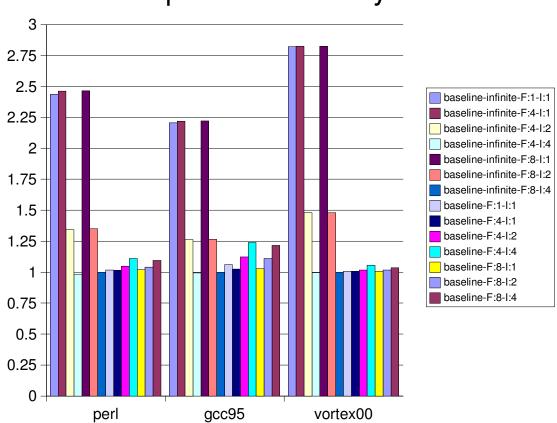

| 6.32 | Baseline Sequential-8 Width Performance                   | 239 |

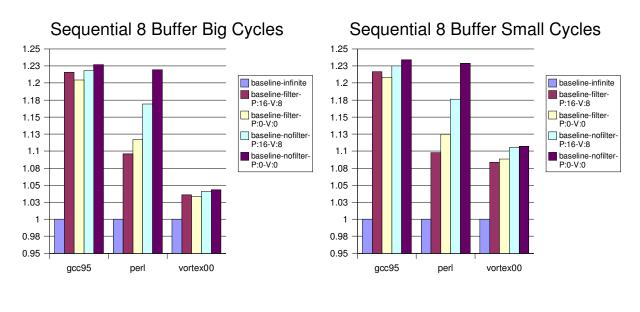

| 6.33 | Baseline Sequential-8 No Buffer Performance               | 242 |

| 6.34 | Static Prefetch Bloat                                     | 243 |

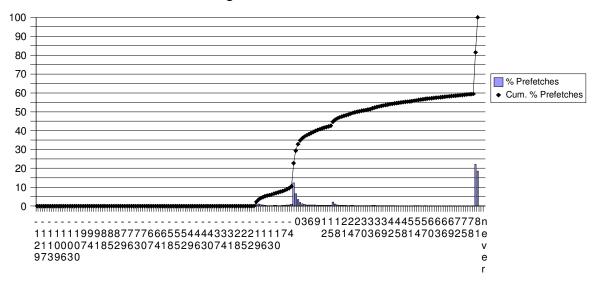

| 6.35 | Dynamic Prefetch Overhead                                 | 244 |

| 6.36 | Cooperative Prefetching Policies Performance              | 245 |

| 6.37 | Cooperative Prefetching Slack                             | 246 |

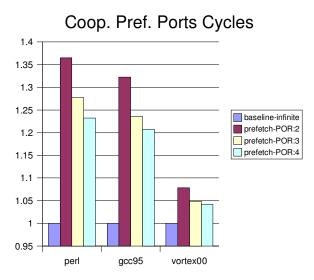

|      | Cooperative Prefetching Ports Performance                 | 247 |

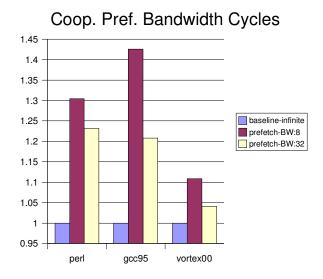

| 6.39 | Cooperative Prefetching Bandwidth Performance             | 247 |

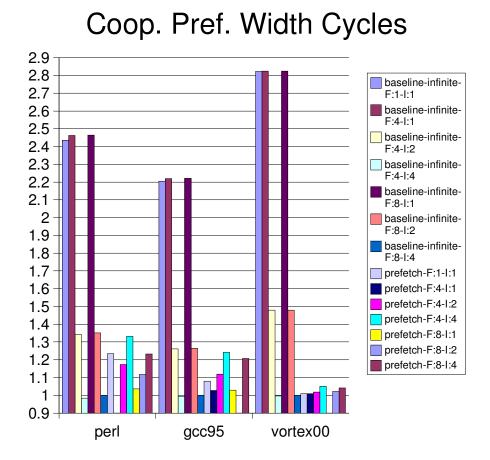

|      | Cooperative Prefetching Width Performance                 | 248 |

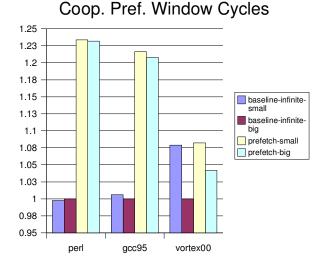

|      | Cooperative Prefetching Window Performance                | 249 |

|      | Example BHGP State                                        | 250 |

|      | Lower-Bound Pipeline Penalty                              | 250 |

|      | Upper-Bound Pipeline Penalty                              | 252 |

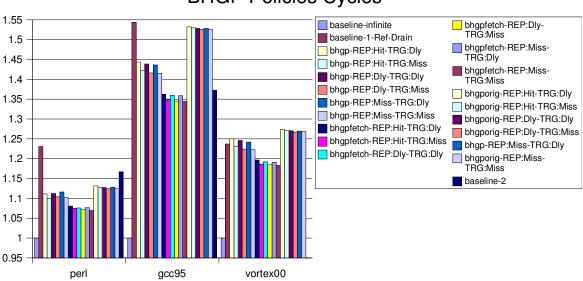

|      | BHGP Performance                                          | 254 |

| 6.46 | BHGP Slack                                                | 256 |

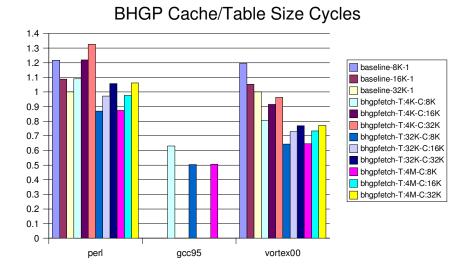

|      | BHGP Cache/Table Size Performance                         | 257 |

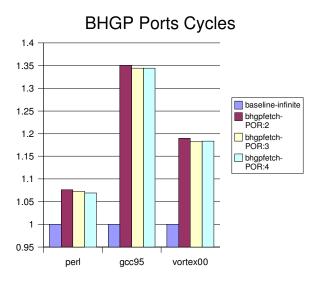

|      | BHGP Ports Performance                                    | 258 |

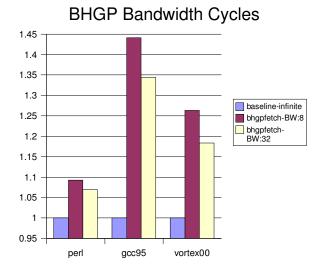

|      | BHGP Bandwidth Performance                                | 258 |

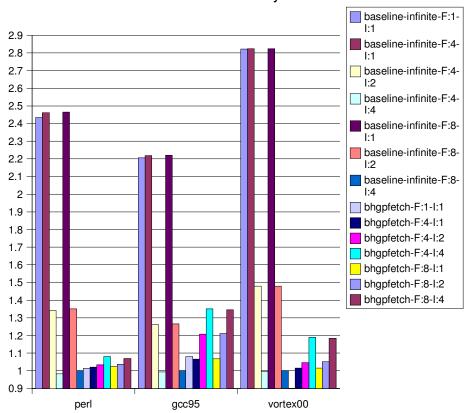

|      | BHGP Width Performance                                    | 259 |

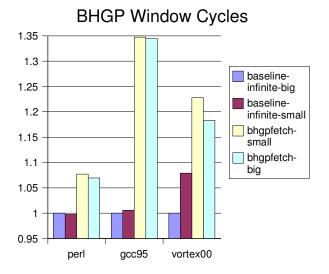

| 6.51 | BHGP Window Performance                                   | 259 |

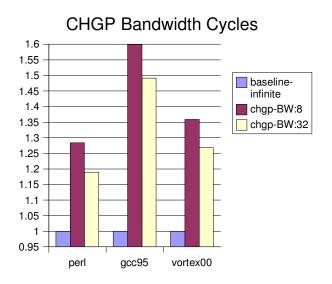

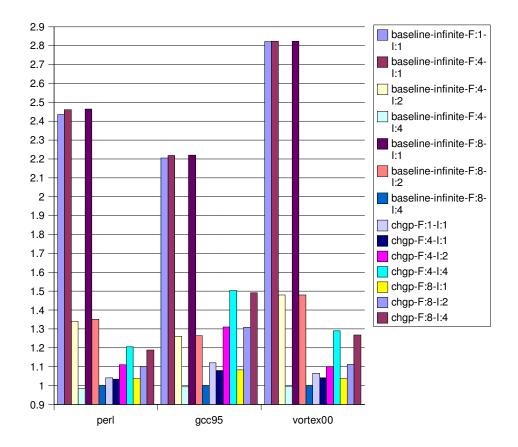

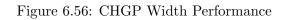

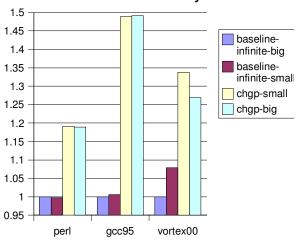

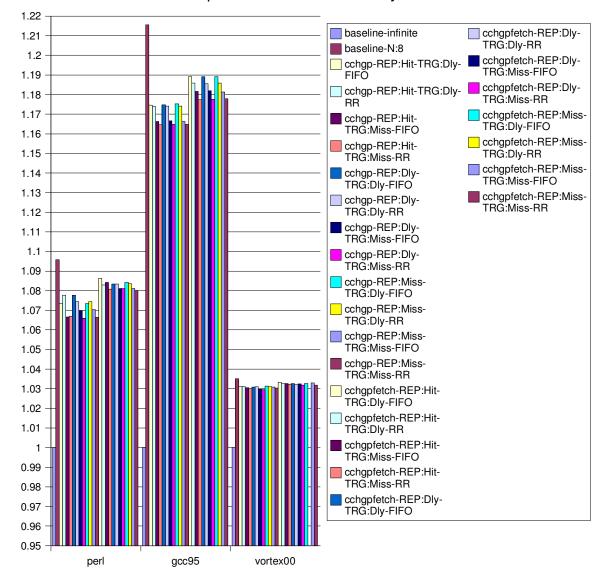

|      | CHGP Performance                                          | 260 |

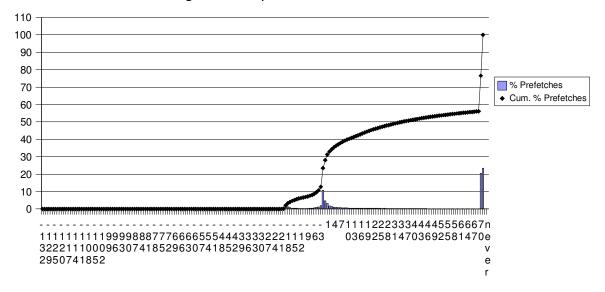

|      | CHGP Slack                                                | 261 |

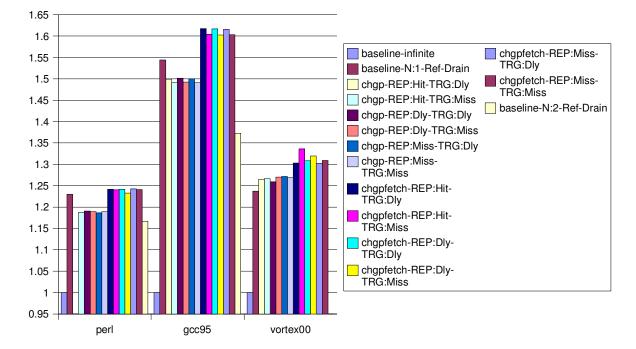

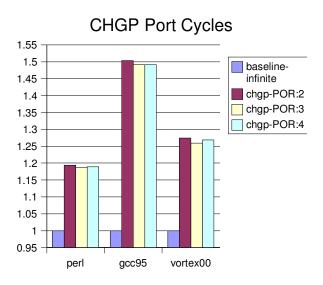

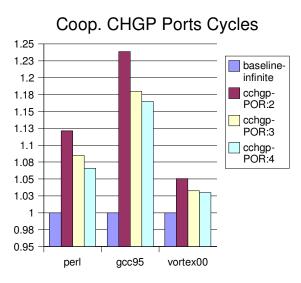

|      | CHGP Ports Performance                                    | 262 |

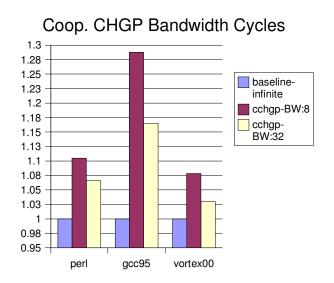

| 6.55 | CHGP Bandwidth Performance                                | 262 |

|      | CHGP Width Performance                                    | 263 |

|      | CHGP Window Performance                                   | 263 |

|      | Cooperative CHGP Performance                              | 265 |

|      | Cooperative CHGP Slack                                    | 266 |

|      | Cooperative CHGP Ports Performance                        | 267 |

|      | Cooperative CHGP Bandwidth Performance                    | 267 |

|      | Cooperative CHGP Width Performance                        | 268 |

|      |                                                           |     |

| 6.63 | Cooperative CHGP Window Performance             |

|------|-------------------------------------------------|

| 6.64 | Fetch-Based Cooperative Prefetching Performance |

| 7.1  | Register Promotion Example                      |

| 7.2  | Register Promotion Performed                    |

| 7.3  | Register Promotion Failure                      |

| 7.4  | Speculative Register Promotion                  |

| 7.5  | SLAT Operation                                  |

| 7.6  | Multiple Register Mappings                      |

| 7.7  | SLAT Register Renaming Impact                   |

| 7.8  | SLAT Aliasing Example                           |

| 7.9  | SLAT Performance                                |

| 7.10 | DL1 Accesses                                    |

| 7.11 | SLAT Prediction Rates                           |

| 7.12 | SLAT Performance                                |

| 7.13 | DL1 Accesses                                    |

| 8.1  | SLAT Aliasing Example                           |

| 8.2  | Speculative Promotion of Potential Aliases      |

| 8.3  | Physical Register Sharing                       |

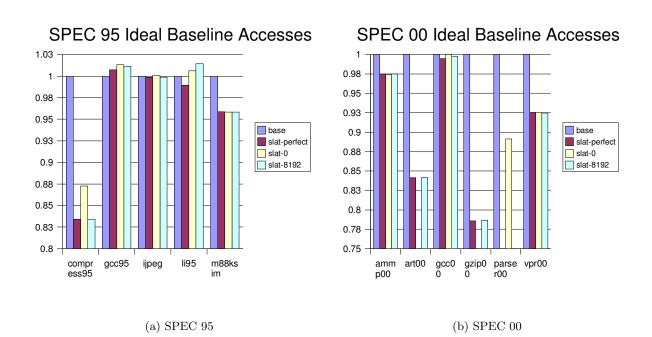

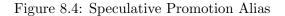

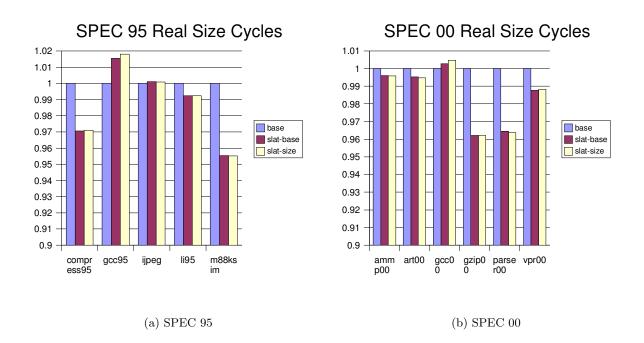

| 8.4  | Speculative Promotion Alias                     |

| 8.5  | Physical Register Sharing Difficulty            |

| 8.6  | LRT Operation                                   |

| 8.7  | LRT Pipeline Flow                               |

| 8.8  | Multiple-size Aliases Through a Union           |

| 8.9  | Multiple-size Aliases Through a Pointer         |

| 8.10 |                                                 |

| 8.11 | SLAT Size Performance                           |

| 8.12 | DL1 Size Accesses                               |

| 8.13 | SLAT Ideal Size Performance                     |

| 8.14 | DL1 Ideal Size Accesses                         |

| 8.15 | SLAT Alias Performance                          |

|      | DL1 Alias Accesses                              |

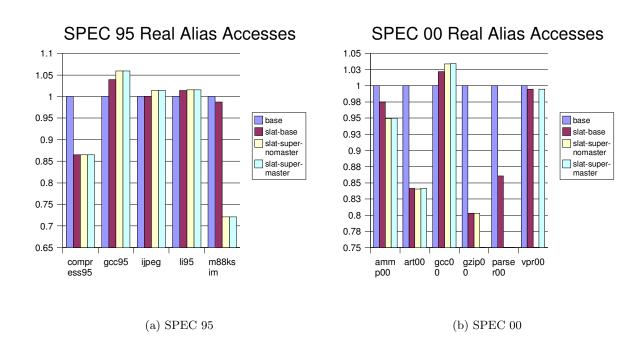

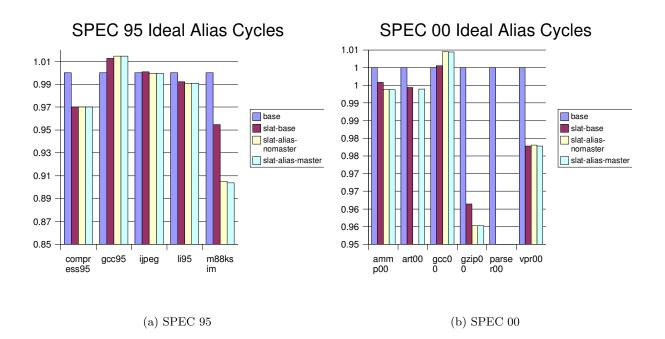

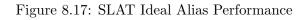

| 8.17 | SLAT Ideal Alias Performance                    |

| 8.18 | DL1 Ideal Alias Accesses                        |

| 8.19 | SLAT Combined Performance                       |

| 8.20 | DL1 Combined Accesses                           |

| 8.21 | SLAT Ideal Combined Performance                 |

| 8.22 | DL1 Ideal Combined Accesses                     |

|      | DL1 Functional Accesses                         |

| 8.24 | DL1 Functional Overhead                         |

| 8.25 |                                                 |

# LIST OF APPENDICES

## APPENDIX

| А | MIRV Optimization Filters and Phase Ordering      | 344 |

|---|---------------------------------------------------|-----|

| В | Suggestions for Computer Architecture Researchers | 348 |

## CHAPTER 1

# Introduction

# 1.1 The Thesis

The subject thesis of this dissertation is organized into three parts. The first concerns the MIRV compiler, a new research tool for computer architects and compiler developers. The second concerns the problem of instruction supply in modern computer systems and the third concerns the data supply problem in such machines.

### 1.1.1 MIRV: An Experimental C/C++ Compiler

Concerning the MIRV compiler:

- MIRV is an extensible and stable compilation tool-chain for computer architecture research.

- The design of MIRV leverages well-known software engineering practices and design patterns to present a modularized interface understandable by computer architects with rudimentary compiler background.

- MIRV provides an extensive set of regression testing and debugging tools that greatly eases the burden of compiler development for the computer architecture researcher.

- In terms of compiler correctness, MIRV outperforms several well-known research compilers currently available to computer architects in academia.

#### **Research Contributions**

We describe MIRV, an experimental C/C++ compiler for computer architecture research, in chapters 2, 3 and 4. MIRV has been designed to provide relatively easy accessibility to computer architects who may not be completely comfortable with compiler theory. It has been designed to provide a framework of pre-built components with which the researcher can construct new program analyses and transformations. The framework uses well-known software engineering design patters to provide a separation between program traversal, analysis and transformation.

The goal of the MIRV project has not initially focused on providing the best possible optimizing compiler around. Rather, the goal has been to provide a research platform at least as good as what is currently available. Chapter 5 presents some comparisons of MIRV to existing research compiler platforms.

Our work in compiler development has produced a set of research tools for computer architects. The MIRV compiler provides a framework for research into cooperative hardware/software design as illustrated in chapters 6, 7 and 8. Several novel features of the compiler tool-chain make it an attractive research platform.

The compiler operates in the traditional fashion, converting high-level source code into a high-level intermediate representation (IR). The high-level IR may be analyzed and transformed by a set of *filters*. A back-end phase converts the high-level IR into a lower-level quad-based IR which may be manipulated by additional filters. A final linear pass converts the quads to machine assembly code.

While the overall operation of the compiler is traditional, several unique features enhance its capabilities in the research environment. The IR itself is a high-level prefix-form tree. The high-level form preserves most of the information available at the source code level, making certain analyses and transformations easier. For example, dominator and postdominator computation is trivial given the structured tree form of the IR [1].

The prefix form of the tree allows the code generator to operate in a linear fashion as explained in section 2.6.1 of chapter 2. A simple LALR attribute grammar<sup>1</sup> is sufficient to generate code in a single pass without additional label patching passes.

The IR is also extensible. MIRV defines a *node attribute* interface for annotating information directly onto the IR tree. This is invaluable in the research environment because the compiler may mark points of interest in the program either for later phases of the compiler such as low-level code generation or it may embed information into the program binary which may be extracted by simulation software. This feature is used in the studies of chapters 7 and 8 to support speculative register allocation.

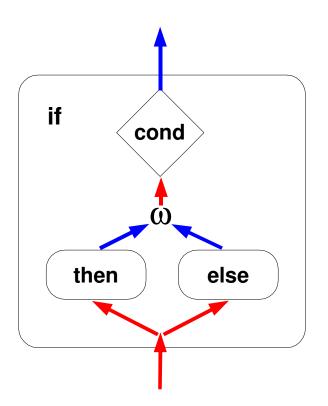

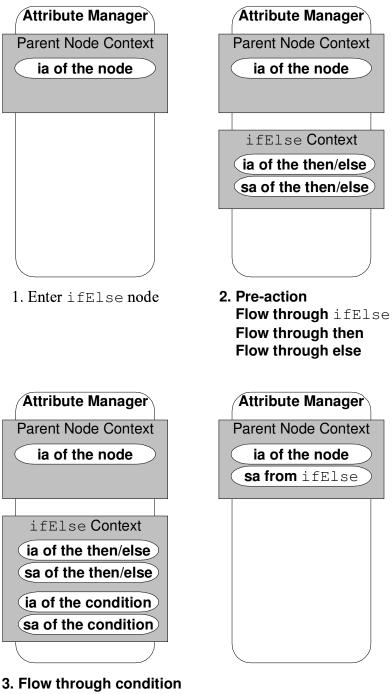

Chapter 3 presents a new software engineering design pattern called *Attribute Flow* for performing program dataflow analysis. This design pattern presents a hybrid of traditional iterative and more recent structural dataflow analysis algorithms. The high-level nature of the IR makes a structural dataflow engine desirable but deriving the dataflow equations for complex program structures can be challenging. Attribute Flow avoids this problem by iteratively applying structural dataflow equations at program control join points. The framework hides the details of the algorithm from the compiler developer, freeing him to

<sup>&</sup>lt;sup>1</sup>for example, as created with a tool such as YACC[2]

concentrate of the representation of dataflow information and the actions necessary at the leaf nodes of the IR tree.

MIRV also includes a unified framework for intra- and inter-procedural program analysis and transformation. Operation in the inter-procedural domain uses the same intermediate form and analysis objects as in the intra-procedural domain. This is primarily provided through an intermediate-form linking phase in the compiler. This capability provides the researcher with a powerful tool for exploration of whole-program compilation without the need for complex link-time or post-link binary rewriting tools. The same familiar compilation model and environment is available in both the intra-procedural and inter-procedural modes of operation.

Finally, we have developed a suite of tools for automatic compiler bug characterization to ease the process of compiler debugging. These are described in chapter 5. The tools leverage the IR linking capabilities of the compiler to automate the bug localization and characterization process. The tools can capture the essence of both compile-time (compiler fault) and run-time (incorrect code generation) bugs. The compiler provides a rich set of command-line hooks to control the number, type and phase ordering of filters, a necessary feature for automated debugging.

In addition to bug characterization, MIRV provides over 700 regression tests and tools to incorporate larger source programs for stress testing. The regression framework has proven portable enough to validate the simulator software used in this work in addition to the compiler itself.

#### 1.1.2 Instruction Prefetching

Concerning instruction supply:

- Previous work in instruction prefetching is underspecified and ambiguous.

- Aggressive sequential instruction prefetching outperforms the previous software instruction prefetching work studied in this dissertation.

- Some previous work on table-based instruction prefetching outperforms simplistic sequential prefetchers, but at a much greater hardware cost.

- New software instruction prefetching schemes proposed in this work slightly outperform sequential prefetching on the benchmarks studied.

#### **Research Contributions**

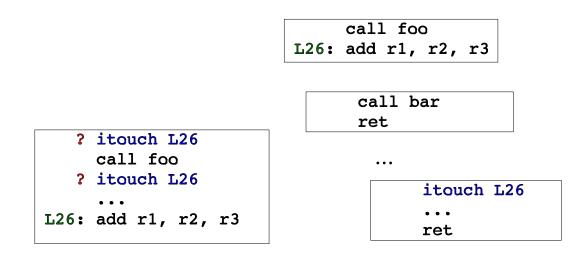

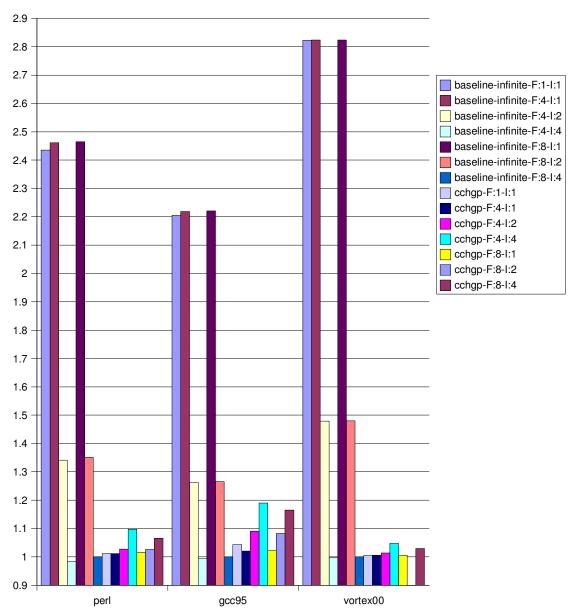

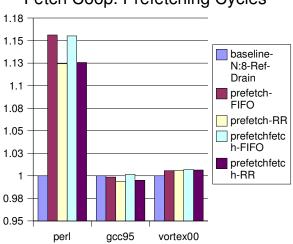

We study some existing instruction prefetching techniques and propose new techniques in chapter 6. During the course of this research we have discovered a number of deficiencies in the description of these techniques. Various points of ambiguity are identified and proposals made as to how to fill in the blanks. We have categorize these points of variance and explore the implied design space. Various combinations of these proposals are studied to determine the variants for which each technique performs best. We organize these points of variation into a *policy* framework that attempts to summarize how the instruction prefetchers studied operate. The studies of chapter 6 show that these points of variation can have a significant effect on the results observed.

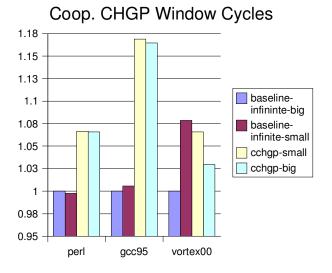

Our examination of software instruction prefetching algorithms identifies several points of commonality. We generalize existing algorithms and develop a *filter* interface to specify how prefetch instructions are scheduled. This framework is formalized into a tuple-based specification that summarizes the operation of specific software instruction prefetching algorithms. Two new software instruction prefetching techniques are proposed. *Compiler Hint Guided Prefetching* (CHGP) and *Cooperative Compiler Hint Guided Prefetching* (Cooperative CHGP) are shown to slightly outperform sequential prefetching on some architectures. The cooperative variant is found to be the better design.

#### 1.1.3 Register Allocation

Concerning data supply:

- Previous work on hardware support for speculative register promotion is implementable on modern microprocessor systems.

- Such implementations do not degrade previously observed potential performance gains of speculative register promotion.

- The previous work can be extended in a straightforward manner to handle register allocation of potentially aliased data items.

- Register allocation of potentially aliased data items can dramatically improve program performance, though the impact is highly program-dependent.

#### **Research Contributions**

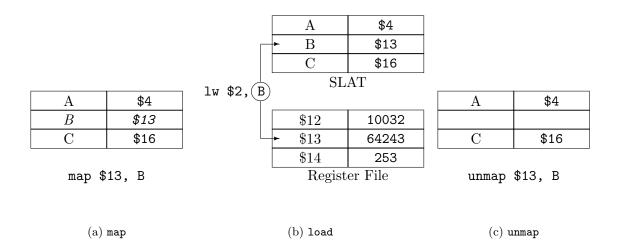

Chapters 7 and 8 present novel developments in register allocation. Chapter 7 explores previous work in speculative register promotion and verifies its implementability and utility on a modern microarchitecture. While the previous work mainly used an instruction counting argument to make its case, we verify the previously published results with cycle-accurate simulation. We discuss additional compiler considerations not covered by previous work, focusing on impacts on the analysis and transformation phases. We develop an Application Binary Interface (ABI) for the Store-Load Address Table (SLAT), the hardware mechanism used to support speculative register promotion.

In chapter 8 we develop extensions to the existing register renaming hardware to support speculative register promotion of potentially aliased data. Our extensions modify the processor register renaming hardware to allow register allocation of potentially aliased data. While only one benchmark benefits from this technique, the improvement is quite dramatic, leading us to conclude that the extensions may be applicable to other programs as well.

### **1.2** Benchmarks

In this section we state our assumptions about the benchmarks used throughout this dissertation. It is practically impossible to fully state all of the assumptions made. In our case we have attempted to state as fully as possible the design parameters used. Because stating the full set is difficult, our goal is to release all of the code used in these studies so that other researchers may benefit from it. This includes the MIRV compiler source, M5 simulator source and benchmark datasets if possible<sup>2</sup>.

Throughout this dissertation we use the SPEC 95 and 2000 benchmark suites in our studies. Most of our studies used the reduced data sets listed in table 1.1. The table includes information about the number of dynamic instructions executed and the instruction memory footprint for benchmarks used in the prefetching studies of chapter 6. We verified some of the data in chapter 6 against the larger SPEC test inputs to confirm that the smaller data sets did not impact the prefetching results observed. We note that some of the results (particularly those in chapters 7 and 8 are missing data for some of the benchmarks. These experiments did not complete in a timely fashion and thus were not available for inclusion.

$<sup>^{2}</sup>$ Licensing restrictions prevent us releasing the benchmarks themselves and some of the data set files.

We include the partial results to maintain consistency among the benchmark sets presented and to provide as much information as possible.

## 1.3 Simulation Environment

Throughout this dissertation we use the M5 simulation environment [3]. M5 is a cycleaccurate, event-driven simulator developed at the University of Michigan. In provides a detailed pipelined, out-of-order superscalar processor model that includes simulation of memory hierarchies with bus contention. M5 also includes device drivers to allow full system execution with operating system effects though our studies did not include this modeling due to the lack of an operating system for our experimental instruction set architecture. Simulation model parameters are included in the chapters relevant to each study performed.

| Benchmark | Suite     | Arguments                                                                                                                                                                                                                                             | Dataset     | Insn. | Size   |

|-----------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|--------|

| compress  | SPEC 95   |                                                                                                                                                                                                                                                       |             |       |        |

|           |           | -quiet -funroll-loops<br>-fforce-mem<br>-fcse-follow-jumps<br>-fcse-skip-blocks                                                                                                                                                                       | regclass.i  |       |        |

| gcc       | SPEC 95   | -fexpensive-optimizations<br>-fstrength-reduce -fpeephole<br>-fschedule-insns<br>-finline-functions<br>-fschedule-insns2 -0                                                                                                                           | from test   | 141 M | 654 KB |

| go        | SPEC 95   | 9 9 null.in                                                                                                                                                                                                                                           | ref input   |       |        |

| ijpeg     | SPEC 95   | <pre>-image_file specmun.ppm<br/>-compression.quality 25<br/>-compression.optimize_coding 0<br/>-compression.smoothing_factor 90<br/>-difference.image 1<br/>-difference.x_stride 10<br/>-difference.y_stride 10<br/>-verbose 1 -GO.findoptcomp</pre> | test input  |       |        |

| li        | SPEC 95   | boyerExit.lsp                                                                                                                                                                                                                                         |             |       |        |

| m88ksim   | SPEC 95   | -c < ctl.lit                                                                                                                                                                                                                                          | train input |       |        |

| perl      | SPEC 95   | < jumble.in                                                                                                                                                                                                                                           | jumble.pl   | 115 M | 107 KB |

| vortex    | SPEC 95   | vortex.lit                                                                                                                                                                                                                                            | 5 1         |       |        |

| ammp      | SPEC 2000 | < bughunt.in                                                                                                                                                                                                                                          |             |       |        |

| art       | SPEC 2000 | -scanfile c756hel.in<br>-trainfile1 a10.img -stride 2<br>-startx 134 -starty 220<br>-endx 139 -endy 225 -objects 1                                                                                                                                    | test input  |       |        |

| bzip2     | SPEC 2000 | input.random 1                                                                                                                                                                                                                                        | test input  |       |        |

| gcc       | SPEC 2000 | bughunt.i -o gcc00.s.log                                                                                                                                                                                                                              |             |       |        |

| gzip      | SPEC 2000 | input.compressed 1                                                                                                                                                                                                                                    | test input  |       |        |

| mcf       | SPEC 2000 | inp.in                                                                                                                                                                                                                                                | test input  |       |        |

| mesa      | SPEC 2000 | -frames 1 -meshfile mesa.in<br>-ppmfile mesa.ppm                                                                                                                                                                                                      | test input  |       |        |

| parser    | SPEC 2000 | 2.1.dict -batch                                                                                                                                                                                                                                       | test input  |       |        |

| equake    | SPEC 2000 | < inp.in                                                                                                                                                                                                                                              | test input  |       |        |

| vortex    | SPEC 2000 | lendian.raw                                                                                                                                                                                                                                           | reduced     | 169 M | 303 KB |

Table 1.1: SPEC Reduced Datasets

# CHAPTER 2

# The MIRV C/C++ Experimental Research Compiler

### 2.1 Introduction

This chapter describes the MIRV C/C++ research compiler. Postiff's dissertation describes the compiler back-end in detail [4]. Therefore, we concentrate on the front-end design. We begin with an overview of the MIRV compilation model in section 2.2. Section 2.3 presents the MIRV language and intermediate format used by the front-end analysis and transformation passes. We describe not only the syntax and semantics but also the internal representation as seen by the programmer in section 2.4. Section 2.5 provides a brief overview of the back-end and low-level code generation process. Special language support required for C and C++ is surveyed in section 2.6 while section 2.7 mentions some other compiler frameworks described in the literature.

Where appropriate, each section presents not only the MIRV design as it currently exists, but also suggestions for future improvements. As with any large software projects, lessons are learned along the way. MIRV is no exception and whether due to programming environment or design limitations, the compiler framework can certainly be improved in several areas. MIRV is an experimental research compiler that we have developed over several years. It compiles programs written in both C and C++ and provides full automatic template instantiation and integration with popular simulation environments such as SimpleScalar [5] and M5 [3]. Back-end targets exist for SimpleScalar/PISA (a MIPS derivative ISA), Intel IA32, ARM and some experimental research instruction set architectures.

### 2.2 Compilation Model

In this section we present the compilation model used in MIRV. The compilation model describes the internal representation of source programs in the compiler and the sequence of actions needed to transform the source into another language (in this case, MIRV and low-level assembly code). The compilation model also presents the Application Programmer Interface (API) available to the compiler designer. The API specifies how one might go about integrating new source language front-ends, analyses and transformations into the compiler. This section concentrates on a broad overview of the "MIRV process." Later sections present in-depth descriptions and API specifications for programming the compiler front-end.

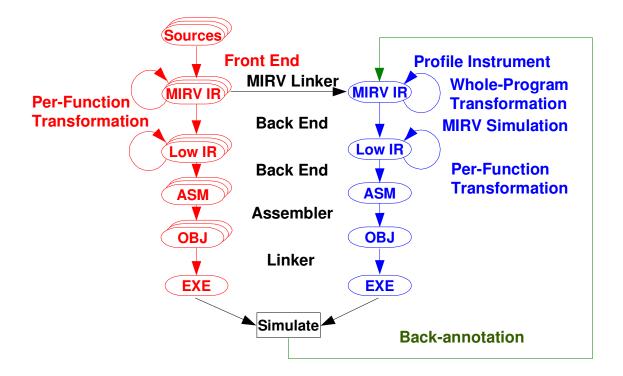

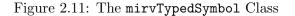

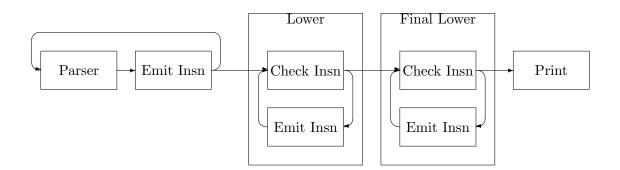

Figure 2.1 presents an overview of the compilation process. The left side presents the traditional mechanism as implemented in MIRV. Multiple source files are compiled individually by the front-end. Each file is translated to a high-level *intermediate representation* (IR) and processed by *filters* in turn. After the front-end processes each file, the back-end is invoked to perform low-level transformations and generate assembly code. The assembler is invoked to create an object module. All object modules are then linked together to produce an executable.

The right side of the figure shows some non-traditional mechanisms available in MIRV.

Figure 2.1: MIRV Compilation Flow

The high-level intermediate representation can be linked together to create one high-level representation of the entire source program. This allows whole-program analysis and transformation. This representation facilitates inter-procedural analysis and optimizations such as call graph construction and function in-lining. In addition, profile information from a previous run of the program can be automatically back-annotated into the representation<sup>1</sup>.

Whole-program analysis has been an active area of research for some time. Many of these studies were performed on object code after program linking [6]. By allowing program linking using the high-level intermediate representation, MIRV provides a consistent environment for performing both intra- and inter-procedural analysis and optimization. We refer to this process as *source-level linking* even though technically the linking occurs within the intermediate representation<sup>2</sup>. This linking process also provides several advantages dur-

$<sup>^{1}</sup>$ Instrumentation of the program need not require a MIRV-linked program. Such a representation is not needed for back-annotation either, though that is the procedure used in our current profiling filters.

$<sup>^{2}</sup>Linking$  in this case refers to the process of resolving external symbol references to the symbol objects

Figure 2.2: MIRV Compilation Model

ing the debug process due to the consistent interface (the MIRV IR file) available to the debugging tools.

#### **Operation Within a Translation Unit**

A translation unit within the context of MIRV is defined as a single file to which translation and transformations are applied. This can be a single high-level C or C++ source file, a pre-translated MIRV IR file or a whole program if source-level linking has been applied.

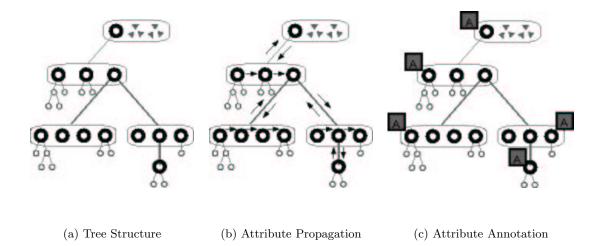

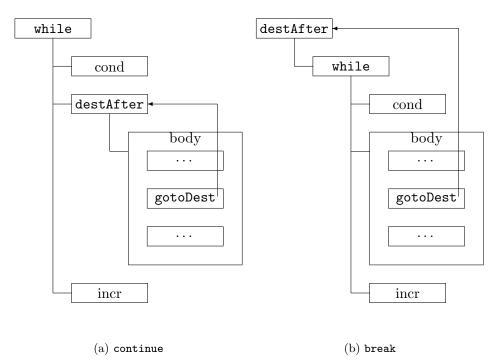

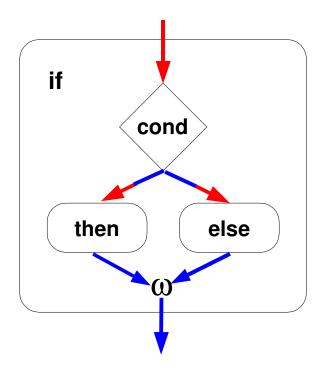

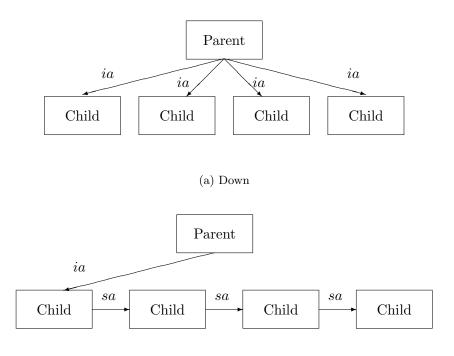

At the translation unit level, the compiler consists of a set of filters that operate on the intermediate representation of the program. The intermediate representation is an operator tree representing the MIRV language where every node may contain a set of user- and compiler-defined attributes. The attributes are usually computed and used by the filters that are invoked on the tree. Successive passes of filters communicate using these node attributes. Figure 2.2 illustrates the pieces in the compilation process. The generic tree structure of MIRV is shown in figure 2.2(a). There are two main groups of attributes: *parse* stored within the MIRV compiler. As the high-level form has no concept of a branch *per se*, label patching

stored within the MIRV compiler. As the high-level form has no concept of a branch *per se*, label patching need not be performed.

attributes and node attributes. Parse attributes are the synthesized attributes and inherited attributes that are passed up and down a parse tree during traversal as shown in figure 2.2(b) [7]. Node attributes are pieces of information that are associated with nodes in the operator tree. Figure 2.2(c) shows an annotated MIRV tree. Note that annotations can appear anywhere on the tree, not just at the leaves.

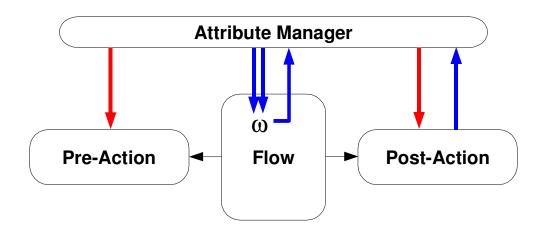

#### 2.2.1 Filters

Filters are categorized according to their purpose into three groups. Analysis filters traverse the tree in some order and perform computation using parse attributes that are propagated during tree traversal. The results of this computation are represented as node attributes on the operator tree. Transformation filters change the structure of the tree by adding and removing nodes. How a transformation filter changes the tree structure is usually determined by the node attributes computed by analysis filters. Snapshot filters neither set node attributes, nor do they alter the structure of the existing tree; they simply traverse the tree and invoke methods on external objects based on the operators and node attributes in the tree. Examples of snapshot filters include the linearizing or "pickling" filter used to print the intermediate form to a file and the high-level MIRV IR simulator [8]. By coordinating the order in which these three types of filters are run, a program can be optimized and translated to a target machine. The level of optimization can be varied by adding and removing filters and changing the order in which filters are run. Filters declare dependencies on various analyses through the attribute system. Therefore, the user need not be concerned about such dependencies when reordering analysis and transformation filters. All filters can be invoked directly from the compiler command-line, another key feature that improves the utility of the tools we discuss below.

#### 2.2.2 Attributes and the Compilation Process

Dependencies between filters exist as the dependence of a filter on a set of node attributes. In other words, a filter does not explicitly specify what other filters must precede its execution but rather states the names of the node attributes it is dependent upon. One use of such dependencies in the compiler is the caching of analysis attributes. Because filters declare which attributes are modified by a program analysis or transformation and which attributes are needed as input to a filter, the compiler can know when to re-invoke a full analysis pass for a transformation filter. Currently, any transformation which alters the program structures is assumed to invalidate all dataflow attributes, though special interfaces exist to allow the filter designer to bypass some of these assumptions for trivial transformations (expression reassociation, for example) <sup>3</sup>

Attributes are internally represented in one of five forms. The simplest is the boolean attribute, represented with the C++ bool type. The int type is used to represent integer attributes. Similarly, double attributes are represented by the double type. A C++ std::string represents string attributes. Finally, a mirvNodeAttribute abstract base class is provided to allow filter designers to create their own types of attributes. Only the first four attributes are directly supported by the MIRV language as representing attributes derived from mirvNodeAttribute would require an extensible parser to read in a MIRV IR

file.

$<sup>^{3}</sup>$ Currently such dependencies are expressed with an explicit query into the attribute database to see which attributes have been invalidated. A more automatic approach to this problem is an area of future work.

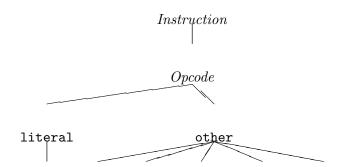

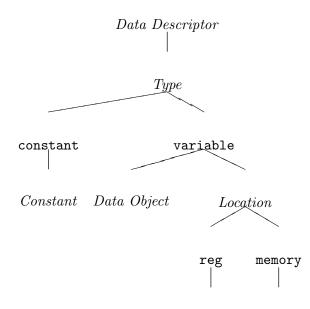

### 2.3 Intermediate Representation Language

In any compiler, the program representation format has a great impact on the analysis and transformation approaches used. For example, iterative dataflow analysis usually implies a low-level basic-block pseudoinstruction representation, while structural dataflow analysis requires high-level information about the control structure of the program [9, 10, 11]. In addition, there is a tension between the desire to know as much information about the program and the desire to expose as much of the computation abstracted by the high-level language as possible to allow effective optimization.

The MIRV compiler front-end uses a tree representation of the MIRV language. The MIRV language is intended to be a generic high-level intermediate language that can be targeted by many different high-level source languages, in the spirit of compilers that use a common analysis format for several high-level languages [12]. The tree is in prefix form, which aids the syntax-directed translation scheme used in the back-end low-level intermediate representation generator by providing proper context to the parser about what is to be expected next in the input stream.

The language itself is quite similar to a sanitized version of the C language, other than its prefix form. Operators exist not only for expression trees, but also loops, switch statements, if-else constructs and so forth. The key difference between this representation and the representation used by most compilers is that the high-level control structure of the program is preserved. While most compilers must build a control graph from a basic block representation to perform some types of analysis, the control structure is implied by the structure of the MIRV language. This structure is available right up to low-level intermediate code generation time, allowing transformations such as loop unrolling and strength reduction with test replacement without the need to re-synthesize important information. Some transformations need to see a large context which is lost during low-level instruction quad generation. Expression reassociation, for example, loses much of its power if the expressions are broken into the two-source, one-destination format typical of low-level quad representations. Other transformations like loop-invariant code motion can make larger motions in a single pass if such context is preserved.

#### Expressions

In MIRV, an *expression* is a computation that does not modify program state. It simply uses available data to perform some arithmetic or reference other data. In particular, unlike in the C language, function calls and assignments are not expressions because they (potentially) modify program state through side-effects.

| Type of Operation  | MIRV Structure        | Description                        |

|--------------------|-----------------------|------------------------------------|

| Direct Reference   | op data               | op := vref, cref or fref           |

|                    | aref data index-list  | Array reference                    |

|                    | vfref aggregate field | Field reference                    |

| Indirect Reference | airef expr index-list | Indirect array reference           |

|                    | vfiref expr field     | Indirect field reference           |

| Address            | addrOf <i>expr</i>    | Take the address                   |

| Size               | sizeOf type           | The size in bytes of <i>type</i>   |

| Arithmetic         | op expr expr          | op := add, sub, mul, div, mod,     |

|                    |                       | pow or sqrt                        |

|                    | neg expr              | Negation                           |

| Bitwise            | op expr expr          | op := and, or, xor, shl, shr, rol, |

|                    |                       | ror or xor                         |

|                    | cpl expr              | Complement                         |

| Boolean            | op expr expr          | op := cand, cor, lt, le, eq, ne,   |

|                    |                       | ge or gt                           |

|                    | not expr              |                                    |

| Casting            | cast type expr        | Cast <i>expr</i> to <i>type</i>    |

| Literal            | lit text              |                                    |

|                    | ulit text expr        | text := printf-style format string |

|                    | blit text expr expr   |                                    |

Table 2.1: MIRV Expressions

Table 2.1 presents the expression operators in the MIRV language. The arithmetic operators are fairly standard. The pow and sqrt operators were included to support ma-

chines with instructions to perform these operations. This was somewhat arbitrary, as one could make a case for including operators such as sin and cos. However, because the C language encapsulates pow, sqrt, sin, cos and many other complex operations in math library functions, these operators are not used in practice<sup>4</sup>.

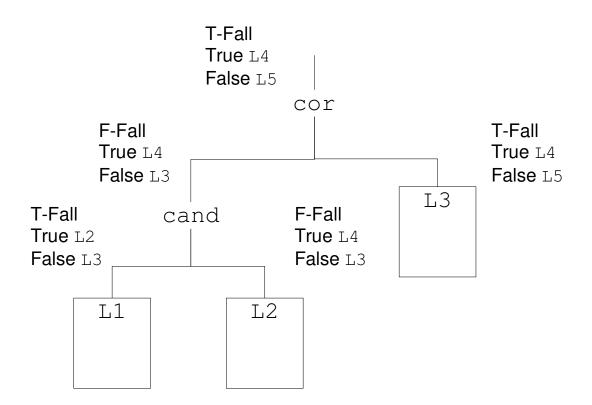

The logical cand and cor operators are analogous to the C && and || operators with one significant difference: they do not short-circuit for the purposes of dataflow analysis. This property allows the compiler to separate program control flow from logical evaluation, simplifying the dataflow model. To preserve the C semantics, the compiler front-end translates the short-circuiting operations to equivalent control flow constructs. In the case where it can prove that side-effects to not exist, the cand and cor operators are used directly, avoiding unnecessary branches. The current back-end does preserve the C semantics in these cases even though correctness does not require it. This provides a significant savings in dynamic instruction count.

The casting operation is used only to maintain type consistency throughout the program. Where C semantics require an implicit cast, the MIRV front-end inserts an explicit cast. This simplifies the code generator by removing the burden of type comparison and cast insertion.

There are six operators to reference various types of data. A vref includes an operand specifying a specific variable in the MIRV program. Variable names are globally unique. An aref works exactly like the C subscript operator. Arguments are an array identifier and index expressions. An airef is an array index off a pointer variable (i.e. pointer arithmetic). A vfref references a field from an aggregate type while a vfiref references a field from a pointer to an aggregate (like C's > operator).

<sup>&</sup>lt;sup>4</sup>The back-end is able to transform some of these function calls into machine instruction sequences.