# Efficient Data Center Architectures Using Non-Volatile Memory and Reliability Techniques

by

David Andrew Roberts

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 2011

Doctoral Committee:

Professor Trevor N. Mudge, Chair Professor David Blaauw Professor Dennis Sylvester Associate Professor Scott Mahlke © <u>David Andrew Roberts</u> 2011 All Rights Reserved

### ACKNOWLEDGEMENTS

I'd first like to thank my research advisor, Trevor Mudge, for his continued support and sharing of his expertise while being flexible enough to let me explore alternative research directions that I found interesting. My committee members David Blaauw, Scott Mahlke and Dennis Sylvester have also had a major influence on the ideas that shaped my thesis. Profs Todd Austin, Mark Brehob and Thomas Wenisch provided valuable advice and collaboration on several of my research papers.

The learning experiences enabled by my managers and colleagues during internships at HP Labs and ARM Ltd. were very rewarding. I'd especially like to thank Parthasarathy Ranganathan, Jichuan Chang and Mehul Shah at HP whom I collaborated with on the "Nanostores" project during the summer of 2009. Partha, Jichuan and I developed the evaluation methodology and system design for this energy-efficient data center architecture. During the initial brainstorming sessions, Mehul provided us with valuable insights on large-sale workloads and the types of system architectures currently used to solve these data-oriented problems. All three contributed significant effort in enhancing and editing our conference paper submissions, for which I am very grateful. Access to their computer resources during my time as a visiting researcher allowed me to continue to perform simulations and run-time measurements using a large number of networked servers.

At ARM I had the pleasure of working with David Bull, Krisztian Flautner, David Flynn and Dipesh Patel on several energy-related projects. Prior to starting my Ph.D studies, they exposed me to CPU energy efficiency concerns and dynamic voltage scaling (DVS), controlled by their Intelligent Energy Manager (IEM) software. I worked on the first implementation of IEM based on Krisztian's thesis work, then went on to explore Razor timing-fault tolerance and fault-tolerant "Block Grouping" caches under their funding while at Michigan.

My fellow graduate students provided inspiration and entertaining discussions, and I'd like to thank Geoff Blake, Shidhartha Das, Ron Dreslinski, Dave Fick, Taeho Kgil, Seokwoo Lee, Yuan Lin, Dave Meisner, Sujay Phadke, Sangwon Seo, Korey Sewell, Denny Vandenberg, Ilya Wagner, Mark Woh and Bo Zhai, among others. I owe much of my success to my girlfriend Dan Chang and the rest of my family for their support and encouragement over the years. I'd also like to thank my friends for giving me the chance to step back from the focus of study and have some fun. Thanks to Bill and Kim Battle, Mike Morelli, Dan O'Karma, Gary Wallen and the rest of the Ann Arbor chapter of the Ride Motorcycle club. And also thanks to musicians Kevin Kapalla, Mumtaz Karatas, Roy Schmidt and Greg Scott for many enjoyable jam sessions, performances, guitar lessons etc. Elson Liu and Adam Zettel, you were great roommates.

# TABLE OF CONTENTS

| ACKNOWLE    | DGEMENTS                                                                                                  |

|-------------|-----------------------------------------------------------------------------------------------------------|

| LIST OF FIG | URES                                                                                                      |

| LIST OF TAI | 3LES                                                                                                      |

|             |                                                                                                           |

| ABSTRACT    | · · · · · · · · · · · · · · · · · · ·                                                                     |

| CHAPTER     |                                                                                                           |

| I. Introd   | luction                                                                                                   |

| 1.1         | Data Center Trends                                                                                        |

| 1.1         | 1.1.1 Energy-efficient Data Center Architectures                                                          |

|             | 1.1.1       Energy-encient Data Center Architectures         1.1.2       Workloads and Datasets           |

| 1.2         | Technology Trends                                                                                         |

| 1.2         | 1.2.1 Storage Technology and I/O interfaces                                                               |

|             | 1.2.1       Storage recimology and 1/O interfaces         1.2.2       Networking and Communication        |

|             | 1.2.2       Networking and Communication       1         1.2.3       Emerging memory technologies       1 |

| 1.3         | Challenges                                                                                                |

| 1.5         | 1.3.1 Overcoming the inefficiencies of existing storage devices 1                                         |

|             | 1.3.1 Overcoming the menciencies of existing storage devices                                              |

|             | 0 1                                                                                                       |

|             | 1.3.3 Modelling and optimization at data-center scale                                                     |

|             | 1.3.4 Overcoming non-volatile memory endurance limitations 1                                              |

| 1 4         | 1.3.5 Breaking CPU voltage-scaling limits                                                                 |

| 1.4         |                                                                                                           |

|             | 1.4.1 Re-architecting the storage hierarchy with Nanostores 1                                             |

|             | 1.4.2 Extending wear-leveling to distributed storage                                                      |

| 1 5         | 1.4.3 Overcoming the limits of CPU voltage scaling $\ldots \ldots \ldots \ldots 1$                        |

| 1.5         | Thesis Structure                                                                                          |

| II. Backg   | round and Related Work                                                                                    |

| 2.1         | Efficient Data Center Architectures                                                                       |

| 2.2         | Emerging Technologies                                                                                     |

|             | 2.2.1 Memory technology scaling trends and limitations                                                    |

|             | 2.2.2 Non-Volatile Memories                                                                               |

|             | 2.2.3 3D die stacking                                                                                     |

| 2.3         | Memory Reliability                                                                                        |

|             | 2.3.1 Non-Volatile Memory Wear-Leveling in Data Centers                                                   |

|             | 2.3.2 Cache Memory Fault Tolerance                                                                        |

|             |                                                                                                           |

| III Nama    | stores: Co-located Compute-Storage NVRAM-based Architecture                                               |

|             |                                                                                                           |

| 101° Da     | ata-Centric Workloads                                                                                     |

| 3.1        | Introduction                                                                                                                                             |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.2        | Architecture: Nanostores                                                                                                                                 |

|            | 3.2.1 Motivation                                                                                                                                         |

|            | 3.2.2 Proposed architecture                                                                                                                              |

| 3.3        | Evaluation Methodology                                                                                                                                   |

|            | 3.3.1 Challenges                                                                                                                                         |

|            | 3.3.2 Proposed benchmarks                                                                                                                                |

|            | 3.3.3 Proposed evaluation methodology                                                                                                                    |

|            | 3.3.4 Choice of parameters and baselines                                                                                                                 |

| 3.4        | Evaluation Results       60                                                                                                                              |

| 0.4        | $3.4.1$ Baseline benefits $\ldots$ $60$                                                                                                                  |

|            | 3.4.2 Analysis of performance benefits                                                                                                                   |

|            | 3.4.3 Analysis of performance benefits                                                                                                                   |

|            |                                                                                                                                                          |

|            |                                                                                                                                                          |

|            | 3.4.5 Other objective functions                                                                                                                          |

|            | 3.4.6 Impact of relaxed power density and network constraints 69                                                                                         |

|            | 3.4.7 Model Validation                                                                                                                                   |

|            | 3.4.8 Discussion                                                                                                                                         |

| 3.5        | Conclusions                                                                                                                                              |

| 4.1        | Volatile Memory Reliability for Data Center and Server Applications 81         Wear-out mitigation techniques       81                                   |

| 4.2        | Estimating storage device wear-out in the Nanostore architecture 82                                                                                      |

| 4.3        | Distributed Wear Leveling                                                                                                                                |

| 1.0        | 4.3.1 Introduction                                                                                                                                       |

|            | 4.3.2 Background and Motivation                                                                                                                          |

|            | 4.3.3 Experimental Methodology                                                                                                                           |

|            | 4.3.4 Distributed Wear Leveling                                                                                                                          |

|            | 4.3.5 Results                                                                                                                                            |

|            | 4.3.6 Conclusion                                                                                                                                         |

| 4.4        | NAND Flash based Disk Cache Reliability                                                                                                                  |

|            |                                                                                                                                                          |

|            | Chip Cache Memory Reliability for Energy Reduction                                                                                                       |

| 5.1        | Introduction                                                                                                                                             |

| 5.2        | Background                                                                                                                                               |

| 5.3        | Impact of on-chip cache failure rate on processor performance                                                                                            |

|            | 5.3.1 On-chip cache device scaling and failure rate                                                                                                      |

|            | 5.3.2 Performance impact of set-associative cache defects                                                                                                |

| 5.4        | Comparison of fault-tolerance techniques                                                                                                                 |

|            | 5.4.1 Existing fault-tolerance schemes                                                                                                                   |

|            | 5.4.2 Proposed fault-tolerance scheme                                                                                                                    |

| 5.5        | Results                                                                                                                                                  |

|            | 5.5.1 Performance and area under voltage scaling                                                                                                         |

|            | 5.5.2 Performance under cell scaling                                                                                                                     |

|            | 5.5.3 Energy saving using block grouping at low voltage                                                                                                  |

| 5.6        | Conclusions                                                                                                                                              |

| 5.0        |                                                                                                                                                          |

| VI. Conc   | lusions and Future Work                                                                                                                                  |

| PPENDICI   | $\mathbb{E}\mathbf{S} \ldots 141$ |

| - <b>D</b> |                                                                                                                                                          |

| BIBLIOGRAPHY | <br> | <br> |  |  |  |  |  |  |  |  |  |  |  | <br>- | 147 |

|--------------|------|------|--|--|--|--|--|--|--|--|--|--|--|-------|-----|

|              |      |      |  |  |  |  |  |  |  |  |  |  |  |       |     |

# LIST OF FIGURES

# Figure

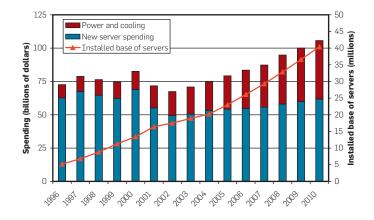

| 1.1  | IDC survey indicates increasing cost of power and cooling $[1, 2]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

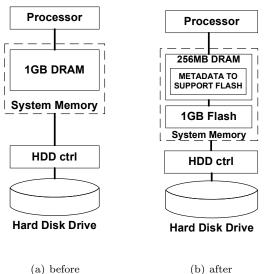

| 1.2  | Comparison of flash usage models in a server [2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7  |

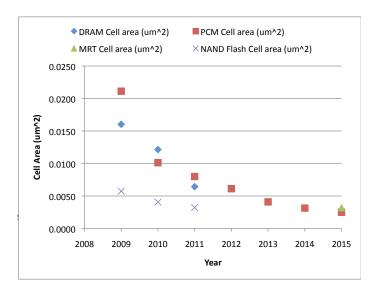

| 2.1  | Predicted cell areas of different memory technologies [3] (DRAM and Flash from ORTC-2A, Phase-Change memory (PCM) from Focus C, PIDS5). Note that DRAM and NAND Flash do not have known manufacturable solutions for scaling beyond 2011 timeframe. For Memristors (MRT) we assume a feature size similar to NAND Flash projections, and cell area factor $A=10f^2$ , based on direct discussions with HP. We do not show MRT predictions prior to the target year of our study (2015) due to the current experimental nature of the technology. | 21 |

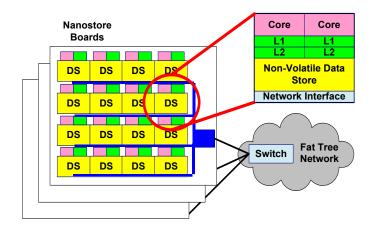

| 3.1  | Nanostore system architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 38 |

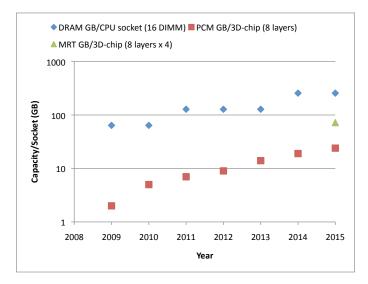

| 3.2  | Per-node capacities derived from ITRS roadmap 2009 [3]. Note that we use design points at the 2015 timeframe in our models. DRAM capacity represents 16 off-chip DIMMs consisting of 16 DRAM chips each. The 3D-stacked PCM and MRT consist of 8 stacked die, while the MRT also has 4 internal layers on each die                                                                                                                                                                                                                               | 39 |

| 3.3  | A data-centric workload taxonomy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 44 |

| 3.4  | Workload mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 45 |

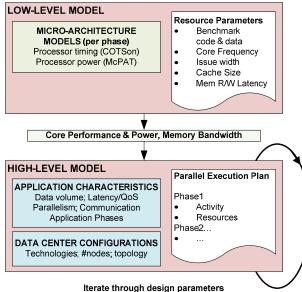

| 3.5  | Two-level simulation with design optimizer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 48 |

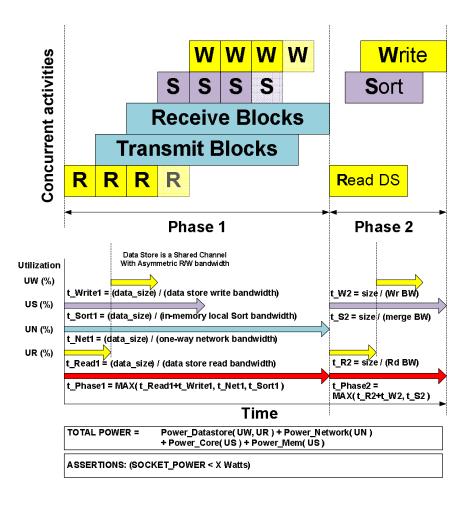

| 3.6  | Sort: Separate Data Store and Main Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 49 |

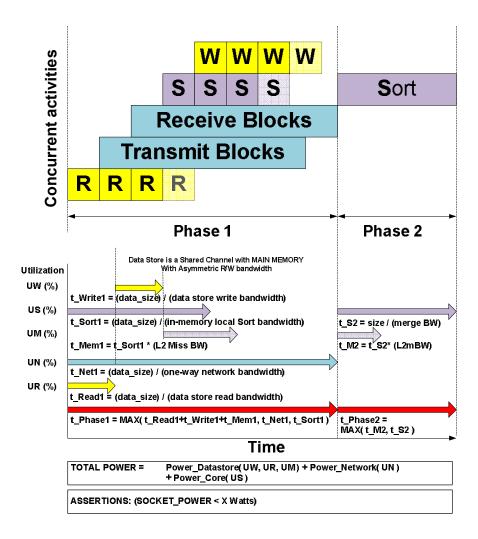

| 3.7  | Sort: Unified Data Store and Main Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 50 |

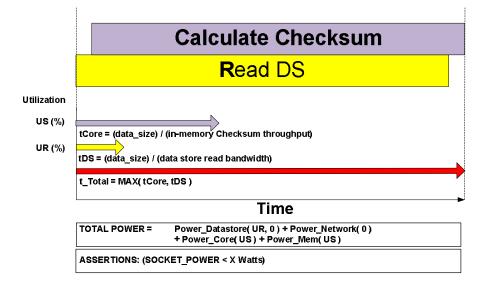

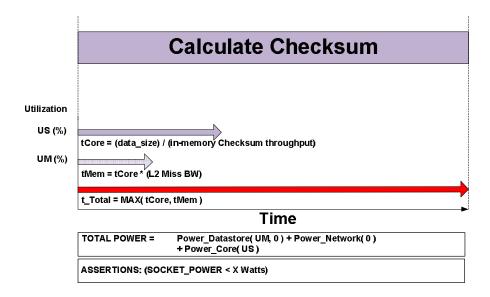

| 3.8  | cksum: Separate Data Store and Main Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 53 |

| 3.9  | cksum: Unified Data Store and Main Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 54 |

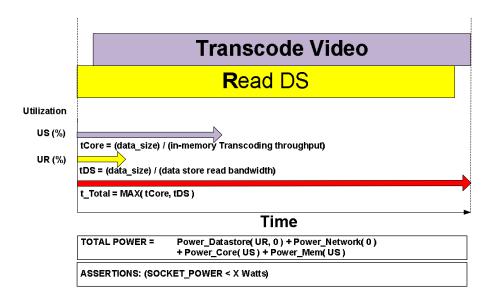

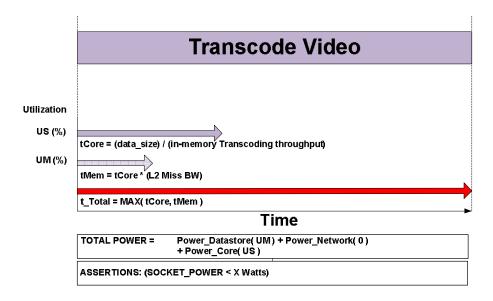

| 3.10 | video: Separate Data Store and Main Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 55 |

| 3.11 | video: Unified Data Store and Main Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 56 |

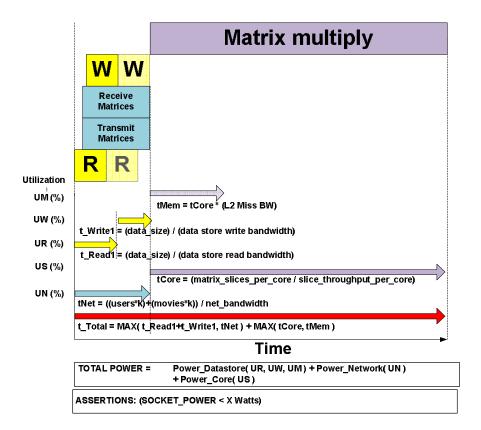

| 3.12 | Recommender                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 57 |

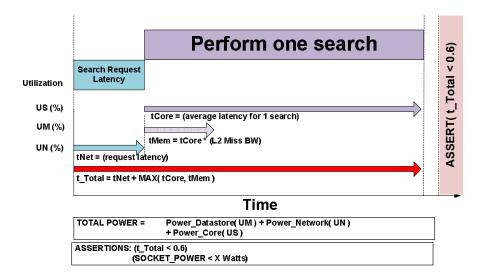

| 3.13 | Search                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 58 |

| 3.14 | System parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 59 |

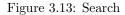

| 3.15 | Baseline architectures                                                                                                                                                                                                                                                                                                       | 59 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

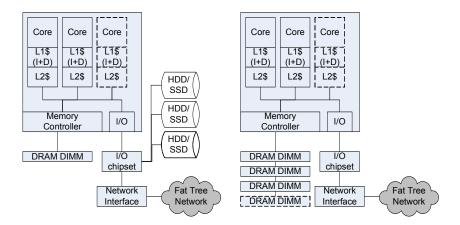

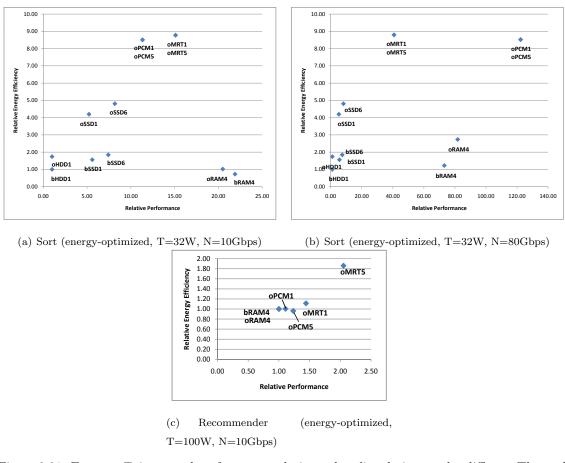

| 3.16 | Performance and energy efficiency improvements relative to 2015 baselines (EDP-<br>optimized).                                                                                                                                                                                                                               | 60 |

| 3.17 | Configurations and scale multipliers of the baseline and SSD/DRAM/nanostore designs. ScaleX refers to the system-level scale factors relative to the baselines, as follows: Node (networked node count) OPS (peak compute throughput (Operations/second)) DS (Data store bandwidth) Net (Network bandwidth)                  | 62 |

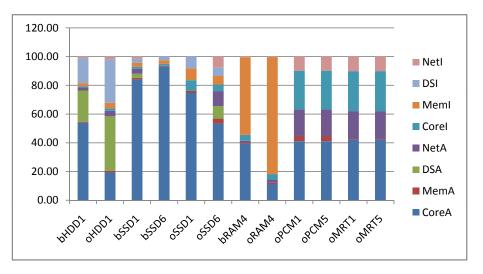

| 3.18 | Power breakdown (% of total) for sort hardware configurations (energy-optimized).<br>Net, DS, Mem and Core refer to network, data store, main memory and core power,<br>respectively. A suffix of I refers to Idle (background) power, and A refers to Active<br>power.                                                      | 66 |

| 3.19 | Impact of the optimizers objective function                                                                                                                                                                                                                                                                                  | 69 |

| 3.20 | Impact of thermal/network constraints                                                                                                                                                                                                                                                                                        | 69 |

| 3.21 | Energy-efficiency and performance relative to baseline designs under different Ther-<br>mal and Network bandwidth limits.                                                                                                                                                                                                    | 72 |

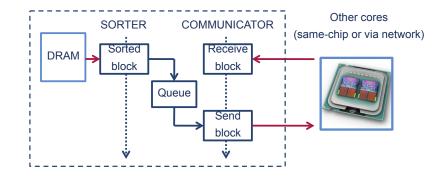

| 3.22 | Block diagram of MPI-based shuffle phase software used in model validation                                                                                                                                                                                                                                                   | 73 |

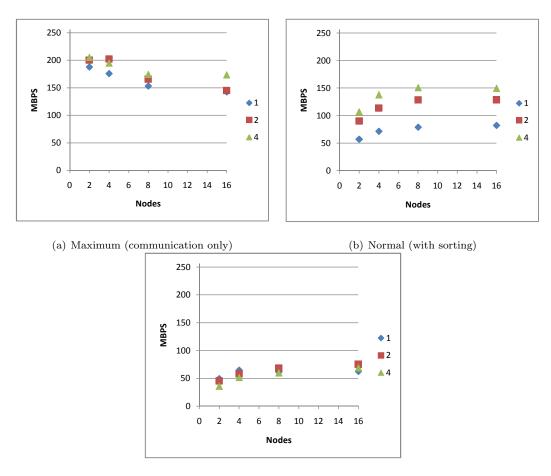

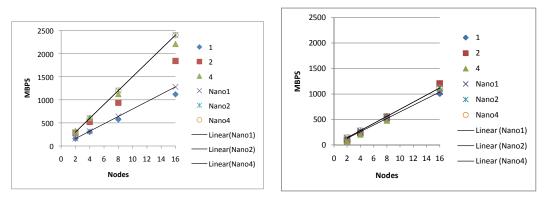

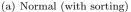

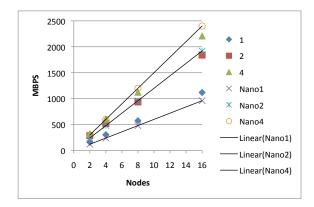

| 3.23 | Per-node network bandwidths. The three points in the legend represent the number of cores per networked node                                                                                                                                                                                                                 | 76 |

| 3.24 | Aggregate data sorting bandwidths. The first three legend items represent measured results for different numbers of cores. The points labelled NanoX represent the theoretical Nanostore performance model for each core count (modelled assuming 80 MB/s local sorting throughput), and their best-fit lines are also shown | 77 |

| 3.25 | Aggregate data sorting bandwidths (Nanostore models assume 60 MB/s local sort-<br>ing throughput).                                                                                                                                                                                                                           | 77 |

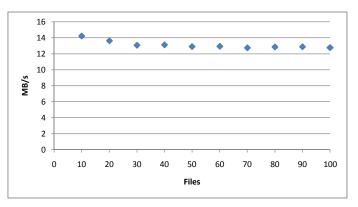

| 3.26 | Measured nsort merge throughput                                                                                                                                                                                                                                                                                              | 78 |

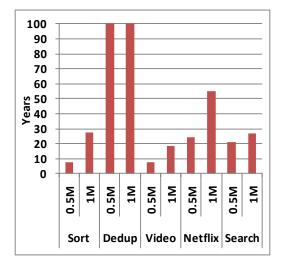

| 4.1  | Estimated lifetime in years for PCRAM based system. Cache sizes in MB are shown below each column                                                                                                                                                                                                                            | 82 |

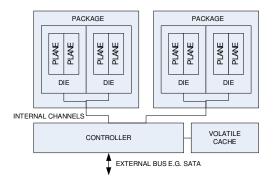

| 4.2  | NAND Flash plane                                                                                                                                                                                                                                                                                                             | 86 |

| 4.3  | NAND Flash SSD                                                                                                                                                                                                                                                                                                               | 86 |

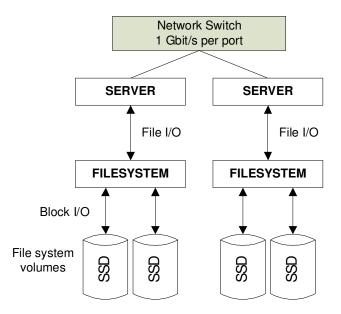

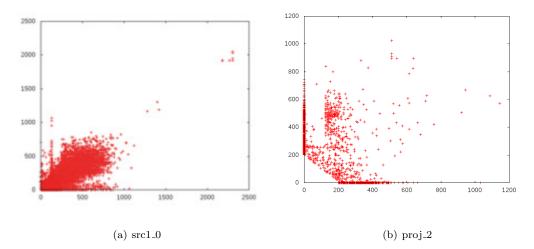

| 4.4  | High-Level System Configuration, This figure shows the physical organization of the baseline system. All 13 servers are connected via a Gigabit Ethernet switch, supporting 1 Gbit/s (128 MB/s) of bandwidth for each one. Every volume is replaced with a 1 TB SSD drive.                                                   | 88 |

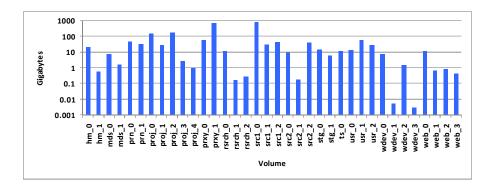

| 4.5  | Total data written (GB) per volume over the 7-day tracing period $\ldots \ldots \ldots$                                                                                                                                                                                                                                      | 90 |

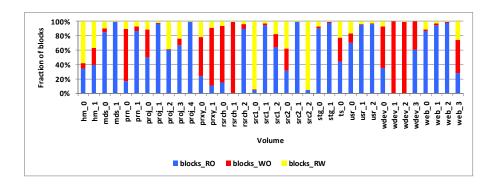

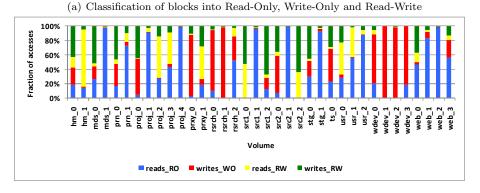

| 4.6  | Block and access classification. Data are for 7-day traces.                                                                                                                                                                                                                                                                  | 91 |

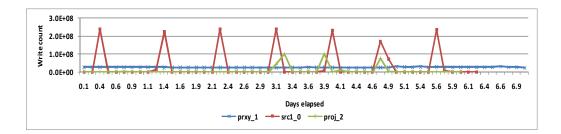

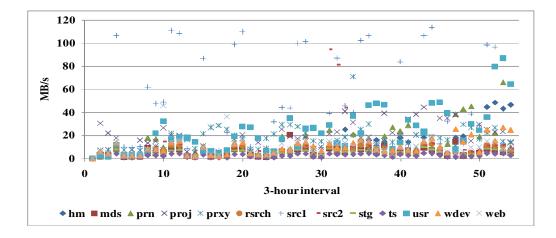

| 4.7  | Time behavior of writes. Each data point is recorded for a 3-hour interval 92                                                                                                                                                                                             |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

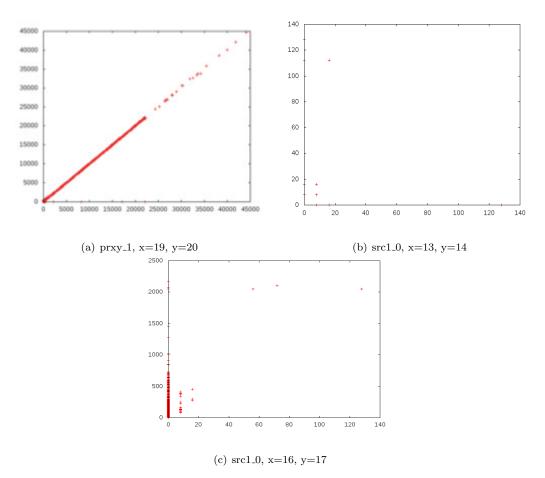

| 4.8  | Correlation between time intervals. Outlier block 48128 has been removed. Each point represents a 64KB block accessed in either (or both) of successive 3-hour intervals. The x-axis represents write count to the block during the first, and y-axis the second interval |

| 4.9  | Correlation between the earliest write bursts. Note that for proj_2, blocks with low write counts were omitted for faster plotting                                                                                                                                        |

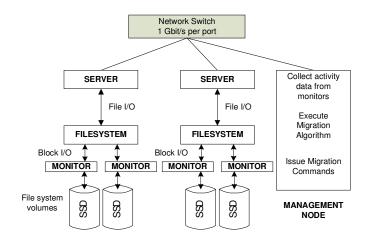

| 4.10 | Top-level diagram    97                                                                                                                                                                                                                                                   |

| 4.11 | Distributed wear leveling algorithms                                                                                                                                                                                                                                      |

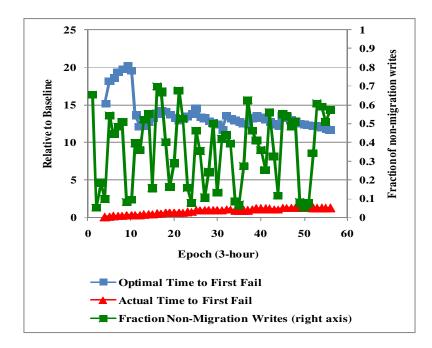

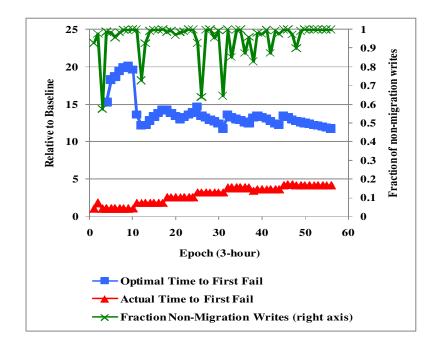

| 4.12 | (RS+POOL) run-time wear-leveling policy. The x-axis represents elapsed time in 3-hour intervals. The y-axis shows improvement over baseline                                                                                                                               |

| 4.13 | (LFPS+POOL) run-time wear-leveling policy. The x-axis represents elapsed time<br>in 3-hour intervals. The y-axis shows improvement over baseline                                                                                                                          |

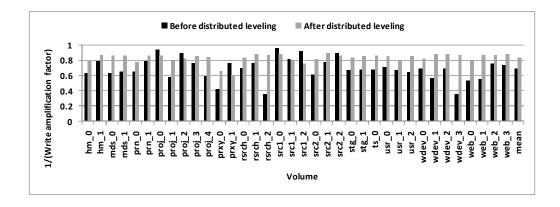

| 4.14 | Local SSD wear-leveling write efficiency                                                                                                                                                                                                                                  |

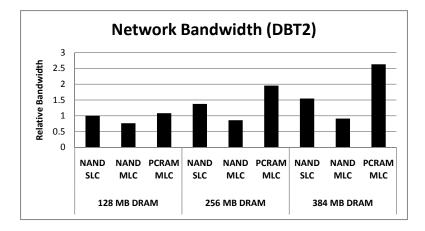

| 4.15 | Peak network bandwidth                                                                                                                                                                                                                                                    |

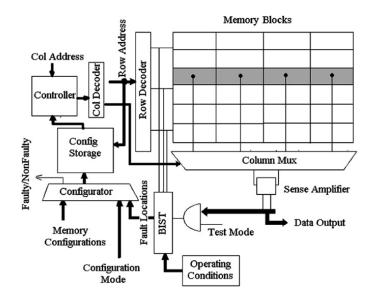

| 4.16 | NAND Flash based disk cache block diagram                                                                                                                                                                                                                                 |

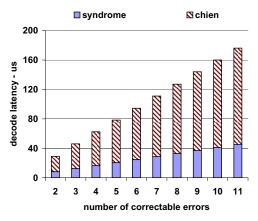

| 4.17 | BCH decoding latency for varying numbers of correctable bits. Source: Taeho Kgil [4]                                                                                                                                                                                      |

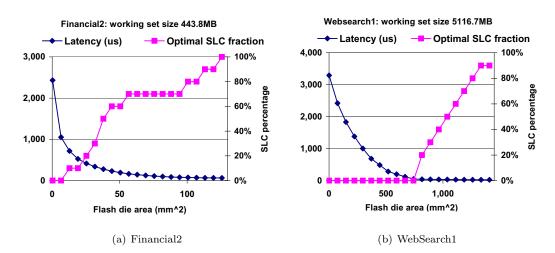

| 4.18 | Optimal access latency and SLC/MLC partition for various multimode MLC Flash sizes                                                                                                                                                                                        |

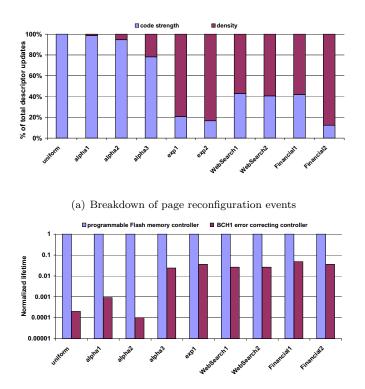

| 4.19 | Relative frequency of lifetime mitigation events and the corresponding improve-<br>ments in lifetime. Source: Taeho Kgil [4]                                                                                                                                              |

| 4.20 | Network bandwidth as a function of DRAM size (including primary disk cache) and secondary disk cache technology. The system was provisioned with 1GB of secondary disk cache                                                                                              |

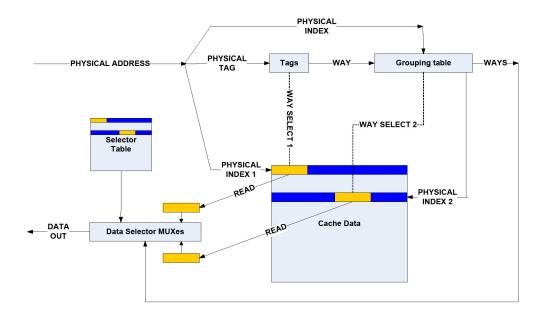

| 5.1  | The one bit implementation (OBI) technique                                                                                                                                                                                                                                |

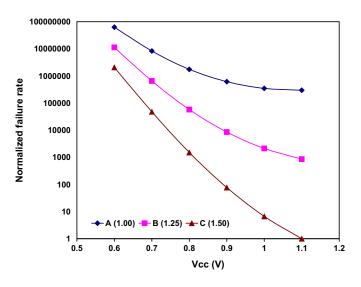

| 5.2  | Normalized cell failure rates as a function of voltage for three different memory cells116                                                                                                                                                                                |

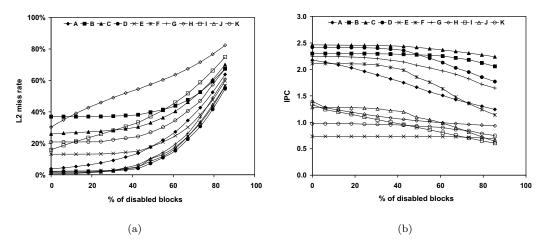

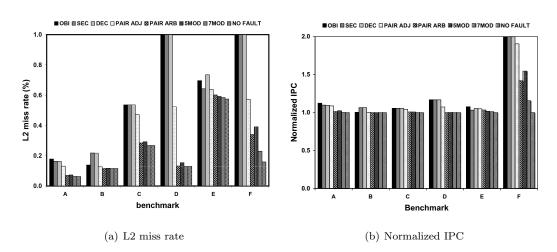

| 5.3  | L2 miss rate in (a) and IPC in (b) as a function of number of randomly disabled<br>blocks. A-Cholesky, B-FFT, C-LUContig, D-LUNoncontig, E-Radix, F-Barnes,<br>G-FMM, H- OceanContig, I-OceanNoncontig, J-Raytrace, and KWaterNSquared,<br>respectively                   |

| 5.4  | The proposed block grouping scheme                                                                                                                                                                                                                                        |

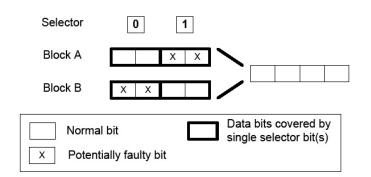

| 5.5  | Example of selector usage (2 bits/selector)                                                                                                                                                                                                                               |

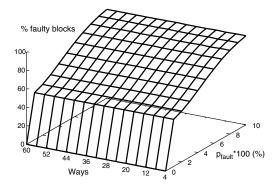

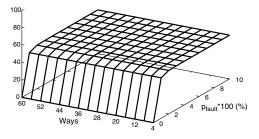

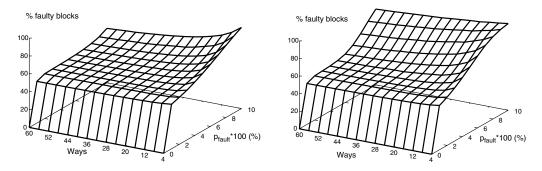

| 5.6  | Percentage of faulty blocks using block pairing $(G = 2)$ for different group restric-<br>tions. Block size = 32 bytes                                                                                                                                                    |

| 5.7 | L2 miss rate in (a) and normalized IPC in (b) for each technique. A-Cholesky,<br>B-FFT, C-LUContig, D-Radix, E-OceanContig, and F-OceanNoncontig, respectively.133 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

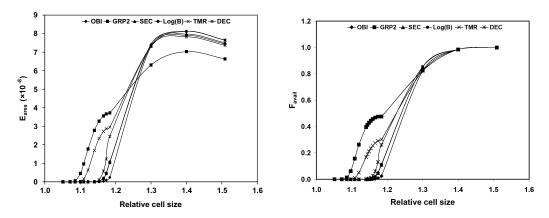

| 5.8 | Comparison of schemes when scaling cell size. Cell size is relative to the smallest considered size from Figure 5.2                                                |

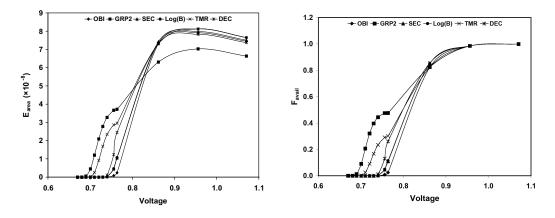

| 5.9 | Comparison of schemes when scaling voltage                                                                                                                         |

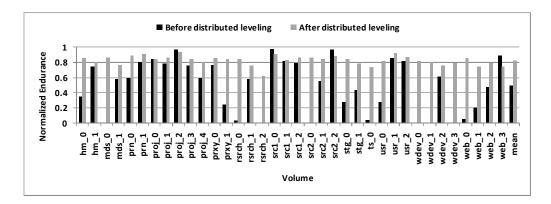

| 7.1 | Start-Gap Normalized Endurance                                                                                                                                     |

# LIST OF TABLES

# <u>Table</u>

| 2.1 | Storage technology parameters (single-cell density, bandwidth, latency, energy and write endurance). We focus on non-volatile memories as candidate permanent data stores. The DRAM DIMM is included for baseline system modelling. The first three rows are estimates for an entire storage device rather than individual bit cells alone, projected to the 2015 timeframe, based on historical scaling trends. We assume 10 Watts total power per HDD and 2 Watts per SSD. Off-chip DRAM access energy is derived from [5]. The lower section contains published parameters from various sources. PCM and Memristor numbers were scaled according to ITRS'09 projections for the year 2015. | 20 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Memory idle power [6]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 22 |

| 3.1 | Network layer scaling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 57 |

| 3.2 | Hardware configurations. Optimized CPUs have their frequency, issue width and number of cores per socket adjusted for optimal system performance (throughput, energy or EDP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 70 |

| 4.1 | List of traces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 39 |

| 4.2 | Baseline SSD parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 96 |

| 5.1 | M5 CPU Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 18 |

| 5.2 | Candidate cache fault-tolerance schemes and their storage overheads for an 1MB cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 21 |

| 5.3 | Selector bit caching parameters and results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 32 |

| 5.4 | Block grouping energy saving example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 36 |

### ABSTRACT

Efficient Data Center Architectures Using Non-Volatile Memory and Reliability Techniques

by David Andrew Roberts

Chair: Trevor N. Mudge

The cost of running a data center is increasingly dominated by energy consumption, contributed by power provisioning, cooling and server components such as processors, memories and disk drives. Meanwhile, emerging classes of complex data center workloads place a heavier burden on processing and storage hardware, involving accesses to huge datasets for each operation. Fortunately, emerging technologies promise better performance and efficiency. Non-volatile (NV) memories for applications such as disk caches [7, 4, 2, 8] are proven ways to save energy, and in recent developments, byte-addressable persistent storage such as phase-change memory (PCM) or Memristors can serve as both main memory and permanent storage, reducing data transfers between layers of hierarchy. Further, 3D die-stacking provides a low-energy high-bandwidth means of connecting storage with computation hardware. The challenge lies in how to optimally combine and balance system elements when data-center workload demands vary significantly. Once combined, new, inherent drawbacks such as limited memory write endurance need to be countered. Further, as processors often dominate system power consumption, they become a critical target for energy optimization. Unfortunately, current CPU architectures cannot fully exploit voltage scaling due to the need for safety margins [9] as well as having large caches that fail at higher voltages than the logic circuits [10].

In this thesis, we address these challenges via the following novel techniques;

- We propose a distributed, energy-efficient data center architecture [11, 12], replacing hard disk drives and DRAM main memory with non-volatile Memristors or PCM. The system is composed of a network of uniform building blocks called Nanostores that combine processors with a permanent data store. To reduce unnecessary data movement, DRAM and disk layers are eliminated, resulting in a flattened memory hierarchy.

- Because NV memories wear out with the number of data writes, we propose novel wear-leveling solutions. First we propose distributed data center wearleveling [13] to address SSD-based and future Nanostore based storage, with a 3.9x improvement in lifetime. Second, we propose server-level reliability improvements for Flash memory based disk caches [4] that provide 20x improve-

ments in lifetime on average.

• We propose a novel on-chip cache fault tolerance scheme that allows more than a 30% improvement in energy efficiency [14, 15, 16].

# CHAPTER I

# Introduction

This thesis proposes that new architectures at the chip, server and data-center levels have the potential to save energy and increase performance by significant factors. Although optimization at any one level provides some of the benefits, the improvements multiply when combined at the system level. In the era of "cloud computing" where applications are provided as a globally accessible service that accesses persistent data, these are critical issues. The data centers which house the computing, storage and associated cooling infrastructure for these services are now being designed around minimizing cooling costs. For example, there have been studies on operating at different temperatures [17] and special building designs for improved cooling [18]. These cooling costs are directly related to the power consumption, so minimizing energy per unit of work (efficiency) can bring significant cost reductions. Meanwhile, the applications themselves have to process and combine multiple discrete data items in a single operation, for example, combining information about multiple friends on a Facebook web page, or correlating the raw text and images of multiple websites [19]. To handle this type of data, alternative storage such as DRAM (instead of hard disk) provides a higher performance, but expensive alternative.

Fortunately, these demands come at a time when technology is becoming available

that may overcome the limitations of conventional architectures. Flash-based solidstate disks have been around for several years and are gradually being adopted to augment or replace hard disks due to their performance and efficiency. Further out on the horizon are competitors to DRAM and SRAM including phase-change memory (PCM), Memristors (MRT) and MRAM (Magnetic RAM) which promise future scalability, higher capacities and lower energy than current storage. Most of these non-volatile memories have an important limitation - finite write endurance that has been addressed through write reduction, wear-leveling and fault-tolerance schemes. However, because we want to take advantage of these devices in the data center, this thesis proposes mechanisms for system-wide wear-leveling rather than conventional leveling inside one SSD only. Finally, we identify that especially for current systems, and even for our new architecture, the CPU often consumes the largest fraction of system power. To address this critical component, we enable an existing energy-saving technique (voltage scaling) to work even more effectively, by reducing the voltage at which on-chip memories fail.

This section describes the changing data center landscape in detail, from system architecture to workload types. We go on to examine emerging technology trends and architectural device parameters, then specify the challenges which this thesis overcomes.

### 1.1 Data Center Trends

#### 1.1.1 Energy-efficient Data Center Architectures

Energy consumed by data centers is a significant contributor of costs to companies and the environment [20]. For example, a survey estimates that over a third of operating costs in 2010 are on power and supporting infrastructure (power distribution and cooling) (see Figure 1.1). In an attempt to reduce these costs, recent research

Figure 1.1: IDC survey indicates increasing cost of power and cooling [1, 2]

has focused on several different approaches to reduce energy footprint. These include aspects such as data center cooling schemes and efficient power supply provisioning. However, this thesis focuses on the server and networking hardware components. In this area, initial work has focused on choosing the right balance of system components to prevent energy waste. For example, simple processors remove circuit complexity and increase efficiency for workloads that perform large amounts if I/O and have low instruction-level parallelism (ILP). Also, the use of solid-state disks instead of hard disks yield further benefits in idle and active power. Components are generally provisioned to be fully utilized. For example, an idle hard disk still consumes a large fraction of full power when not being accessed, unless it is switched to a low-power state with long wake-up delay. A typical study of this type is JouleSort [21] which employs a low-power CPU with 13 laptop disk drives to sort a fixed amount of data using minimum energy. More radical system architecture changes take component integration even further and utilize low-power cores with emerging memory technologies. Low-power cores are viable for storage I/O intensive workloads because they do not need to perform complex processing on data (reducing circuit complexity), and can run at a low frequency and voltage. Flash based storage is better than hard

disk because is has almost no idle power (versus up to 80% of peak for hard disks) and lower access energy per bit. For example, FAWN and Gordon [22][23] approach the problem by combining low-power, simple processors with energy-efficient Flash memory. Gordon represents a distributed network of nodes consisting of a large amount of Flash memory for storage and a small amount of DRAM along with a power-efficient 1.9 GHz Intel Atom processor. They emphasize a 75% reduction in power consumption combined with 900 MB/s of storage bandwidth over conventional designs. FAWN is a similar system but uses 500 MHz cores and is designed specifically for a key-value data store. While these two designs derive their benefits from low-power cores and Flash-based storage, there is another performance-driven end of the spectrum. RamCloud [24] is another architecture trend whose energy efficiency has not been widely studied. A RamCloud uses distributed DRAM main memory to hold all persistent data instead of disk drives. It is argued that because of the very low latency and high bandwidth of DRAM, energy per operation can be orders of magnitude lower than hard disks based systems, and 5-10x better than Flash SSD systems. Our results also demonstrate that applications which are not bottlenecked on other system components such as the network do have better energy per operation than disk based systems. Our Nanostore design provides even greater benefits however, by combining non-volatility with low latency and high bandwidth similar to DRAM.

#### 1.1.2 Workloads and Datasets

The amount of data being created is exploding, growing significantly faster than Moore's law. For example, the size of the largest data warehouse in the Winter Top Ten Survey has been increasing at a cumulative annual growth rate of 173% [25]. The amount of online data is estimated to have risen nearly 60-fold in the last seven years [26]. Data from richer sensors, digitization of offline content, and new applications like twitter, search, etc., will only increase data growth rates. Indeed, it is estimated that only 5% of the worlds offline data has been made online so far [27]. This growth in data is leading to a corresponding growth in data-centric applications that operate on data in diverse ways (capture, classify, analyze, process, archive, etc). Compared to traditional enterprise workloads (e.g., online transaction processing, web services), emerging data-centric workloads change a lot of assumptions about system design. These workloads typically operate at larger scale (hundreds of thousands of servers) and on more diverse data (e.g., structured, unstructured, rich media) with I/O intensive, often random, data access patterns and limited locality. In addition, these workloads have been characterized by a lot of innovations in the software stack targeted at increased scalability and commodity hardware (e.g., Google MapReduce/BigTable). MapReduce [28] is a software framework that breaks workloads into "Map" and "Reduce" functions. During the map phases, data is separated into small units and each one is processed on a different worker node. The results are sent back to a master node where the Reduce function extracts the final answer from all of the sub-problem results. BigTable is the distributed database system used to handle data manipulation by MapReduce tasks. As for the applications themselves, emerging data center workloads have diverse requirements in multiple dimensions. For example, some impose a response time constraint e.g. Web searches, while others may be background tasks, such as data compression and de-duplication. Other dimensions include compute complexity, I/O intensity, data access locality and volume of data to be processed in a single operation. These application requirements significantly influence the best system architecture for performance or energy efficiency. Further, we would like to ensure that the data center architecture that we propose provides benefits for all types of workload. To ensure this, in Section 3.2.1

we propose a taxonomy of the relevant dimensions that a representative data center benchmark set should cover. We then use benchmark models that we identified to optimize our proposed efficient data center design in Section 3.3.3.

### 1.2 Technology Trends

### 1.2.1 Storage Technology and I/O interfaces

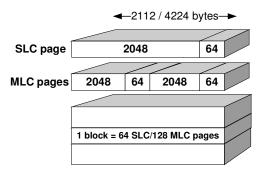

Historically, hard disk drives have been the major persistent storage device used in data centers. They are available in a wide range of capacities up to around 2 GB, and with multiple rotational speeds to trade off latency, bandwidth and cost. With a relatively high random seek time of several milliseconds, sequential accesses provide higher performance. A further drawback of hard disks is that even when idle, a large fraction of peak power is consumed by the spinning disk. Although disks can be "spun down" during idle periods, the long spin-up times reduce energy savings. More recently, NAND Flash-based solid-state disks (SSDs) have been made available, offering random access times of tens of microseconds, with much lower idle power. The highest-performing SSDs are composed of single-level (SLC) Flash which stores one bit per cell. Cheaper, denser Flash chips using multi-level cells (MLC) can be used at the price of roughly double the read latency and triple the write latency for 2-bit-per-cell MLC. Clearly, NAND Flash is most suitable for data where high IOPS (I/Os per second) are required. Due to the price premium of an SSD, hybrid systems are likely to be more common in the near-term.

Current consumer-grade hard disks and solid-state disks employ serial-ATA (SATA) interfaces, allowing throughputs of up to 3 Gbit/s or 6 Gbit/s for revision 2 or 3 of the standard. This narrow channel can act as a bottleneck for SSDs, preventing the peak theoretical throughput of the storage medium from being reached. Therefore, multiple drives on separate channels can be used together for higher bandwidths. For

more I/O intensive workloads that can benefit from greater bandwidths, PCI-express based I/O cards based on NAND Flash memory [29] provide bandwidths up to 1.5 GB/s. These bandwidths are still very low relative to the memory interface of a typical computer system, and present a bottleneck for workloads that spend most of their time moving data with little or no local manipulation.

The usage models pursued by industry and academia for NAND Flash integration can be categorized as follows [2].

- Extended system memory usage model: A NAND Flash memory module is connected to the current system memory interface or to a dedicated Flash memory interface.

- Storage accelerator usage model: A NAND Flash PCI express card is connected to the PCI express interface.

- Alternative storage device usage model: A Solid State Drive (SSD) replaces or augments the hard disk drive. It is connected to the disk interface. An example would be a SATA SSD.

|                            | Primary<br>powersavings | Secondary<br>powersavings | Hardware<br>complexity | OS kernel<br>modification | Application<br>modification | Comments                                                |

|----------------------------|-------------------------|---------------------------|------------------------|---------------------------|-----------------------------|---------------------------------------------------------|

| Extended system<br>memory  | DRAM                    | Disk                      | Minimal                | Medium                    | None                        | Extend kernel memory manager<br>to manage Flash devices |

| I/O accelerator            | Disk                    | DRAM                      | Medium                 | Medium                    | Yes                         | Need to build I/O accelerator<br>driver stack           |

| Alternative storage device | Disk                    | DRAM                      | High                   | Minimal                   | None                        | Need to implement filesystem<br>for Flash               |

Figure 1.2: Comparison of flash usage models in a server [2]

Each usage model presents a unique set of benefits and challenges. Figure 1.2 qualitatively captures them.

The "extended system memory" usage model presents Flash as a part of the system memory. It addresses the rising contribution of power consumed by DRAM in addition to the electrical constraints limiting the integration of more system memory. For example, to increase storage capacity without having to reduce the operating frequency of the memory channel, [30] packs more DRAM onto each DIMM module. Using denser memory such as Flash or PCRAM may serve a similar purpose. However, this usage model requires modification to the operating system kernel. Specifically, the current implementation in the kernel memory manager that supports non-uniform memory architectures needs to be aware of the unique organization and behavior of Flash. Flash reliability management can be performed by the kernel memory manager with the assistance of the Flash controller.

The "storage accelerator" usage model presents Flash as a PCI express device that can be directly managed by the user application. This usage model allows the server application to manage Flash directly as a cache that stores frequently accessed code and data. It reduces the number of accesses to the hard disk drive thereby reducing overall disk power. Further, it may also be used as a way to implement the "extended system memory" usage model but with several drawbacks such as higher latency, lower throughput and added complexity in managing Flash. Flash management is distributed across the user application, device driver stack and the Flash PCI express card firmware. To truly leverage Flash as a "storage accelerator," the user application should be Flash aware. A device driver stack needs to be implemented to support the PCI express device. The device driver stack needs to implement device sharing mechanisms such that other con- current user applications and kernel components can make use of it simultaneously. In Fusion-IOs Solid State Storage [29]— they have also shown the "storage accelerator" usage model can expose the Flash PCI express device as an SSD by providing disk emulation features in the device driver stack.

The "alternative storage device" usage model presents Flash as an SSD that re-

8

places a hard disk drive. This usage model improves the latency and throughput to disk and reduces overall disk power consumption in a data center. With appropriate filesystems such as ZFS [31] it improves storage device scalability in a data center. Flash reliability management is performed by the Flash device controller in the SAN or NAS. However, this usage model also requires modification in the kernel, and a complex Flash device controller that is capable of performing intelligent Flash reliability management. A customized filesystem needs to be implemented to fully take advantage of the benefits of Flash. Further, this usage model ties itself to the non-Flash aware features that are found in a hard disk drive interface protocol such as SATA. Flash-specific commands have only just been implemented in the disk drive standards, such as the TRIM command which informs an SSD when certain blocks are no longer needed, assisting in garbage collection. On the other hand, the operating system in the "extended main memory" model has full visibility of memory page classification and activity statistics that can be used for more intelligent mapping of data to Flash. Servers clearly benefit from all three usage models that essentially integrate Flash as a faster hard disk or disk cache. All usage models help (1) reduce unnecessary standby power from hard disk drives and (2) improve overall throughput by reading and writing from disk cache instead of a hard disk drive.

This thesis proposes to employ the "extended system memory" storage model to reap the benefits of using the same physical medium for memory and persistent storage. When moving from Flash-based storage to an emerging resistive memory such as PCRAM, the storage cells already have similar properties to the system memory. Indeed, several proposals have been made for using PCRAM as a DRAM main memory replacement [32, 33, 34]. It is a logical extension of this model to combine main memory and data storage in the same device, minimizing inter-device data transfers and maximizing communication bandwidth.

#### 1.2.2 Networking and Communication

Different communication paths are fundamental to data center systems, and we described the storage layer in the previous section. Inter-server data center networks can currently contribute up to 50% of cluster power [35]. Therefore it is important to consider the network as both a potential performance bottleneck and power consumer, as we do in this thesis. Modern Ethernet networking can provide 40-100 Gbit/s per link (40/100GBASE). In terms of topologies, many have been explored, including more traditional folded clos (fat-tree) [36, 37] as well as proposals for other designs such as flattened butterfly [35]. This design supports the same bisection bandwidth (peak bandwidth when network is split into two equal parts) with fewer links and router chips. Further, there have been proposals for dynamically adjusting the bandwidth to enable power scaling (power proportionality) in network interfaces (NICs) and switches. This is particularly useful for energy saving where bandwidth demand varies over a period of time.

Optics have also been studied for on-chip communication [38, 39], promising higher performance for connecting cores and memories. However, we do not consider onchip optical networking for this thesis because practical implementations are likely to be beyond our target 2015 timeframe. However, we do exploit 3D die stacking technology [40, 41, 42, 43, 44]. Instead of using an external bus that is restricted by pin count, through-silicon vias (TSVs) are used to connect die together. By using a short, wide interconnect between processors and memory, higher bandwidths and lower bus energy can be achieved. In addition, it allows tight integration of devices with different process technologies, such as logic and DRAM processes.

#### 1.2.3 Emerging memory technologies

Charge-based memories such as DRAM and Flash memory are reaching scaling limits [3] where manufacturing solutions beyond a 2012 time-frame are not known. This is due to the decreasing amounts of charge that can be stored in any bit cell. Fortunately, resistance-based memories such as Phase-Change memory (PCM) are in production and do not depend on charge storage to record data values [32, 45]. Instead, PCM employs a chalcogenide glass material that can change between crystalline and amorphous states when heated, correspondingly changing its resistance. The major drawback with PCM is a high programming current. Other resistive RAMs (RRAM) [46] may help to overcome the high write-current limitations of PCM. The Memristor [47], for example, is predicted to have much lower write energy and higher density due to a multi-layer crossbar architecture [43, 48].

Each technology has system-level drawbacks, such as high latency (Flash), high idle power (DRAM) or high write energy (PCM). We consider these architectural and power parameters during our data center modelling and optimization process. In this work we consider DRAM, PCM and Memristors as the main memory and primary data store, with their different latency, energy and density characteristics, to determine the best data center configuration for each one.

### 1.3 Challenges

#### 1.3.1 Overcoming the inefficiencies of existing storage devices

System memory power (DRAM power) and disk power contribute as much as 40% to the overall power consumption in a data center [8]. Further, current trends suggest that this will continue to increase at a rapid rate as more DRAM and disk drives are integrated to improve throughput. Both technologies also have a signifi-

cant idle power component, further reducing efficiency. There are emerging memory devices in the technology pipeline that may address this concern. These devices typically display high density and consume low idle power. Flash, Phase Change RAM (PCRAM), Memristors and Magnetic RAM (MRAM) fall into this class. Flash is an attractive technology that is already deployed heavily in various computing platforms. Today, NAND Flash can be found in hand-held devices such as smart phones, digital cameras and MP3 players. This has been made possible because of its high density, low power properties and non-volatility. Its popularity has meant that it is the focus of aggressive process scaling and innovation. The rapid rate of improvement in density has become the primary driver to consider Flash for other usage models. There are several Flash usage models in the data center that are currently being examined by industry and academia to address rising power and cooling costs, among other things. Recently, PCRAM has received much attention because of the challenges Flash faces when we scale below the 22nm process technology node. Studies [3] have shown that PCRAM is expected to scale better than Flash post 22nm and emerge as an important and widely used memory device. It currently has DRAM-like read latencies and has been proposed as a DRAM replacement. Memristors [47] are a memory technology predicted to behave similarly to PCRAM with potential for even higher capacity than PCRAM due to their stacked crossbar structure. Although their basic parameters may be better than DRAM or Flash, the most effective ways of integrating them in a system still need to be explored.

#### 1.3.2 Breaking the I/O bandwidth barrier

In Section 1.2.1 we mentioned that the fastest PCI-express based Flash storage cards can achieve around 1.5 GB/s bandwidth. However, modern off-chip DRAM interfaces can achieve over 10 GB/s of throughput, while on-chip 3D-stacked processor designs such as [40] achieve over 32 GB/s of bandwidth. As an extreme example, a 3D-stacked DRAM-PCRAM checkpointing system was designed for 2.5 TB/s transfers [49]. By opening up the bandwidth per unit of capacity, it may be possible to reach new levels of performance and efficiency in the data center. This in itself raises issues of balance in provisioning processors and networking, as well as reaching other constraints such as power density.

#### 1.3.3 Modelling and optimization at data-center scale

Detailed performance and power modelling is possible for individual servers, processing and storage devices. However, when modelling systems that are scaled up to Petabytes of storage and thousands of compute nodes, detailed full-system simulation requires unrealistic amounts of time and hardware. Simplified models may run faster at the cost of some accuracy. Therefore, choosing the right methodology to draw meaningful conclusions about data center designs remains a major challenge.

### 1.3.4 Overcoming non-volatile memory endurance limitations

With growing numbers of Flash based SSDs in use, as well as emerging technologies such as resistive memories, there are concerns over whether the memories will last long enough to be viable solutions. The majority of NV memories can only sustain a limited number of re-writes per bit before becoming unreliable (around  $10^5$ for NAND Flash and  $10^8$  for PCRAM, for example). Further, due to the very low latency of emerging NV memories, the write limit can be reached in a very short time and can be exploited by viruses, for example. These issues have been addressed to some extent using wear-levelling techniques [50, 51] whereby writes are spread across memory locations as evenly as possible within a chip or SSD. However, in the data center, there is significant imbalance of write-bandwidth between individual SSDs. This makes effective wear-levelling difficult to perform in an ensemble, and no solutions currently exist to address this.

### 1.3.5 Breaking CPU voltage-scaling limits

Processors consume a large fraction of energy in the data center, and improved efficiencies in this component will have a significant overall impact. To minimize power, an appropriate power supply voltage is used at a given frequency, including a safety margin to accommodate power supply noise and process variations. However, processor architectures cannot fully exploit voltage scaling due to the need for safety margins [9] as well as having large caches that fail at higher voltages than the core logic [10]. On-chip SRAM caches operating at the same voltage as the rest of the core can limit voltage reduction at lower frequencies, restricting chip-wide energy savings. As voltage is reduced, increasing numbers of bits fail to operate, but gorrecting them with conventional error-correcting codes (ECC) can introduce intolerable latencies. There is clearly a need for low-latency fault-tolerance schemes to maintain a functional cache with small latency overhead.

# 1.4 Contributions

#### 1.4.1 Re-architecting the storage hierarchy with Nanostores

This thesis proposes and evaluates a novel data center system architecture that enables higher energy efficiency and performance to be achieved compared to conventional disk-based or DRAM-based architectures. The key features of the design are a uniform storage building block consisting of processing cores, a network interface, 3D-stacked interconnect and a unified data store/main memory device. By allowing I/O to take advantage of the high bandwidth normally reserved for main memory alone, emerging I/O intensive workloads get significant performance and energy-delay-product (EDP) increases over an aggressively optimized baseline. The unified storage design also removes the need for data copying between disk and RAM. Further energy efficiency is gained from the use of low-power cores and efficient storage technologies. The nodes or "Nanostores" are networked in a conventional fat-tree configuration and appear to software as a conventional cluster of networked servers.

### 1.4.2 Extending wear-leveling to distributed storage

We propose extending wear-leveling algorithms normally constrained to a single storage drive to the entire data center. This is required to support the energy efficiency improvements of distributed non-volatile storage (SSDs or Nanostores). By exploiting typical access patterns present in data center disk workloads, we are able to significantly increase the time to first failure (TTFF) of a data center storage ensemble. Further, we propose novel techniques to increase the performance and lifetime of MLC Flash memory devices installed in servers. These include dynamically switching between SLC and MLC modes for pages of Flash, and progressively increasing the number of correctable errors to minimize average access latency.

### 1.4.3 Overcoming the limits of CPU voltage scaling

Because CPU energy is a significant power consumer for several data center workloads (especially in non-optimized conventional designs), we focus on techniques to reduce CPU power. Our first contribution was a voltage control system for a delay-fault-tolerant processor that can remove voltage safety margins [52, 53, 54]. The second (which is the focus of this thesis) is a low-latency cache fault-tolerance scheme that allows whole-chip energy savings by enabling cache operation at reduced voltages [14, 15, 16].

# 1.5 Thesis Structure