# **Efficient Execution of Compressed Programs**

by

**Charles Robert Lefurgy**

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 2000

Doctoral Committee:

Professor Trevor Mudge, Chair Professor Richard Brown Assistant Professor Steve Reinhardt Assistant Professor Gary Tyson There is a right physical size for every idea.

— Henry Moore (1898-1986). English sculptor.

© Charles Robert Lefurgy 2000

To my parents, Clark and Sarah.

# Acknowledgments

Trevor Mudge served as my advisor during the course of my graduate studies. His persistent question-asking helped shape the course of my research.

Eva Piccininni and Ed Kohler developed an ARM microprocessor that supports software-assisted decompression based on the results of my research. Eva wrote the first software version of our CodePack-like compression/decompression software. She also performed many experiments for optimizing hybrid programs in compressed code systems. Eva was especially helpful as a coauthor on our publications which presented the initial research results of this dissertation. Ed developed the first hardware description of a microprocessor with instruction set extensions for executing compressed programs. In addition, he mapped the design onto an FPGA for running large application simulations. Ed and Eva were both helpful in implementing and critiquing initial versions of the software decompression method that is the basis for much of this dissertation.

A significant amount of my time in graduate school was spent working with the MIRV team to build a C compiler. Although I did not ultimately use this compiler for my dissertation research, working on that project has broadened my understanding of computer architecture. I thank the members of the MIRV team, Matt Postiff, David Greene, David Helder, and Kris Flautner, for answering the countless questions I had about compilers.

Finally, I would like to thank my parents, Clark and Sarah, who supported me throughout my academic endeavors. My father sparked my interest in computers when he presented me with my first programming book at age eight.

# **Table of Contents**

| Dedication   |                                          | ii   |

|--------------|------------------------------------------|------|

| Acknowled    | gments                                   | iii  |

| List of Tab  | les                                      | vi   |

| List of Figu | ires                                     | viii |

| Chapter 1    | Introduction                             | 1    |

| 1.1          | Data compression                         | 2    |

| 1.2          | Text compression                         | 4    |

| 1.3          | Repetition in object code                | 6    |

| 1.4          | 1                                        | 6    |

| 1.5          | Organization                             | 7    |

| Chapter 2    | Background                               | 9    |

| 2.1          | General code compression techniques      | 10   |

| 2.2          | Decompression of individual instructions | 12   |

| 2.3          | Decompression at procedure call          | 18   |

| 2.4          | Decompression within the memory system   | 19   |

| 2.5          | Decompression at load-time               | 20   |

| 2.6          | Compiler optimizations for compression   | 24   |

| 2.7          | Conclusion                               | 28   |

| Chapter 3    | Instruction-level compression            | 29   |

| 3.1          | Introduction                             | 29   |

| 3.2          | Overview of compression method           | 30   |

|              | Experiments                              | 34   |

| 3.4          | Discussion                               | 43   |

| 3.5          | Conclusion                               | 44   |

| Chapter 4    | Hardware-managed decompression           | 46   |

| 4.1          | Introduction                             | 46   |

| 4.2          | Related work                             | 47   |

| 4.3          | Compression architecture                 | 47   |

| 4.4          | Simulation environment                   | 50   |

| 4.5          | Results                                  | 53   |

| 4.6          | Conclusion                               | 60   |

| Chapter 5    | Software-managed decompression           | 62   |

| 5.1          | Introduction                             | 62   |

| 5.2         | Related work                                     | 63  |

|-------------|--------------------------------------------------|-----|

| 5.3         | Software decompressors                           | 64  |

| 5.4         | Compression architecture                         | 66  |

| 5.5         | Simulation environment                           | 71  |

| 5.6         | Results                                          | 73  |

| 5.7         | Conclusion                                       | 76  |

| Chapter 6   | Optimizations for software-managed decompression | 79  |

| 6.1         | Introduction                                     | 79  |

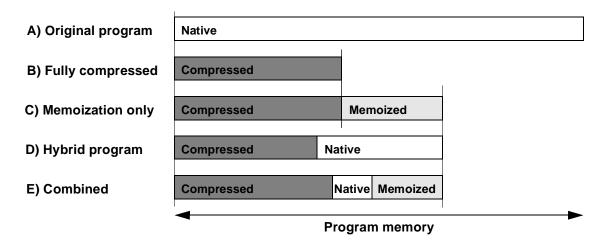

| 6.2         | Hybrid programs                                  | 81  |

| 6.3         | Memoization                                      | 88  |

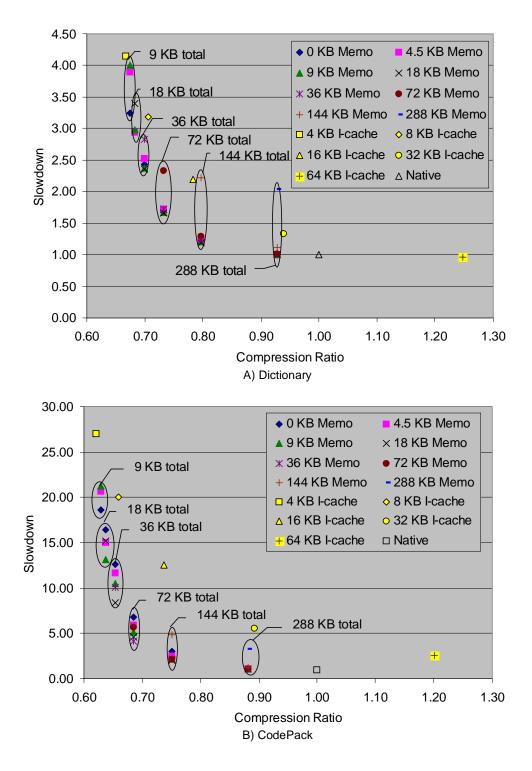

| 6.4         | Memoization and selective compression            | 105 |

| 6.5         | Conclusion                                       | 112 |

| Chapter 7   | Conclusion                                       | 131 |

| 7.1         | Research contributions                           | 131 |

|             | Future work                                      | 134 |

| 7.3         | Epilogue                                         | 136 |

| Appendix A  | A Program listings                               | 137 |

| A.1         | Macros                                           | 138 |

|             | Dictionary                                       | 139 |

|             | Dictionary Memo-IW                               | 141 |

| A.4         | •                                                | 144 |

| A.5         | Dictionary Memo-EW                               | 147 |

| A.6         | Dictionary Memo-EL                               | 151 |

| A.7         | CodePack                                         | 155 |

| A.8         |                                                  | 162 |

|             | CodePack Memo-IL                                 | 170 |

|             | CodePack Memo-EW                                 | 178 |

| A.11        | CodePack Memo-EL                                 | 188 |

| Bibliograpl | ıy                                               | 197 |

# **List of Tables**

| Table 3.1:  | Maximum number of codewords used in baseline compression         | 38  |

|-------------|------------------------------------------------------------------|-----|

| Table 4.1:  | Benchmarks                                                       | 51  |

| Table 4.2:  | Simulated architectures                                          | 52  |

| Table 4.3:  | Compression ratio of .text section                               | 53  |

| Table 4.4:  | Composition of compressed region                                 | 54  |

| Table 4.5:  | Instructions per cycle                                           | 55  |

| Table 4.6:  | Index cache miss ratio for cc1                                   | 56  |

| Table 4.7:  | Speedup due to index cache                                       | 56  |

| Table 4.8:  | Speedup due to decompression rate                                | 57  |

| Table 4.9:  | Comparison of optimizations                                      | 57  |

| Table 4.10: | Variation in speedup due to instruction cache size               | 58  |

| Table 4.11: | Performance change by memory width                               | 59  |

| Table 4.12: | Performance change due to memory latency                         | 60  |

| Table 5.1:  | Simulation Parameters                                            | 71  |

| Table 5.2:  | Compression ratio of .text section                               | 74  |

| Table 5.3:  | Slowdown compared to native code                                 | 74  |

| Table 6.1:  | Taxonomy of cache access instructions                            | 93  |

| Table 6.2:  | Memoization table contents                                       | 97  |

| Table 6.3:  | Performance of memoization                                       | 104 |

| Table 6.4:  | Memory on System-on-Chip                                         | 108 |

| Table 6.5:  | Area and performance as a function of I-cache size (cc1)         | 113 |

| Table 6.6:  | Area and performance as a function of I-cache size (ghostscript) | 113 |

| Table 6.7:  | Area and performance as a function of I-cache size (go)          | 113 |

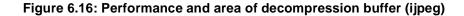

| Table 6.8:  | Area and performance as a function of I-cache size (ijpeg)       | 113 |

| Table 6.9:  | Area and performance as a function of I-cache size (mpeg2enc)    | 114 |

| Table 6.10: | Area and performance as a function of I-cache size (pegwit)      | 114 |

| Table 6.11: | Area and performance as a function of I-cache size (perl)        | 114 |

| Table 6.12: | Area and performance as a function of I-cache size (vortex)      | 114 |

| Table 6.13: | Decompression buffer performance and area (cc1)                  | 115 |

| Table 6.14: | Decompression buffer performance and area (ghostscript)          | 117 |

| Table 6.15: | Decompression buffer performance and area (go)                   | 119 |

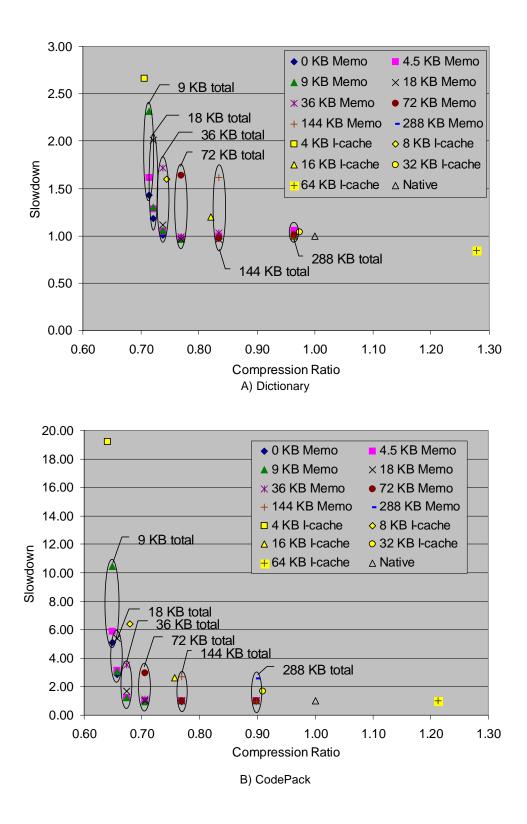

| Table 6.18:Decompression buffer performance and area (pegwit)125Table 6.19:Decompression buffer performance and area (perl)127 | Table 6.16: | Decompression buffer performance and area (ijpeg)    | 121 |

|--------------------------------------------------------------------------------------------------------------------------------|-------------|------------------------------------------------------|-----|

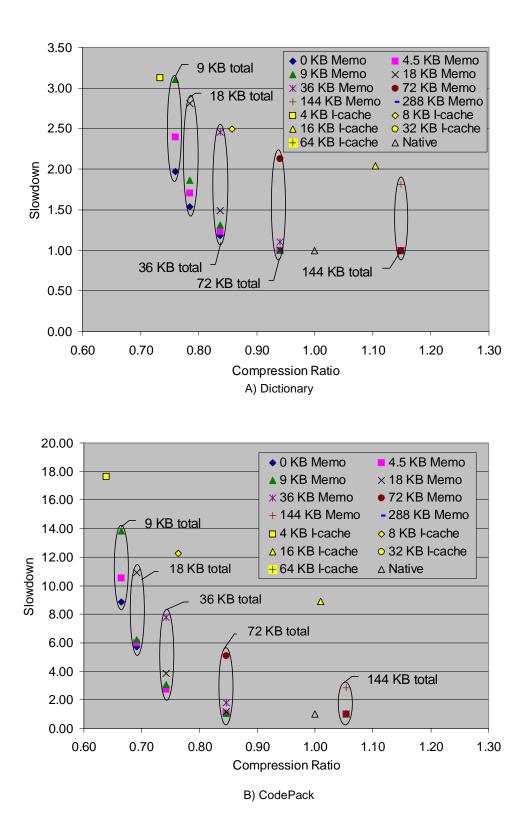

| Table 6.19:Decompression buffer performance and area (perl)127                                                                 | Table 6.17: | Decompression buffer performance and area (mpeg2enc) | 123 |

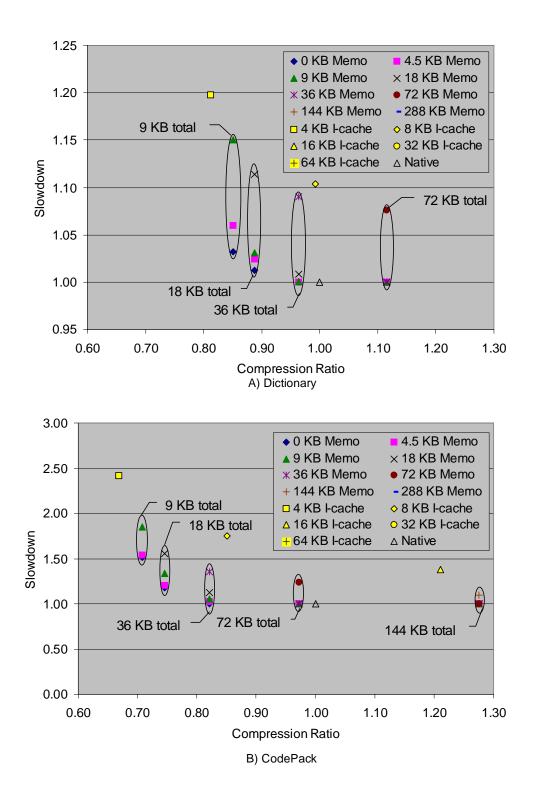

|                                                                                                                                | Table 6.18: | Decompression buffer performance and area (pegwit)   | 125 |

| Table 6.20:Decompression buffer performance and area (vortex)129                                                               | Table 6.19: | Decompression buffer performance and area (perl)     | 127 |

|                                                                                                                                | Table 6.20: | Decompression buffer performance and area (vortex)   | 129 |

# **List of Figures**

| Figure 1.1:  | Instruction bit patterns                                         | 7  |

|--------------|------------------------------------------------------------------|----|

| Figure 2.1:  | Dictionary compression                                           | 10 |

| Figure 2.2:  | Custom instruction sets                                          | 16 |

| Figure 2.3:  | BRISC                                                            | 17 |

| Figure 2.4:  | Procedure compression                                            | 18 |

| Figure 2.5:  | Compressed Code RISC Processor                                   | 19 |

| Figure 2.6:  | Slim binaries                                                    | 21 |

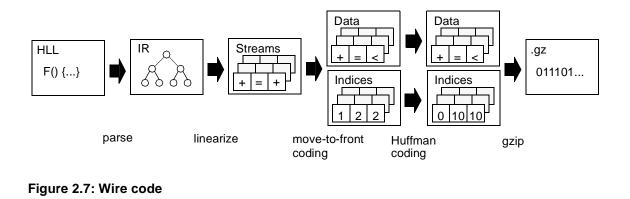

| Figure 2.7:  | Wire code                                                        | 22 |

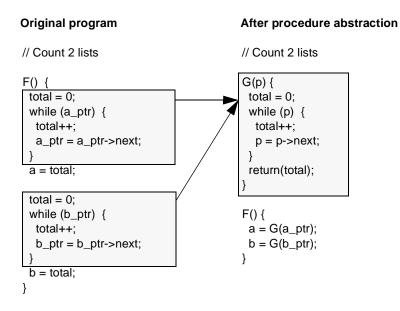

| Figure 2.8:  | Procedure abstraction                                            | 25 |

| Figure 2.9:  | Mini-subroutines                                                 | 26 |

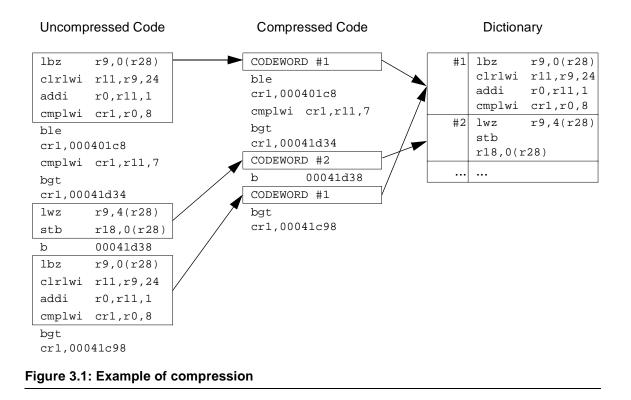

| Figure 3.1:  | Example of compression                                           | 31 |

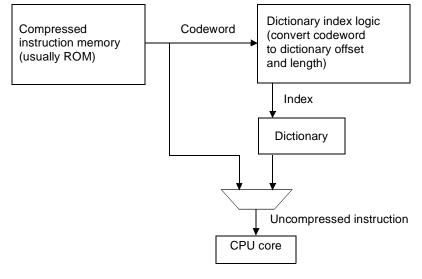

| Figure 3.2:  | Compressed program processor                                     | 34 |

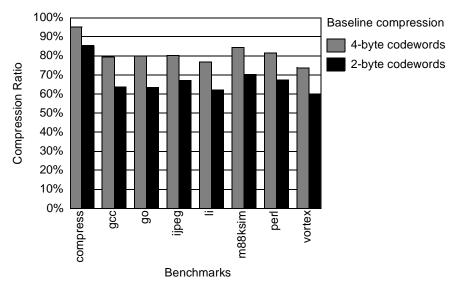

| Figure 3.3:  | Compression ratio using 2-byte and 4-byte codewords              | 36 |

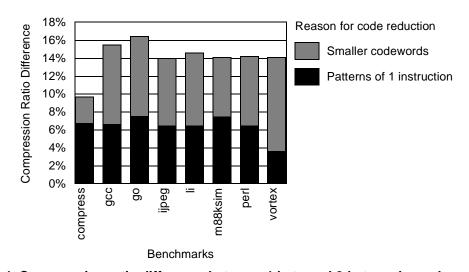

| Figure 3.4:  | Compression ratio difference between 4-byte and 2-byte codewords | 37 |

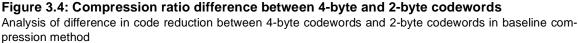

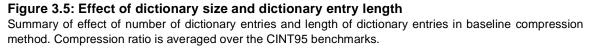

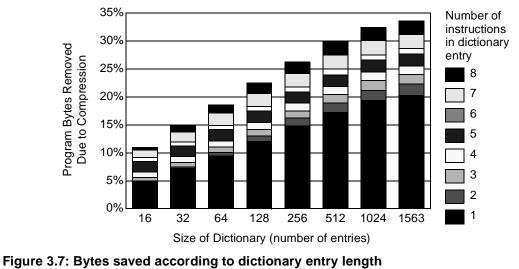

| Figure 3.5:  | Effect of dictionary size and dictionary entry length            | 37 |

| Figure 3.6:  | Composition of dictionary for ijpeg                              | 39 |

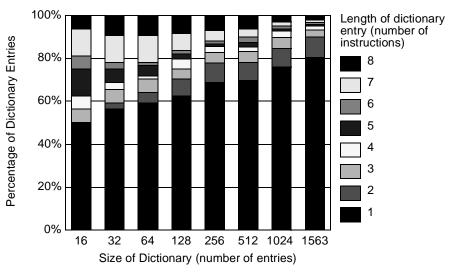

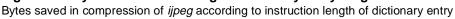

| Figure 3.7:  | Bytes saved according to dictionary entry length                 | 39 |

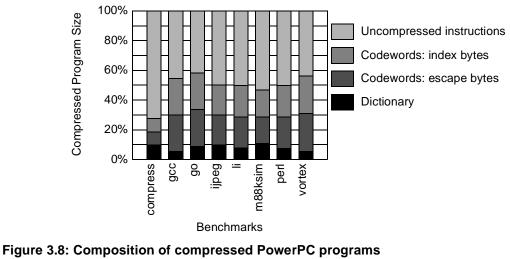

| Figure 3.8:  | Composition of compressed PowerPC programs                       | 40 |

| Figure 3.9:  | Nibble aligned encoding                                          | 41 |

| Figure 3.10: | Nibble compression for various instruction sets                  | 42 |

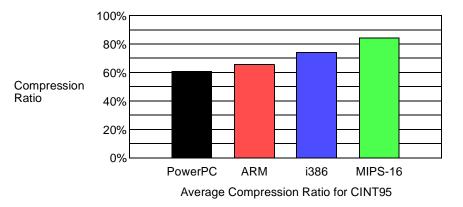

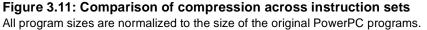

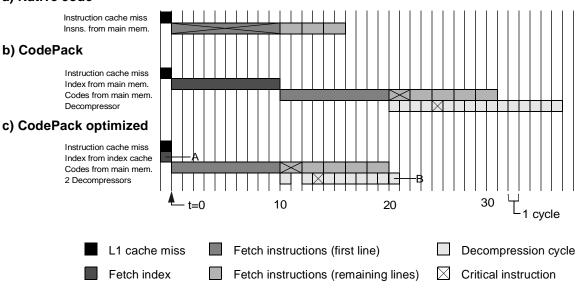

| Figure 3.11: | Comparison of compression across instruction sets                | 42 |

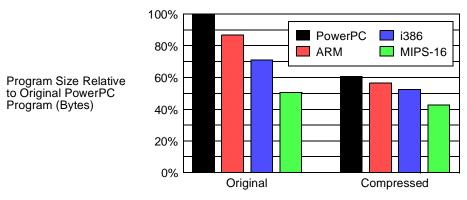

| Figure 3.12: | Comparison of MIPS-2 with MIPS-16                                | 43 |

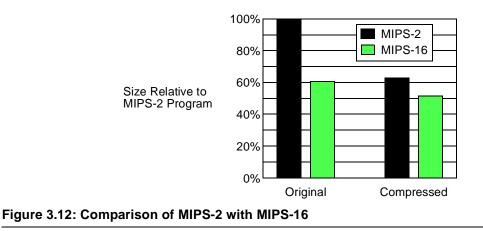

| Figure 4.1:  | CodePack decompression                                           | 48 |

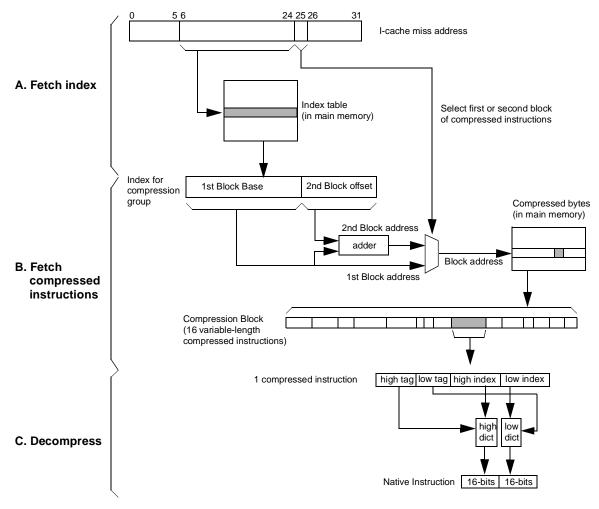

| Figure 4.2:  | Example of L1 miss activity                                      | 52 |

| Figure 5.1:  | Dictionary compression                                           | 65 |

| Figure 5.2:  | L1 miss exception handler for dictionary decompression method    | 72 |

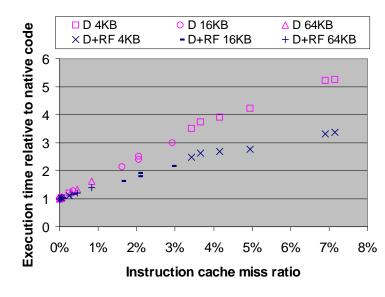

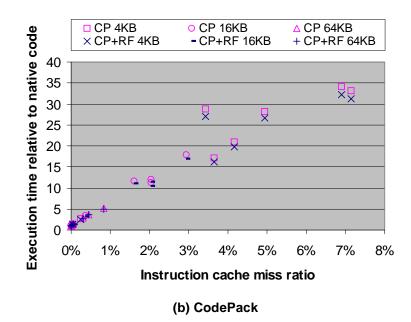

| Figure 5.3:  | Effect of instruction cache miss ratio on execution time         | 77 |

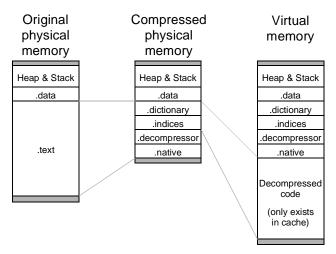

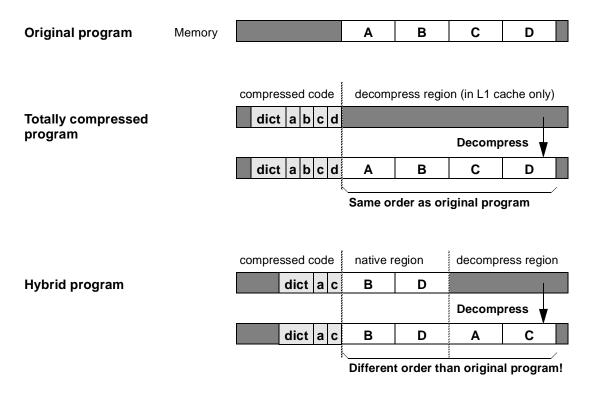

| Figure 6.1:  | Memory layout for dictionary compression                         | 83 |

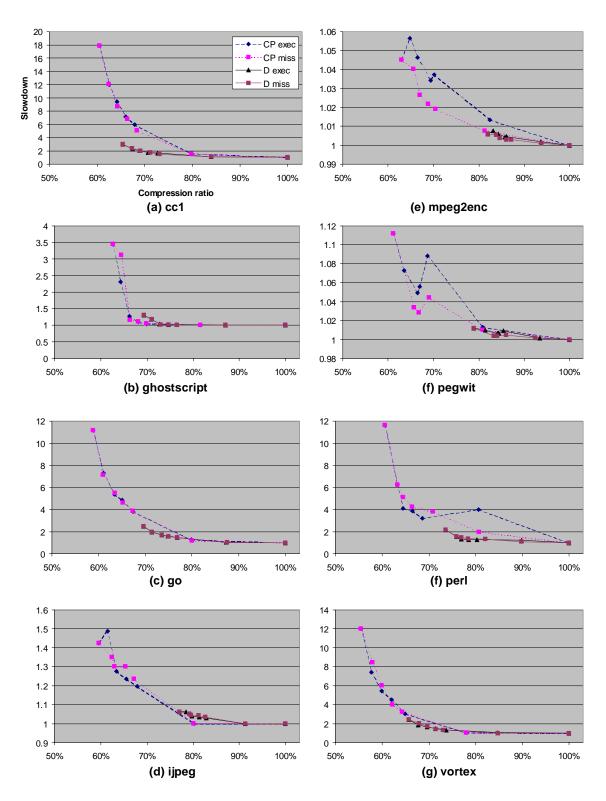

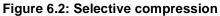

| Figure 6.2:  | Selective compression                                            | 84 |

| Figure 6.3:  | Procedure placement in hybrid programs                           | 87 |

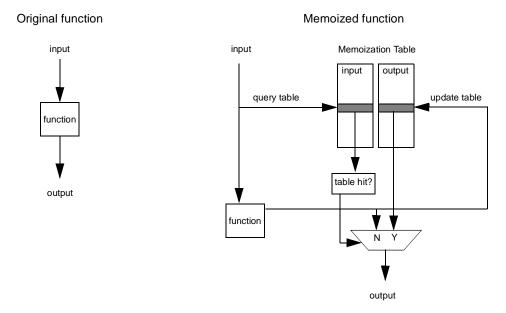

| Figure 6.4:  | Memoization overview                                             | 88 |

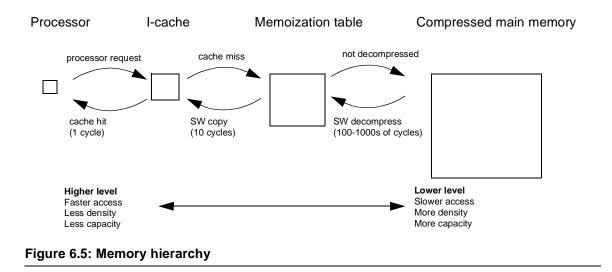

| Figure 6.5:  | Memory hierarchy                                           | 89  |

|--------------|------------------------------------------------------------|-----|

| Figure 6.6:  | Memoized decompressor                                      | 98  |

| Figure 6.7:  | Memo-IW                                                    | 99  |

| Figure 6.8:  | Memo-IL                                                    | 100 |

| Figure 6.9:  | Memo-EW                                                    | 101 |

| Figure 6.10: | Memo-EL                                                    | 103 |

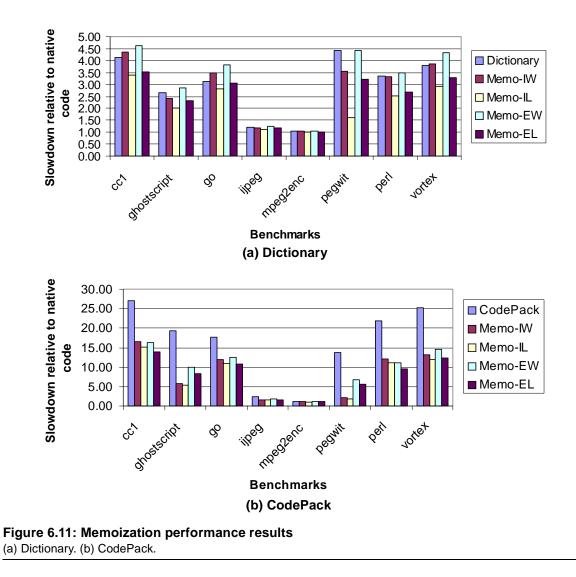

| Figure 6.11: | Memoization performance results                            | 105 |

| Figure 6.12: | Memory usage                                               | 107 |

| Figure 6.13: | Performance and area of decompression buffer (cc1)         | 116 |

| Figure 6.14: | Performance and area of decompression buffer (ghostscript) | 118 |

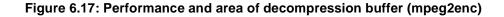

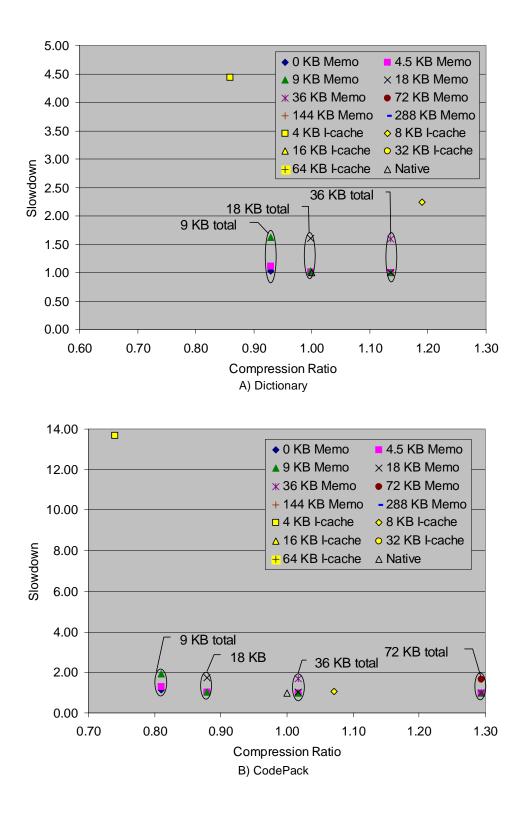

| Figure 6.15: | Performance and area of decompression buffer (go)          | 120 |

| Figure 6.16: | Performance and area of decompression buffer (ijpeg)       | 122 |

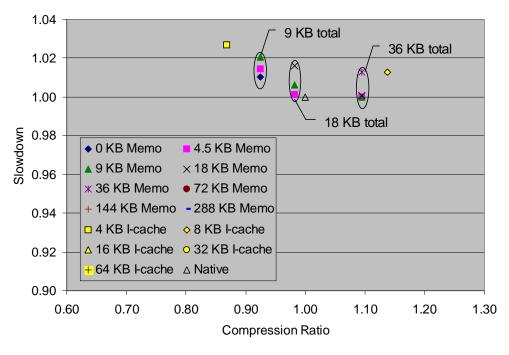

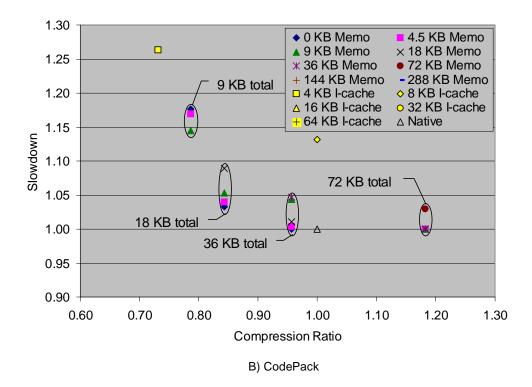

| Figure 6.17: | Performance and area of decompression buffer (mpeg2enc)    | 124 |

| Figure 6.18: | Performance and area of decompression buffer (pegwit)      | 126 |

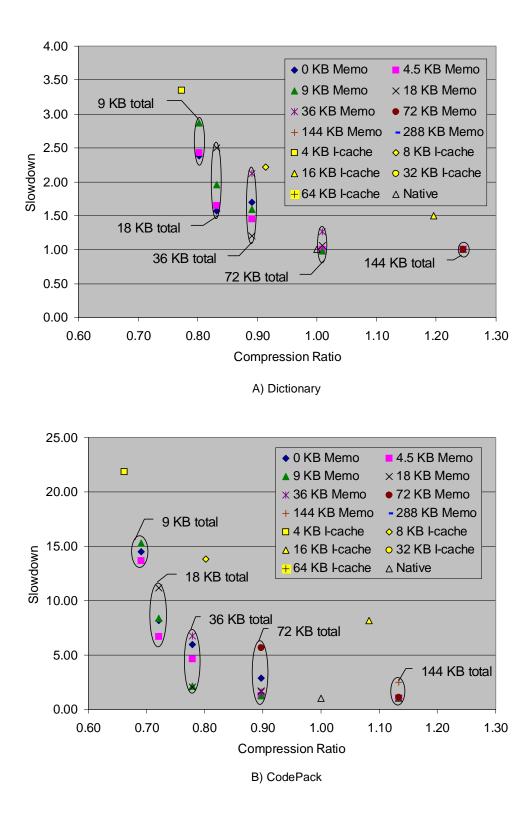

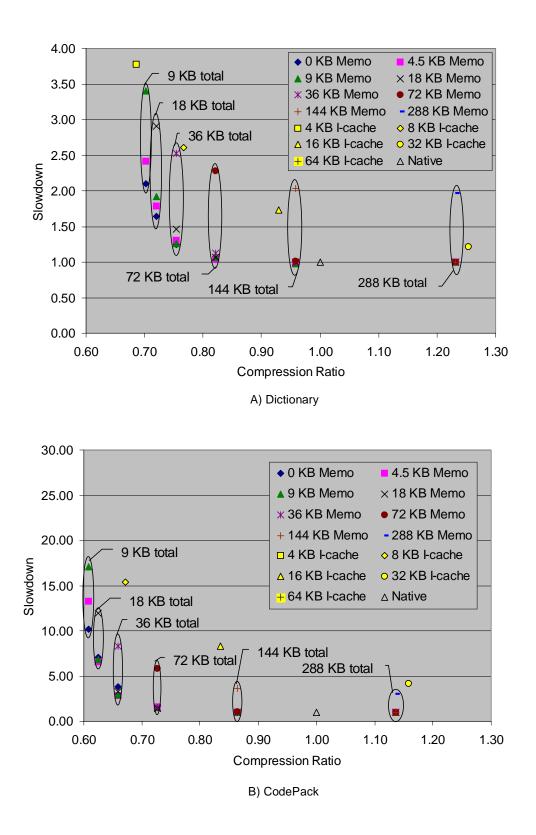

| Figure 6.19: | Performance and area of decompression buffer (perl)        | 128 |

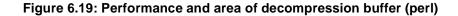

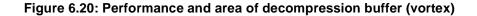

| Figure 6.20: | Performance and area of decompression buffer (vortex)      | 130 |

# Chapter 1 Introduction

Embedded microprocessors are highly constrained by cost, power, and size. This is particularly true for high-volume, low-margin consumer applications. Reducing microprocessor die area is an important way to save cost because it not only allows more dies to be put on a wafer, but it can vastly improve die yield. For control-oriented embedded applications, the most common type, a significant portion of the die area is used for program memory. Therefore, using smaller program sizes implies that smaller, cheaper dies can be used in embedded systems. An additional pressure on program memory is the relatively recent adoption of high-level languages for embedded systems. As typical code sizes have grown, high-level languages are being used to control development costs. However, compilers for these languages often produce code that is much larger than hand-optimized assembly code. Thus, the ability to compile programs to a small representation is important to reduce both software development costs and manufacturing costs.

High performance systems are also impacted by program size due to the delays incurred by instruction cache misses. A study at Digital [Perl96] measured the performance of an SQL server on a DEC 21064 Alpha. Due to instruction cache misses, the application could have used twice as much instruction bandwidth as the processor was able to provide. This problem is exacerbated by the growing gap between the cycle time of microprocessors and the access time of commodity DRAM. Reducing program size is one way to reduce instruction cache misses and provide higher instruction bandwidth [Chen97a].

#### **Research contribution**

Both low-cost embedded systems and high-performance microprocessors can benefit from small program sizes. This dissertation focuses on program representations of

embedded applications, where execution speed can be traded for improved code size. We examine *code compression* methods which reduce program code size by using data compression techniques. In general, the usual techniques of text compression, typified by Ziv-Lempel compression, cannot be directly applied to programs because they require that the complete program be compressed or decompressed at once. If a program cannot be incrementally decompressed then the operation of decompressing the complete program will require more (temporary) memory than the uncompressed program — defeating the original reason for employing compression. Incremental decompression avoids this problem. However, incremental decompression requires that information about program labels (jump and call targets) be recoverable incrementally too.

Previous research in this area has suggested that compressed code systems will execute programs slower than native code systems, especially when the decompression is done in software. The primary goal of this research is to demonstrate that compressed programs can still execute with a high level of performance. First, we shows that even simple instruction-level compression methods can attain interesting levels of compression. This is important for building fast decompressors that will operate with high performance. Second, we show a hardware decompression method that can often eliminate the decompression penalty and sometimes execute compressed programs faster than native programs. Third, we examine the performance of decompression in software. Software decompression is interesting because it reduces the die area and cost of embedded microprocessors while allowing greater design flexibility. However, the decompression overhead is extremely high compared to hardware decompression. We present methods that greatly reduce the software decompression overhead and demonstrate that compressed multimedia applications execute with nearly the same performance as native programs.

This chapter introduces data compression and its application to program compression. It concludes with an overview of the organization of this dissertation.

# **1.1 Data compression**

The goal of data compression is to represent information in the smallest form that still holds the information content. Traditional data compression methods make several

assumptions about the data being compressed. First, it is assumed that the compression must be done in a single sequential pass over the data because typical data may be too large to contain in storage (main memory or disk) at one time. One example of such data is a continuous stream of video. Second, this single pass approach takes advantage of history of recent symbols in the data stream. History information allows compressors to utilize repetition in the data and modify the compression technique in response to the changing characteristics of the data stream. This constrains the decompressor to start at the beginning of the data stream. The decompressor cannot begin decompressing at an arbitrary point in the data stream because it will not have the history information that the decompression algorithm depends upon. Third, most data compression methods use bit-aligned output to obtain the smallest possible representations.

In contrast, compression algorithms for computer programs use a significantly different set of assumptions in order to retain acceptable levels of performance.

First, programs are small enough to fit in storage, so the compressor can optimize the final compressed representation based on the entire program instead of using only recent history information. However, compression cannot be applied to the program as a whole, because it would be necessary to decompress the entire program at once to execute it – invalidating any execution-time size advantage. Therefore, programs must use incremental decompression. As the program executes, units of it are decompressed and executed. As more of the program is decompressed, previously decompressed units must be discarded due to system memory constraints. The unit of compression could be a procedure, a cache line, or an individual instruction. This allows the decompressed unit and the complete compressed program to use less memory than the original native code program.

Second, since decompression will occur as the program is executing, it is desirable to begin decompression at arbitrary points in the program. This is important to consider when choosing the unit of incremental decompression. For example, since program execution can be redirected at branch instructions it would be ideal for the decompression to begin at any branch target. This effectively splits the program into blocks of instructions defined by branch targets. The unpredictable nature of the execution path between program runs is likely to constrain the length of history information available to the compressor.

The third assumption about compressed programs is that a decompressed block may not be entirely executed due to branch instructions that cause early exit from the block. While larger block sizes may improve performance of history-based compression methods, they will also decrease program performance by causing time to be wasted decompressing instructions that are not executed. Therefore, techniques such as Ziv-Lempel compression which rely on the recent history information of large compression buffers may be unsuitable for compressing programs that require high-performance or high levels of compression. Unfortunately, smaller block sizes may also decrease program performance. Small blocks require the decompressor be invoked more frequently. This can be detrimental to performance if the invocation overhead is significant.

Fourth, most microprocessors have alignment restrictions which impose a minimum size on instructions. For example, compressors may restrict their encodings to begin on byte boundaries so that the decompressors can quickly access codewords. This would require the use of pad bits to lengthen the minimum size of codewords.

Finally, an advantage that programs have over typical data is that portions of the program (statements, instructions, etc.) can be rearranged to form an equivalent program. The code-generation phase of a compiler could assist in generating compression-friendly code. This may allow the compressor to find more compressible patterns.

## **1.2 Text compression**

Lossless compression or text compression refers to a class of *reversible* compression algorithms that allow the compressed text to be decompressed into a message identical to the original. They are particularly tailored to use a linear data stream. These properties make text compression applicable to computer programs, which are linear sequences of instructions. Surveys of text compression techniques have been written by Lelewer and Hirschberg [Lelewer87] and Witten et al. [Witten90]. Compression algorithms that are not lossless are called lossy. These algorithms are used for compressing data (typically images) that can tolerate some data loss in the decompressed message in exchange for a smaller compressed representation. Since computer programs must be executed without ambiguity, lossy compression is not suitable for them.

Text compression methods fall into two general categories: statistical and dictionary [Bell90]. Statistical compression uses the frequency of singleton characters to choose the size of the codewords that will replace them. Frequent characters are encoded using shorter codewords so that the overall length of the compressed text is minimized. Huffman encoding of text is a well-known example. Dictionary compression selects entire phrases of common characters and replaces them with a single codeword. The codeword is used as an index into the dictionary entry which contains the original characters. Compression is achieved because the codewords use fewer bits than the characters they replace.

There are several criteria used to select between using dictionary and statistical compression techniques. Two very important factors are the *decode efficiency* and the overall *compression ratio*. The decode efficiency is a measure of the work required to re-expand a compressed text. The compression ratio is defined by the formula:

$$compression \ ratio = \frac{compressed \ size}{original \ size}$$

(Eq. 1.1)

Dictionary decompression uses a codeword as an index into the dictionary table, then inserts the dictionary entry into the decompressed text stream. If codewords are aligned with machine words, the dictionary lookup is a constant time operation. Statistical compression, on the other hand, uses codewords that have different bit sizes, so they do not align to machine word boundaries. Since codewords are not aligned, the statistical decompression stage must first establish the range of bits comprising a codeword before text expansion can proceed.

It can be shown that for every dictionary method there is an equivalent statistical method which achieves equal compression and can be improved upon to give better compression [Bell90]. Thus statistical methods can always achieve better compression than dictionary methods albeit at the expense of additional computation requirements for decompression. It should be noted, however, that dictionary compression yields good results in systems with memory and time constraints because one entry expands to several characters. In general, dictionary compression provides for faster (and simpler) decoding, while statistical compression yields a better compression ratio.

## **1.3 Repetition in object code**

Object code generated by compilers mostly contains instructions from a small, highly used subset of the instruction set. This causes a high degree of repetition in the encoding of the instructions in a program. In the programs we examined, only a small number of instructions had bit pattern encodings that were not repeated elsewhere in the same program. Indeed, we found that a small number of instruction encodings are highly reused in most programs.

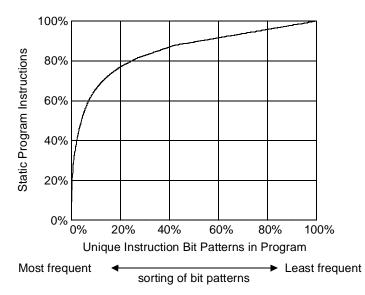

To illustrate the repetition of instruction encodings, we profiled the SPEC CINT95 benchmarks [SPEC95]. The benchmarks were compiled for PowerPC with GCC 2.7.2 using -O2 optimization. In Figure , the results for the *go* benchmark show that 1% of the most frequent instruction words account for 30% of the program size, and 10% of the most frequent instruction words account for 66% of the program size. On average, more than 80% of the instructions in CINT95 have bit pattern encodings which are used multiple times in the program. In addition to the repetition of single instructions, we also observed that programs contain numerous repeated sequences of instructions. It is clear that the repetition of instruction encodings provides a great opportunity for reducing program size through compression techniques.

# 1.4 Scope

This dissertation only addresses the problem of compressing instruction memory. Some embedded applications require much more data memory than instruction memory. For such applications, compressing data memory may be more beneficial. However, the characteristics of program data are highly application specific. No single compression algorithm is suitable for all types of data. The data size problem is has been partly addressed by the wide variety of application specific data compression formats available (JPEG, MPEG, gzip, etc.). On the other hand, the program code in different applications tends to look similar because the same language, the instruction set, is used to express the

#### Figure 1.1: Instruction bit patterns

This graph shows the unique instruction bit patterns in a program as a percentage of static program instructions. The data is from the *go* benchmark compiled for PowerPC. The x-axis is sorted by the frequency of bit patterns in the static program.

program. Therefore, a single compression algorithm can compress a range of applications quite well.

Another important issue for embedded systems is power dissipation. Since a compressed program may trade an improved size for a longer running time, it is possible that it will dissipate more power than a larger program that runs for a shorter time. However, requirements for embedded systems vary widely. A cell phone must run on batteries, but a printer is plugged into an outlet. The suitability of code compression depends on the underlying requirements of the embedded system. Regardless, embedded systems can always benefit from lower manufacturing costs made possible by using smaller microprocessor dies. Therefore, the focus of this dissertation is how to utilize die area to execute compressed programs efficiently.

# **1.5 Organization**

The organization of this dissertation is as follows. Chapter 2 reviews previous work to obtain small program sizes. This chapter provides important background for understanding the remainder of the dissertation. Chapters 3, 4 and 5 are largely independent and can be read in any order. Chapter 3 contains the results of a preliminary experi-

ment that applies text compression techniques to programs at the instruction level. Chapter 4 provides an in-depth study of using hardware-managed decompression. Chapter 5 implements decompression in software. In some applications, the overhead of decompression is comparable to that in hardware-managed decompression. However, many applications experience considerable slowdown. This slowdown is addressed in Chapter 6 which presents optimizations for software decompression. Finally, Chapter 7 concludes the dissertation and suggests possible future work.

# Chapter 2 Background

This chapter surveys previous program compression techniques. Previous methods have performed compression in the compiler, assembler, linker, or in a separate post-compilation pass. Most program compression systems do compression only during initial program creation and do not re-compress the program as it is running. Decompression can be performed on individual instructions immediately before execution, when a procedure is called, in the memory system as instructions are fetched, or when the program is loaded into memory. Because the point at which decompression occurs varies widely among systems, we organize our presentation according to the decompression methods. Some of the questions to consider when comparing compression schemes are:

- When is compression done? (In compiler or post-compilation pass?)

- What is the compression algorithm? (Ziv-Lempel, arithmetic, etc.)

- What is compressed? (Instructions, data, or both?)

- When does the system detect that decompression must occur? (During a cache miss, during a procedure call, etc.)

- How are instructions decompressed? (With software or hardware assistance?)

- Where is decompressed code stored? (In the instruction cache or main memory?)

- How is the decompressed code managed? (How much decompressed code is available at once? What gets replaced when more instructions are decompressed?)

This chapter begins with an overview of general techniques that are found in many compressed code systems. This is followed by a discussion of individual compressed code systems organized by decompression method. The chapter ends with a discussion on the role of compiler optimizations in producing small programs.

# 2.1 General code compression techniques

This section reviews some common techniques that many compressed code systems use.

### 2.1.1 Dictionary compression

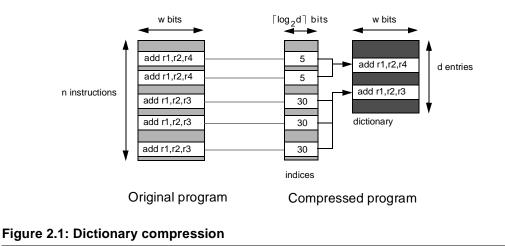

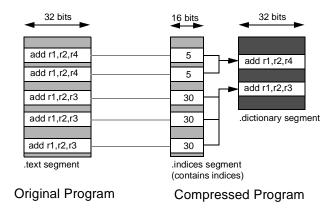

*Dictionary compression* uses a dictionary of common symbols to remove repetition in the program. A symbol could be a byte, an instruction field, a complete instruction, or a group of instructions. The dictionary contains all of the unique symbols in the program. Each symbol in the program is replaced with an index into the dictionary. If the index is shorter than the symbol it replaces, and the overhead of the dictionary is not large, compression will be realized. Figure 2.1 shows an example of dictionary compression where the symbols are entire machine instructions.

In order for compression to be achieved, Equation 2.1 must hold.

$$nw > n \lceil \log_{\gamma}(d) \rceil + dw \qquad (Eq. 2.1)$$

In this equation, n is the number of static instructions in the program, w is the number of bits in a single instruction, and d is the number of symbols in the dictionary. Of course, this equation does not account for the size of specific implementations of the decompressor which also uses microprocessor die area.

If the dictionary contains all the symbols required to reconstruct the original program, then it is said to be complete. If the dictionary is not complete, then an escape mechanism is necessary to tell the decompressor not to use the dictionary, but instead to interpret some raw bits in the compressed program as symbols for the decompressed program. This will result in some expansion of the compressed program. Using some raw bits in the compressed program prevents the dictionary from growing very large and holding symbols that do not repeat frequently in the original program.

Lefurgy et al. [Lefurgy97] use dictionary entries that each hold one or more instructions. Taunton [Taunton91] divides 32-bit instructions into 24-bit and 8-bit fields. The 24-bit field is encoded with its dictionary entry and the 8-bit field is left raw. This is done because the repetition of the entire 32-bit instruction is lower than the 24-bit field and would cause the dictionary to be very large. Citron considers a similar encoding for 32-bit buses between the CPU and main memory [Citron95].

## 2.1.2 Difference encoding

A table of values can be compressed by using *difference* or *delta encoding*. The first value is coded explicitly. The next value is encoded as the difference between it and the first value. The remaining values are encoded as the difference between them and the previous value. When the difference between values is small (such as in a sorted list), then the difference can be encoded in fewer bits than the original values. This has been used to compress decoding tables within compressed programs [Taunton91, Wolfe92, IBM98].

### **2.1.3 Data packing**

Codewords can have sizes that do not align to machine-word boundaries. This slows down access to them. Therefore, fields within codewords are often packed in pairs to improve data alignment. For example, consider using 12-bit codewords that consist of a 4-bit control nibble followed by an 8-bit index. Two codewords might be packed together so that the first byte contains both 4-bit nibbles, the second byte contains the first index, and the third byte contains the second index. On a byte-aligned processor, this allows the decompressor to use a natural byte load instruction to access each part of the code word.

A second reason to use data packing is for speed of parsing and simplification of decompression logic. CodePack [IBM98] uses data alignment to quickly parse codewords in the compression stream. Two control fields of either 2 or 3 bits each are followed by two variable-length index fields. The second control field always starts at either the third or fourth bit of the stream, so it is easy to find. If the control and index fields alternated, there would be a much larger range of possibilities for the starting position of the second control field. This would have complicated the decompression logic. However, since the control fields are easy to find and tell the decompressor how long the index fields are, the following codewords can quickly be located in the compressed stream. Data packing may enable multiple codewords to be identified and decompress the codewords. Taunton mentions the possibility of breaking variable-sized fields in codewords into separate streams to improve load and buffering efficiency [Taunton91]. This allows a single load to be used for each data item, rather than constructing larger items from individual byte loads due to misalignment.

# 2.2 Decompression of individual instructions

This section reviews decompression techniques that target individual instructions.

A conventional microprocessor must fetch and decode an instruction before it is executed. The decoding process expands the native instruction word into many control signals within the microprocessor. Thus, the encoding of the instruction set can be considered a form of compression since the number of control signals is typically greater than the number of bits in the instruction word. In this case, the decompression of the instruction is done by the hardware decode stage of the microprocessor.

The decoding of an instruction may also be done in software by an interpreted-program system. In this case, the application program is written in a highly encoded instruction set that the underlying processor cannot decode or execute. Instead, an interpreter program written in the native instruction set fetches and decodes the instructions in the application. The interpreter is responsible for executing a series of native code instructions to emulate the behavior of the interpreted instruction. These native code instructions are then decoded in the normal manner on the microprocessor.

These decompression techniques described below are divided into two categories. The first category covers the design of instruction sets which are decoded in hardware by the decode stage of a conventional microprocessor. The second category covers interpreted-program environments which decode instructions in software. Both systems decode (or decompress) each instruction individually.

### **2.2.1 Instruction set design**

In our experiments, we have observed that the size of programs encoded in conventional instruction sets can differ by a factor of two. This shows that instruction set design is important to achieve a small program size. Bunda et al. [Bunda93] studied the benefit of using 16-bit instructions over 32-bit instructions for the DLX instruction set. 16bit instructions are less expressive than 32-bit instructions, which causes the number of instructions executed in the 16-bit instruction programs to increase. They report that the performance penalty for executing more instructions was often offset by the increased fetch efficiency.

### **Dual-mode instruction sets**

The work of Bunda et al. can be extended to a microprocessor that utilizes both a 32-bit instruction set and a 16-bit instruction set. A control bit in the processor selects the current instruction set used to decode instructions. This allows a program to have the advantages of wide, expressive instructions for high-performance and short instructions for code density. ARM and MIPS are examples of such dual-mode instruction sets. Thumb [ARM95, Turley95] and MIPS-16 [Kissell97] are defined as the 16-bit instruction set subsets of the ARM and MIPS-III architectures.

A wide range of applications were analyzed to determine the composition of the subsets. The instructions included in the subsets are either frequently used, do not require a full 32-bits, or are important to the compiler for generating small object code. The original 32-bit wide instructions have been re-encoded to be 16-bits wide. Thumb and MIPS-

16 are reported to achieve code reductions of 30% and 40%, respectively [ARM95, Kissell97].

Thumb and MIPS-16 instructions have a one-to-one correspondence to instructions in the base architectures. In each case, a 16-bit instruction is fetched from the instruction memory, decoded to the equivalent 32-bit wide instruction, and passed to the processor core for execution. The 16-bit instructions retain use of the 32-bit data paths in the base architectures.

The Thumb and MIPS-16 instructions are unable to use the full capabilities of the underlying processor. The instruction widths are shrunk at the expense of reducing the number of bits used to represent register designators and immediate value fields. This confines programs to eight registers of the base architecture and significantly reduces the range of immediate values. In addition, conditional execution is not available in Thumb and floating-point instructions are not available in MIPS-16.

Compression in Thumb and MIPS-16 occurs on a per procedure basis. There are special branch instructions to toggle between 32-bit and 16-bit modes.

Thumb and MIPS-16 instructions are less expressive than their base architectures. Therefore, programs require more instructions to accomplish the same tasks. This requires a program to execute more instructions, which reduces performance. For example, Thumb code runs 15% - 20% slower on systems with ideal instruction memories (32-bit buses and no wait states) [ARM95].

### **Custom encodings**

A somewhat different approach was introduced by Larin and Conte [Larin99]. They assume that the embedded processor can be optimized to a specific program. They use the compiler to generate both the compressed program and a custom programmed logic array to fetch and decompress it. One technique they use is to customize the instruction set for the program by shortening instruction fields that are too wide. For example, if only eight registers are used in the program, then the register fields can be shortened to 3 bits. Another technique they use is to Huffman code whole instructions, fields within instructions, or bytes of the instructions. The trade-off here is that as the compressed program becomes smaller, the Huffman decoder becomes larger.

One interesting note is that the compiler removes rare instructions and replaces them with a group of equivalent common instructions that map to shorter Huffman codes. Even though this form of strength-reduction lengthens the final compressed program, it makes the decoder implementation easier by reducing the maximum codeword size that must be decoded.

### 2.2.2 Interpretation

Interpreted-program environments are another method to attain small code size [Klint81]. Typically, application source code is compiled to a space-efficient intermediate form. An interpreter, compiled to native instructions, interprets the intermediate form into native instructions that accomplish the required computation. Because the intermediate code does not need to be concerned with host limitations (instruction word size and alignment), the intermediate instructions can be quite small. Typical interpreted programs for 32-bit instructions have speeds 5-20 times slower than native code and are up to 2 times smaller [Fraser95, Ernst97]. Interpreted code for the TriMedia VLIW processor is 8 times slower than native code and is 5 times smaller [Hooger99].

#### **Directly Executed Languages**

Flynn introduced the notion of Directly Executed Languages (DELs) whose representation could be specifically tailored to a particular application and language [Flynn83]. A DEL is a program representation that is between the level of the source language and machine language. DEL programs are executed by a DEL-interpreter which is written in the machine language. The advantage of DELs are that they provide an efficient method to represent programs. The DEL representation is small for several reasons. First, the DEL representation uses the operators of the source language. Assuming that the high level language is an ideal representation of the program, then these are obviously the correct operators to choose. Second, the DEL does not use conventional load/store instructions, but directly refers to objects in the source language. For example, if a program specifies a variable, the DEL-interpreter is responsible for finding the storage location of the variable and loading it into a machine register. Third, all operators and operands are aligned to 1bit boundaries. The field size of operands changes depending on the number of objects the

Figure 2.2: Custom instruction sets

current scope can reference. Fields are  $\log_2 N$  bits in length for a scope with N objects. For example, if a procedure references eight variables, each variable would be represented as a 3-bit operand. The interpreter tracks scope information to know which set of variables are legal operands at any point in the program.

Flynn measured conventional machine language representations of programs and found them to be between 2.6 to 5.5 times larger than the DEL representation.

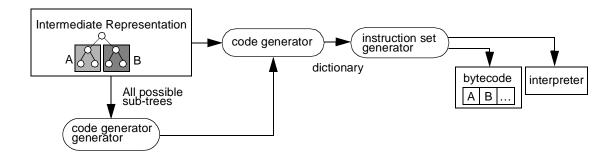

#### **Custom instruction sets**

Whereas Flynn used the high level language as a basis for the operators in DELs, Fraser [Fraser95] used a bottom-up approach and created macro-instructions from instructions in the compiler intermediate representation (IR). He found repeating patterns in the IR tree and used these as macro-instructions in his compressed code. The code generator emits byte code which is interpreted when executed. This process is illustrated in Figure 2.2. The overhead for this interpreter is only 4-8 KB. Fraser showed that this compression method is able to reduce the size of programs by half when compared to SPARC programs. However, the programs execute 20 times slower than the original SPARC programs.

#### BRISC

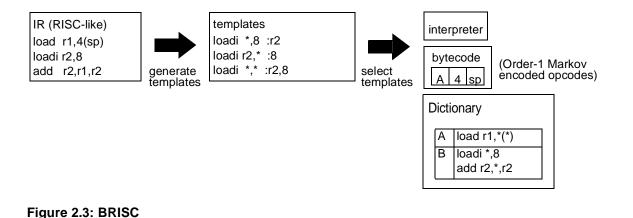

Ernst et al. [Ernst97] developed BRISC which is an interpretable compressed program format for the Omniware virtual machine (OmniVM). The compression method is illustrated in Figure 2.3. BRISC adds macro-instructions to the OmniVM RISC instruction set. BRISC achieves small code size by replacing repeated sequences of instructions in the

# OmniVM RISC code with a byte codeword that refers to a macro-instruction. Macroinstructions that differ slightly may be represented using the same codeword and different arguments. Such macro-instructions are templates that have fields which are supplied by the arguments. The argument values are located in the instruction stream after the codeword. The codewords are encoded using a order-1 Markov scheme. This allows more opcodes to be represented with fewer bits. However, decoding becomes more complicated since decoding the current instruction is now a function of the previous instruction opcode and the current opcode. When BRISC is interpreted, programs run an average of 12.6 times slower than if the program was compiled to native x86 instructions. When BRISC is compiled to native x86 instructions and executed, the program (including time for the compilation) is only 1.08 times slower than executing the original C program which has been compiled to x86 instructions.

Since the compressed program is interpreted, there is a size cost (either hardware or software) for the interpreter. If the size of the interpreter is small enough so that the interpreter and the BRISC program are smaller than a native version of the program, then this system could be useful for achieving small code size in embedded systems.

More complicated compression algorithms have combined operand factorization with Huffman and arithmetic coding [Lekatsas98, Araujo98].

## 2.3 Decompression at procedure call

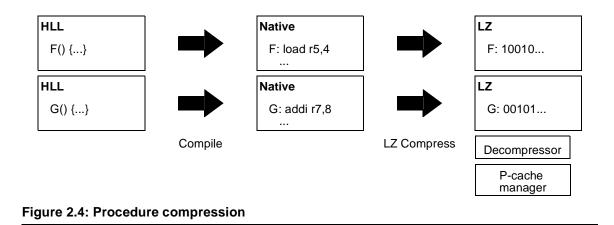

Kirovski et al. [Kirovski97] describe a compression method that works at the granularity of procedures. Figure 2.4 illustrates procedure compression. Each procedure in the program is compressed using a Ziv-Lempel compression algorithm. A segment of memory is reserved as a *procedure cache* for decompressed procedures. On a procedure call, a directory service locates the procedure in compressed space and decompresses it into the procedure cache. The directory maps procedures between compressed and decompressed address space. For this scheme, a small map with one entry per procedure is sufficient. When there is no room in the procedure cache, a memory management routine evicts procedures to free the resource. Procedures are placed in the procedure cache at an arbitrary address. Intra-procedural PC-relative branches, the most frequent type, will automatically find their branch targets in the usual way. Procedure calls, however, must use the directory service to find their targets since they may be located anywhere in the procedure cache. One appealing point of this compression technique is that it can use existing instruction sets and be implemented with minimal hardware support (an on-chip RAM for the procedure cache).

The authors obtained a 60% compression ratio on SPARC instructions. However, it is not clear if this compression ratio accounts for the directory overhead, decompression software, procedure cache management software, and the size of the procedure cache. One

Figure 2.5: Compressed Code RISC Processor

problem is that procedure calls can become expensive since they may invoke the decompression each time they are used. When using a 64 KB procedure cache, the authors measured an average run-time penalty of 166%. When the two programs, *go* and *gcc*, were excluded from the measurement, the average run-time penalty was only 11%. One possible reason for the high overhead is that whole procedures are decompressed, but few instructions are executed in the procedure. Another reason is that executing procedure calls may cause the caller to be evicted from the procedure cache before it has finished. In this case, when the callee exits, the caller must be decompressed again. A final reason for slow execution is that managing fragmentation in the procedure cache may be expensive.

## 2.4 Decompression within the memory system

Decompression within the memory system hides the process of decompression from the microprocessor core. This allows the system to reuse the original core design without modification. Decompression is triggered with the microprocessor fetches instructions. From the microprocessor's perspective, decompression appears as a long latency memory access.

### 2.4.1 Compressed Code RISC Processor

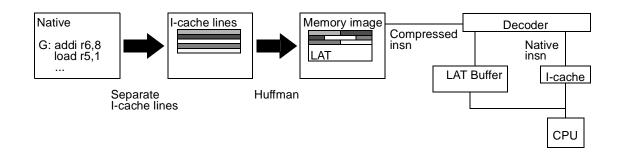

The Compressed Code RISC Processor (CCRP) [Wolfe92, Kozuch94] is an interesting approach that employs an instruction cache that is modified to run compressed programs. The CCRP system is illustrated in Figure 2.5. At compile-time, the cache line bytes are Huffman encoded. At run-time, cache lines are fetched from main memory, decompressed, and put in the instruction cache. Instructions fetched from the cache have the same addresses as in the original program. Therefore, the core of the processor does not need modification to support compression. However, cache misses are problematic because missed instructions in the cache do not reside at the same address in main memory. CCRP uses a Line Address Table (LAT) to map missed instruction cache addresses to main memory addresses where the compressed code is located.

The authors report a 73% compression ratio for MIPS instructions. A working demonstration of CCRP has been completed [Benes97, Benes98]. Implemented in 0.8μm CMOS, it occupies 0.75 mm<sup>2</sup>, and can decompress 560 Mbit/s.

Lekatsas and Wolf explore other compression algorithms for CCRP [Lekatsas98]. Their SAMC (Semi-adaptive Markov Compression) algorithm combines a Markov model with an arithmetic coder. Each instruction is partitioned into small blocks. Since each instruction is partitioned the same way, blocks with the same location in each instruction define a stream. All streams are compressed separately. This attains a 57% compression ratio on MIPS programs. Their SADC (Semi-adaptive Dictionary Compression) algorithm creates a dictionary of the instruction fields (opcode, register, immediate, and long immediate). In addition, the dictionary contains entries consisting of common combinations of adjacent fields (such as an opcode and a register). The dictionary indices are Huffman encoded. This attains a 52% compression ratio on MIPS. However, the price of better compression is a more complicated decompressor.

# 2.5 Decompression at load-time

This section describes systems that decompress programs when they are loaded over a network or from a disk. These techniques are not directly applicable to memorylimited computers because at execution time the compressed programs are expanded to full-size native programs. Although these techniques do not save space at execution time, they provide some of the smallest program representations.

### **2.5.1 Slim binaries**

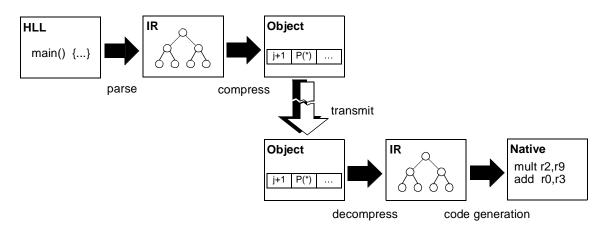

Franz and Kistler developed a machine-independent distribution format called *slim binaries* [Franz94, Franz97]. The slim binary format is a compressed version of the abstract syntax tree (AST) in the compiler. The compression is done by using a dictionary of sub-trees previously seen in the AST. When the program is run, the loader reads the slim binary and generates native code on-the-fly. The process is illustrated in Figure 2.6. The benefit of slim binaries is that abstract syntax trees compress well so that the distribution format is very small. This reduces the time to load the program from disk into memory. The time for code-generation is partially hidden because it can be done at the same time that the program is being loaded. Franz and Kistler reported that loading and generating code for a slim binary is nearly as fast as loading a native binary.

Even though the slim binary format represents programs in a very small format (smaller than 1/3 the size of a PowerPC binary), this size does not include the size of the code generator. Slim binaries may work well to reduce network transmission time of programs, but they are not suitable for embedded systems that typically run a single program because the slim binary format is not directly executable. There is no program size benefit at run-time because a full size native binary must be created to run the program. The only size benefit is during the time the program is stored on disk or being transmitted over a network.

### 2.5.2 Wire codes

Ernst et al. [Ernst97] also introduced an encoding scheme that is suitable for transmitting programs over networks. Figure 2.7 illustrates how it works. The authors compress the abstract syntax tree of the program in the following manner. First, the tree is linearized and split into separate streams of operators and literal operands. The literal operand stream is further separated into streams for each operand type. Second, each stream is move-to-front encoded. Move-to-front coding works by moving symbols to the front of the stream as they are referenced. Assuming that the symbols have temporal-locality, the indices used to address the symbols in the stream will tend to have small values. The indices are coded with a variable-length scheme that assigns short codes to the indices with small values and long codes to the indices with large values. This results in a compact representation for the frequently used symbols at the front of the stream. In the wire code, the move-to-front indices are Huffman-coded. Finally, the results are passed through the *gzip* program. They achieve very small code sizes (1/5 the size of a SPARC executable). When the program is received, it must be decompressed and compiled before execution. Therefore, this is not a representation that can be used at execution-time.

### 2.5.3 RISC iX

Taunton describes the use of dictionary compression for a low-cost computer using the ARM processor [Taunton91]. Each page of text and data in the executable is compressed. The decompressor is integrated with the operating system and each page is decompressed as it is demand loaded. The compression algorithm saves 45-50% disk space on a RISC iX system and causes programs to load 40% faster from disk. Taunton notices that compressed programs load faster over the network on diskless machines than native code. In addition, the RISC iX virtual memory system does not place text pages in the swap area. Instead, it reloads them through the file system and decompresses them again. This performance penalty was necessary to reduce disk space in a low-cost workstation. Taunton also notes that shared libraries are a form of code compression for saving space on disk and memory.

### 2.5.4 File system

Techniques used to save space in the file system compress both instructions and data. These techniques could be useful in an embedded system that uses a file system in a long-term, nonvolatile memory, for instance.

#### **Cate and Gross**

Cate and Gross [Cate91] investigate using the filesystem to automatically compress the least recently used files and decompress them when the user accesses them. Using a PPM (prediction by partial matching) compression algorithm resulted in a compression factor of 3. They compressed the least recently used 75% of files and kept other files in their original non-compressed format. This resulted in a typical decompression time of 50 seconds per user per day. Thus, compression can double the available disk storage while causing minimum performance degradation.

### **Coffing and Brown**

Coffing and Brown [Coffing97] augmented the Linux filesystem to support automatic compression of files with gzip. Their system is based on that of Cate and Gross, but uses different compression policies. First, they divide files into separate units and have the ability to compress each unit independently. This improves random access time to large files. When part of a file is accessed, the remaining units are speculatively decompressed assuming that the user will want access to other sections of the file. Very large files are never fully decompressed to avoid filling the disk. Small files whose compression may not save at least one disk block are not compressed. One interesting problem the authors found

was that file fragmentation increased significantly as files were decompressed and recompressed.

#### **Compression cache**

Compression has also been used to improve virtual memory management. Douglis [Douglis93] modified the Sprite operating system to compress pages of memory with the LZRW1 algorithm [Williams91]. Before pages are written to backing store (disk), they are first compressed and kept in a *compression cache*. The compression cache is a new level in the virtual memory hierarchy between memory and disk. When the compression cache is full, some compressed pages are written to backing store. In some cases, it allows the working set of a program to remain entirely in main memory and use backing store. When the working set it much larger than available memory, compression reduces the I/O to backing store. Douglis found that applications had speedups ranging from 0.73 to 2.68. Some benchmarks had slowdowns because 1) the number of incompressible pages was very high so that the time taken to compress and decompress did not offset the I/O time, and 3) the benchmarks had non-sequential data access patterns which did not allow the cost of compression and decompression to be amortized over many data accesses.

# 2.6 Compiler optimizations for compression

Data compression works by taking advantage of predictability (repetition) in the data stream. The compiler can therefore improve the compressibility of a program by generating code that is more regular and repetitious. Two techniques for accomplishing this are *procedure abstraction* and *register renaming*.

### **2.6.1 Procedure abstraction**

Procedure abstraction [Standish76] is a program optimization for procedure oriented languages that replaces repeated sequences of common code with function calls to a single function that performs the required computation. Figure 2.8 shows an example of procedure abstraction with a high-level language. Compilers can apply procedure abstraction on an intermediate representation or native instructions. Sequences of code that are

#### Figure 2.8: Procedure abstraction

Procedure abstraction is an optimization to reduce code size. The sections of code in procedure F are generalized to form procedure G. Procedure F is re-written to call G.

identical, except for the values used, can be bound to the same abstracted function and supplied with arguments for the appropriate values.

#### Kunchithapadam and Larus

Kunchithapadam and Larus apply procedure abstraction at the level of native instructions by rewriting binary executables [Kunchit99]. They combined this optimization with procedure layout so that the abstracted procedures were adjacent in memory to the function that calls them the most. They find this optimization yields most of its benefit when applied to straightline sequences of instructions. Using larger sequences that included some control-flow only marginally improved their results. For many programs, they found that code size decreased up to 5% and performance improved between 3-9%. However, in some instances, they found that performance could decrease 5-27% which suggests that the effect of procedure abstraction on cache performance needs more study.

#### **Mini-subroutines**

Liao et al. propose a software method for supporting compressed code [Liao95, Liao96]. They find *mini-subroutines* which are common sequences of instructions in the program. Each instance of a mini-subroutine is removed from the program and replaced

|    |       |            |    |        |            | _ |    |         |

|----|-------|------------|----|--------|------------|---|----|---------|

| F: | lbz   | r9,0(r28)  | G: | lbz    | r9,0(r28)  |   | G: | G: lbz  |

|    | multi | r11,r9,24  |    | multi  | r11,r9,24  |   |    | multi   |

|    | addi  | r0,r11,1   |    | addi   | r0,r11,1   |   |    | addi    |

|    | cmpli | cr1,0,r0,8 |    | cmpli  | cr1,0,r0,8 |   |    | cmpli   |

|    | ble   | cr1,+64    |    | return |            |   |    |         |

|    | lbz   | r9,0(r28)  |    |        |            |   |    |         |

|    | multi | r11,r9,24  | F: | call   | G          |   | F: | F: call |

|    | addi  | r0,r11,1   |    | ble    | cr1,+64    |   |    | ble     |

|    | cmpli | cr1,0,r0,8 |    | call   | G          |   |    | call    |

# Original (9 instructions)

Mini-subroutine (8 instructions)

Call-dictionary (7 instructions)

#### Figure 2.9: Mini-subroutines

with a call instruction. The mini-subroutine is placed once in the text of the program and ends with a return instruction. Mini-subroutines are not constrained to basic blocks and may contain branch instructions under restricted conditions. The prime advantage of this compression method is that it requires no hardware support. However, the subroutine call overhead will slow program execution. This method is similar to procedure abstraction at the level of native instructions, but without the use of procedure arguments.

A hardware modification is proposed to support code compression consisting primarily of a *call-dictionary* instruction. This instruction takes two arguments: *location* and *length*. Common instruction sequences in the program are saved in a dictionary, and the sequence is replaced in the program with the *call-dictionary* instruction. During execution, the processor jumps to the point in the dictionary indicated by *location* and executes *length* instructions before implicitly returning. The advantage of this method over the purely software approach is that it eliminates the return instruction from the mini-subroutine. However, it also limits the dictionary to sequences of instructions within basic blocks.

Figure 2.9 compares the mini-subroutine and call-dictionary methods. A potential problem with these compression methods are that they introduce many branch instructions into a program, thus reducing overall performance. The authors report a 88% compression ratio for the mini-subroutine method and an 84% compression ratio for the call-dictionary method. Their compression results are based on benchmarks compiled for the Texas Instruments TMS320C25 DSP.

## 2.6.2 Register renaming

Typically, very few opcodes are used by compilers to generate code. Inspite of this, instructions usually differ from one another due to using different register names in their register fields. Register renaming can improve repetition in the program by renaming the registers of an instruction so that it matches another instruction in the program whenever possible. This increases the number of instructions in the program that are identical and allow the compressor to make use of the repetition.

#### **Cooper and McIntosh**

Cooper and McIntosh [Cooper99] use register renaming to increase opportunities to apply procedure abstraction and cross-jumping [Wulf75]. They search the entire executable binary for sequences of instructions (possibly spanning several basic blocks) that have similar data-flow and control-flow. They then attempt to make the sequences identical by renaming registers in the live ranges that flow through the sequences. Once the sequences are identical, then procedure abstraction or cross-jumping is applied. They report a 5% average code size reduction and 6% average decrease in dynamic instructions when their code reduction optimizations are applied to optimized programs.

### Debray et al.

Debray et al. [Debray99] also combine the techniques of procedure abstraction and register renaming in a binary-rewriting tool. The primary difference is that they use basic blocks, rather than live ranges as the unit of renaming registers. They find basic blocks with matching data-flow graphs and attempt to rename the registers within the basic blocks so that the instructions match. Register move instructions are sometimes inserted before and after the basic blocks to enable renaming. They look at the control-flow between basic blocks so that blocks can be combined into larger units of abstraction. If possible, identical blocks are moved into dominating, or post-dominating blocks to remove copies. Otherwise, the identical basic blocks are then used as candidates for procedure abstraction. Blocks of instructions in the function prologue and epilogue that save and restore registers are treated specially. These are abstracted into procedures. However, the entry point into the abstracted prologue and epilogue changes depending on what registers the caller needs to save and restore. The authors report a compression ratio ranging

from 73% to 81% for Alpha executables produced with gcc 2.7.2.2 with "-O2" optimization (no loop-unrolling and no inlining). They also report performance increases of up to 18% and decreases of up to 28%.

# **2.7 Conclusion**

It is clear that there are many opportunities on several levels to reduce the size of programs. However, it is difficult to compare the results of the research efforts to date. Each study uses a different compiler, instruction set, and compiler optimizations. It is not meaningful to say that a program was compressed 20% or 50% without knowing what standard this was measured against. Poorly written programs with no optimization may compress very well because they are full of unnecessary repetition while programs that already have an efficient encoding will seem not to compress very well. The value of the techniques presented here is that they represent a range of solutions to program representation. These techniques are not mutually exclusive – it is possible to combine them since they take advantage of different levels of representation.

# Chapter 3 Instruction-level compression

In this chapter, we present a study that examines the feasibility of compressing programs at the instruction-level. The results of this study show that ordinary programs contain repetition at the instruction level that can be readily compressed. Programs are compressed with a post-compilation analyzer that examines program object code and replaces common sequences of instructions with a single codeword. A compression-aware microprocessor could execute the compressed instruction sequences by fetching codewords from the instruction memory, expanding them back to the original sequence of instructions in the decode stage, and issuing them to the execution stages. We demonstrate our technique by applying it to the PowerPC, ARM, i386, and MIPS-16 instruction sets.

# **3.1 Introduction**

This chapter studies a compression method similar to the *call-dictionary* scheme [Liao95]. Common sequences of native instructions in object code are replaced with codewords. We extend this work by considering the advantages from using smaller instruction (codeword) sizes. Liao considers the *call-dictionary* instruction to be the size of one or two instruction words. This requires the dictionary to contain sequences with at least two or three instructions, respectively, since shorter sequences would be no bigger than the *call-dictionary* instruction and no compression would result. This method misses an important compression opportunity. We will show that there is a significant advantage for compressing patterns consisting of only one instruction.

Liao et al. do not explore the trade-off of the field widths for the *location* and *length* arguments in the *call-dictionary* instruction. We vary the parameters of *dictionary size* (the number of entries in the dictionary) and the *dictionary entry length* (the number

of instructions at each dictionary entry) thus allowing us to examine the efficacy of compressing instruction sequences of any length.

This chapter is organized as follows. First, the compression method is described. Second, the experimental results are presented. This chapter ends with conclusions about the compression method and proposals for how it might be improved.

# 3.2 Overview of compression method

The compression method finds sequences of instructions (some of length one) that are frequently repeated throughout a single program and replaces the entire sequence with a single codeword. All rewritten (or encoded) sequences of instructions are kept in a dictionary which, in turn, is used at program execution time to expand the singleton codewords in the instruction stream back into the original sequence of instructions. Codewords assigned by the compression algorithm are indices into the instruction dictionary.

The final compressed program consists of codewords interspersed with uncompressed instructions. Figure 3.1 illustrates the relationship between the uncompressed code, the compressed code, and the dictionary. A complete description of our compression method is presented in Chapter 3.

# 3.2.1 Algorithm

The compression method is based on the technique introduced in [Bird96, Chen97b]. A dictionary compression algorithm is applied after the compiler has generated the program. We search the program object modules to find common sequences of instructions to place in the dictionary. The algorithm has three parts:

- 1. Building the dictionary

- 2. Replacing instruction sequences with codewords

- 3. Encoding codewords

### **Building the dictionary**

For an arbitrary text, choosing those entries of a dictionary that achieve maximum compression is NP-complete in the size of the text [Storer77]. As with most dictionary methods, we use a greedy algorithm to quickly determine the dictionary entries. On every

iteration of the algorithm, we examine each potential dictionary entry and find the one that results in the largest immediate savings. The algorithm continues to pick dictionary entries until some termination criteria has been reached; this is usually the exhaustion of the codeword space. The maximum number of dictionary entries is determined by the choice of the encoding scheme for the codewords. Obviously, codewords with more bits can index a larger range of dictionary entries. We limit the dictionary entries to sequences of instructions within a basic block. We allow branch instructions to branch to codewords, but they may not branch within encoded sequences. We also do not compress branches with offset fields. These restrictions simplify code generation.

### **Replacing instruction sequences with codewords**

Our greedy algorithm combines the step of building the dictionary with the step of replacing instruction sequences. As each dictionary entry is defined, all of its instances in the program are replaced with a token. This token is replaced with an efficient encoding in the encoding step.

### **Encoding codewords**

*Encoding* refers the process of converting tokens to the actual representation of the codewords in the compressed program. Variable-length codewords, (such as those used in the Huffman encoding) are expensive to decode. A fixed-length codeword, on the other hand, can be used directly as an index into the dictionary making decoding a simple table lookup operation.

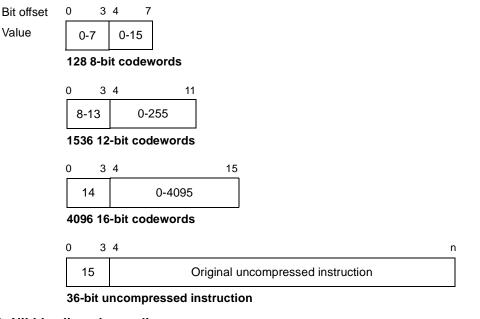

The baseline compression method uses a fixed-length codeword to enable fast decoding. We also investigate a variable-length scheme. However, we restrict the variable-length codewords to be a multiple of some basic unit. For example, we present a compression scheme with 8-bit, 12-bit, and 16-bit codewords. All instructions (compressed and uncompressed) are aligned on 4-bit boundaries. This achieves better compression than a fixed-length encoding, but complicates decoding.

### **3.2.2 Related issues**

### **Branch instructions**

One obvious side effect of a compression scheme is that it alters the locations of instructions in the program. This presents a special problem for branch instructions, since branch targets change as a result of program compression.

To avoid this problem, we do not compress relative branch instructions (i.e. those containing an offset field used to compute a branch target). This makes it easy for us to patch the offset fields of the branch instruction after compression. If we allowed compression of relative branches, we might need to rewrite codewords representing relative branches after a compression pass; but this would affect relative branch targets thus requiring a rewrite of codewords, etc. The result is again an NP-complete problem [Szymanski78].

Indirect branches are compressed in our study. Since these branches take their target from a register, the branch instruction itself does not need to be patched after compression, so it cannot create the codeword rewriting problem outlined above. However, jump tables (containing program addresses) need to be patched to reflect any address changes due to compression.

### **Branch targets**

Instruction sets restrict branches to use targets that are aligned to instruction word boundaries. Since our primary concern is code size, we trade-off the performance advantages of these aligned instructions in exchange for more compact code. We use codewords that are smaller than instruction words and align them on 4-bit boundaries. Therefore, we need to specify a method to address branch targets that do not fall at the original instruction word boundaries.

One solution is to pad the compressed program so that all branch targets are aligned as defined by the original ISA. The obvious disadvantage of this solution is that it will increase program size.

A more complex solution (the one we have adopted for our experiments) is to modify the control unit of the processor to treat the branch offsets as aligned to the size of the codewords. The post-compilation compressor modifies all branch offsets to use this alignment.

One of our compression schemes requires that branch targets align to 4-bit boundaries. In PowerPC and ARM, branch targets align to 32-bit boundaries. Since branches in the compressed program specify a target aligned to a 4-bit boundary, the target could be in any one of eight positions within the original 32-bit boundary. We use 3 bits in the branch offset to specify the location of the branch target within the usual 32-bit alignment. Overall, the range of the offset is reduced by a factor of 8. In our benchmarks, less than 1% of the branches with offsets had a target outside of this reduced range. Branch targets in i386 align to 8-bit boundaries. We use 1 bit in the offset to specify the 4-bit alignment of the compressed instruction within the usual 8-bit alignment. This reduces the range of branch offsets by a factor of two. In our benchmarks, less than 2.2% of the branch offsets were outside this reduced range. Branches requiring larger ranges are modified to load their targets through jump tables. Of course, this will result in a slight increase in the code size for these branch sequences.

Figure 3.2: Compressed program processor

### 3.2.3 Compressed program processor