### ABSTRACT

### SOFTWARE-ORIENTED MEMORY-MANAGEMENT DESIGN

by

#### **Bruce Ledley Jacob**

Chair: Trevor N. Mudge

Changing trends in technologies, notably cheaper and faster memory hierarchies, have made it worthwhile to revisit many hardware-oriented design decisions made in previous decades. Hardware-oriented designs, in which one uses special-purpose hardware to perform some dedicated function, are a response to a high cost of executing instructions out of memory; when caches are expensive, slow, and/or in scarce supply, it is a perfectly reasonable reaction to build hardware state machines that do not compete with user applications for cache space and do not rely on the performance of the caches. In contrast, when the caches are large enough to withstand competition between the application and operating system, the cost of executing operating system functions out of the memory subsystem decreases significantly, and software-oriented designs become viable. Software-oriented designs, in which one dispenses with special-purpose hardware and instead performs the same function entirely in software, offer dramatically increased flexibility over hardware state machines at a modest cost in performance.

This dissertation explores a software-oriented design for a virtual memory management system. It shows not only that a software design is more flexible than hardware designs, but that a software scheme can perform as well as most hardware schemes. Eliminating dedicated special-purpose hardware from processor design saves chip area and reduces power consumption, thus lowering the overall system cost. Moreover, a flexible design aids in the portability of system software. A software-oriented design methodology should therefore benefit architects of many different microprocessor designs, from general-purpose processors in PC-class and workstation-class computers, to embedded processors where cost tends to have a higher priority than performance. The particular implementation described in the following chapters, which is centered around a virtual cache hierarchy managed by the operating system, is shown to be useful for real-time systems, shared-memory multiprocessors, and architecture emulation.

# SOFTWARE-ORIENTED

# **MEMORY-MANAGEMENT DESIGN**

by

**Bruce Ledley Jacob**

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in the University of Michigan 1997

**Doctoral Committee:**

Professor Trevor Mudge, Chair Adjunct Assistant Professor Charles Antonelli Professor Richard Brown Assistant Professor Peter Chen Associate Professor Farnam Jahanian

This book is merely a personal narrative, and not a pretentious history or a philosophical dissertation. It is a record of several years of variegated vagabondizing, and its object is rather to help the resting reader while away an idle hour than afflict him with metaphysics, or goad him with science.

Still, there is quite a good deal of information in the book. I regret this very much; but really it could not be helped: information appears to stew out of me naturally, like the precious ottar of roses out of the otter. Sometimes it has seemed that I would give worlds if I could retain my facts; but it cannot be. The more I caulk up the sources, and the tighter I get, the more I leak wisdom. Therefore, I can only claim indulgence at the hands of the reader, not justification.

Excerpted from Prefatory, *Roughing It* — Mark Twain

Bruce Ledley Jacob

©

All Rights Reserved

- 1997

For my Family

(my family, my family-in-law, and most especially my truly adorable wife)

# ACKNOWLEDGMENTS

Thanks to the members of my thesis committee, who have given me good advice and perspective over the last few years in the classroom, at informal hallway meetings, and at various local restaurants. Thanks especially to my thesis chair, whose dogged question-asking indirectly unearthed much found herein.

#### PREFACE

In the fall of 1995 we began a project to build a 1GHz PowerPC processor in gallium arsenide (GaAs); my duties included the design of the memory management system, both software and hardware. The problem to solve initially was threefold:

- 1. Reduce transistor count

- 2. Reduce complexity

- 3. Increase performance

These could be restated as:

- 1. Make it *small*

- 2. Make it *simple*

- 3. Make it *fast*

These goals may appear over-simplistic; I believe that they are not. What is not immediately obvious is that they are in order of priority, and that when viewed as requirements and not simply good engineering advice, they define a clear path to achieving our performance goals. To explain their rationale: if we could not make our design small, we would almost certainly not be able to build it at all—GaAs does not allow one the luxury of a large design. If it could not be made simple, we would probably not be able to debug it. If it could not be made fast, we would lose face but the design would still work. Therefore, we considered it worthwhile to sacrifice a small amount of performance if doing so would make the design smaller or simpler.

One maxim that can be drawn from these requirements is: *whenever it is possible to implement a given function in software it is worthwhile to do so, unless the performance cost of doing so is prohibitive.* The thesis work presented in this dissertation is the result of investigating the validity and implications of that maxim in the domain of memory management.

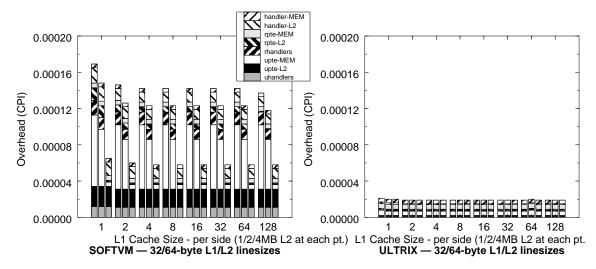

The memory-management design that adheres to this maxim is a software-oriented one. A software-oriented design is one in which the designer eliminates a piece of special-purpose hard-ware that performs some dedicated function and instead performs the same function entirely in software. For instance, the *translation lookaside buffer (TLB)* is a specialized hardware structure

that performs a dedicated function; it provides protection and address translation for physically indexed or physically tagged caches. It is not needed if one uses virtually addressed caches (except for the protection function, which can be ignored or supported by keeping protection information in each cache line). We eliminated the traditional TLB structure and replaced it with virtually indexed, virtually tagged caches that are managed by the operating system—in such a scheme, address translation is performed not in hardware but entirely in software by system-level software routines.

A hardware-oriented PowerPC memory-management architecture has essentially three TLBs: the segment registers, the traditional page-oriented TLB, and the superpage-oriented BAT registers (*Block-Address Translation*). The segment registers are required to implement the PowerPC's segmented address space. With a software-oriented design, we were able to eliminate the remaining two TLB structures at virtually no performance cost.

Once our investigations showed the scheme to be viable (its performance is roughly that of a system with a TLB), it occurred to us that we had designed a system that could potentially compete in performance with any memory-management scheme, but which offered dramatically increased flexibility over traditional designs. Thus, this memory-management organization might be useful even if one is not building a processor in a resource-poor technology such as GaAs. This dissertation explores the possibilities for such a design, comparing the performance and physical requirements (e.g. chip area) of a hardware-oriented scheme against the requirements of a software-oriented one. We discuss the flexibility of a software-oriented design and, briefly, its benefits for multiprocessor systems, real-time systems, architecture emulation, and reconfigurable computing.

# TABLE OF CONTENTS

| DEDICATION i                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------|

| ACKNOWLEDGMENTS ii                                                                                                         |

| PREFACE iv                                                                                                                 |

| TABLE OF CONTENTS v                                                                                                        |

| LIST OF FIGURES x                                                                                                          |

| LIST OF TABLES xv                                                                                                          |

| CHAPTER 1                                                                                                                  |

| INTRODUCTION: VIRTUAL MEMORY,<br>THREE DECADES LATER                                                                       |

| 1.1Motivation11.2Background and Previous Work in Memory Management Design51.3Dissertation Overview71.4Scope of the Thesis5 |

| CHAPTER 2                                                                                                                  |

| A VIRTUAL MEMORY PRIMER 10                                                                                                 |

| <ul> <li>2.1 Introduction</li></ul>                                                                                        |

| 2.2.4 Further Memory-Management Research                                                                                   |

| 2.3.1 Hierarchical Page Tables                                                                                             |

| MEMORY MANAGEMENT HARDWARE AND ITS            |    |

|-----------------------------------------------|----|

| SUPPORT FOR OPERATING SYSTEMS FUNCTIONS       | 36 |

| 3.1 Introduction                              | 36 |

| 3.2 Operating System Requirements             | 37 |

| 3.2.1 Address Space Protection                |    |

| 3.2.2 Shared Memory                           |    |

| 3.2.3 Large Address Spaces                    | 38 |

| 3.2.4 Fine-Grained Protection                 |    |

| 3.2.5 Sparse Address Spaces                   | 38 |

| 3.2.6 Superpages                              | 39 |

| 3.2.7 Direct Memory Access                    | 39 |

| 3.3 Memory Management Units                   | 40 |

| 3.3.1 MIPS                                    | 40 |

| 3.3.2 Alpha                                   | 43 |

| 3.3.3 PowerPC                                 | 44 |

| 3.3.4 PA-RISC 2.0                             | 46 |

| 3.3.5 SPARC V9                                | 48 |

| 3.3.6 Pentium Pro                             | 50 |

| 3.3.7 SPUR                                    | 53 |

| 3.3.8 SOFTVM                                  | 54 |

| 3.4 A Taxonomy of Address Space Organizations | 55 |

| 3.4.1 Single-Owner, No ID (SONI)              |    |

| 3.4.2 Single-Owner, Single-ID (SOSI)          |    |

| 3.4.3 Single-Owner, Multiple-ID (SOMI)        | 60 |

| 3.4.4 Multiple-Owner, No ID (MONI)            |    |

| 3.4.5 Multiple-Owner, Single-ID (MOSI)        | 61 |

| 3.4.6 Multiple-Owner, Multiple-ID (MOMI)      |    |

| 3.5 Conclusions                               | 62 |

|                                               |    |

| EXPERIMENTAL METHODOLOGY                 | 64 |

|------------------------------------------|----|

| 4.1 Introduction                         | 64 |

| 4.2 PUMAmm: Memory Management Simulation | 65 |

| 4.2.1 SOFTVM Virtual Memory              | 67 |

| 4.2.2 Ultrix/MIPS Virtual Memory         | 68 |

| 4.2.3 Mach/MIPS Virtual Memory           | 69 |

| 4.2.4 BSD/Intel Virtual Memory           | 70 |

| 4.2.5 PA-RISC Virtual Memory             | 72 |

| 4.3 Benchmark Measurements               | 73 |

| 4.3.1 Setup on PowerPC                   | 77 |

| 4.3.2 Setup on Alpha                     |    |

| 4.4 Conclusions                          | 77 |

|                                          |    |

| SOFTWARE-MANAGED ADDRESS TRANSLATION                        | 78 |

|-------------------------------------------------------------|----|

| 5.1 Introduction                                            | 78 |

| 5.2 Background and Previous Work                            | 80 |

| 5.2.1 Problems with Virtual Caches                          | 80 |

| 5.2.2 Segmented Translation                                 | 81 |

| 5.2.3 MIPS: A Simple 32-bit Page Table Design               |    |

| 5.2.4 SPUR: In-Cache Address Translation                    |    |

| 5.2.5 VMP: Software-Controlled Caches                       | 83 |

| 5.3 Software-Managed Address Translation                    | 83 |

| 5.3.1 Handling the Cache-Miss Exception                     |    |

| 5.3.2 An Example of softvm and Its Use                      |    |

| 5.3.3 Memory System Requirements, Revisited                 |    |

| 5.4 Discussion                                              |    |

| 5.4.1 Performance Overview                                  | 90 |

| 5.4.2 Baseline Overhead                                     |    |

| 5.4.3 Writebacks                                            |    |

| 5.4.4 Fine-Grained Protection                               |    |

| 5.4.5 Sensitivity to Cache Organization—Preliminary Results |    |

| 5.5 Conclusions                                             |    |

|                                                             |    |

| 99  |

|-----|

| 100 |

| 106 |

| 115 |

| 126 |

| 126 |

| 134 |

| 135 |

|     |

| 144 |

| 146 |

|     |

| 179 |

| 179 |

| 181 |

| 182 |

| 182 |

| 183 |

|     |

| 6.7.1 Large (e.g. 64-bit) Addressing Schemes         | 183 |

|------------------------------------------------------|-----|

| 6.7.2 Single Address Space Operating Systems         | 183 |

| 6.8 Compatibility with Different Cache Organizations | 185 |

| 6.8.1 Write-Back Caches                              | 185 |

| 6.8.2 Write-Through Caches                           | 185 |

| 6.9 Conclusions                                      | 186 |

| 6.9.1 Performance Recapitulation                     | 186 |

| 6.9.2 The Good News                                  | 188 |

| 6.9.3 The Bad News                                   | 188 |

# THE PROBLEMS WITH VIRTUAL CACHES 7.2 ..... Background and Perspective ...... 190 7.2.3 ... The Consistency Problem of Virtual Caches ...... 194 7.3 ..... Shared Memory vs. the Virtual Cache ...... 197 7.3.1 ... The Problems with Virtual-Address Aliasing ...... 197 7.3.2 ... The Problems with Address-Space Identifiers ...... 199

| THE PROBLEMS WITH INTERRUPTS               |                                  |

|--------------------------------------------|----------------------------------|

| AND A SOLUTION BY REDEFINING THEI          | R PRECISION 211                  |

|                                            |                                  |

| 8.1 Introduction                           |                                  |

| 8.2 Precise Interrupts and Pipelined Proce | ssors                            |

| 8.3 Relaxed-Precision Interrupts           |                                  |

| 8.3.1 Definition                           |                                  |

| 8.3.2 A Model for Relaxed-Precisio         | on Interrupts 218                |

| 8.3.3 The Performance Benefits of          | Relaxed-Precision Interrupts 229 |

| 8.4 Conclusions                            |                                  |

|                                            |                                  |

| TH      | E PROBLEMS WITH MULTIMEDIA SUPPORT    |     |

|---------|---------------------------------------|-----|

| AN      | D A SOLUTION USING SEGMENTATION       | 235 |

| 9.1     | Introduction                          | 235 |

|         | Superpage Support                     |     |

|         | Performance Measurements              |     |

|         | Conclusions                           |     |

| 9.4     | Conclusions                           | 241 |

| CHAPTER | 10                                    |     |

|         |                                       |     |

| TH      | E PROBLEMS WITH LARGE OFF-CHIP CACHES |     |

| AN      | D A SOLUTION USING PHYSICAL MEMORY    | 242 |

|         |                                       |     |

| 10.1    | 1 Introduction                        | 242 |

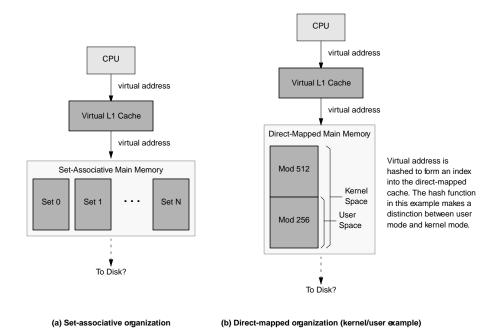

| 10.2    | 2 Main Memory as a Virtual Cache      | 243 |

|         | 10.2.1 . Fully Associative Designs    | 246 |

|         | 10.2.2 . Set-Associative Designs      | 247 |

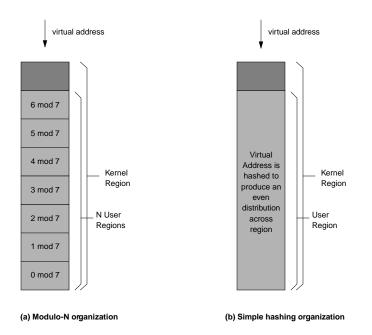

|         | 10.2.3 . Direct-Mapped Designs        | 247 |

| 10.3    | 3 Experiments                         | 248 |

| 10.4    | 4 Conclusions                         | 249 |

|         |                                       |     |

| CHAPTER | 11                                    |     |

|         |                                       |     |

| 00      | NCLUSIONS                             | 250 |

| APPENDIX     | <br>255 |

|--------------|---------|

|              |         |

| BIBLIOGRAPHY | <br>262 |

# LIST OF FIGURES

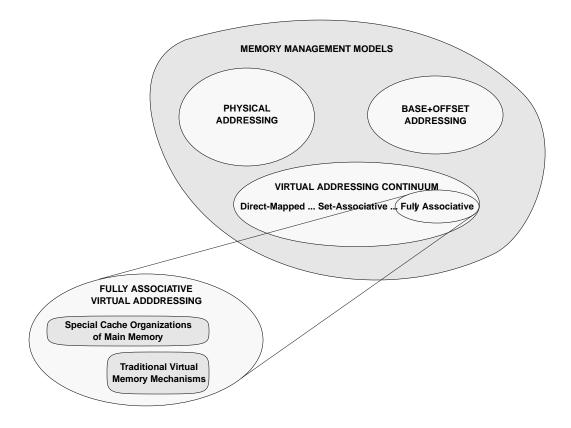

| Figure 2.1:  | Memory management models 11                                           |

|--------------|-----------------------------------------------------------------------|

| Figure 2.2:  | The Physical Addressing model of program creation and execution 12    |

| Figure 2.3:  | The Base+Offset Addressing model of program creation and execution 12 |

| Figure 2.4:  | The Virtual Addressing model of program creation and execution        |

| Figure 2.5:  | Comparison of the three models                                        |

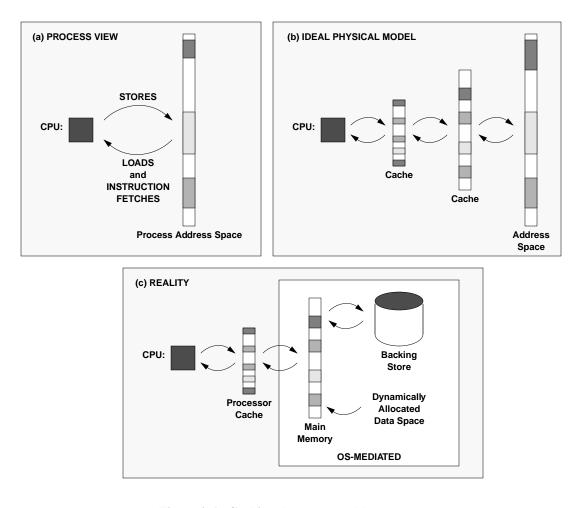

| Figure 2.6:  | Caching the process address space                                     |

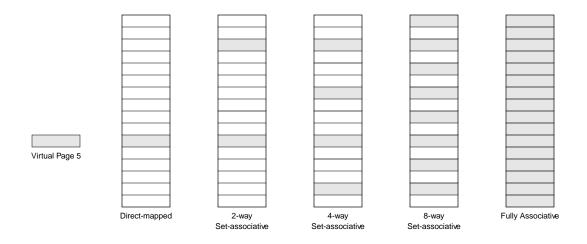

| Figure 2.7:  | Associative organizations of main memory                              |

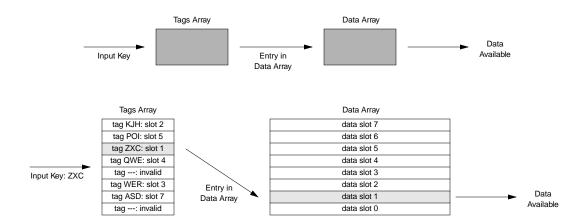

| Figure 2.8:  | An idealized fully associative cache lookup                           |

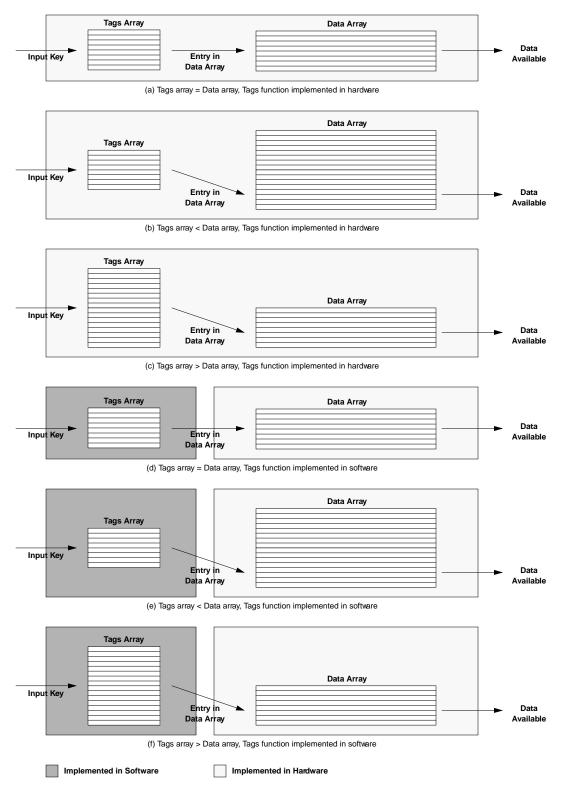

| Figure 2.9:  | Alternative designs for associative cache lookup                      |

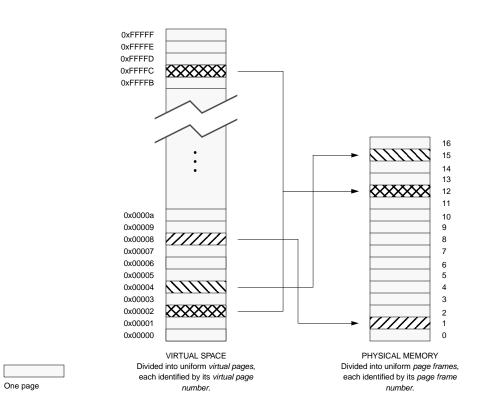

| Figure 2.10: | Mapping virtual pages into physical page frames                       |

| Figure 2.11: | A logical Page Table Entry                                            |

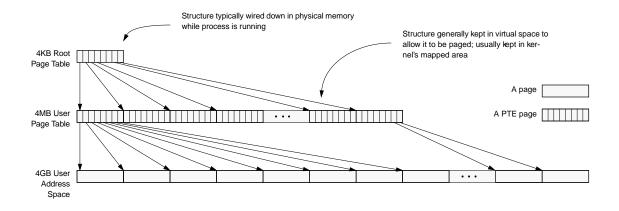

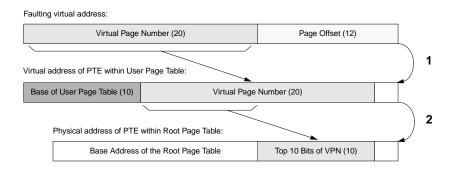

| Figure 2.12: | Classical two-level hierarchical page table                           |

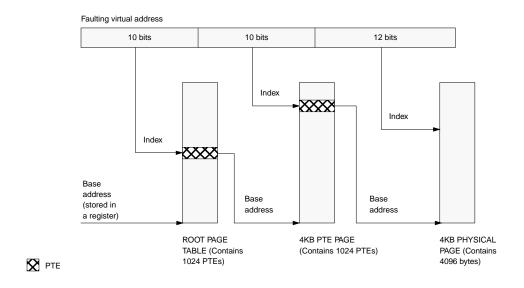

| Figure 2.13: | Top-down access method for hierarchical page table                    |

| Figure 2.14: | Bottom-up algorithm for hierarchical page table                       |

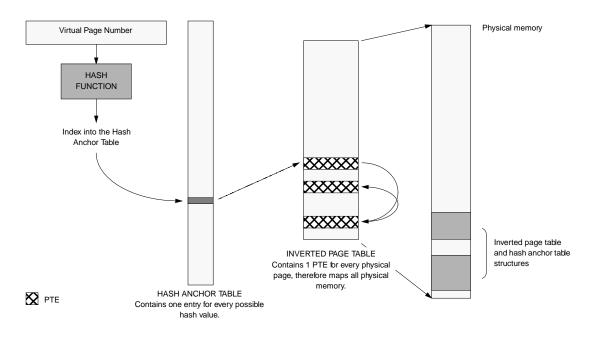

| Figure 2.15: | Classical inverted page table structure                               |

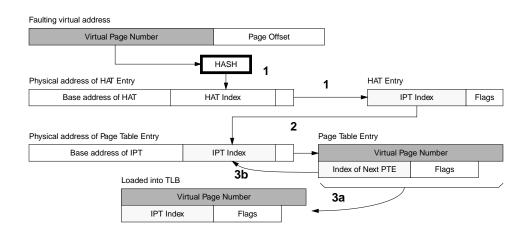

| Figure 2.16: | Lookup algorithm for inverted page table                              |

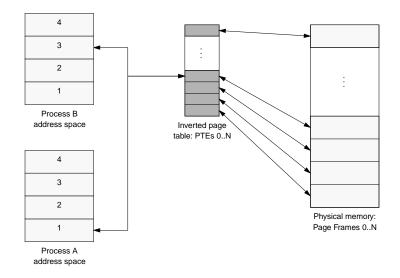

| Figure 2.17: | Inverted page table and shared memory                                 |

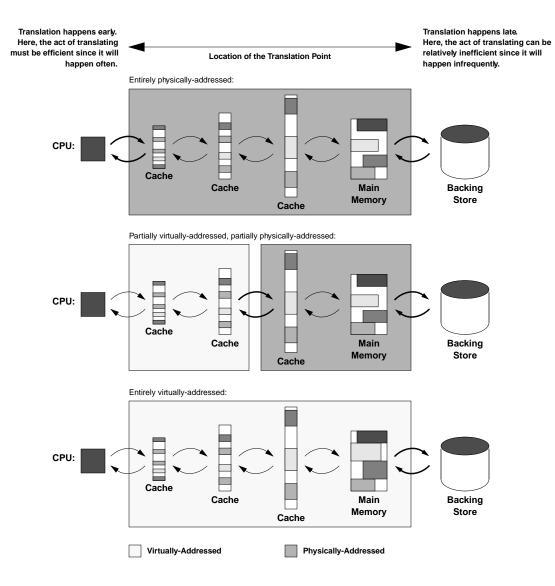

| Figure 2.18: | Possible locations of the translation point                           |

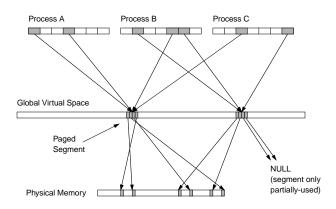

| Figure 3.1:  | Sparse address spaces                                                 |

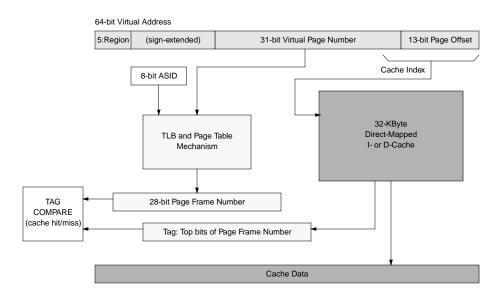

| Figure 3.2:  | The MIPS R10000 address translation mechanism                         |

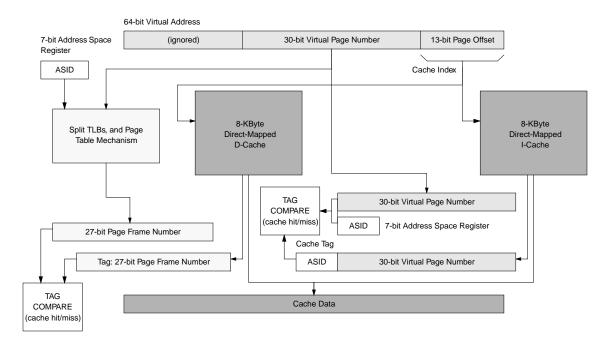

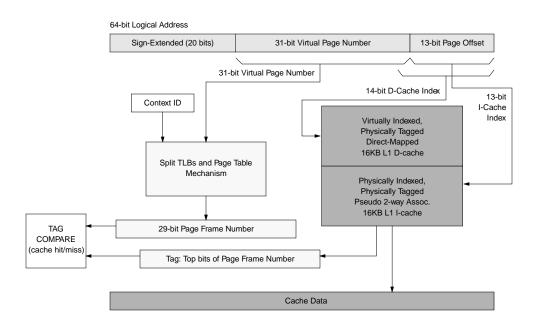

| Figure 3.3:  | The Alpha 21164 address translation mechanism                         |

| Figure 3.4:  | The PowerPC 604 address translation mechanism                         |

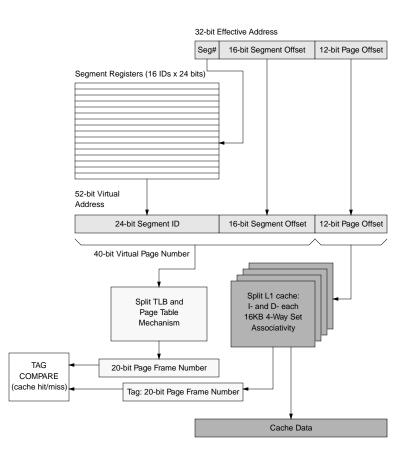

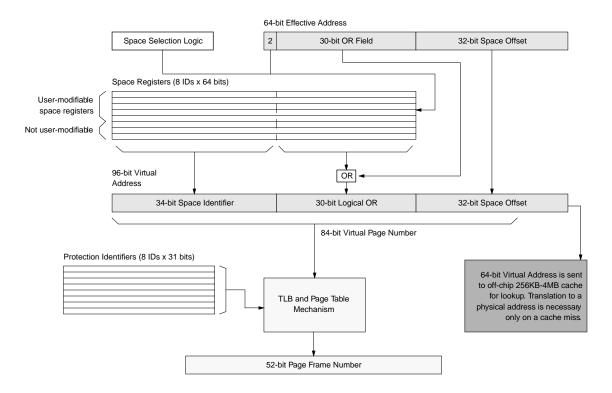

| Figure 3.5:  | The PA-8000 address translation mechanism                             |

| Figure 3.6:  | The UltraSPARC address translation mechanism                          |

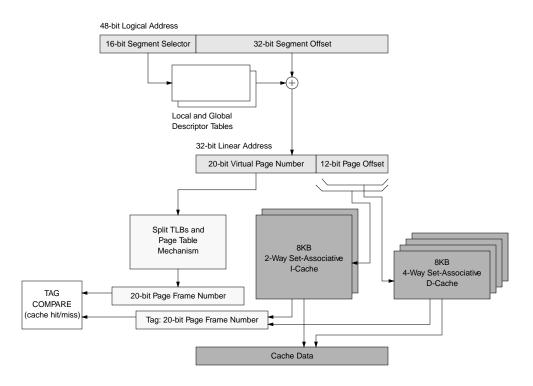

| Figure 3.7:  | The Pentium Pro address translation mechanism                         |

| Figure 3.8:  | The SPUR address translation mechanism                                |

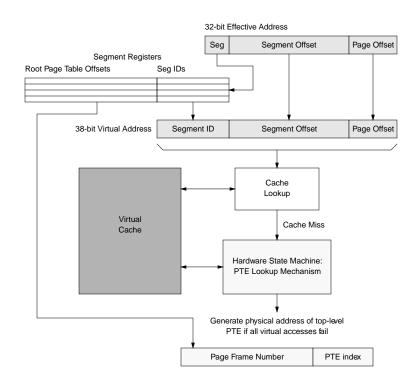

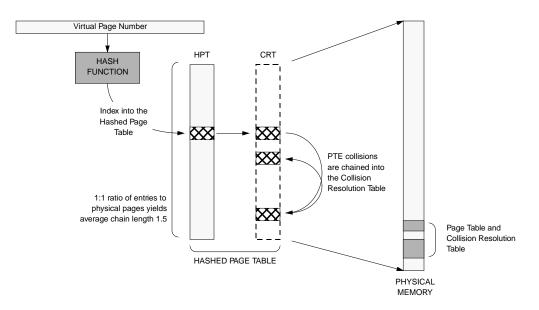

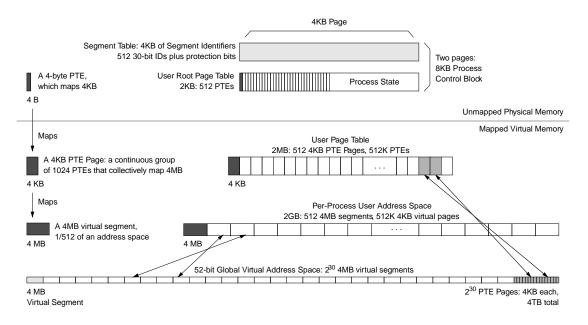

| Figure 3.9:  | The SOFTVM address translation mechanism                                         |

|--------------|----------------------------------------------------------------------------------|

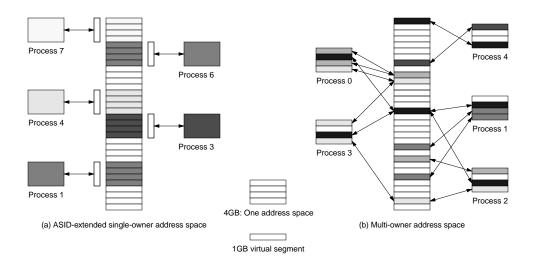

| Figure 3.10: | The difference between ASIDs and a multiple-owner address space                  |

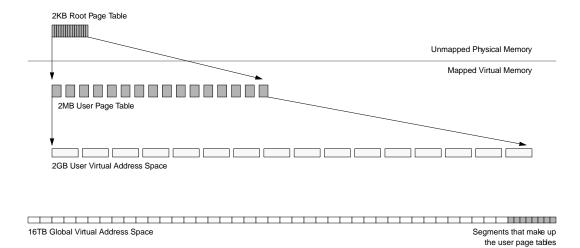

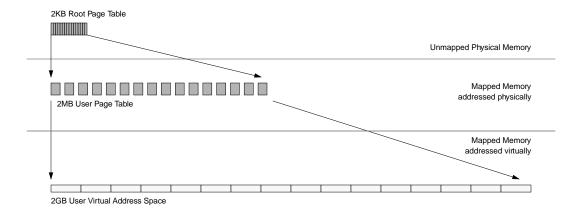

| Figure 4.1:  | The SOFTVM page table organization                                               |

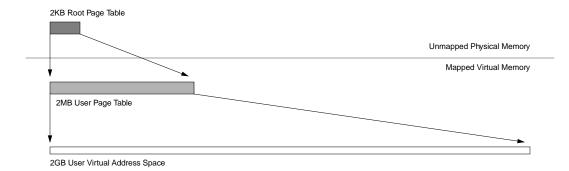

| Figure 4.2:  | The Ultrix/MIPS page table organization                                          |

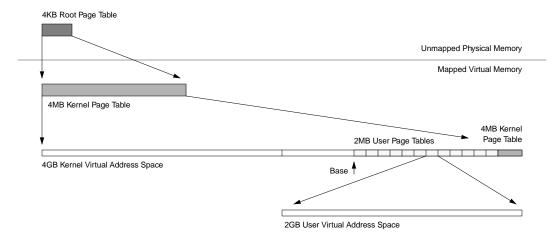

| Figure 4.3:  | The Mach/MIPS page table organization 70                                         |

| Figure 4.4:  | The BSD/Intel page table organization 71                                         |

| Figure 4.5:  | The PA-RISC page table organization                                              |

| Figure 5.1:  | The MIPS 32-bit hierarchical page table                                          |

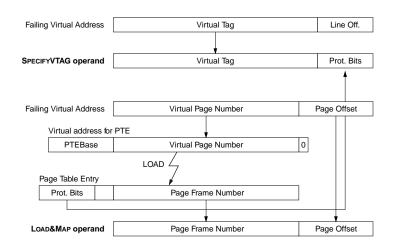

| Figure 5.2:  | SpecifyVTAG and Load⤅ 85                                                         |

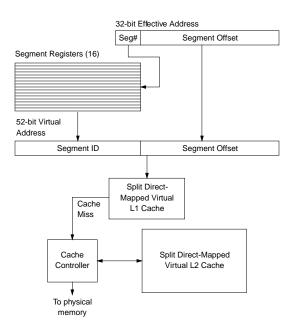

| Figure 5.3:  | The example address translation mechanism                                        |

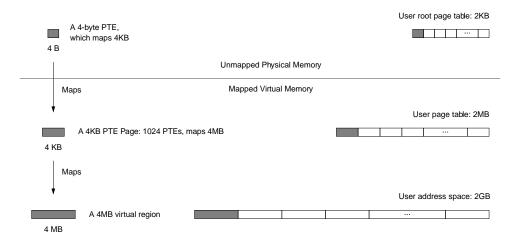

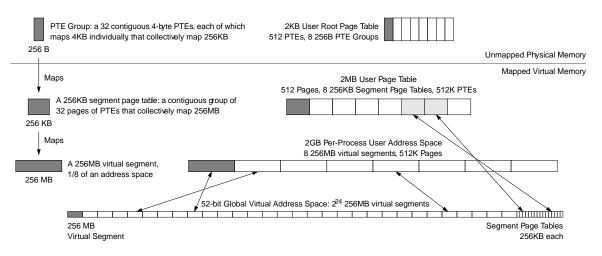

| Figure 5.4:  | An example page table organization                                               |

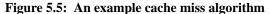

| Figure 5.5:  | An example cache miss algorithm                                                  |

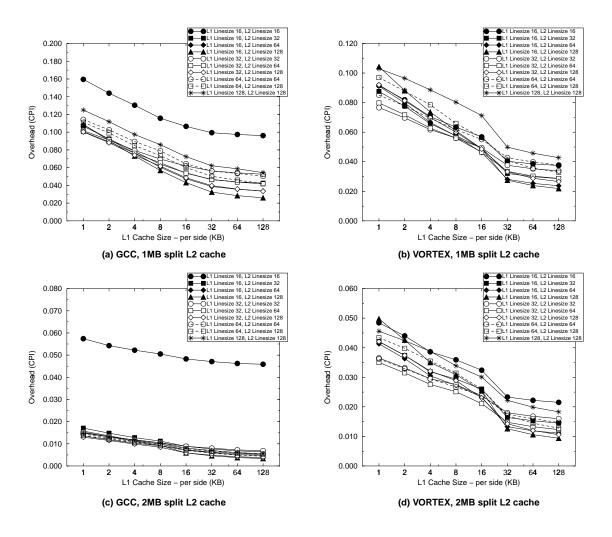

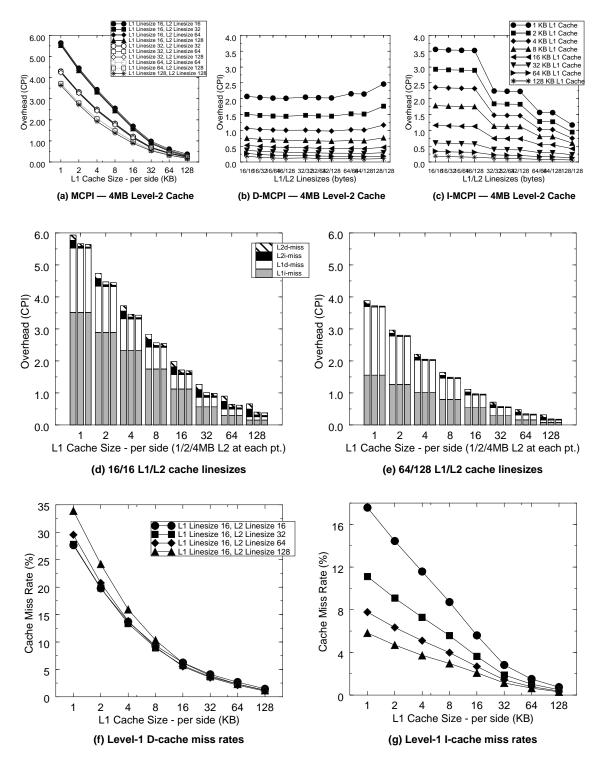

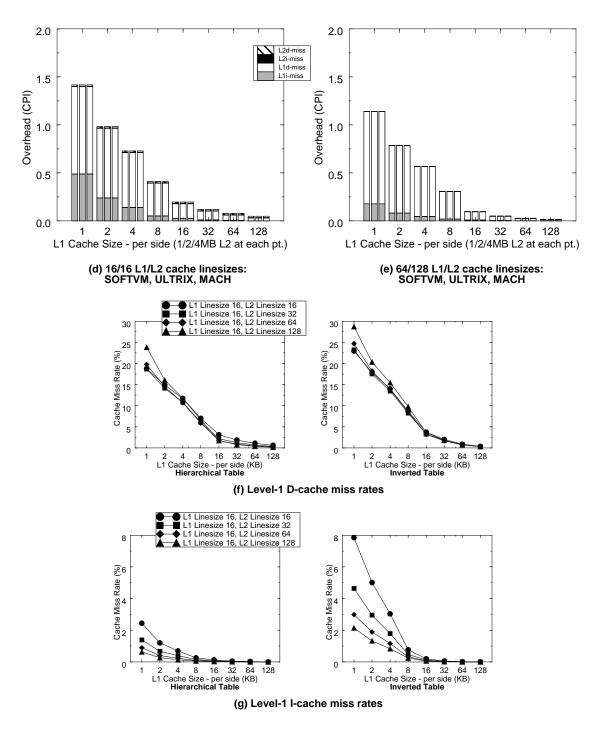

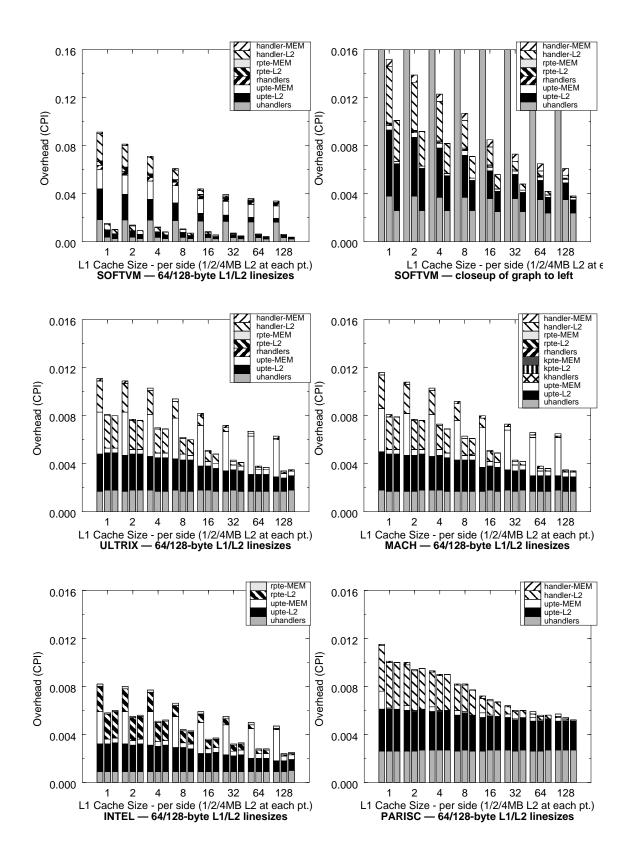

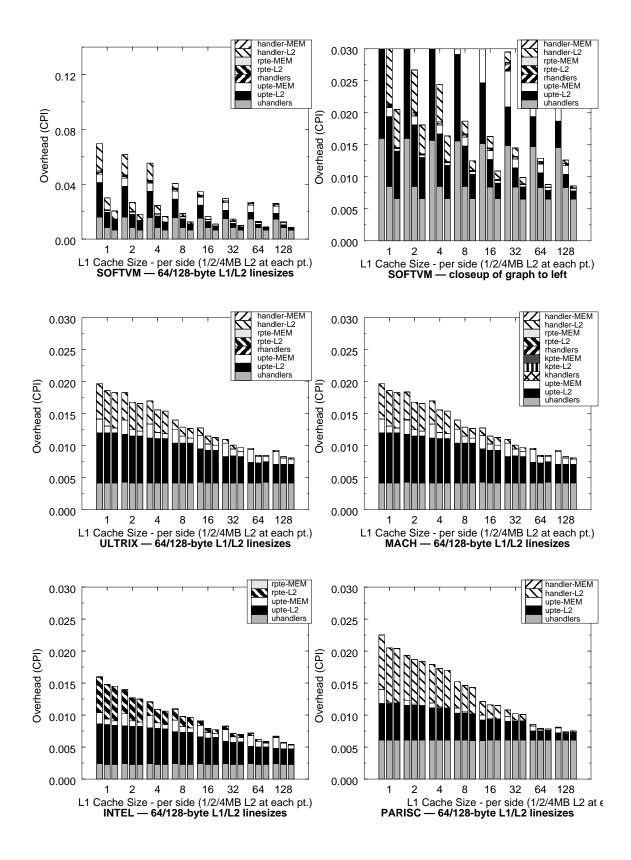

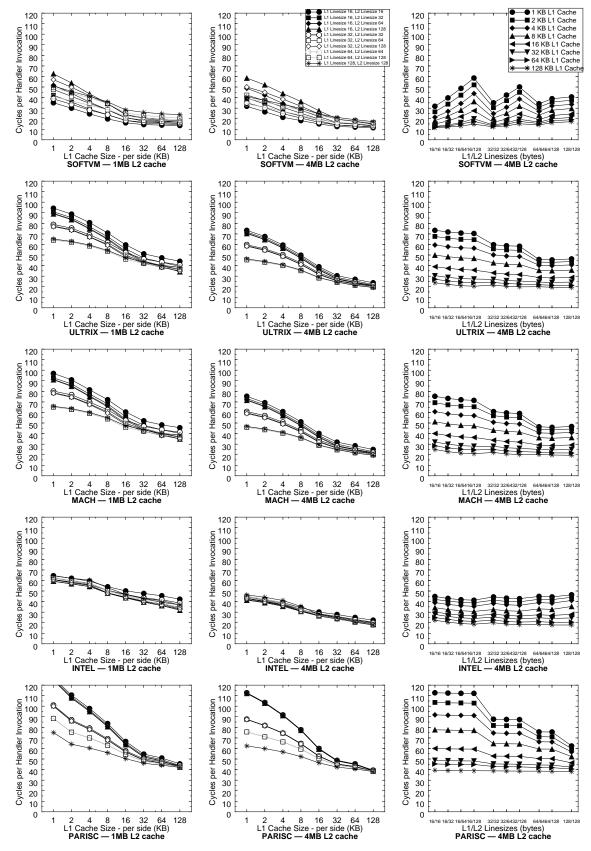

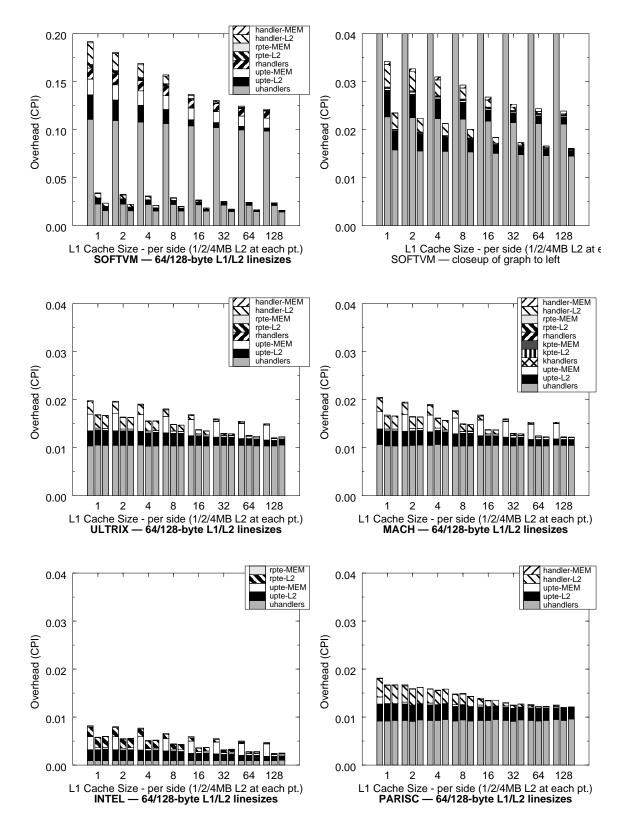

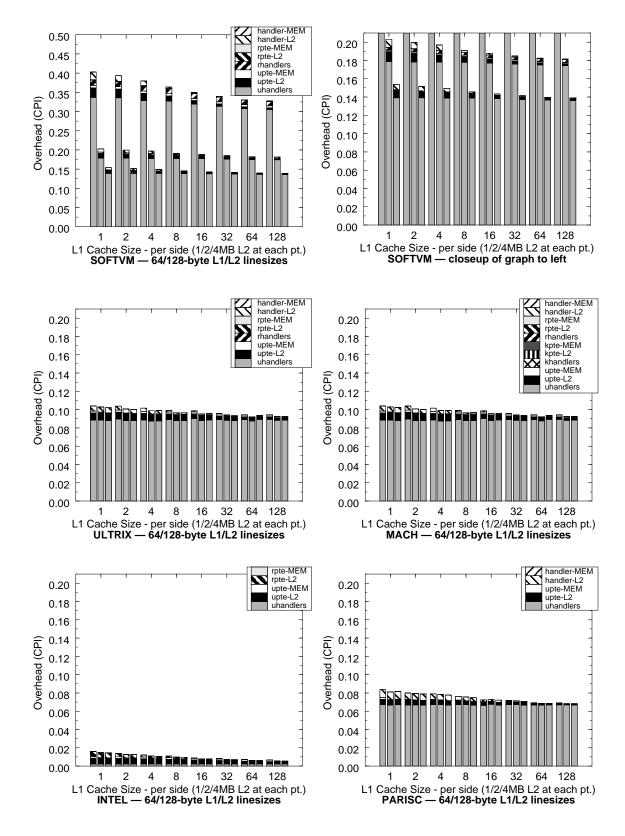

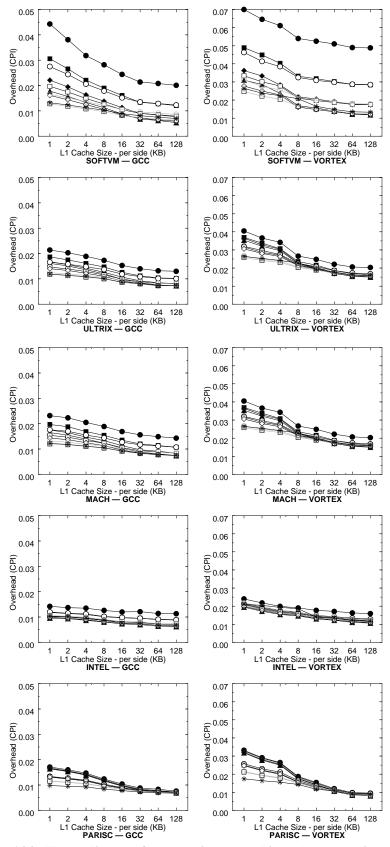

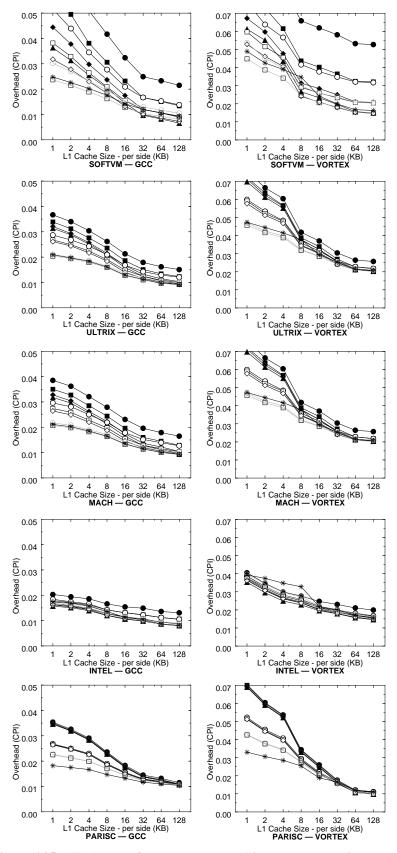

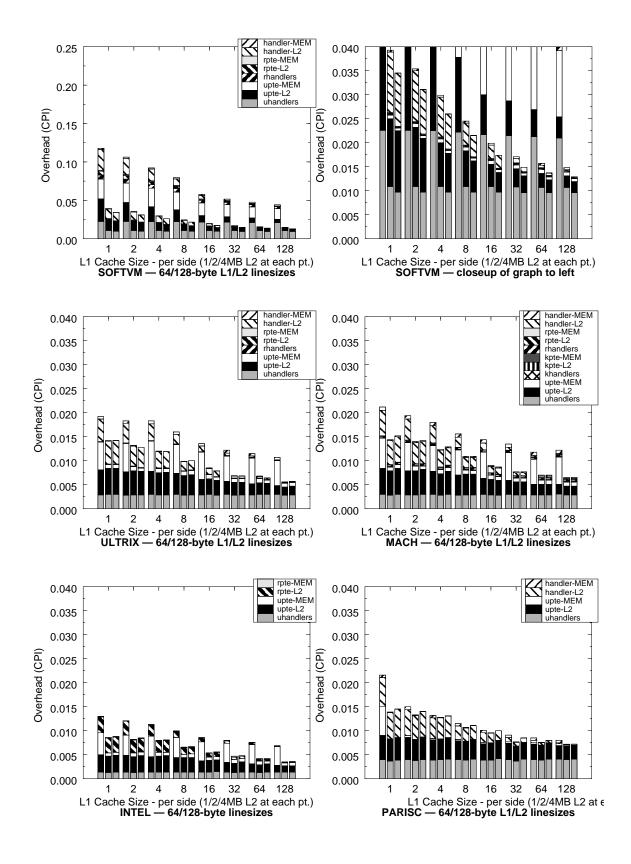

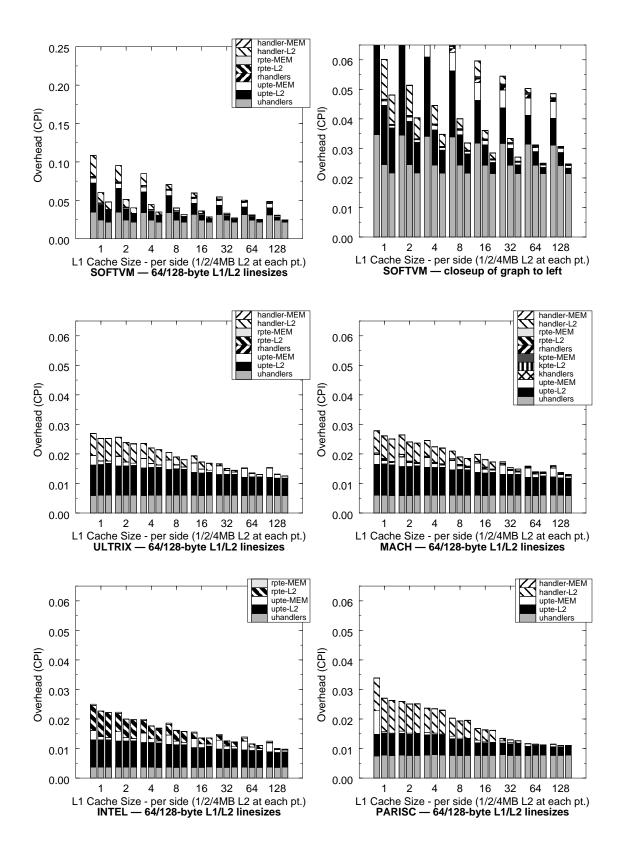

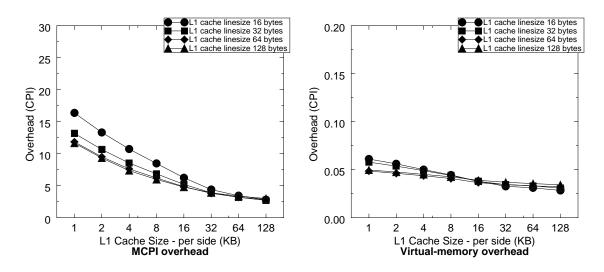

| Figure 5.6:  | The effect of cache size and linesize on software-managed address translation 96 |

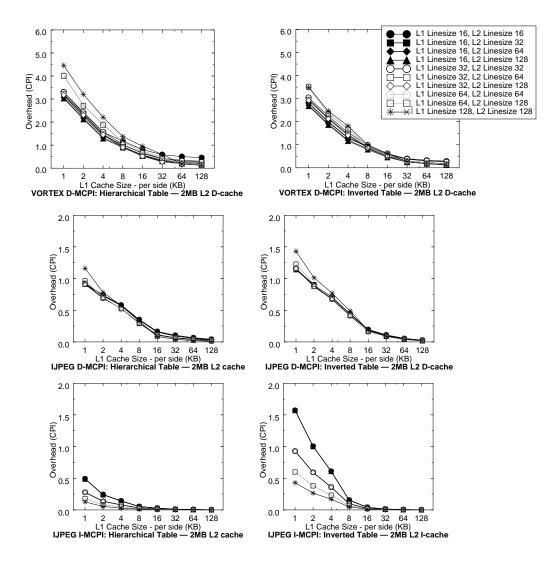

| Figure 6.1:  | MCPI variations in response to differing page table organizations 100            |

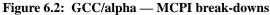

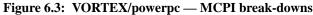

| Figure 6.2:  | GCC/alpha — MCPI break-downs 102                                                 |

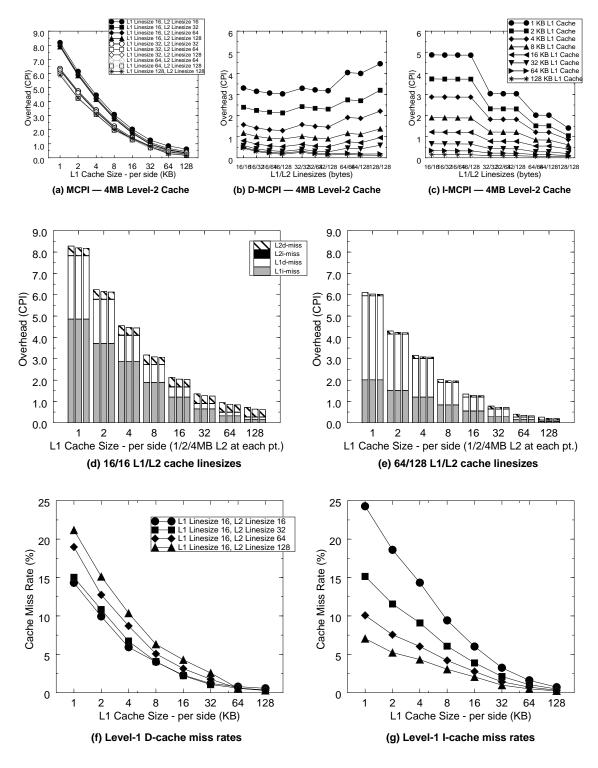

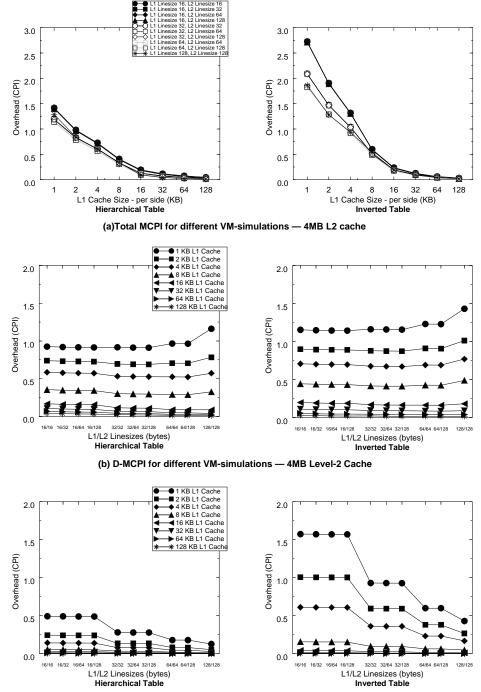

| Figure 6.3:  | VORTEX/powerpc — MCPI break-downs 103                                            |

| Figure 6.4:  | IJPEG/alpha — MCPI break-downs 104                                               |

| Figure 6.5:  | IJPEG/alpha — MCPI break-downs, cont'd 105                                       |

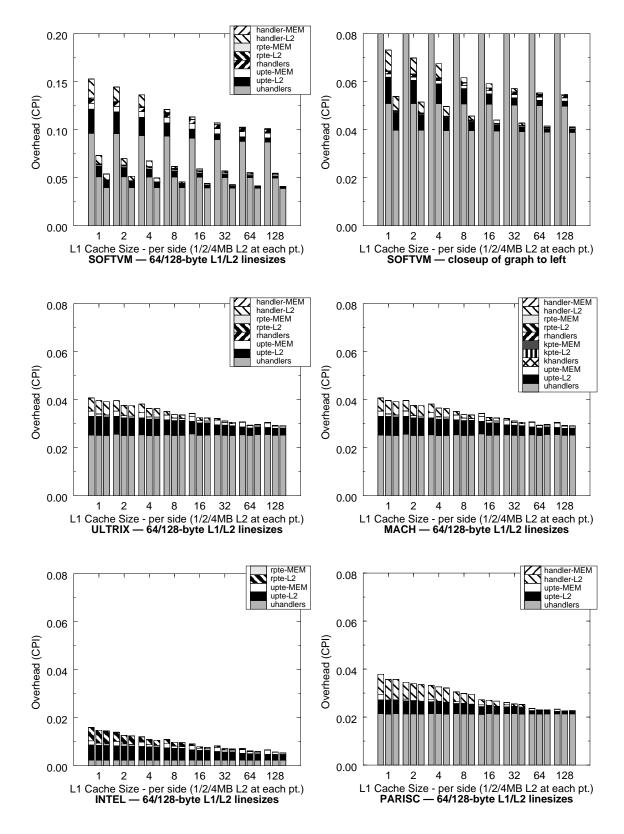

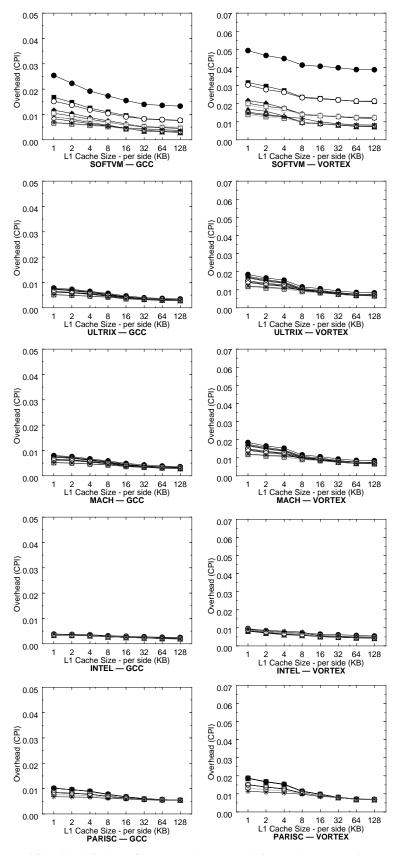

| Figure 6.6:  | GCC/alpha — VMCPI vs. cache size 107                                             |

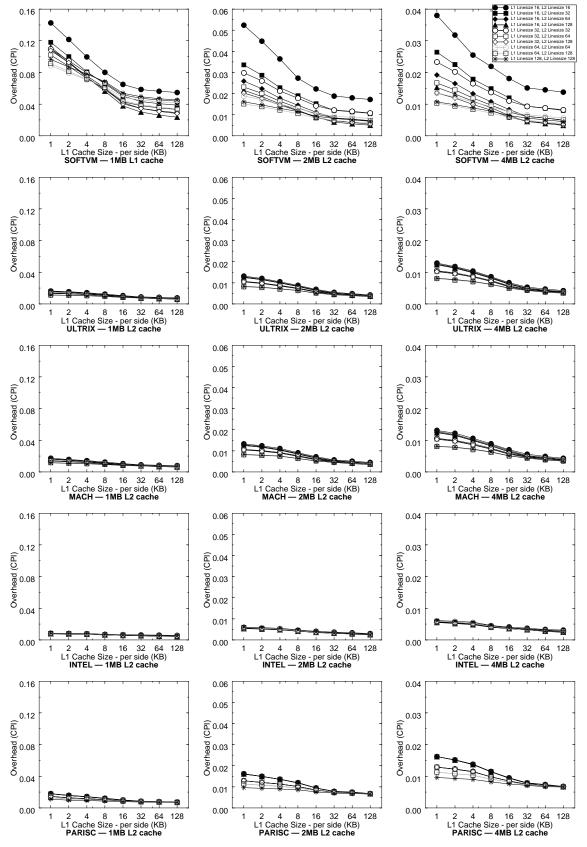

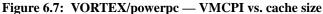

| Figure 6.7:  | VORTEX/powerpc — VMCPI vs. cache size 108                                        |

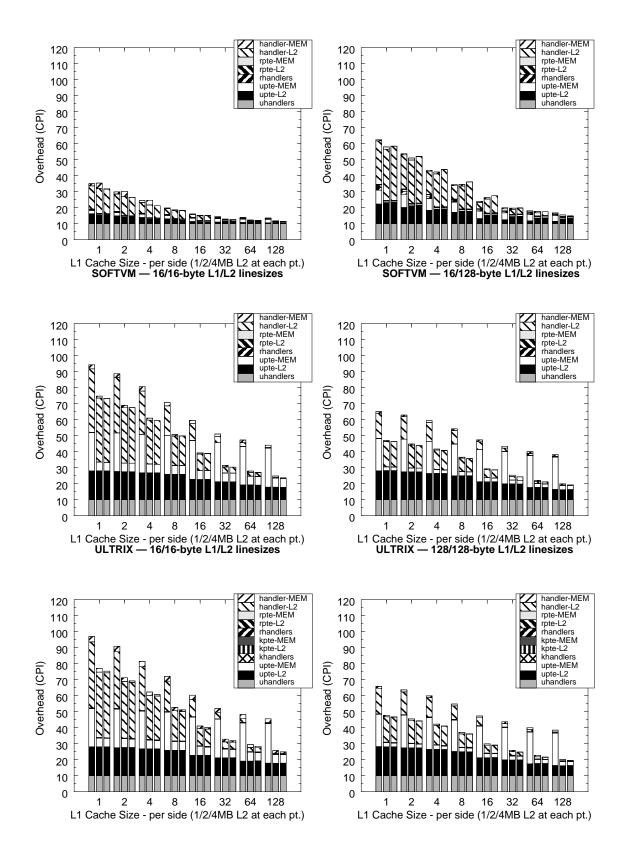

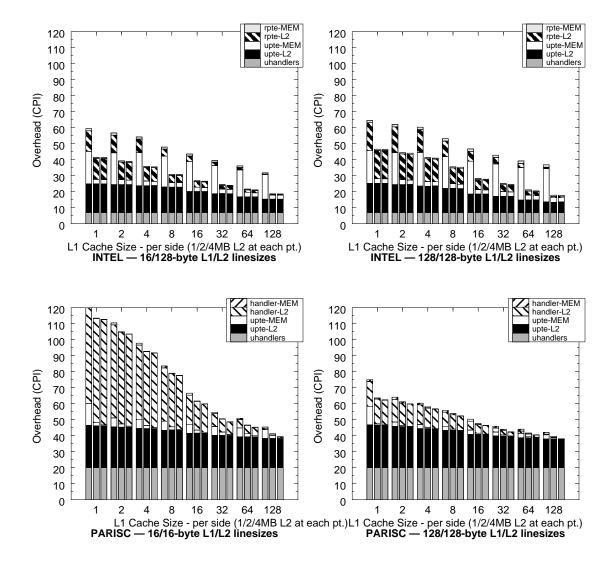

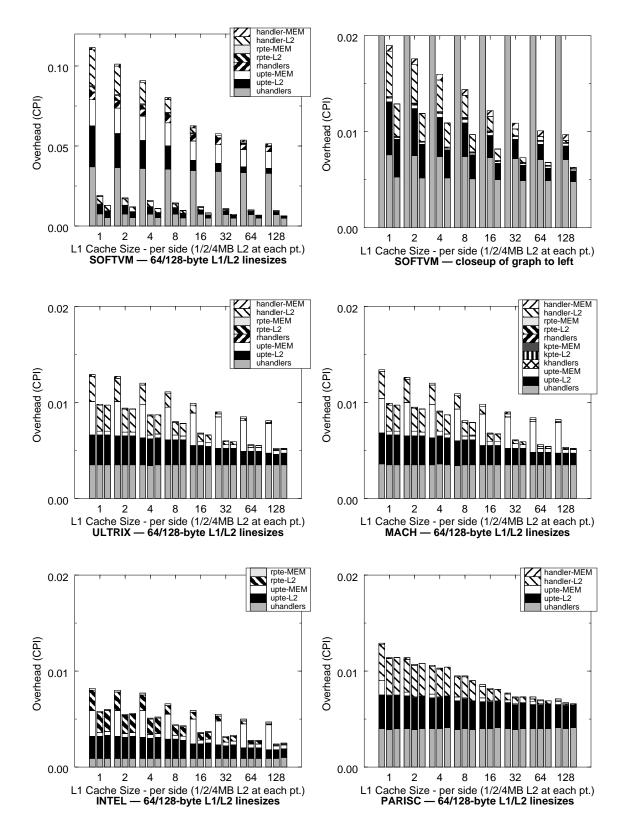

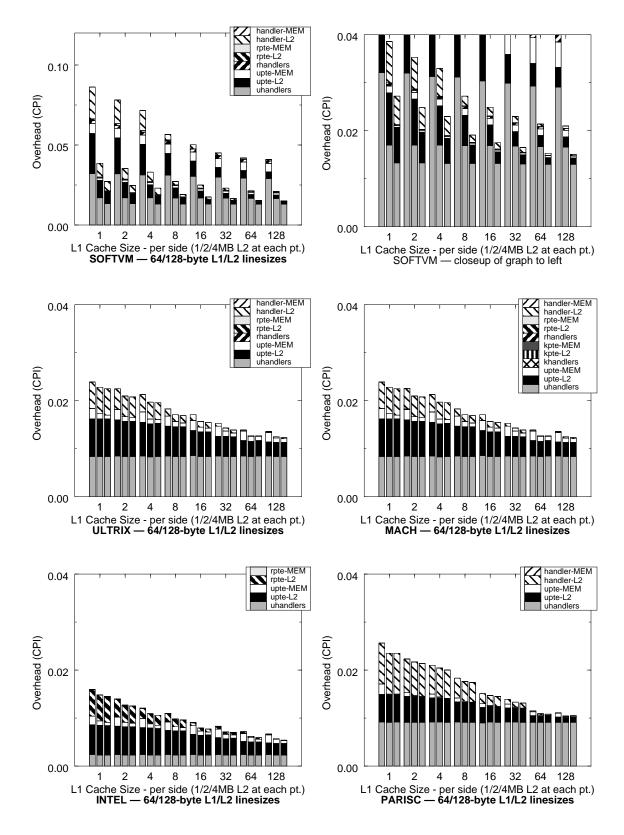

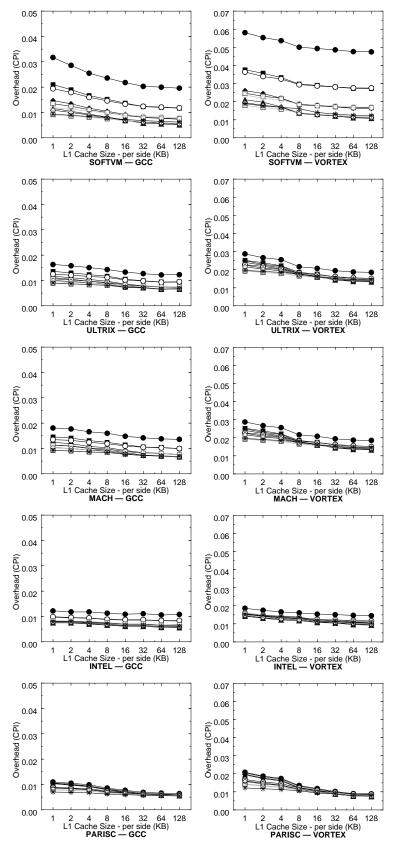

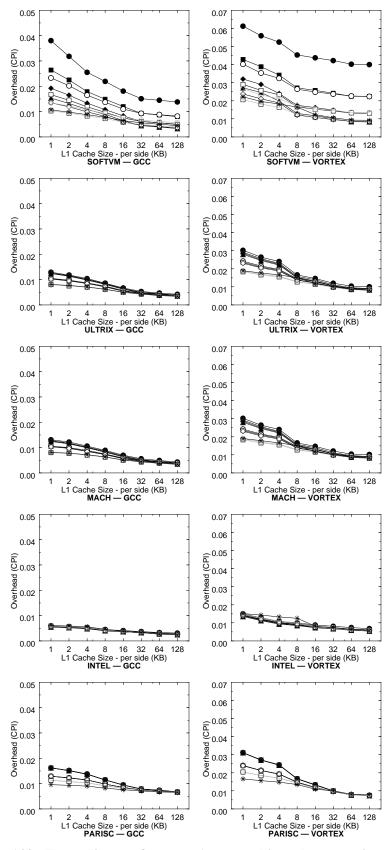

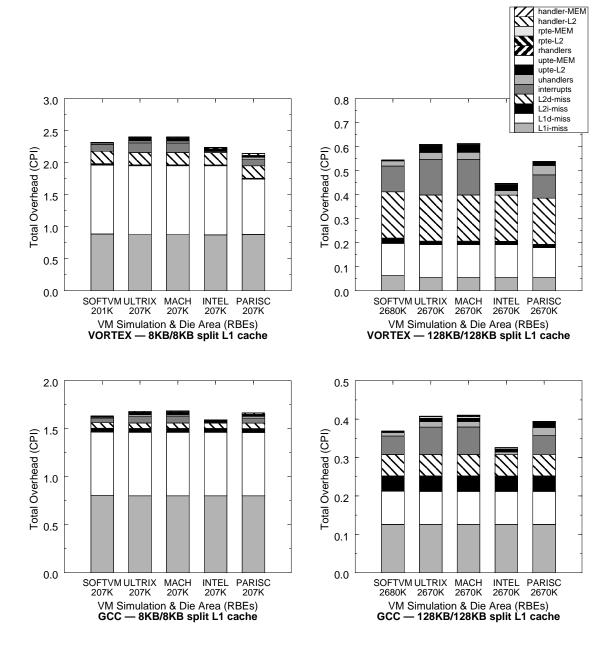

| Figure 6.8:  | GCC/alpha — VMCPI break-downs 111                                                |

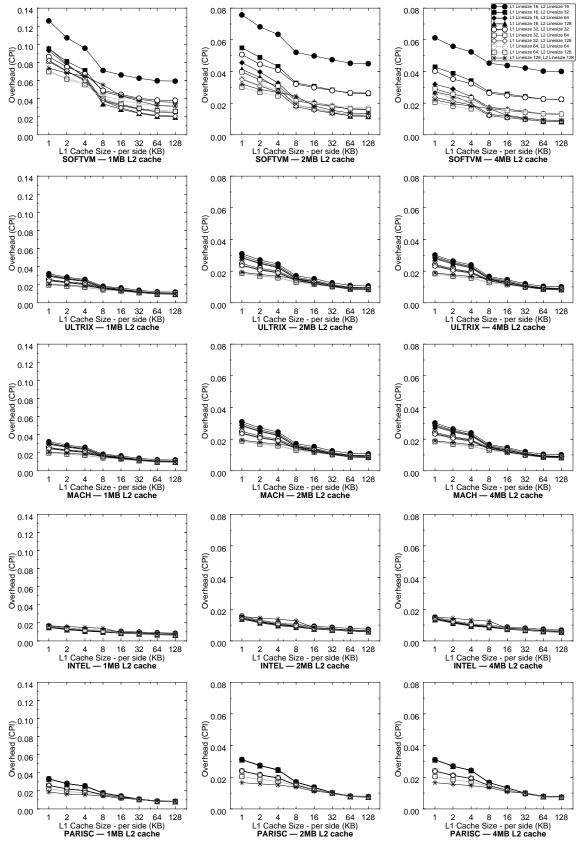

| Figure 6.9:  | VORTEX/powerpc — VMCPI break-downs 112                                           |

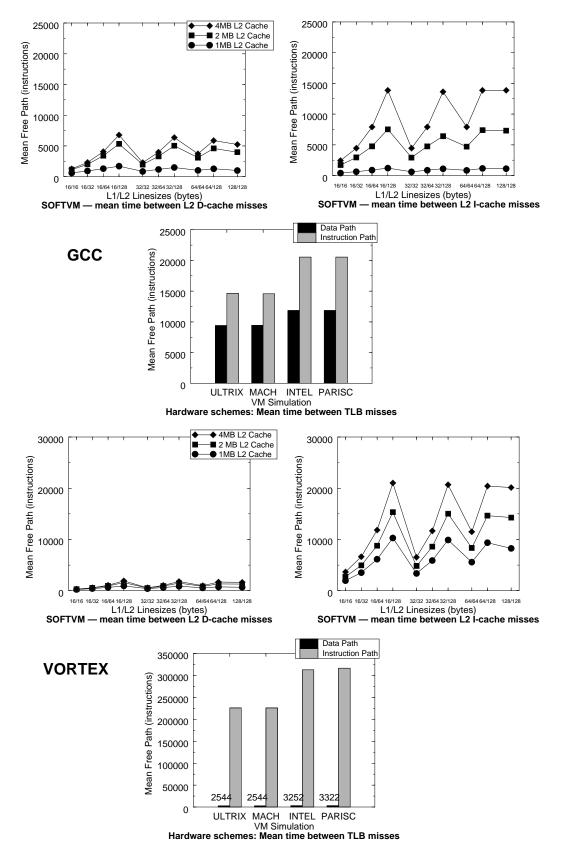

| Figure 6.10: | Mean time between handlers for GCC/alpha and VORTEX/powerpc 117                  |

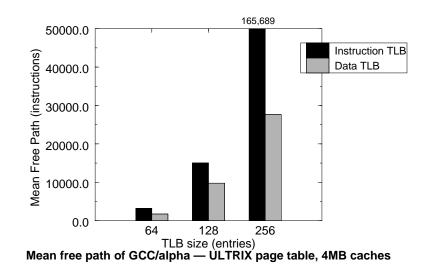

| Figure 6.11: | The cost of using smaller TLBs 118                                               |

| Figure 6.12: | GCC/alpha — Per-invocation costs of the handlers 121                             |

| Figure 6.13: | GCC/alpha — Break-downs for handler invocations 123                              |

| Figure 6.14: | GCC/alpha — Break-downs for handler invocations, cont'd 124                      |

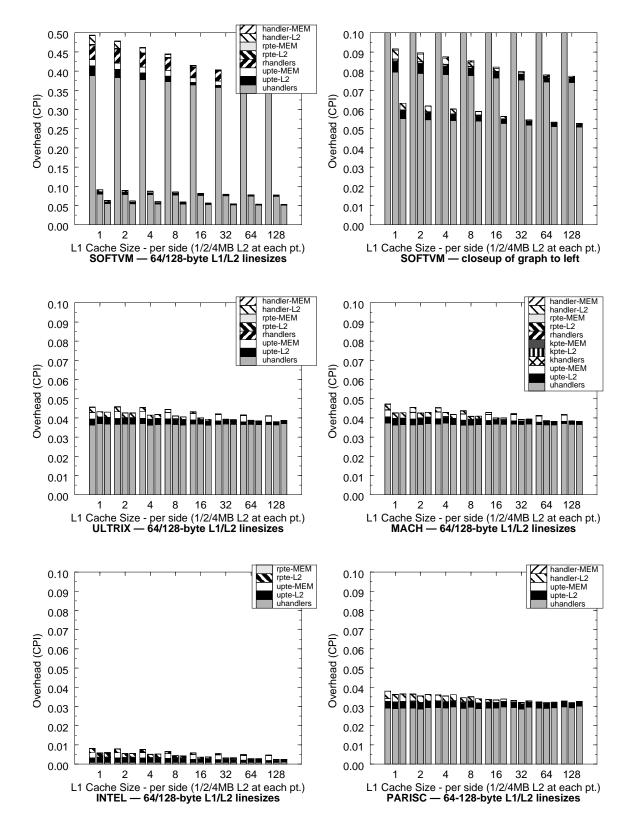

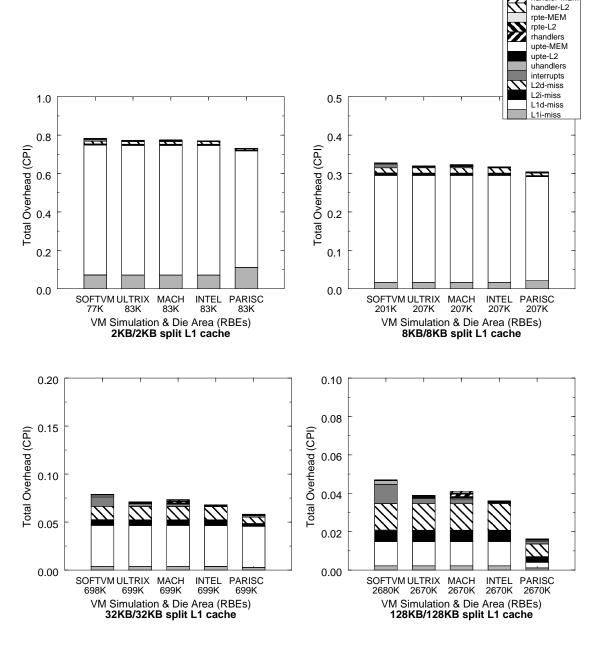

| Figure 6.15: | GCC/alpha recalculations for low-overhead interrupts 128                         |

| Figure 6.16: | GCC/alpha recalculations for medium-overhead interrupts 129                      |

| Figure 6.17: | GCC/alpha recalculations for high-overhead interrupts 130                        |

| Figure 6.18: | VORTEX/powerpc recalculations for low-overhead interrupts 131                    |

| Figure 6.19: | VORTEX/powerpc recalculations for medium-overhead interrupts 132                 |

| Figure 6.20: | VORTEX/powerpc recalculations for high-overhead interrupts 133                   |

| Figure 6.21: | The high-performance-1 memory-hierarchy access-time model 136                    |

|              |                                                                                  |

| Figure 6.22: | The high-performance-2 memory-hierarchy access-time model 137            |

|--------------|--------------------------------------------------------------------------|

| Figure 6.23: | The medium-performance-1 memory-hierarchy access-time model 138          |

| Figure 6.24: | The medium-performance-2 memory-hierarchy access-time model 139          |

| Figure 6.25: | The low-performance memory-hierarchy access-time model 140               |

| Figure 6.26: | Cold-cache measurements for GCC/alpha 142                                |

| Figure 6.27: | Cold-cache measurements for VORTEX/powerpc 143                           |

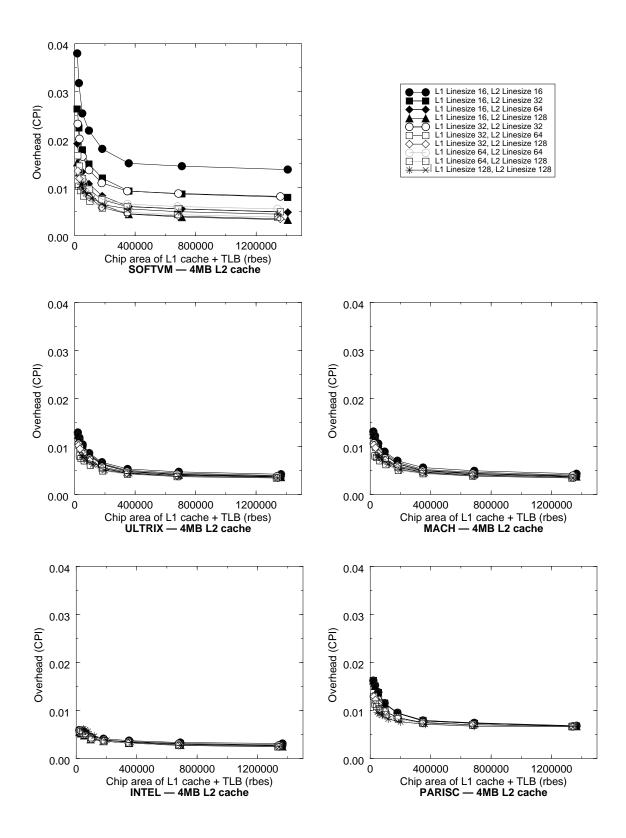

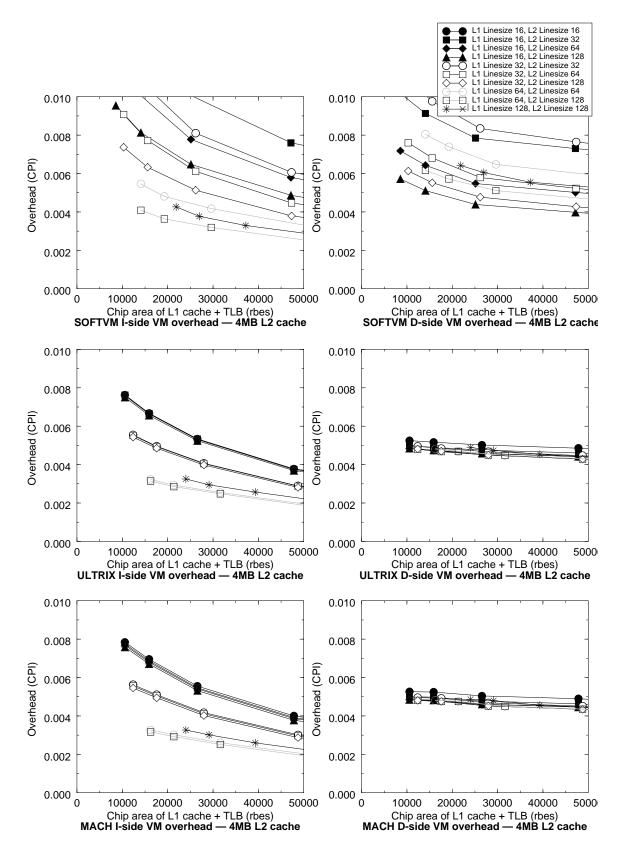

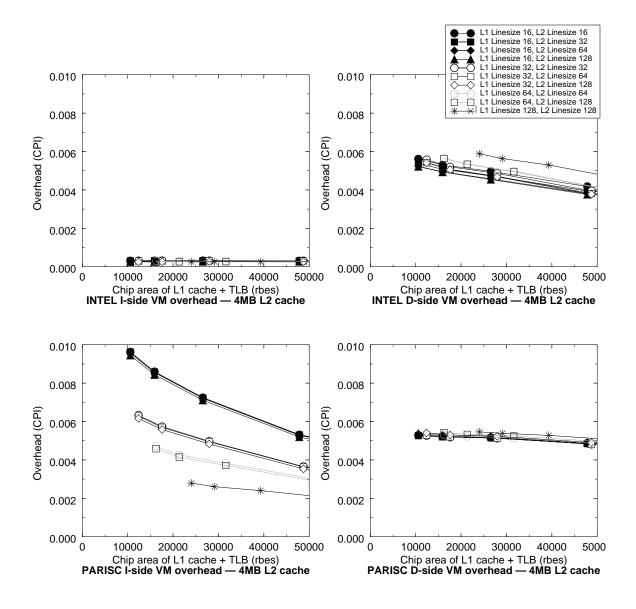

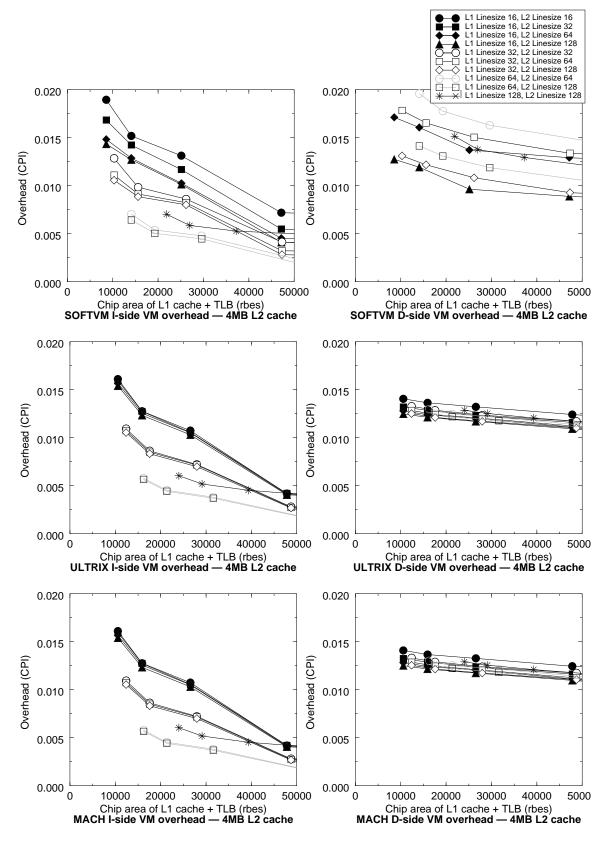

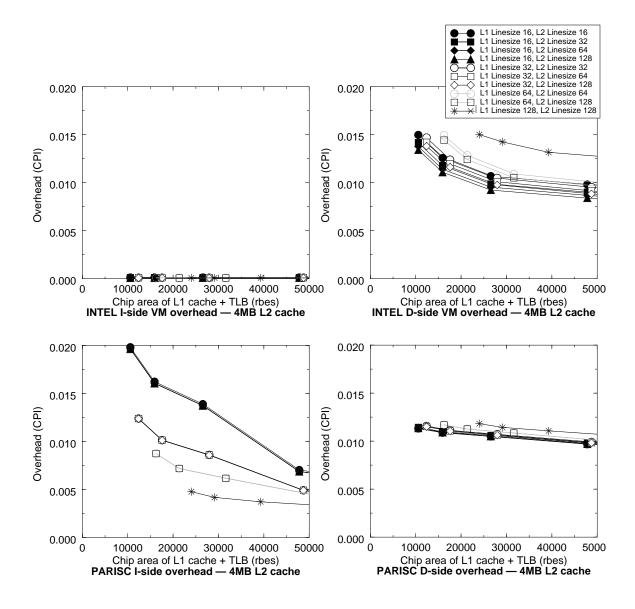

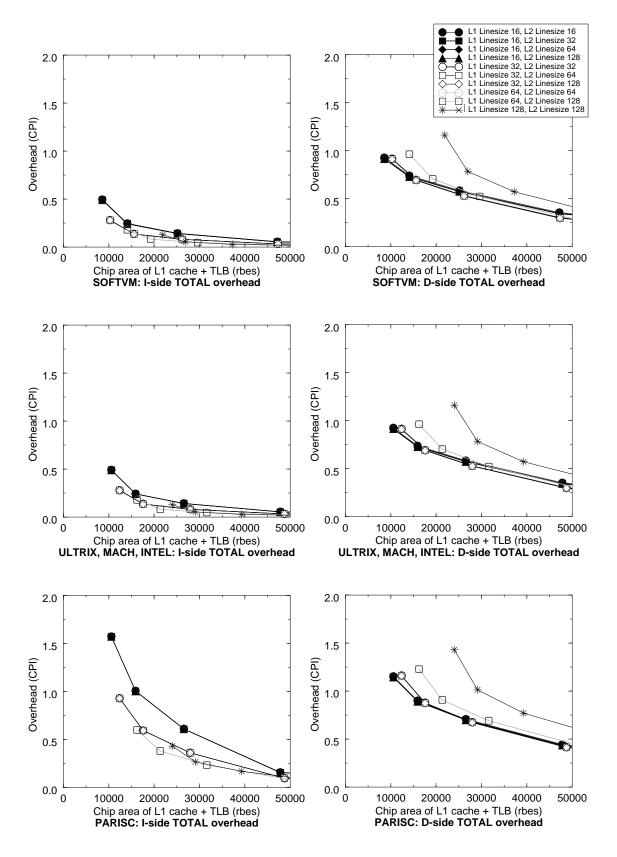

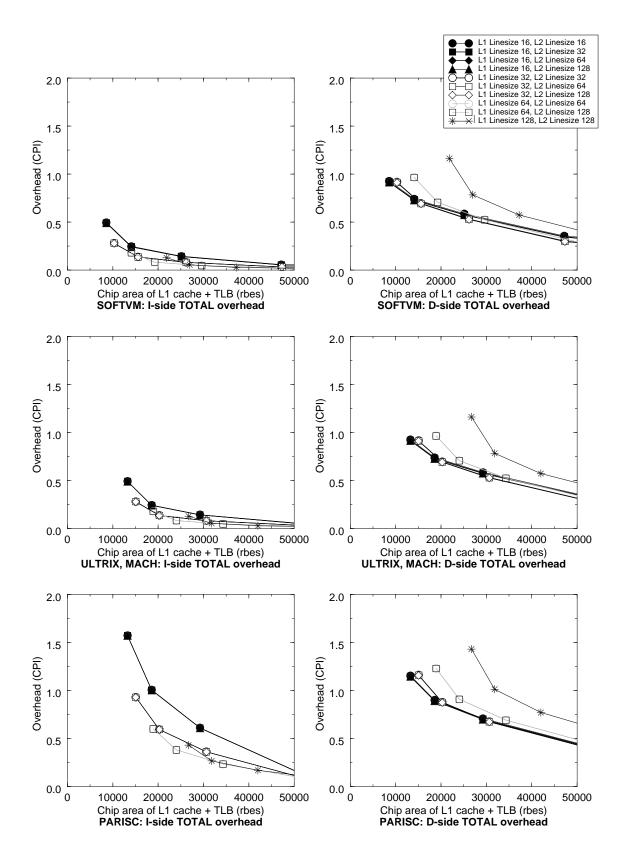

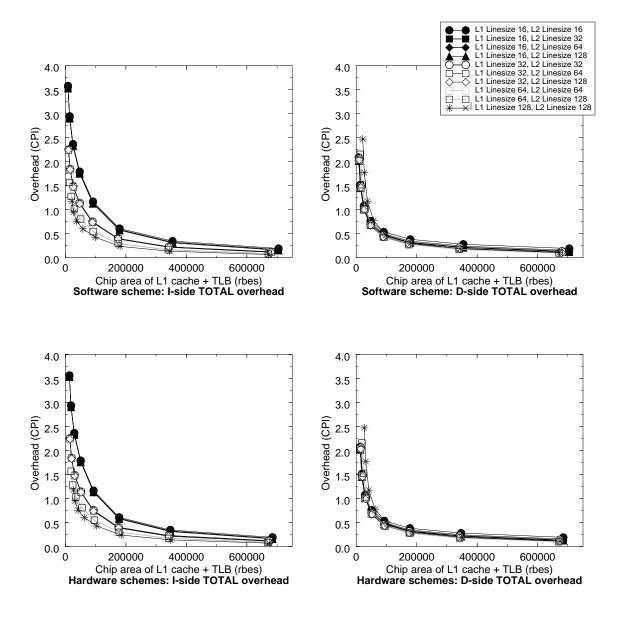

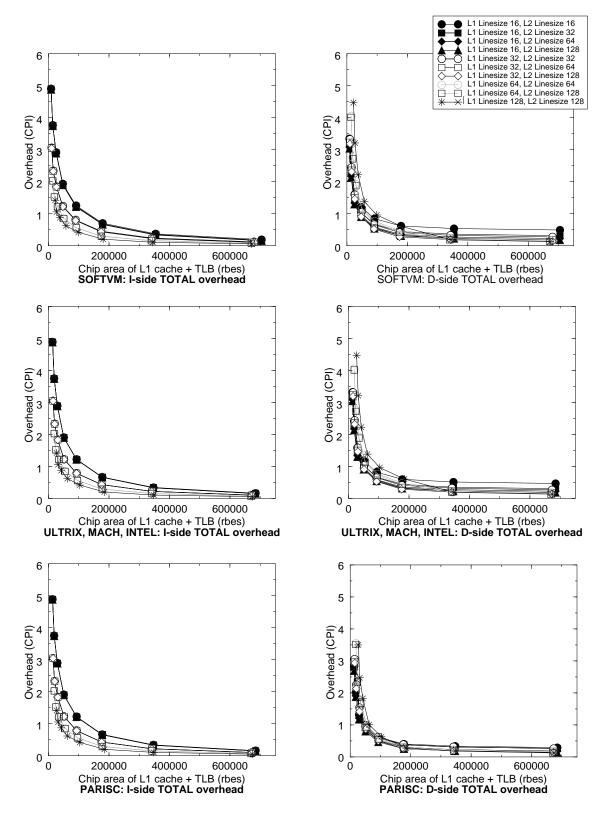

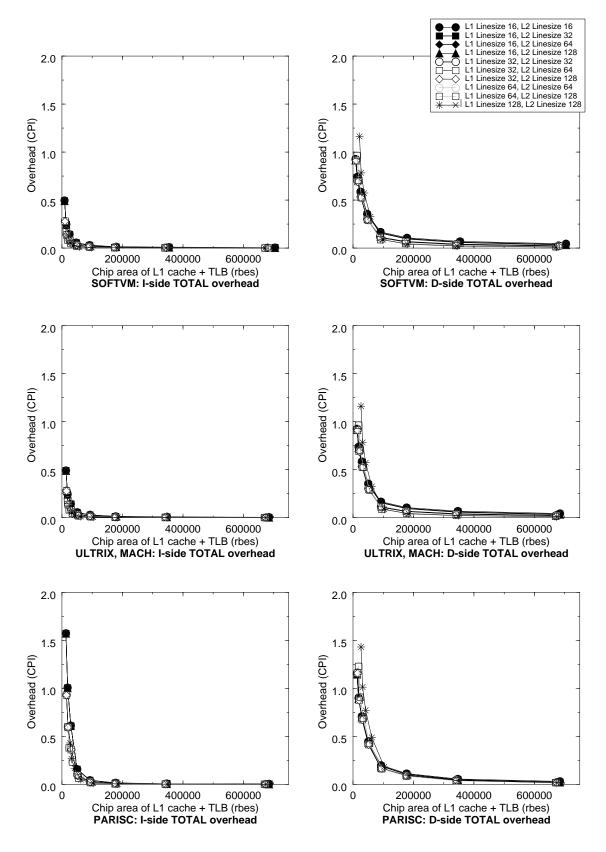

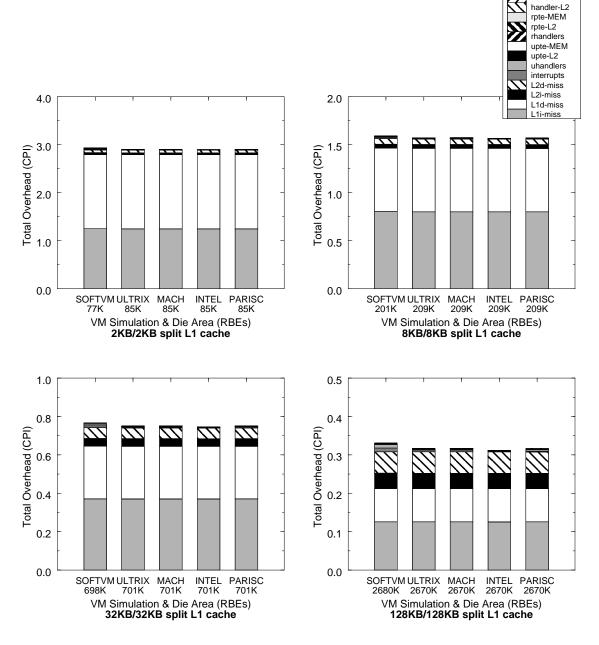

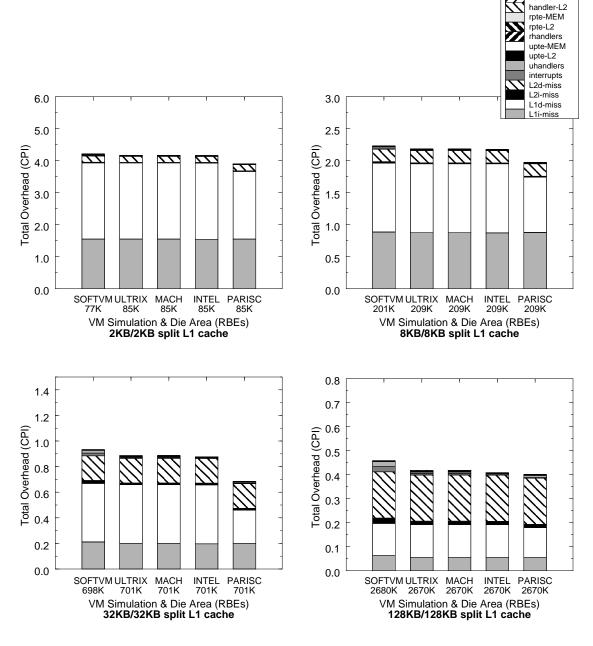

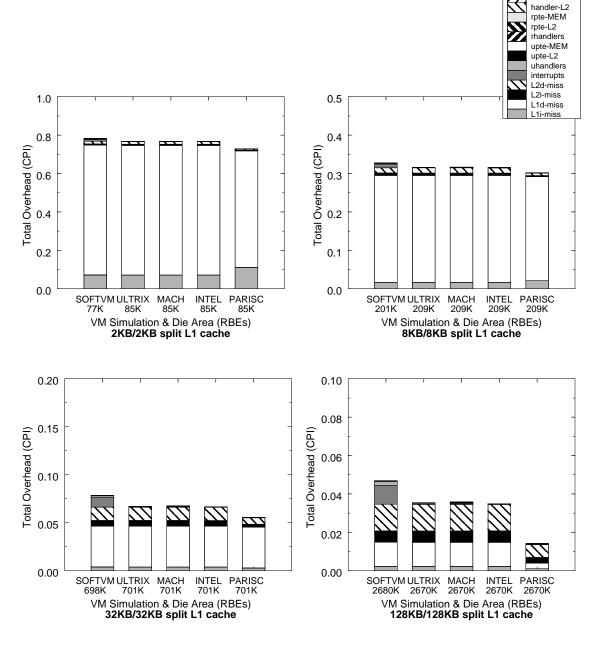

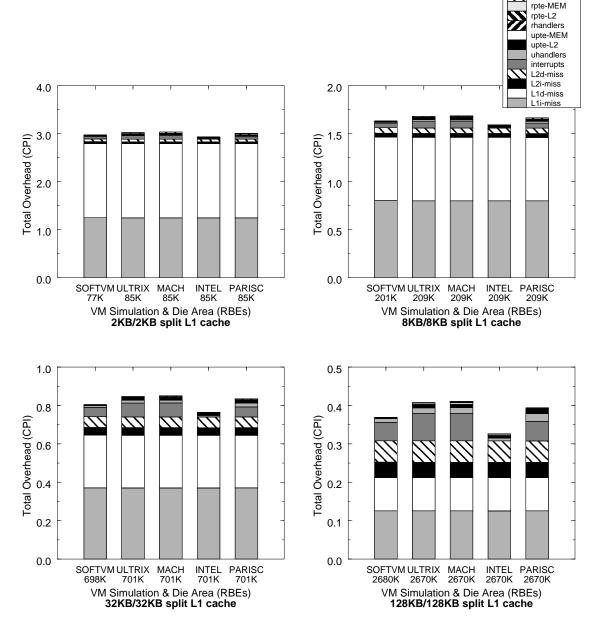

| Figure 6.28: | GCC/alpha — VM overhead as a function of die area 147                    |

| Figure 6.29: | VORTEX/powerpc — VM overhead as a function of die area 148               |

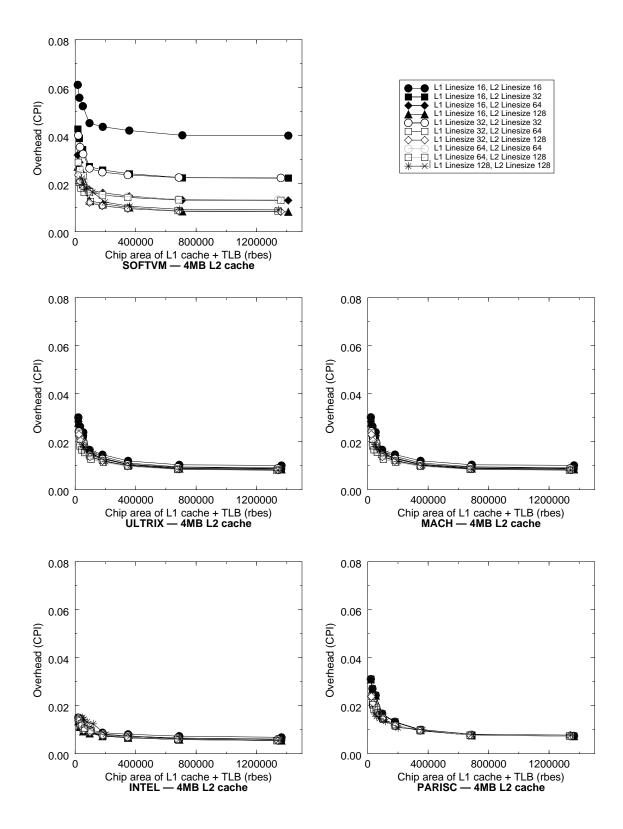

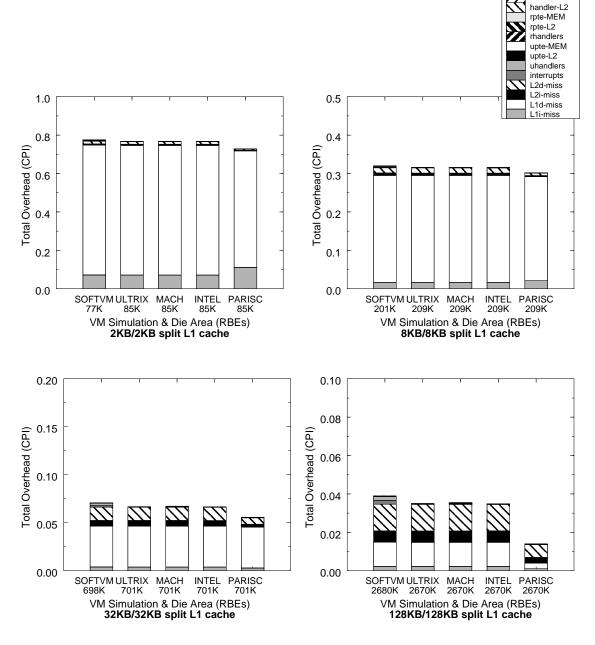

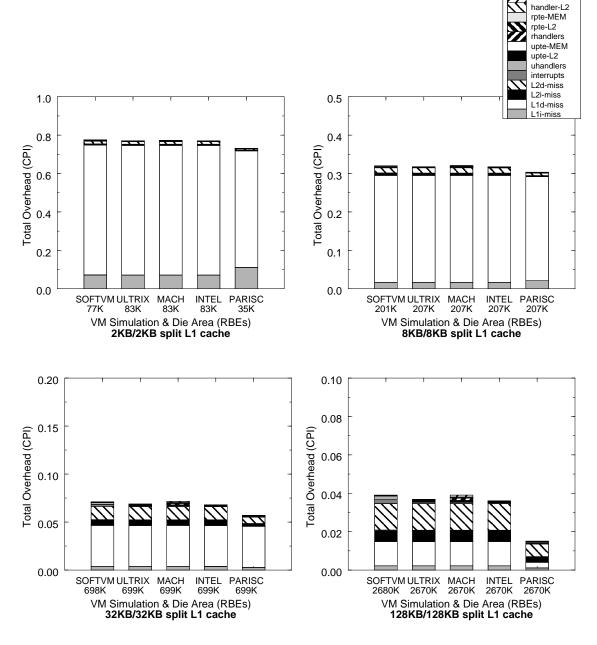

| Figure 6.30: | GCC/alpha — VM overhead vs. die-area, restricted design 150              |

| Figure 6.31: | GCC/alpha — VM overhead vs. die-area, restricted design, cont'd 151      |

| Figure 6.32: | VORTEX/powerpc — VM overhead vs. die-area, restricted design 152         |

| Figure 6.33: | VORTEX/powerpc — VM overhead vs. die-area, restricted design, cont'd 153 |

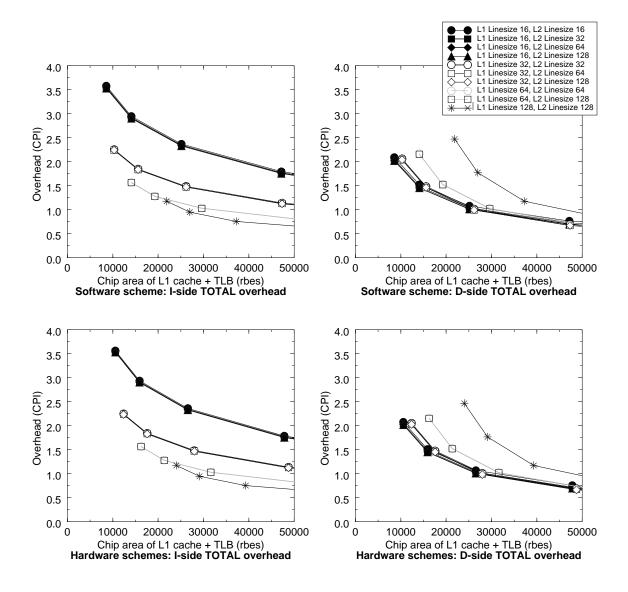

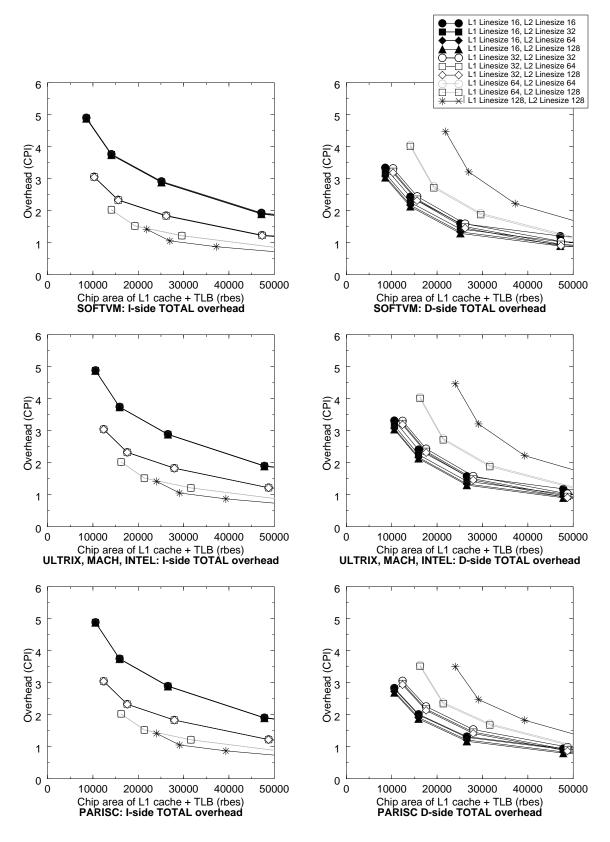

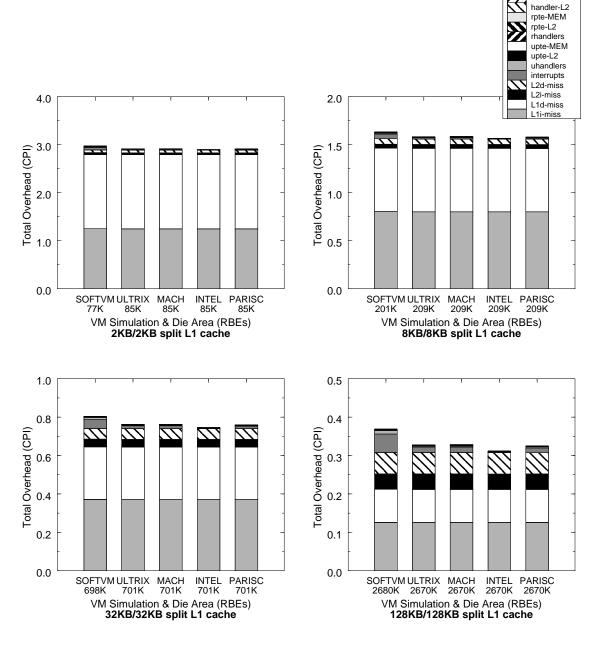

| Figure 6.34: | GCC/alpha — Total overhead vs. die-area, restricted design 154           |

| Figure 6.35: | VORTEX/powerpc — Total overhead vs. die-area, restricted design 155      |

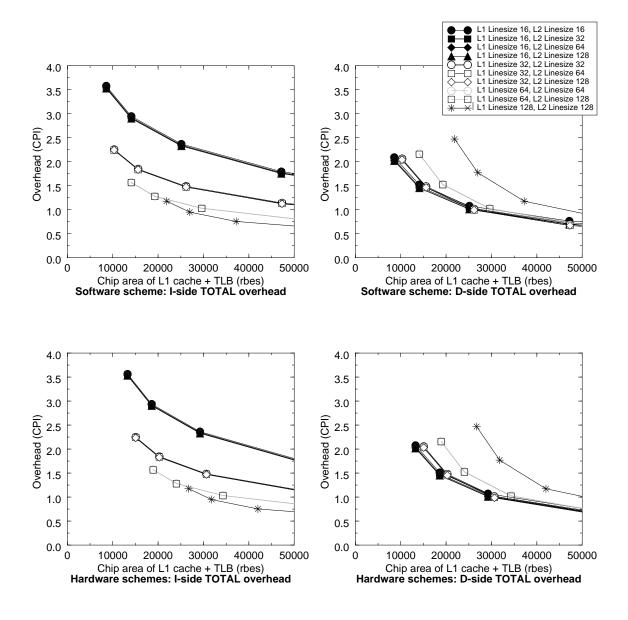

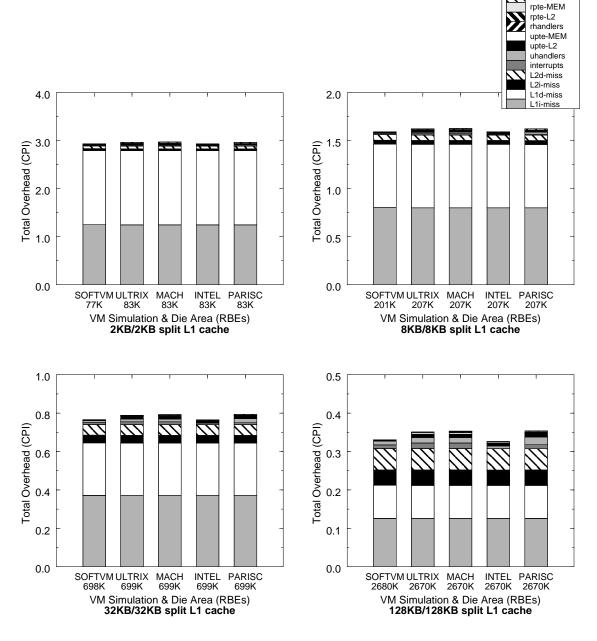

| Figure 6.36: | IJPEG/alpha — Total overhead vs. die-area, low-power design 156          |

| Figure 6.37: | GCC/alpha — Total overhead vs. die-area, low-power design 158            |

| Figure 6.38: | VORTEX/powerpc — Total overhead vs. die-area, low-power design 159       |

| Figure 6.39: | IJPEG/alpha — Total overhead vs. die-area, low-power design 160          |

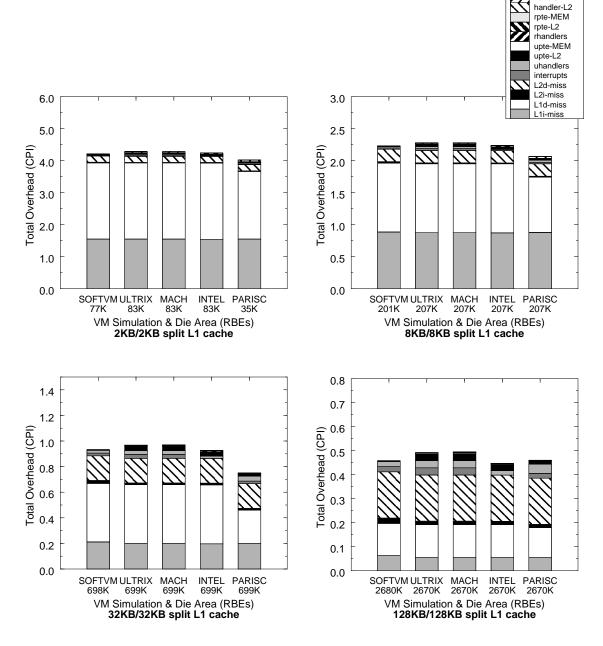

| Figure 6.40: | GCC/alpha — TOTAL overhead vs. die-area, all cache sizes 161             |

| Figure 6.41: | VORTEX/powerpc — TOTAL overhead vs. die-area, all cache sizes 162        |

| Figure 6.42: | IJPEG/alpha — TOTAL overhead vs. die-area, all cache sizes 163           |

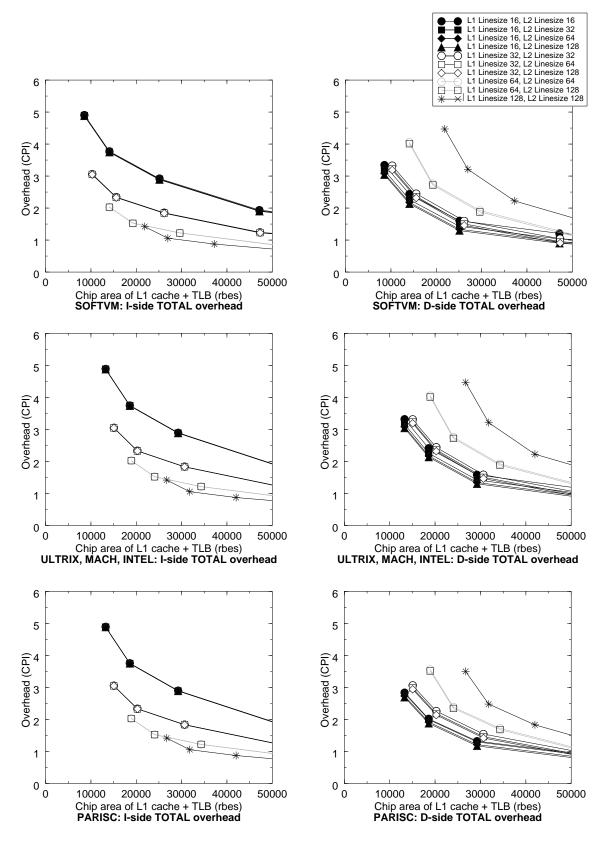

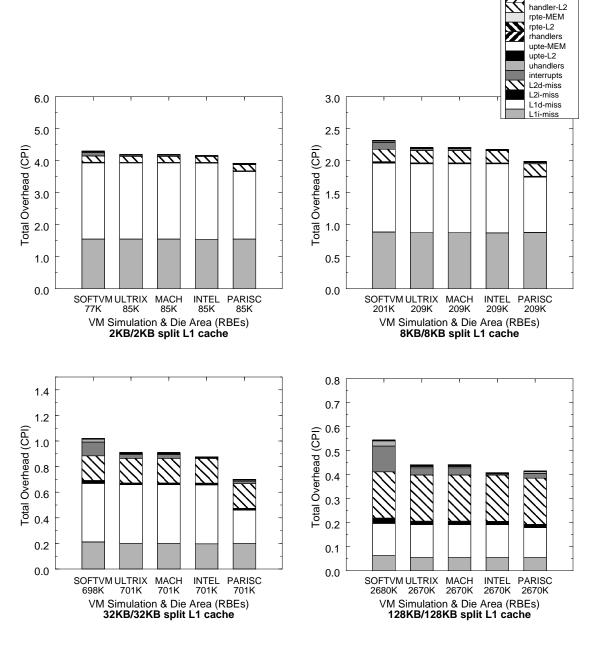

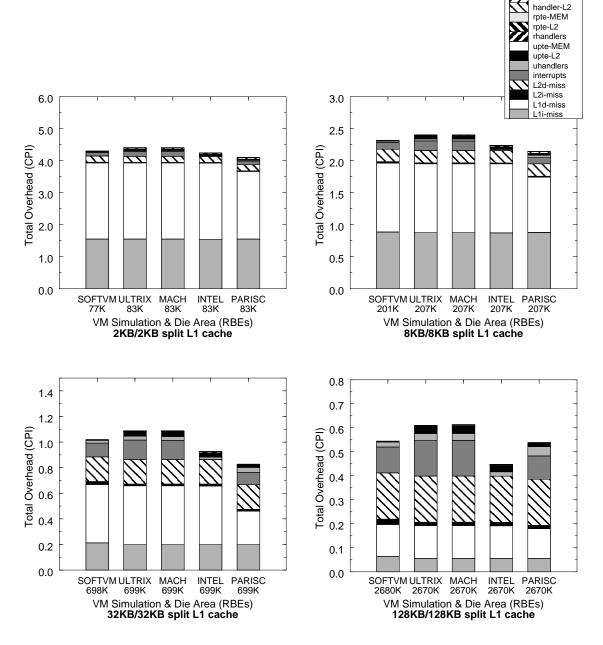

| Figure 6.43: | GCC/alpha — split 128/128-entry TLBs and a 10-cycle interrupt 165        |

| Figure 6.44: | VORTEX/powerpc — split 128/128-entry TLBs and a 10-cycle interrupt 166   |

| Figure 6.45: | IJPEG/alpha — split 128/128-entry TLBs and a 10-cycle interrupt 167      |

| Figure 6.46: | GCC/alpha — split 128/128-entry TLBs and a 50-cycle interrupt 168        |

| Figure 6.47: | VORTEX/powerpc — split 128/128-entry TLBs and a 50-cycle interrupt 169   |

| Figure 6.48: | IJPEG/alpha — split 128/128-entry TLBs and a 50-cycle interrupt 170      |

| Figure 6.49: | GCC/alpha — split 64/64-entry TLBs and a 10-cycle interrupt 171          |

| Figure 6.50: | VORTEX/powerpc — split 64/64-entry TLBs and a 10-cycle interrupt 172     |

| Figure 6.51: | IJPEG/alpha — split 64/64-entry TLBs and a 10-cycle interrupt 173        |

| Figure 6.52: | GCC/alpha — split 64/64-entry TLBs and a 50-cycle interrupt 175          |

| Figure 6.53: | VORTEX/powerpc — split 64/64-entry TLBs and a 50-cycle interrupt 176     |

| Figure 6.54: | IJPEG/alpha — split 64/64-entry TLBs and a 50-cycle interrupt 177        |

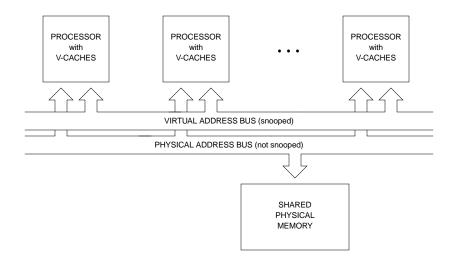

| Figure 6.55: | Shared-memory multiprocessor organization                                |

|              |                                                                          |

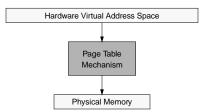

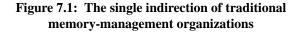

| Figure 7.1:  | The single indirection of traditional memory-management organizations                 | 192 |

|--------------|---------------------------------------------------------------------------------------|-----|

| Figure 7.2:  | Multiple levels of indirection in a segmented<br>memory-management organization       | 192 |

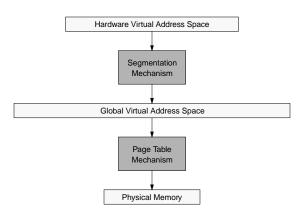

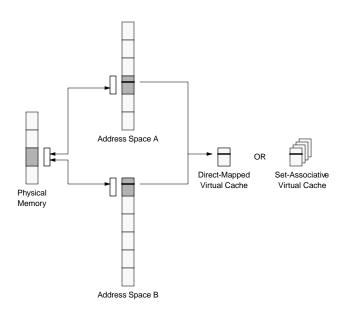

| Figure 7.3:  | The synonym problem of virtual caches                                                 | 194 |

| Figure 7.4:  | Simple hardware solutions to page aliasing                                            | 195 |

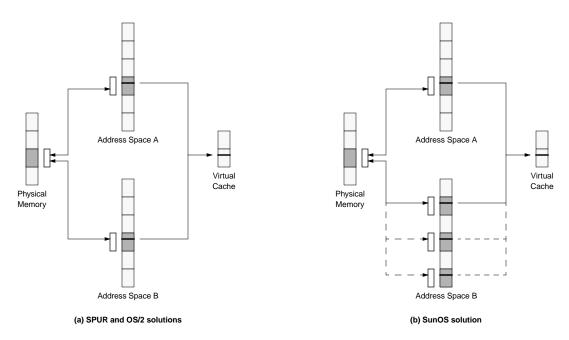

| Figure 7.5:  | Synonym problem solved by operating system policy                                     | 196 |

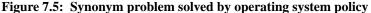

| Figure 7.6:  | The problem with allowing processes to map shared data at different virtual addresses | 198 |

| Figure 7.7:  | The use of segments to provide virtual address aliasing                               | 201 |

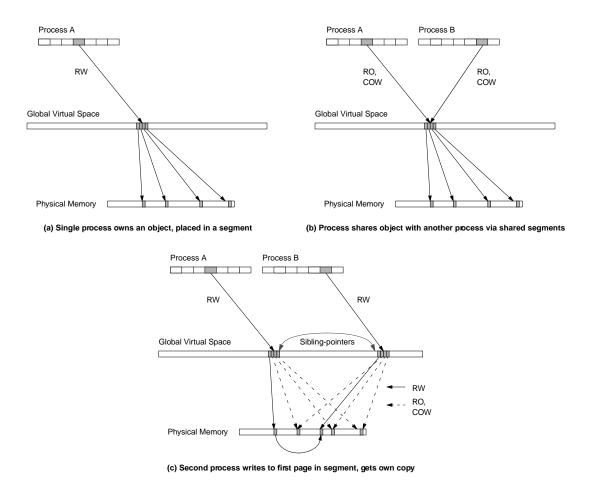

| Figure 7.8:  | Copy-on-write in a segmented architecture                                             | 202 |

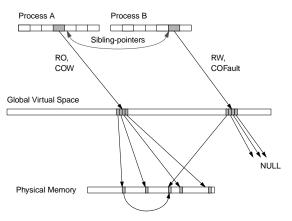

| Figure 7.9:  | An alternate implementation of copy-on-write                                          | 203 |

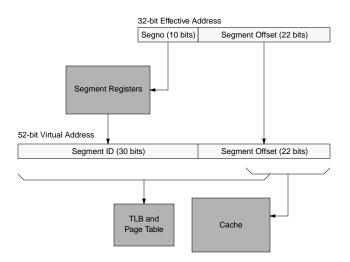

| Figure 7.10: | Segmentation mechanism used in Discussion                                             | 204 |

| Figure 7.11: | A global page table organization                                                      | 205 |

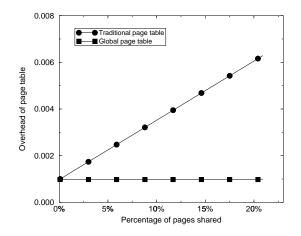

| Figure 7.12: | Comparison of page table space requirements                                           | 207 |

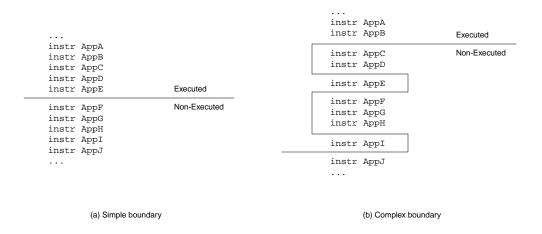

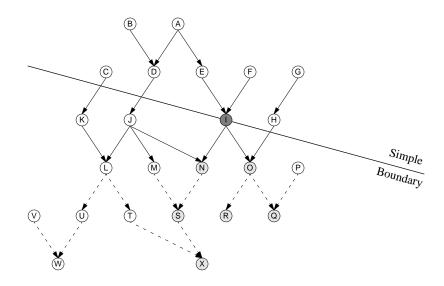

| Figure 8.1:  | Simple and complex boundaries in the dynamic instruction stream                       | 212 |

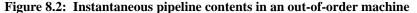

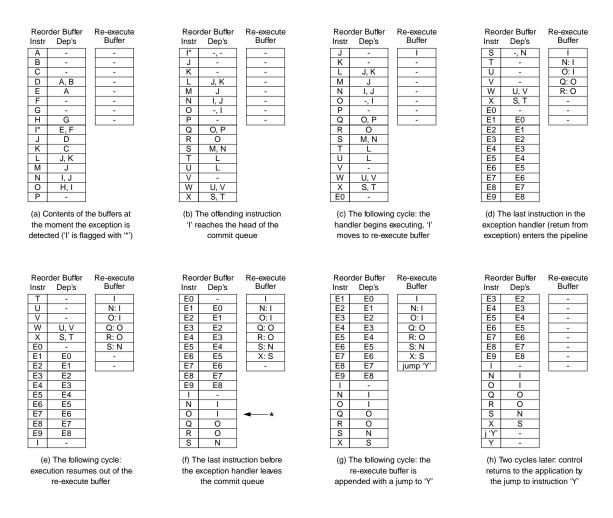

| Figure 8.2:  | Instantaneous pipeline contents in an out-of-order machine                            | 213 |

| Figure 8.3:  | Example of relaxed-precision interrupt handling                                       | 216 |

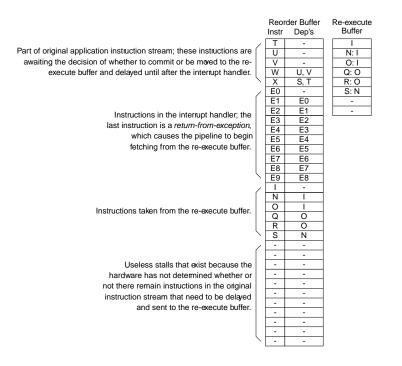

| Figure 8.4:  | Sequential operation of the reorder buffer and re-execute buffer                      | 220 |

| Figure 8.5:  | The problem with short interrupt handlers and large reorder buffers                   | 222 |

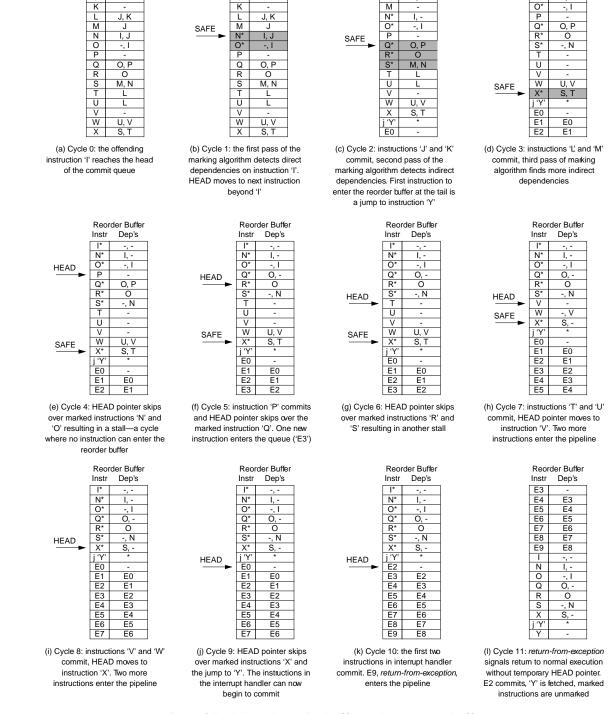

| Figure 8.6:  | Parallel operation of the reorder buffer and re-execute buffer                        | 224 |

| Figure 8.7:  | Merged reorder buffer and re-execute buffer                                           | 226 |

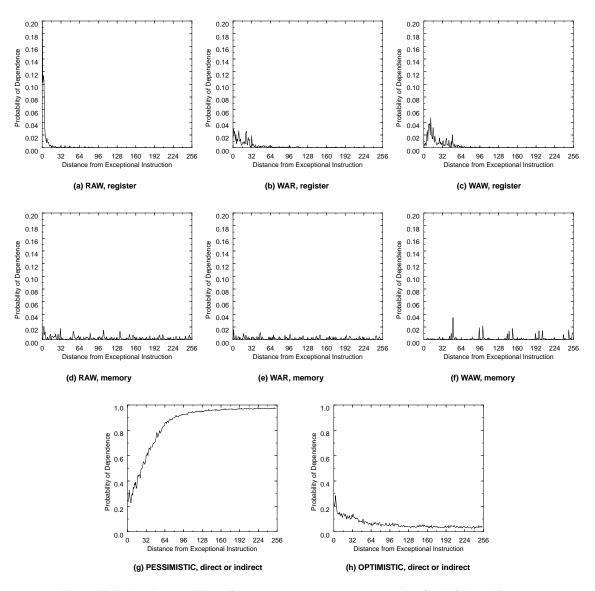

| Figure 8.8:  | Register-register & memory-memory dependencies for VORTEX/alpha                       | 230 |

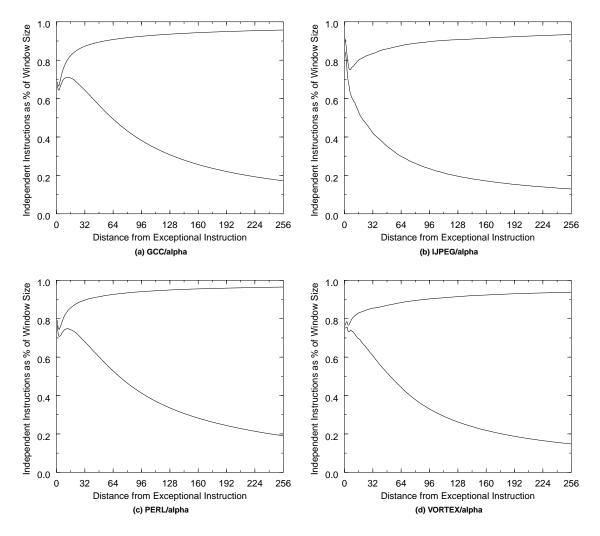

| Figure 8.9:  | Dependence of instructions on the head of the reorder buffer                          | 231 |

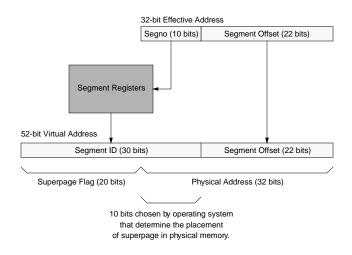

| Figure 9.1:  | Superpage support in a SOFTVM-like architecture                                       | 237 |

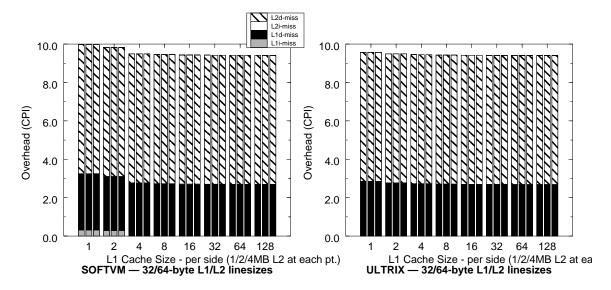

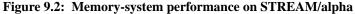

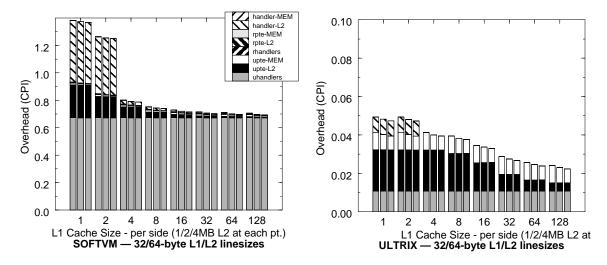

| Figure 9.2:  | Memory-system performance on STREAM/alpha                                             | 238 |

| Figure 9.3:  | Virtual memory performance on STREAM/alpha                                            | 239 |

| Figure 9.4:  | VM performance on STREAM/alpha, using superpages                                      | 240 |

| Figure 10.1: | Main memory as a cache                                                                | 243 |

| Figure 10.2: | Alternative cache-like organizations for physical memory                              | 246 |

| Figure 10.3: | Modulo-N and hashing organizations for direct-mapped cache                            | 248 |

| Figure 10.4: | The VM-overhead of the DRAM cache: GCC/alpha                                          | 249 |

| Figure 11.1: | Total overhead: split 64/64-entry TLBs and a 50-cycle interrupt                       | 252 |

# LIST OF TABLES

| Table 3.1: | Comparison of architectural features<br>in six commercial memory-management units | 40 |

|------------|-----------------------------------------------------------------------------------|----|

| Table 3.2: | Address size as a function of page size                                           | 44 |

| Table 3.3: | Characteristics of the Owner/ID Taxonomy                                          | 56 |

| Table 4.1: | Simulation details                                                                | 65 |

| Table 4.2: | Simulated page-table events                                                       | 66 |

| Table 4.3: | Most-used SPEC '95 integer benchmarks                                             | 74 |

| Table 4.4: | Components of MCPI                                                                | 75 |

| Table 4.5: | Components of VMCPI                                                               | 76 |

| Table 5.1: | Qualitative comparison of cache-access/address-translation mechanisms             | 91 |

| Table 5.2: | TLB overhead of several operating systems                                         | 92 |

| Table 5.3: | Overhead of software-managed address translation                                  | 92 |

| Table 5.4: | Page protection modification frequencies in Mach3                                 | 94 |

| Table 6.1: | Interrupt models 1                                                                | 26 |

| Table 6.2: | Memory hierarchy access-time models 1                                             | 34 |

| Table 6.3: | Die areas (RBEs) for different physically-addressed caches 1                      | 44 |

| Table 6.4: | Die areas (RBEs) for different virtually-addressed caches 1                       | 45 |

| Table 6.5: | Die areas (RBEs) for different set-associative TLBs                               | 45 |

## INTRODUCTION: VIRTUAL MEMORY, THREE DECADES LATER

This is a study of memory management design in the face of changing technology characteristics. Our current model of memory management, virtual memory, was defined over three decades ago when memory was expensive and in short supply. The cost of executing a single instruction was high relative to the cost of performing the same function entirely in hardware, and so our definition of the virtual memory model reflects a hardware-oriented perspective. However, despite the fact that technology has changed drastically, the current designs of virtual memory systems and the hardware structures that support virtual memory remain largely as they were three decades ago. As we will see in this dissertation, the current model could use rethinking; doing so can buy one flexibility, performance, and simplicity of design.

## 1.1 Motivation

There are several obvious trends guiding the design and implementation of today's microprocessors: faster clock speeds, larger and cheaper memories, more on-chip devices, increased flexibility, and an increased focus on testability and reliability.

Most of these are a result of shrinking feature sizes. Shrinking feature sizes allows shorter cycle times; microprocessor clock speeds are increasing toward and beyond the 1GHz milepost, and Digital has announced a 533MHz Alpha processor while rumored to be testing a fabbed 800MHz part. The increasing capacities and decreasing prices of both physical memory and cache memory have reached the point where the home computer typically has 16MB or more of physical memory and 512KB of Level-2 cache; workstation-class machines have roughly an order of magnitude more of each. This is arguably enough to run several programs at once in memory, and the cost of doubling one's Level-2 cache or physical memory size is roughly 10% of the cost of the base machine; for instance, today's personal computers come with 16MB and cost around \$2000,

while DRAM runs \$5-10 per megabyte. More devices available per die make it worthwhile to create simple on-processor memories to speed up computations—examples include large caches, stream buffers, and branch prediction tables. There are also trends unrelated to shrinking feature sizes; one is the demand for increased flexibility, as evidenced by the rise of the software-walked page table seen in most major commercial microprocessors today, and an increased attention paid to architecture emulation and (re)configurable computing. There is also an enormous emphasis placed on testability and reliability, especially in the wake of the Intel FDIV debacle.

These trends seem to suggest a design philosophy:

- 1. Make it simple

- 2. Do it in software

A simpler design implies less hardware in the critical path and would therefore allow one to better exploit the processor speeds available; it might also lead to reduced power requirements. Complex designs such as large, fully-associative memory structures wreak havoc with both clock speed and power consumption. The increased availability of on-chip real estate can be used for storage areas for small programs that are executed very frequently and should not run the risk of eviction from the cache—in essence, on-chip firmware. Performing as many functions in software as is reasonable certainly increases the flexibility of the system, and it also benefits testability and reliability; less logic hardware should result in (statistically) fewer hardware bugs, and though software is no easier to verify than hardware, it is far easier to repair in the field.

On the down side, moving features out of hardware and into software increases code size and thus places more stress on instruction caches, but this may be offset somewhat by increased cache and physical memory sizes. This is a question that we will address in this dissertation.

This thesis investigates the design philosophy stated above as it applies to memory management: which functions of memory management should be performed in hardware and which should be performed in software? For instance, traditional systems have used a hardware structure designed to aid memory management, the *translation lookaside buffer (TLB)*. The TLB is an example of *hardware-oriented design*; it is a specialized hardware structure that performs some dedicated function. In the case of the TLB, the dedicated function is virtual-address translation; the TLB translates virtual addresses to physical ones. The problem that this hardware feature can pose is its effect on memory-system performance; address translation is linked to cache access in that one must have the correct translation resident in the TLB before one can access the contents of the cache. As long as the TLB maps an appreciable amount of the cache, it is not a bottleneck. However, as soon as the cache is significantly larger than the amount of memory that the TLB can map (called the *TLB reach* [Talluri & Hill 1994]), managing the contents of the TLB begins to dominate memory-management costs. Previous studies show that typical well-behaved TLB overheads are on the order of 10% of a system's execution time [Bala et al. 1994, Chen et al. 1992, Nagle et al. 1993, Talluri & Hill 1994, Clark & Emer 1985, Anderson et al. 1991, Huck & Hays 1993, Rosenblum et al. 1995]. Several of these studies have also shown that systems less well-behaved can exhibit much larger TLB overheads—on the order of 50% of total execution time [Anderson et al. 1991, Huck & Hays 1993, Rosenblum et al. 1995]. Like it or not, we have to pay more attention to the TLB.

There is a question begging to be asked: why is this happening? Why does the TLB account for any of the memory overhead? The TLB does not come for free; it is a cache for the operating system's mapping information and as such needs to be loaded with more current or more relevant information from time to time. It is not stateless but rather state-full and its state must be kept consistent with the rest of the processor. This requires management and thus overhead. Today's large working-set sizes require large caches, which in turn require large TLBs; if the TLB is not large enough to map the cache, it can become a performance drain. If the TLB could scale to large sizes as easily as caches, there would be no problem. However, TLBs do not tend to scale as well as caches; it is difficult to make a TLB large without significantly slowing down processor speed or increasing power consumption. One may choose a set-associative organization rather than a fully associative organization; this would address the speed and power consumption problems, but such a design would have a significantly lower hit-rate than a fully associative organization of the same size. One could always increase the size of the set-associative design to obtain a better hit-rate. For example, for exceptionally good performance we would like a split TLB arrangement equivalent in hit-rate to two 128-entry fully associative TLBs [Nagle et al. 1993]. As shown by Nagle et al., this is more or less equivalent to two 4-way set-associative 512-entry TLBs. The chip area required to build this equals the size of a small L1 cache, and if we simply double the L1 cache we can eliminate more overhead than if we increase the size of the TLB; it is not worthwhile to increase the TLB in this way (we will discuss this in more detail in Chapter 6). Another simple solution is to increase the page size, thus increasing the TLB reach by the same factor that one increases the page size. However, Talluri and Hill have shown that this increases working-set size, it is difficult to reconcile with the operating system, and it is less effective at reducing overhead than supporting multiple page sizes [Talluri et al. 1992, Talluri & Hill 1994].

There is another solution. One useful feature of large caches is that they make viable implementation choices that are not viable with small caches. In particular, *software-oriented*

3

*design* becomes viable, in which we eliminate special-purpose hardware that performs some dedicated function and instead perform the same function entirely in software. Software-oriented designs were not in fashion previously, for example three decades ago when virtual memory was developed, since caches and physical memories were not large enough to withstand the competition between the data and instructions needed for the program and the data and instructions needed for the software design. However, now that caches are both large and inexpensive this competition is reduced considerably, and software-oriented design is worth reconsidering.

This dissertation looks at the viability of a software-oriented design for memory management. It shows that one can remove the TLB and the rest of the memory-management unit and perform their equivalent functions efficiently in software. Doing so makes the memory-management design simpler, smaller, and more flexible without a significant impact on performance. We have found that the TLB is unnecessary if one uses large virtually-addressed caches, and it is even possible to increase performance by eliminating the TLB if the caches are large enough. For example, a system with a split 4MB Level-2 cache and a split 256-entry TLB has the same virtual-memory performance as a software scheme with no TLB. Reducing the size of the TLBs by 50% increases the overhead of the hardware scheme by a factor of five.

This makes a software-oriented memory management design a competitive alternative to a hardware-oriented design; it is generally worth paying a small price in performance to get increased flexibility (for example, a hardware-walked page table will always yield better performance than a software-walked page table of similar design, yet most microprocessors today walk the page table in software for increased flexibility). The fact that such flexibility can come without a significant cost in performance is very good news.

Eliminating dedicated special-purpose hardware from processor design saves chip area and reduces power consumption, lowering the overall system cost. Moreover, a flexible design should aid in the portability of system software. A software-oriented design methodology would likely benefit many different microprocessor designs, from general-purpose processors in PC-class and workstation-class computers, to embedded processors where cost tends to have a higher priority than performance. The particular implementation described in the following chapters, which is centered around a virtual cache hierarchy managed by the operating system, is shown to be useful in the areas of real-time systems, shared-memory multiprocessors, architecture emulation, and reconfigurable computing.

#### **1.2 Background and Previous Work in Memory Management Design**

Virtual memory is a technique for managing the resource of physical memory. It provides to the application an illusion of a very large amount of memory—typically much larger than is actually available. Its chief advantage is that it supports the execution of processes only partially resident in memory. In a virtual memory system, only the most-often used portions of a process's address space actually occupy physical memory; the rest of the address space is stored on disk until needed.

Most processors support virtual memory through a hardware *memory management unit* (*MMU*) that translates virtual addresses to physical addresses. The classic MMU design, as seen in the DEC VAX, GE 645, and Intel x86 architectures [Clark & Emer 1985, Organick 1972, Intel 1993], is comprised of two parts: the translation lookaside buffer and a finite state machine. The TLB is an on-chip memory structure that caches the page table; it holds only page table entries. Its job is to speed address translation. If the necessary translation information is on-chip in the TLB, the system can translate a virtual address to a physical address without requiring an access to the page table. In the event that the translation information is not found in the TLB (an event called a *TLB miss*), one must search the page table for the translation and insert it into the TLB before processing can continue. Early designs provided a hardware state machine to perform this activity; in the event of a TLB miss, the state machine would walk the page table, locate the translation information, insert it into the TLB, and restart the computation.

Translation lookaside buffers are fairly large; they usually have on the order of 100 entries, making them several times larger than a register file. They are typically fully associative, and they are often accessed every clock cycle. In that clock cycle they must translate both the I-stream and the D-stream. They can constrain the chip's clock cycle as they tend to be fairly slow, and they are also power-hungry (both are a function of the TLB's high degree of associativity). The finite state machine tends to be a very efficient design as it does not affect the state of the machine. When the system takes a TLB miss, the state of the machine freezes; as opposed to the consequences of taking an interrupt, the contents of the pipeline are unaffected and the reorder buffer need not be flushed. The I-cache is not affected and the D-cache is only affected if the page table is located in cacheable space. So at the very worst, the execution of the state machine will impact a few lines in the D-cache. Otherwise, the system is not penalized at all. Some designs do not even freeze the pipeline; for instance, the Intel Pentium Pro allows instructions that are independent of the faulting instruction to continue processing while the TLB miss is being serviced [Upton 1997]. The pri-

5

mary disadvantage of the state machine is that the page table organization is effectively etched in stone; the system has little flexibility in choosing a design suited to its needs if it is different than the organization expected by the hardware.

Clearly, there are advantages and disadvantages to the classical hardware-oriented design of the memory management unit, which implies that there is room for alternatives. There have been several such alternative designs in the past decade, in which all or part of the memory management unit is replaced by an equivalent software design. The following are a few of the precedents set for software-oriented memory management design.

#### MIPS

The MIPS was one of the first commercial architectures to offer a software-managed TLB [Kane & Heinrich 1992], though the Astronautics Corporation of America holds a patent for a software-managed design [Smith et al. 1988]. The MIPS designers noticed that the general-purpose exception mechanism could be used to handle TLB misses, which would eliminate the need for the on-chip hardware implementing the finite state machine. The MIPS design showed that with reasonably large instruction caches, the finite state machine could be removed without a substantial performance hit. With large caches, the cache competition between the operating system's TLB-miss handler and normal application code did not affect performance significantly.

#### **SPUR**

The Berkeley SPUR project [Ritchie 1985, Hill et al. 1986, Wood et al. 1986] took a different tack on the design of their memory management unit. The designers noticed that when one caches the operating system's page table, there would often be times when a particular page table entry in the TLB would also be present in the on-chip cache. This suggests a waste of on-chip resources, and so the designers decided to eliminate the TLB. They retained the finite state machine. They used a large virtual cache, and in the event that a reference missed the cache, the finite state machine walked the page tables in the virtual cache, performed the translation, and brought the missing datum in from main memory. The SPUR design showed that with a reasonably large data cache, the TLB could be removed without a substantial performance hit. With large caches, the cache competition between the operating system's page table and normal application data did not affect performance significantly.

#### VMP

The VMP multiprocessor [Cheriton et al. 1989, Cheriton et al. 1988, Cheriton et al. 1986] did away with both the TLB and the state machine. The VMP was a bus-based shared-memory multiprocessor organization, with each processor controlling a large virtual cache. The flexibility of the software-managed cache allowed the designers to test cache-coherency protocols in software. In the event of a cache miss, the operating system handled the cache-refill by performing the translation and loading the missing datum off the bus from shared memory, possibly invalidating copies in the caches of other processors. The VMP design showed that with reasonably large caches, the MMU could be eliminated without a substantial performance hit. With large caches, the cache competition between the operating system and normal application instructions and data did not affect performance significantly.

## **1.3** Dissertation Overview

There have been several precedents set for eliminating part or all of the hardware memory management unit. In this thesis we quantify the performance effects of executing its function entirely in software, and we discuss many of the ramifications of doing so.

Chapters 2 and 3 provide a high-level look at memory management. The chapters first paint virtual memory as merely one possible memory management organization out of many viable alternatives. The chapters describe the methods and goals of virtual memory, including typical operating system functions and their implementations, support required of the hardware by the operating system, and examples of how today's processors provide that support.

Chapter 4 presents the experimental methodology used to obtain the performance measurements in this dissertation. Trace-driven simulation of a memory hierarchy is used, with traces taken from the SPEC'95 benchmark suite. The traces include application references and all operating system activity related to TLB-miss handling or cache-miss handling (analogous to TLB-miss handling for a software-managed TLB).

Chapter 5 discusses the details of eliminating the memory management unit and presents some preliminary measurements. The chapter shows that address translation can be performed entirely in software if the operating system handles all Level-2 cache misses. The chapter also discusses how a software-oriented scheme supports the operating system requirements detailed in earlier chapters.

Chapter 6 presents much more detailed performance measurements and compares and contrasts the software-oriented mechanism with other schemes, including contemporary addressing schemes, different cache organizations, and existing multiprocessor organizations. It concludes with The Good News and The Bad News: eliminating memory management hardware can increase system flexibility, but the proposed alternative mechanisms have problems of their own to solve. These include the virtual-cache synonym problem, the overhead of the exception mechanism, the performance hit of multimedia-type applications, and the cost of off-chip Level-2 caches. Chapters 7 through 10 deal with each of these problems in turn.

Chapter 7 describes the problems inherent in using large virtually-addressed caches and provides a simple hardware/software solution that is low-overhead and flexible. The problems arise from the use of *address-space-identifier (ASID) aliasing* and *virtual-address aliasing*, two techniques used to support shared virtual memory that cause increased overhead and possible data inconsistencies in virtual caches. Hardware segmentation is a simple mechanism that, properly used, allows aliasing without the possibility of introducing data inconsistencies. The chapter also discusses how the solution could benefit general systems with memory management units and TLBs.

Chapter 8 provides a first-order cost analysis of the handling of an interrupt and describes a method to allow the hardware to handle certain interrupts specially (including the cache-miss exception required by Chapter 5). It argues that the classic definition of precise interrupts is too restrictive, that a precise interrupt should reflect the ordering of the application's implicit dependency graph (which can have many different partial orders), not necessarily the sequential partial order represented by the static program code. Redefining precise interrupts in this way can reduce the cost of an exception by an order of magnitude.

Chapter 9 addresses the problem of supporting multimedia-type applications—those that show poor temporal locality but good spatial locality. These will cause a cache-miss exception every time a new *cache line* is touched, whereas a processor with a TLB will take a TLB miss every time a new *page* is touched. This could potentially result in an overhead several orders of magnitude larger than that of a hardware-oriented scheme. Solutions include prefetching and direct but secure access to physical memory.

Chapter 10 describes several alternative organizations for main memory that allow one to do away with the Level-2 cache. This would be important for a low-cost or embedded system. These cache-like main memory organizations were hinted at in Chapter 2 while discussing alternative designs for virtual memory.

Chapter 11 concludes.

### **1.4** Scope of the Thesis

The primary contributions of this thesis are the following:

- 1. A detailed discussion of the design of a software-oriented memory-management architecture, including both software and hardware components

- 2. An in-depth performance comparison of five very different memory-management systems: a software-oriented scheme, Mach as implemented on MIPS, Ultrix as implemented on MIPS, an Intel x86 page table and MMU, and the inverted page table of HP-UX

- 3. The presentation of a low-overhead interrupt mechanism for handling memorymanagement-related interrupts

The focus of this thesis is on the design of virtual memory management subsystems (including both hardware and software structures) for very fast uniprocessors. Virtual memory is a programming model that has proven its worth over the last thirty years; it provides an abstraction for addressing memory that simplifies the design and creation of applications at a modest cost in run-time overhead. Though alternatives to virtual memory look promising, we should continue to provide virtual address translation even as clock speeds increase dramatically, placing structures such as the translation lookaside buffer on the list of potentially performance-limiting critical paths. One possible design, as already mentioned, is to eliminate the TLB altogether, providing the abstraction of virtual memory through the combination of virtually-addressed caches and software support in the operating system. This dissertation looks at the relationships between the TLB and structures found in both the architecture and the operating system, explains their purpose, and offers alternative designs. It compares the performance of several very different memory-management designs through trace-driven simulations; the hardware-oriented schemes are given simulated fully-associative TLBs that are extremely large (128 entries in both the I-TLB and the D-TLB, which is as large or larger than any commercially-available TLBs as of this writing), so as to compare a software-oriented scheme to the best hardware schemes possible. The simulations show that the software-oriented scheme performs similarly to the hardware-oriented schemes, and at a reduced cost in die area for Level-1 cache sizes less than 128KB.

## A VIRTUAL MEMORY PRIMER

This chapter provides definitions and descriptions of the terms and mechanisms used in memory management in general, and virtual memory in particular. It begins with a high-level description of virtual memory as one of many possible techniques of memory management.

### 2.1 Introduction

In the ideal world programs are written once, need little help to start running, and while running need little management. As frequently happens when designing a system, not all the desired characteristics can be accommodated at the same time. This results in many different models for organizing a computer system, each of which makes different tradeoffs for different reasons. For example, it is simpler to write an operating system if programs need little management once they are running. Though intuitively straightforward, it typically puts more responsibility on the shoulders of the compiler and programmer. It is simpler to write a compiler if it needs to know very little about the hardware or operating system, which typically makes the operating system more complex. It is simpler for the user if he or she needs to write a program only once to cover many different hardware/operating-system organizations. This also tends to make the operating system and runtime support system (including the microarchitecture) more complex.

Each of these models represents a different priority, a different tradeoff of complexity for ease of use or ease of design. Virtual memory is simply one of many possible models—one in which the tradeoff buys simplicity in the design of applications at a reasonably low overhead in performance (time) and memory (space).

10

Figure 2.1: Memory management models

There are at least three ways to manage physical memory. The first, *physical addressing*, uses physical addresses in the program itself. The second, *base+offset addressing*, uses relative offsets in the program and adds the physical base address at runtime. The third, *virtual addressing*, uses any appropriate naming scheme in the program (usually relative offsets) and relies upon the operating system and hardware to translate the references to physical addresses at runtime. Traditional virtual memory is therefore a small subset of the virtual addressing model of memory management.

### 2.2 What Is Virtual Memory?

There are many different models for managing physical memory; what exactly do these different models look like? The simplest model of program creation and execution is perhaps to determine what memory is available, reserve it so that no other process uses it, and write a program to use the memory locations reserved. This allows the process to execute without any management from the operating system and is therefore very low-overhead. However, this requires one to rewrite the program every time it is run—a tedious task, but one that can be left to the operating system. At process start-up, the operating system can modify every pointer reference in the application (including loads, stores, and absolute jumps) to reflect the address at which the program is loaded. The program as it resides in main memory references itself directly, and so contains

| Program's View of the World: |         |  |         |  |  |  |

|------------------------------|---------|--|---------|--|--|--|

| Physical Memory:             | Program |  | Program |  |  |  |

|                              |         |  |         |  |  |  |

| Reality:                     |         |  |         |  |  |  |

| Physical Memory:             | Program |  | Program |  |  |  |

#### Figure 2.2: The Physical Addressing model of program creation and execution

In this model, a program's view of itself in its environment (physical memory) is equivalent to reality; a program contains knowledge of the structure of the hardware. A program can be entirely contiguous in memory, or it can be split into multiple pieces, but the locations of all parts of the program are known to the program's code and data.

| Program's View of the World: |         |         |   |         |  |  |

|------------------------------|---------|---------|---|---------|--|--|

| Region 1:                    | Program |         |   |         |  |  |

| Region 2:                    | Program |         |   |         |  |  |

| Reality:                     |         |         | 1 |         |  |  |

| Physical Memory:             |         | Program |   | Program |  |  |

|                              |         |         |   |         |  |  |

**Figure 2.3: The Base+Offset Addressing model of program creation and execution** In this model, a program's view of itself in its environment is not equivalent to reality, but it sees itself as a set of contiguous regions. It does not know where in physical memory these regions are located, but the regions must be contiguous; they cannot be fragmented.

implicit knowledge about the structure and organization of the physical memory. This model is depicted in Figure 2.2; a program sees itself exactly as it resides in main memory.

A second model is to write the program once using load and store addresses that are offsets from the beginning of the program—a variable that will be stored in a known hardware register. At runtime, one can load the program wherever it fits and place its location in the register so that all loads and stores go to the correct locations. The disadvantage of this scheme is that without extra hardware the program must be contiguous in memory, or divided into a set of contiguous regions (each with its location stored in a hardware register or saved in a well-known memory location). This model is depicted in Figure 2.3; a process sees itself as a contiguous region or set of contiguous regions. The organization of the hardware is not exposed to the static program.

| Program's View of the World: |         |  |         |  |  |  |  |

|------------------------------|---------|--|---------|--|--|--|--|

| "Virtual" Memory:            | Program |  | Program |  |  |  |  |

|                              |         |  |         |  |  |  |  |

| Reality:                     |         |  |         |  |  |  |  |

| Physical Memory:             |         |  |         |  |  |  |  |

**Figure 2.4: The Virtual Addressing model of program creation and execution** In this model, a program's view of itself in its environment has virtually nothing to do with reality; a program can consider itself a collection of contiguous regions or a set of fragments, or one large monolithic program. The operating system considers the program nothing more than a set of uniform virtual pages, and loads them as necessary into physical memory. The entire program need not be resident in memory, and it need not be contiguous.

A third model is to write the program as if it is loaded at physical memory location zero, load the program wherever it fits (not necessarily location zero), and use some as yet undefined mechanism to translate the program's addresses to the equivalent physical addresses while it is running. This model is depicted in Figure 2.4. The program is completely independent of the hardware organization. The advantage of this scheme is that one never needs to rewrite the program, and it can be fragmented in main memory—bits and pieces of the program can lie scattered throughout main memory, and the program need not be entirely resident to execute. The disadvantage is the potential overhead of the translation mechanism.

#### 2.2.1 Three Models of Addressing: Physical, Base+Offset, and Virtual

The three models can be called *physical addressing*, *base+offset addressing*, and *virtual addressing*. Their structure is compared in Figure 2.5. The primary difference between the three is whether or not the hardware organization is exposed to either the program or the process. We have made a distinction between the two to clarify the differences between the three models: a *program* is a static file on disk or in memory, and a *process* is a running (dynamic) program. The first scenario, *physical addressing*, has the program using physical addresses to reference memory locations in its address space, and thus the program contains some knowledge of the underlying hardware organization. The dynamic execution of the program uses these same addresses, so the process also contains knowledge of the underlying hardware. The second scenario, *base+offset addressing*, has the program using relative addresses from a variable base, which represents little knowledge of the underlying hardware except support in the form of an addressing mode or trans-

|                                                                           |                    | Program                                                                                                     |          |                                                                                                             |                           |

|---------------------------------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------|---------------------------|

| Physical Memory:                                                          |                    |                                                                                                             |          |                                                                                                             |                           |

| <b>CODE:</b> c = a + b; gotc                                              | <b>0</b><br>LABEL; | 0x100000                                                                                                    |          |                                                                                                             | MAX<br>PHYSICAL<br>MEMORY |

| PHYSICAL<br>ADDRESSING                                                    | Program:           | load \$r1, 0x100000<br>load \$r2, 0x100004<br>add \$r3, \$r2, \$r1<br>store \$r3, 0x100008<br>jump 0x10A000 | Process: | load \$r1, 0x100000<br>load \$r2, 0x100004<br>add \$r3, \$r2, \$r1<br>store \$r3, 0x100008<br>jump 0x10A000 |                           |

|                                                                           |                    |                                                                                                             | 1        |                                                                                                             |                           |

| BASE+OFFSET<br>ADDRESSING<br>(the value<br>0x100000 is<br>stored in \$rB) | Program:           | load \$r1, 0+\$rB<br>load \$r2, 4+\$rB<br>add \$r3 \$r2 \$r1<br>store \$r3 8+\$rB<br>jump 0xA000+\$rB       | Process: | load \$r1, 0x100000<br>load \$r2, 0x100004<br>add \$r3, \$r2, \$r1<br>store \$r3, 0x100008<br>jump 0x10A000 | Hardware-<br>Dependent    |

| VIRTUAL                                                                   | Program:           | load \$r1, 0                                                                                                | Process: | load \$r1, 0                                                                                                | Hardware-                 |

| ADDRESSING                                                                | og.diii.           | load \$r7, 0<br>add \$r2, 4<br>add \$r3 \$r2 \$r1<br>store \$r3 8<br>jump 0xA000                            |          | load \$r2, 4<br>add \$r3 \$r2 \$r1<br>store \$r3 8<br>jump 0xA000                                           | Independent               |

#### Figure 2.5: Comparison of the three models

This illustrates the similarities and differences between the various models of addressing using a somewhat contrived and simplistic example. A program is loaded into main memory to observe the behavior of each model executing a simple piece of code. For each model, the illustration shows what its code looks like, as stored in memory, as well as the dynamic execution stream generated by the process. In the Physical and Base+Offset models, the dynamic execution of the program uses physical addresses. In the Virtual model, no physical addresses are produced by the executing program; its virtual addresses are translated to physical ones by the hardware and operating system.

lation mechanism. Here, the program does not know anything about the underlying hardware but the process does. The static program is written with offsets from the beginning of its address space, but the dynamic program, the process, generates a stream of references that address physical memory directly. Therefore the process implicitly knows the structure of physical memory. In the third scenario, *virtual addressing*, the program is written as before with offsets from the start of its address space, and the running process uses these virtual addresses. The process generates addresses that are completely independent of the memory organization; it can use arbitrary names to reference locations in its address space, provided the names are consistent and constitute a function—i.e., for every name there is only one corresponding physical location. These names are translated by the operating system and/or hardware after the process generates them, and so neither the program nor the process contain any knowledge of the memory system.

The design of the operating system determines which category a given system is in; the categorization has little to do with the hardware. Physical addressing can be implemented on any

architecture, base+offset addressing can be implemented on any architecture that has the appropriate addressing mode or address translation hardware, and virtual addressing can be implemented on any architecture including those that do not explicitly support virtual addressing. The following sections discuss the relative merits of the three models.

**Physical Addressing.** In physical addressing, process execution behaves differently (from the point of view of the process) every time the program is executed on a machine with a different memory organization, and is likely to behave differently every time it is executed on the same machine with the same organization, since the program is likely to be loaded at a different location every time. Physical addressing systems outnumber virtual addressing systems: an example is the operating system for the original Macintosh, which did not have the benefit of a memory-management unit [Apple Computer, Inc. 1992]. Though newer Macintosh systems have an optional virtual memory implementation, many applications require that the option be disabled during their execution.

The advantages of the physically-addressed scheme are its simplicity and performance. The disadvantages include slow process start-up and decreased flexibility. At process start-up, the entire text area (and possibly the data area, if it contains self-referential pointers at compile time) must be edited to reflect the location of the process in main memory. While this is easily amortized over the runtime of a long-running process, it is not clear whether the speed advantages outweigh this initial cost for short-running programs. Decreased flexibility also can lead to performance loss; since the program cannot be fragmented or partially loaded, the entire program file must be read into main memory for the program to execute. This can create problems for systems with too little memory to hold all the active processes; entire processes will be swapped in and out, whether their working set is large or small. Clearly, it does not benefit performance if pages that the process never touches are constantly swapped in and out of memory.

**Base+Offset Addressing.** In base+offset addressing, like physical addressing, process execution behaves differently every time the program is executed on a machine with a different memory organization, and it is likely to behave differently every time it is executed on the same machine with the same organization, since the program is likely to be loaded at a different location every time. Base+offset systems far outweigh all other systems combined: an example is the DOS/Windows system [Duncan et al. 1994]. The Intel architecture has a combined memory management architecture that places a base+offset design on top of a virtual addressing design. The base+offset design is built into the addressing mechanism, so the program file need not explicitly reference any base register: the Intel architecture provides several registers to hold "segment" offsets, so a program can be composed of several regions, each of which must be complete and contiguous, but that need not touch each other.

The advantages of this scheme are that the code needs no editing at process start-up and the performance is equal to that of the physical addressing model. The disadvantages of the scheme are similar to physical addressing: a region must not be fragmented in main memory, though the Intel design mitigates this somewhat by allowing a program to be fragmented into several smaller pieces, by adding an orthogonal paged memory management subsystem.

**Virtual Addressing.** In virtual addressing, process execution behaves identically every time the program is executed, even if the machine's organization changes, and even if the program is run on different machines with wildly different memory organizations. Virtual addressing systems include nearly all academic systems, most Unix-based systems, and many Unix-influenced systems such as Windows NT, OS/2, and Spring [Custer 1993, Deitel 1990, Hamilton & Kougiouris 1993, Mitchell et al. 1994].

The advantages of the system are that the code need not be edited on loading, one can run programs on systems with very little memory, and one can easily juggle many programs in physical memory because fragmentation of a program is allowed. In contrast, systems that require process regions to remain contiguous in physical memory might end up unable to execute processes because no single unused region is large enough to hold the process, even if many scattered unused areas together would be large enough. Indeed, this is the advantage of adding a virtual-addressing layer to the Intel memory management architecture: it allows programs to be fragmented at the page level, a benefit large enough to overcome the performance overhead of a second level of address translation in the x86. The disadvantage of the virtual addressing scheme is the increased amount of space required to hold the translation information, and the increased path length between address generation and data availability. These figures have traditionally been no more than a few percent in time and space.

Now that the cost of memory has decreased significantly, it is quite possible the schemes that waste memory for better performance (physical and base+offset addressing) are the best

choices. Memory is cheap, and perhaps the best design is one that simply loads every program entirely into memory and assumes that any memory shortage will be fixed by the addition of more DRAM. However, the general consensus is that virtual addressing is more flexible than the other schemes, and we have come to accept its overhead as reasonable. It (arguably) provides a more intuitive and bug-free paradigm for programming and process management than schemes which rely on the organization of the hardware. This thesis work therefore only delves into virtual memory; it does not consider designs that fall into other categories.

### 2.2.2 The Virtual Addressing Continuum

In the virtual addressing model, processes execute in imaginary address spaces that are mapped onto physical memory by the operating system, therefore the processes generate instruction fetches and loads and stores using imaginary or "virtual" names for their instructions and data. The ultimate home for the process's address space is *backing store*, usually a disk drive; this is where the process's instructions and data come from and where all of its permanent changes go to. Every hardware memory structure between the CPU and the backing store is a cache for the instructions and data in the process's address space. This includes main memory—main memory is really nothing more than a cache for a process's virtual address space. A cache operates on the principle that a small, fast storage device can hold the most important data found on a larger, slower storage device, effectively making the slower device look fast. The large storage area in this case is the process address space initially comes from the program file stored on disk, or is created on demand and defined to be zero. Figure 2.6 illustrates.