US008549207B2

## (12) United States Patent

Satpathy et al.

#### (54) CROSSBAR CIRCUITRY FOR APPLYING AN ADAPTIVE PRIORITY SCHEME AND METHOD OF OPERATION OF SUCH CROSSBAR CIRCUITRY

(75) Inventors: Sudhir Kumar Satpathy, Ann Arbor, MI (US); David Theodore Blaauw, Ann Arbor, MI (US); Trevor Nigel Mudge, Ann Arbor, MI (US); Dennis Michael

Sylvester, Ann Arbor, MI (US)

(73) Assignee: The Regents of the University of

Michigan, Ann Arbor, MI (US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 401 days.

This patent is subject to a terminal disclaimer.

(21) Appl. No.: **12/926,462**

(22) Filed: Nov. 18, 2010

(65) **Prior Publication Data**

US 2011/0138098 A1 Jun. 9, 2011

#### Related U.S. Application Data

- (63) Continuation-in-part of application No. 12/458,511, filed on Jul. 14, 2009, now Pat. No. 8,230,152, which is a continuation-in-part of application No. 12/379,191, filed on Feb. 13, 2009, now Pat. No. 8,108,585.

- (51) Int. Cl.

G06F 13/00 (2006.01)

G06F 9/32 (2006.01)

H03K 17/00 (2006.01)

H04Q 3/00 (2006.01)

H04Q 11/00 (2006.01)

G11C 19/00 (2006.01)

H04L 12/50 (2006.01)

- (52) U.S. Cl.

# (10) Patent No.: US 8,549,207 B2 (45) Date of Patent: \*Oct. 1, 2013

(58) Field of Classification Search

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

(Continued)

#### FOREIGN PATENT DOCUMENTS

EP 0 744 879 11/1996 EP 1089461 A2 \* 4/2001 (Continued)

OTHER PUBLICATIONS

DaeHo Seo; Thottethodi, M., "Table-lookup based Crossbar Arbitration for Minimal-Routed, 2D Mesh and Torus Networks," Parallel

and Distributed Processing Symposium, 2007. IPDPS 2007. IEEE International, pp. 1,10, Mar. 26-30, 2007.\*

#### (Continued)

Primary Examiner — Faisal M Zaman

(74) Attorney, Agent, or Firm — Nixon & Vanderhye P.C.

#### (57) ABSTRACT

Crossbar circuitry has an array of data input and output paths where the data output paths are transverse to the data input paths. At each intersection between a data input path and a data output path, a crossbar cell is provided which includes a configuration storage circuit programmable to store a routing value, a transmission circuit, and an arbitration circuit. In a transmission mode of operation, the transmission circuit is responsive to the routing value being a first value, indicating that the data input path should be coupled to the data output path, to detect the data input along the data input path, and to output an indication of that data on the data output path at the associated intersection. In an arbitration mode of operation, the arbitration circuitry is operable to selectively modify the voltage on said plurality of bit lines in order to apply an adaptive priority scheme.

#### 31 Claims, 32 Drawing Sheets

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 5 500 014    |               | 6/1006  | ***              |         |

|--------------|---------------|---------|------------------|---------|

| 5,530,814    |               | 6/1996  | Wong et al.      |         |

| 5,689,644    | A             | 11/1997 | Chou et al.      |         |

| 5,781,717    | A             | 7/1998  | Wu et al.        |         |

| 5,857,111    | A             | 1/1999  | Oda              |         |

| 5,896,516    | A *           | 4/1999  | Powell et al     | 710/317 |

| 5,991,296    | A             | 11/1999 | Mu et al.        |         |

| 6,125,429    | A *           | 9/2000  | Goodwin et al    | 711/143 |

| 6,356,111    | B1            | 3/2002  | Moss             |         |

| 6,690,597    | B1            | 2/2004  | Perlov et al.    |         |

| - , ,        | B1 *          | 3/2004  | Abu-Lebdeh et al | 710/317 |

| 6,771,162    | B1            | 8/2004  | Moss             |         |

| - , ,        | B2            | 10/2004 | Sota             |         |

| - ) )        | B2            | 9/2005  | Chan             |         |

| 7,020,131    | В1            | 3/2006  | Yun et al.       |         |

|              | B2 *          | 1/2007  | Dell et al       |         |

| 7,178,005    | B1 *          | 2/2007  | Jordan et al     |         |

| , ,          | B2 *          | 7/2007  | Cummings et al   |         |

| 7,424,013    | B1 *          | 9/2008  | Yun et al        | 370/389 |

| 7,643,493    | B1            | 1/2010  | Sayrafian-Pour   |         |

| 7,657,693    | B2            | 2/2010  | Singh et al.     |         |

|              | B1 *          | 3/2011  | MacAdam          |         |

| 8,108,585    | B2 *          | 1/2012  | Satpathy et al   | 710/317 |

| 8,155,134    | B2 *          | 4/2012  | Fairhurst et al  | 370/413 |

| 8,230,152    | B2 *          | 7/2012  | Satpathy et al   | 710/317 |

| 8,255,610    | B2 *          | 8/2012  | Satpathy et al   | 710/317 |

| 2003/0221043 | A1*           | 11/2003 | Sota             |         |

| 2004/0047334 | A1*           | 3/2004  | Francois et al   | 370/351 |

| 2004/0062238 | A1*           | 4/2004  | Yoshizawa et al  | 370/360 |

| 2004/0083326 | A1*           | 4/2004  | Wang et al       | 710/317 |

| 2004/0120337 | A1            | 6/2004  | Jun et al.       |         |

| 2005/0097256 | A1*           | 5/2005  | Jones            | 710/316 |

| 2006/0031625 | A1*           | 2/2006  | Chan             | 710/316 |

| 2008/0186961 | A1*           | 8/2008  | Yun et al        | 370/360 |

| 2009/0034517 | A1*           | 2/2009  | Yang et al       | 370/357 |

| 2009/0089478 | A1*           | 4/2009  | Singh et al      | 710/317 |

| 2010/0090189 | A1            | 4/2010  | Savransky        |         |

| 2010/0211719 | A1            | 8/2010  | Satpathy et al.  |         |

| 2011/0138098 | $\mathbf{A}1$ | 6/2011  | Satpathy et al.  |         |

| 2011/0181307 | A1*           | 7/2011  | Kuekes           | 324/722 |

| 2012/0254491 | A1*           | 10/2012 | Satpathy et al   | 710/116 |

|              |               |         |                  |         |

#### FOREIGN PATENT DOCUMENTS

| EP | 1115230       | A2 | * | 7/2001  |

|----|---------------|----|---|---------|

| GB | 2 261 131     |    |   | 10/1991 |

| GB | 2261131       | Α  | * | 5/1993  |

| JР | 2000-22728    |    |   | 1/2000  |

| JР | 2000022728    | Α  | * | 1/2000  |

| JР | 2001197068    | Α  | * | 7/2001  |

| JР | 2002-342306   |    |   | 11/2002 |

| JР | 2004-78713    |    |   | 3/2004  |

| JР | 2008-46997    |    |   | 2/2008  |

| WO | WO 9935879    | A1 | * | 7/1999  |

| WO | WO 2004049645 | A1 | * | 6/2004  |

| WO | WO2005/020066 |    |   | 3/2005  |

|    |               |    |   |         |

#### OTHER PUBLICATIONS

Minkenberg, C.; Abel, F.; Gusat, M., "Reliable control protocol for crossbar arbitration," Communications Letters, IEEE, vol. 9, No. 2, pp. 178,180, Feb. 2005.\*

Minkenberg, C.; Iliadis, I.; Abel, F., "Low-latency pipelined crossbar arbitration," Global Telecommunications Conference, 2004. Globecom '04. IEEE , vol. 2, pp. 1174,1179 vol. 2, Nov. 29-Dec. 3, 2004.\*

Nitta, C.; Farrens, M.; Akella, V., "DCAF—A Directly Connected Arbitration-Free Photonic Crossbar for Energy-Efficient High Performance Computing," Parallel & Distributed Processing Symposium (IPDPS), 2012 IEEE 26th International, pp. 1144,1155, May 21-25, 2012.\*

"NB9103112: Neural-Network Controller for Large Crosspoint Networks" Mar. 1, 1991, IBM, IBM Tevhnical Disclosure Bulletin, vol. 33, Iss. 10B, pp. 112-116.

"NB9103106: Hierarchical Neural Network-Based Controller for Crosspoint Networks" Mar. 1, 1991, IBM, IBM Technical Disclosure Bulletins, vol. 33, Iss. 10B, pp. 106-109.

A. Marrakchi et al, "A Neural Net Arbitrator for Large Crossbar Packet-Switches" IEEE Transactions on Circuits and Systems, vol. 36, No. 7, Jul. 1989, pp. 1039-1041.

J. Ghosh et al, "Neural Networks for Fast Arbitration and Switching Noise Reduction in Large Crossbars" IEEE Transactions on Circuits and Systems, vol. 38, No. 8, Aug. 1991, pp. 895-904.

Notice of Allowance mailed Mar. 22, 2012 in co-pending U.S. Appl. No. 12/458.511.

Golshan et al., "A novel reduced swing CMOS BUS interface circuit for high speed low power VLSI systems", *IEEE Explore*, Jan. 22, 2009, pp. 351-354.

Chang et al., "A 50 Gb/s 32×32 CMOS Crossbar Chip using Asymmetric Serial Links", Computer System Laboratory, Stanford University, Apr. 1999, (4 pages).

Wu et al., "A 2Gb/s 256 \* 256 CMOS Crossbar Switch Fabric Core Design using Pipelined MUX", *IEEE*, Jul. 2002, pp. II-568-II-571. Wijetunga, "High-performance crossbar design for system-on-chip", 3<sup>rd</sup> *IEEE International Workshop*, Jun. 2003, (6 pages).

Borgatti et al., "A Multi-Context 6.4Gb/s/Channel On-Chip Communication Network Using 0.18µm Flash-EEPROM Switches and Elastic Interconnects", *IEEE International Solid-State Circuits Conference*, Sep. 2003, (3 pages).

Chi et al., "Decomposed Arbiters for Large Crossbars with Multi-Queue Input Buffers", IEEE International Conference on Computer Design, Oct. 14-16, 1991, pp. 233-238.

Delgado-Frias et al., "A VLSI Crossbar Switch with Wrapped Wave Front Arbitration", IEEE Transactions on Circuits and Systems, vol. 50, Issue 1, Jan. 2003, pp. 135-142.

Kavaldjiev et al., "A Virtual Channel Router for On-chip Networks", IEEE International SoC Conference, Sep. 12-15, 2004, pp. 289-293. Shin et al, "Round-robin Arbiter Design and Generation", International Symposium on System Synthesis, 2002, pp. 243-248.

Molnar et al., "Simple Circuits that Work for Complicated Reasons", International Symposium on Advanced Research in Asynchronous Circuits and Systems, 2000, 12 pages.

Josephs et al., "CMOS Design of the Tree Arbiter Element", IEEE Transactions on VLSI systems, vol. 4, Issue 4, Dec. 1996, pp. 472-476.

Plummer, "Asynchronous Arbiters", IEEE Transactions on Computers Archive, vol. 21, Issue 1, Jan. 1972), pp. 37-42.

UK Search Report dated Apr. 16, 2010 for GB 1000172.5.

<sup>\*</sup> cited by examiner

FIG. 5 (continued)

FIG. 6 (continued)

FIG. 10D

FIG. 11D

FIG. 14

## **ENCODER:**

FIG. 15A

## DECODER:

FIG. 15B

FIG. 15C

FIG. 15D

FIG. 16

FIG. 17A

FIG. 17B

1

#### CROSSBAR CIRCUITRY FOR APPLYING AN ADAPTIVE PRIORITY SCHEME AND METHOD OF OPERATION OF SUCH CROSSBAR CIRCUITRY

This application is a continuation-in-part of U.S. application Ser. No. 12/458,511 filed Jul. 14, 2009 now U.S. Pat. No. 8,230,152, which is a continuation-in-part of U.S. application Ser. No. 12/379,191 filed Feb. 13, 2009 now U.S. Pat. No. 8,108,585, the entire contents of each of which are hereby incorporated by reference.

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates to crossbar circuitry for applying an adaptive priority scheme, and a method of operation of such crossbar circuitry.

#### 2. Description of the Prior Art

A crossbar circuit is a switch infrastructure for connecting 20 multiple inputs to multiple outputs in a matrix manner. Accordingly, crossbar circuitry can be used to interconnect a plurality of source circuits and a plurality of destination circuits such that data input to the crossbar circuitry from any of the plurality of source circuits can be output to any of the plurality of destination circuits. Crossbar circuits can be used in a variety of implementations. For example, in a data processing system implementation, such crossbar circuitry can be used to interconnect a plurality of processors used to perform data processing operations on data values with a 30 plurality of memory devices used to store those data values, thereby allowing the data values from any memory device to be routed to any processor.

Known techniques for producing crossbar circuits require a large area for the crossbar circuitry due to the components 35 required to form the crossbar circuitry and the significant number of control lines required for routing control signals to those components, and also consume significant power. Further, their complexity tends to grow rapidly with size, making many of the known techniques impractical for use with crossbar circuits required to interconnect a large number of source circuits with a large number of destination circuits. Some known techniques are discussed below.

The article "A 50 Gb/s 32×32 CMOS Crossbar Chip using Asymmetric Serial Links" by K Chang et al, 1999 Sympo- 45 sium on VLSI Circuits, Digest of Technical Papers, Pages 19 to 22, and the article "A 2 Gb/s 256×256 CMOS Crossbar Switch Fabric Core Design using Pipelined MUX" by T Wu et al, IEEE International Symposium on Circuits and System, 2002, Pages 568 to 571, describe crossbar circuits using a 50 hierarchical arrangement of multiplexers to enable the routing of data from any input source to any output destination. However, such MUX-based crossbar circuits are relatively large in size, and have a large power consumption. Further, they typically require a considerable number of control lines 55 in order to control the various multiplexers. Such MUX-based designs are not typically scalable with an increase in the number of inputs and outputs to be supported, at least in part because it becomes increasingly difficult as the size increases to route the necessary control signals to the various multi- 60 plexers. Further, if the input data is multi-bit data routed over an input bus, the routing of the data paths themselves becomes very complex.

The article "A Novel Reduced Swing CMOS Bus Interface Circuit for High Speed Low Power VLSI Systems" by R Golshan et al, IEEE International Symposium on Circuits and System, Pages 351 to 354, 1994, describes an X-Y style

2

crossbar circuit where the input paths pass in a horizontal direction and the output paths pass in a vertical direction. At the intersection between each input path and output path, a storage element in the form of a flip-flop circuit is provided whose output controls a transistor used to couple the input path to the output path. However, such a design requires a large number of control lines to program the various flip-flops in order to configure the crossbar circuit to perform the required routing. Further, the input data provided on an input data path is used to drive the output data on the relevant output data path. As the crossbar circuit becomes larger to accommodate larger numbers of inputs and outputs, the capacitance of the output data paths increases, and accordingly it is necessary to provide larger drive transistors on the inputs in order to overcome the increased capacitance. In addition, the coupling transistor driven by the flip-flop at the interconnection between a data input path and a data output path also needs to increase in size as the crossbar circuit increases in size. Further, it will typically be necessary to include one or more buffers in the data output paths as the crossbar circuitry increases in size. All of these factors give rise to significant problems in layout of the elements of the crossbar circuit and the associated control lines, particularly as the crossbar circuit increases in size to accommodate more inputs and outputs. Accordingly, this approach becomes complex and is not scalable.

The article "High-Performance Crossbar Design for System-On-Chip" by P Wijetunga, Proceedings of the Third IEEE International Workshop on System-On-Chip for Real-Time Applications, 2003, describes a crossbar design employing a pass-transistor chain as transmission circuitry to be located at each intersection between the data input paths and the data output paths. When the pass-transistor chain is required to couple the input data to the output data path, a current sensing circuit located on the output data path is used to detect the input data value. A significant disadvantage of this design is that it consumes large power due to the requirement for current sensing devices to be located on each output path. Further, a large number of control signals need routing within the crossbar circuitry, and indeed those control signals will dominate the routing requirements as the crossbar circuit increases in size to accommodate more inputs and outputs. Hence, again, this design is not readily scalable to larger designs of crossbar circuitry.

The article "A Multi-Context 6.4 Gb/s/Channel On-Chip Communication Network using 0.18 µm Flash-EEPROM Switches and Elastic Interconnects" by M Borgatti et al, ISSCC 2003, Session 26, Embedded and Digital Systems, Paper 26.5, describes a programmable crossbar implemented using a matrix of modified flash-EEPROM devices. However, as is clear from Figure 26.5.6, the number of memory cells involved in routing a data input from a source device to a destination device depends on where those devices are connected into the crossbar, and accordingly the timing for signals passing through the crossbar is not deterministic. Further, a large number of control lines will be required to enable programming of the various flash-EEPROM cells, and a significant amount of time will be required to program those various flash-EEPROM cells. Any reconfiguration of the crossbar device will hence also take a significant time.

Accordingly, such a design of crossbar is complex, and will increase in complexity as more input devices and output devices need to be supported by the crossbar, due to the proliferation in control lines required. Further, since the timing of the crossbar is not deterministic, this will make the crossbar design inappropriate for certain implementations.

In summary, it will be appreciated from the above discussions that existing crossbar designs typically involve complex routing of control signals, with that complexity rapidly increasing as the size of the crossbar increases. Often the designs consume significant power consumption and lack 5 scalability, due partly to the number of control lines required, and partly due to the need to increase the size of certain components provided within the crossbar as the size of the crossbar increases.

Commonly owned US published patent application 2010/ 10 0211719, the entire contents of which are hereby incorporated by reference, describes a crossbar circuit design where routing patterns are cached locally at crosspoints in the crossbar and are then used to route data. This significantly reduces routing congestion when producing the wiring layout for the 15 crossbar circuit. The design is readily scalable, and hence the crossbar circuitry can be readily utilised even where the number of source circuits and destination circuits to be connected to the crossbar circuitry is large. Further, the design produces a regular layout providing a fixed latency for the transfer of 20 hierarchical approach towards making a large crossbar switch data through the crossbar circuitry.

Another issue in crossbar design is how to provide the crossbar with collision detection and resolution abilities. Multiple requests for the same destination in a switching fabric is termed a collision. With increasing number of 25 sources and destinations, collisions get more frequent. Under such circumstances, arbitration becomes a bottle-neck in the overall efficiency of the crossbar circuitry.

Most contemporary switching fabrics consist primarily of two modules: a crossbar to transmit data, and an arbiter to 30 configure the crossbar. In such an implementation, the source circuits send requests to the arbiter for channels. The arbiter samples all requests and using some priority assignment scheme, grants some or all of the requests and configures the crossbar accordingly. This scheme poses two major problems 35

- 1) Routing all request signals from the source circuits to the arbiter, and all the grant signals back, becomes increasingly difficult for larger systems; and

- 2) The arbiter needs to have knowledge of all incoming 40 requests as well the current state of the crossbar, before it can make a decision. Monitoring the state of the crossbar every cycle requires additional logic as well as interconnects. This contributes to additional delay.

A number of attempts have been made to address the scal- 45 ability and arbitration delay of packet switching networks. In the article by Chi H. et. al. entitled "Decomposed Arbiters for Large Crossbars with Multi-Queue Input Buffers," IEEE International Conference on Computer Design, 14-16 Oct. 1991, pages: 233-238, the authors discuss decomposing arbiters, so that some requests can be granted before the arbitration process completes. However, the worst case arbitration delay still remains the same. In general, the arbitration delay grows linearly with size.

In the article by Delgado-Frias et. al. entitled "A VLSI 55 Crossbar Switch with Wrapped Wave Front Arbitration," IEEE Transactions on Circuits and Systems, Volume 50, Issue 1, January 2003 Pages: 135-141, and the article by Kavaldjiev N. et. al. entitled "A Virtual Channel Router for On-chip Networks," IEEE International SoC Conference, 12-15 Sep. 60 2004, pages: 289-293, the authors discuss the handling of arbitration within a crossbar. However, the disclosed implementations are not scalable and are restricted to a crossbar of size 4\*4.

In the article by Shin E. et. al. entitled "Round-robin Arbi- 65 ter Design and Generation," International Symposium on System Synthesis, 2002, pages: 243-248, the authors propose

a tool to generate a round robin arbiter. The approach is hierarchical, attempting to make a 32\*32 switch out of 4\*4

In the article by William W. Plummer entitled "Asynchronous Arbiters", IEEE Transactions on Computers Archive Volume 21, Issue 1 (January 1972) Pages 37-42, the article by Charles E. Molnar et. al. entitled "Simple Circuits that Work for Complicated Reasons," International Symposium on Advanced Research in Asynchronous Circuits and Systems, 2000. (ASYNC 2000) Proceedings, and the article by Mark B. Josephs et. al. entitled "CMOS Design of the Tree Arbiter Element," IEEE Transactions on VLSI systems, Volume 4, Issue 4, December 1996 Page(s):472-476, some asynchronous techniques for arbitration are described. These designs exploit meta-stability to achieve randomness. However, delay in meta-stable systems can become high at times, thereby restricting their use in real time systems that require guaranteed throughput.

In summary, many solutions available in literature take a using 2\*2 or 4\*4 switches. Hence, the delay grows linearly with the size of the crossbar switch. This leaves no room for voltage scaling in wide and parallel systems (SIMD/MIMD type applications).

Further, in previous attempts to integrate the arbiter and the crossbar together, such as for example discussed in the earlier mentioned article "A Virtual Channel Router for On-chip Networks," IEEE International SoC Conference, 12-15 Sep. 2004, pages: 289-293, it has only been possible to bring them spatially close. However, the logic and interconnect for both functionalities have remained exclusive.

In conventional implementations, collision detection and resolution is done hierarchically. This is achieved in multiple stages of arbitration logic, wherein after each stage the number of requests is reduced by a certain fraction.

Commonly owned US published patent application US 2010/0211720, the entire contents of which are hereby incorporated by reference, describes a self-arbitrating design of crossbar circuitry that enables a very efficient resolution of conflicts to be performed by applying a predetermined priority scheme, whilst providing a very regular design, with uniform delay across all paths, and which requires significantly less control lines that typical prior art crossbar designs. Such crossbar circuitry is readily scalable to form large crossbars.

However, certain types of priority scheme are still difficult to implement efficiently, for example adaptive priority schemes where the relative priorities of the source circuits change between each application of the adaptive priority scheme. US 2010/0211720 proposed the use of a priority configuration module which, in a priority assignment mode of operation, was able to reprogram the values in selected priority storage circuits of the crossbar. It was also identified that such a priority configuration module could be made adaptive by monitoring activity of the crossbar and determining how to update the priority storage circuits dependent on that analysis. However, such an approach impacts efficiency of the crossbar for a number of reasons.

Firstly it is necessary to enter a dedicated priority assignment mode of operation in order to reprogram the priority storage circuits, thereby causing clock cycles to be spent purely performing the priority update process. Typically it is also only possible at one time to reprogram the storage circuits of the crossbar cells connected to one data output path. Furthermore, for the adaptive priority configuration module, it is necessary first to extract information from the crossbar indicative of the activities of the crossbar, then to analyse that extracted information, and then to input the revised priority

data into the crossbar for storage within the relevant priority storage circuits, thereby leading to an inefficient update process

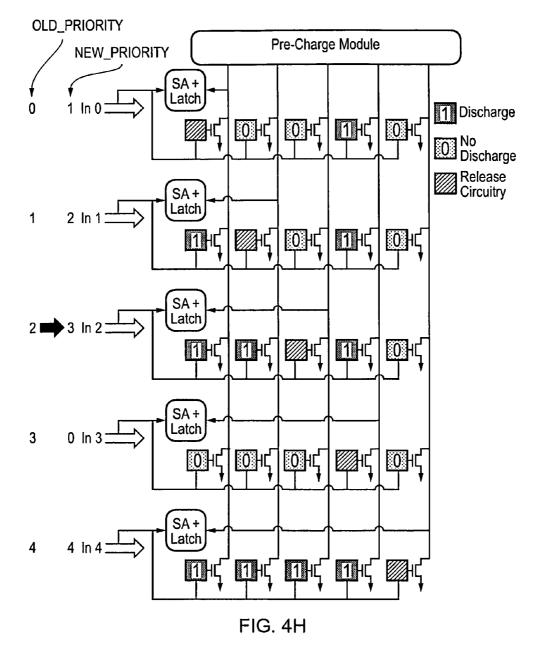

One type of adaptive priority scheme which has traditionally been difficult to implement efficiently is the least recently granted (LRG) priority scheme, where the relative priorities of the various source circuits are updated dependent on which source circuit wins a current arbitration process. In particular, if source circuit X wins the arbitration process, then in accordance with the LRG scheme all sources having a lower priority than source X have their priorities increased, all sources having a higher priority than source X have their priorities maintained at their current level, and source X has its priority demoted so as to have the lowest relative priority.

Although the LRG priority scheme guarantees fairness, 15 and a better quality of service (QoS) than other priority schemes (for example round-robin, pseudo round-robin, random priority assignment, etc), its hardware implementation typically results in a significant overhead in the area, performance and energy consumption of the crossbar circuit. In 20 addition the hardware complexity grows quadratically with the size of the crossbar circuit.

In contemporary switching fabrics that support LRG, the arbiter updates the priorities assigned to different sources by keeping track of all incoming and granted requests in the 25 network. This requires additional memory, processing elements and wires to implement this in hardware.

Accordingly, it would be desirable to provide an improved crossbar design that alleviates the above described problems associated with supporting adaptive priority schemes.

## SUMMARY OF THE INVENTION

Viewed from a first aspect, the present invention provides crossbar circuitry for interconnecting a plurality of source 35 circuits and a plurality of destination circuits such that data input to the crossbar circuitry from any of said plurality of source circuits can be output to any of said plurality of destination circuits, the crossbar circuitry comprising: a plurality of data input paths passing through said crossbar circuitry, 40 each data input path being connectable to one of said plurality of source circuits and providing a plurality of word lines; a plurality of data output paths passing through said crossbar circuitry transverse to the plurality of data input paths, each data output path being connectable to one of said plurality of 45 destination circuits and providing a plurality of bit lines; a crossbar cell associated with each intersection between one of said data input paths and one of said data output paths, each crossbar cell comprising: configuration storage circuitry programmable in an arbitration mode of operation to store a 50 routing value in dependence on a voltage on at least one of said plurality of bit lines, the routing value being programmed to a first value to indicate that data input along the word lines of the data input path to the associated intersection is to be output on the bit lines of the data output path at the associated 55 intersection, and the routing value being programmed to a second value to indicate that data input along the word lines of the data input path to the associated intersection is not to be output on the bit lines of the data output path at the associated intersection; transmission circuitry which in a transmission 60 mode of operation is responsive to the routing value having said first value to detect the data input along the word lines of the data input path and to output an indication of that data on the bit lines of the data output path at the associated intersection; arbitration circuitry that operates in said arbitration 65 mode of operation in dependence on a transmission request received by the crossbar cell from the source circuit con6

nected to the data input path of the associated intersection, if the transmission request is asserted to indicate that said source circuit wishes to route data from the data input path to the data output path at the associated intersection, the arbitration circuitry being arranged to operate in combination with the arbitration circuitry of other crossbar cells associated with the same data output path to selectively modify the voltage on the plurality of bit lines in order to apply an adaptive priority scheme, such that in the presence of multiple asserted transmission requests for said same data output path, the configuration storage circuitry of only one crossbar cell associated with said same data output path has its routing value programmed to said first value, thereby resolving conflict between said multiple asserted transmission requests according to said adaptive priority scheme; and priority storage circuitry configured to store priority data identifying which of the plurality of bit lines are to have their voltage modified by the associated arbitration circuitry in order to apply the adaptive priority scheme; the priority storage circuitry being configured, between each application of the adaptive priority scheme by the arbitration circuitry, to self update the priority data stored therein in dependence on the voltage of at least one of the plurality of bit lines.

In accordance with the present invention, crossbar cells are associated with each intersection between a data input path and a data output path, with each crossbar cell comprising transmission circuitry arranged in a transmission mode of operation to selectively connect data on its data input path to its data output path in dependence on a routing value stored in an associated configuration storage circuit, and arbitration circuitry that operates in an arbitration mode of operation in combination with the arbitration circuitry of other crossbar cells in order to resolve conflicts between multiple asserted transmission requests. In particular, if a transmission request is asserted from a source circuit to a crossbar cell, then the arbitration circuitry of that crossbar cell operates in combination with the arbitration circuitry of other crossbar cells associated with the same data output path to selectively modify the voltage on the plurality of bit lines in order to apply an adaptive priority scheme, such that in the presence of multiple asserted transmission requests for that same data output path, the configuration storage circuitry of only one crossbar cell associated with the same data output path has its routing value programmed to a first value (i.e. the value that causes the crossbar cell to couple its data input path to its data output path in the transmission mode of operation).

In addition, each crossbar cell has priority storage circuitry configured to store priority data identifying which of the plurality of bit lines are to have their voltage modified by the associated arbitration circuitry in order to apply the adaptive priority scheme, and the priority storage circuitry is configured, between each application of the adaptive priority scheme by the arbitration circuitry, to self update the priority data stored therein in dependence on the voltage of at least one of the plurality of bit lines.

Hence, it can be seen that in accordance with the present invention, in the arbitration mode of operation, the bit lines of the data output paths are re-used to detect conflicts for particular data output paths, to resolve those conflicts such that at any point in time only one source circuit is granted access to a particular data output path, and to update the priority data stored in the priority storage circuitry. This provides a fast and scalable technique for implementing adaptive priority schemes within a crossbar circuit. The approach is significantly more scalable than prior art techniques (in embodiments of the present invention the hardware complexity grows linearly with the size of the interconnection network

provided by the crossbar), and can be implemented with little overhead to the interconnection network, and little perfor-

In the arrangement of the present invention, both the arbiter and the crossbar functions are integrated together within the 5 crossbar circuitry. The arbiter is highly logic dominated while the crossbar is highly routing dominated, and by bringing these two functions together within the crossbar cells of the crossbar circuitry, a more efficient utilisation of routing tracks and silicon space in the chip is achieved. In addition, the 10 communication overhead that traditionally is incurred between the crossbar and the arbiter is now alleviated. By storing the crossbar configuration at the crossbar cells associated with each intersection within the crossbar circuitry, this allows re-utilisation of the bit lines of the data output paths for 15 arbitration.

In accordance with the present invention, the crossbar circuitry can be laid out in the style of an SRAM array topology, with the crossbar cells being laid out in an array, the data input paths providing word lines, and the data output paths provid- 20 ing bit lines. Such an arrangement allows for a very efficient layout both in terms of size and in terms of the number of interconnects required.

Whilst the adaptive priority scheme can take a variety of forms, in one embodiment the adaptive priority scheme is a 25 least recently granted (LRG) scheme. As mentioned earlier, LRG schemes have traditionally been complex to implement in hardware, and hence the ability to provide an LRG scheme using embodiments of the present invention presents a very significant improvement over the known prior art approaches. 30

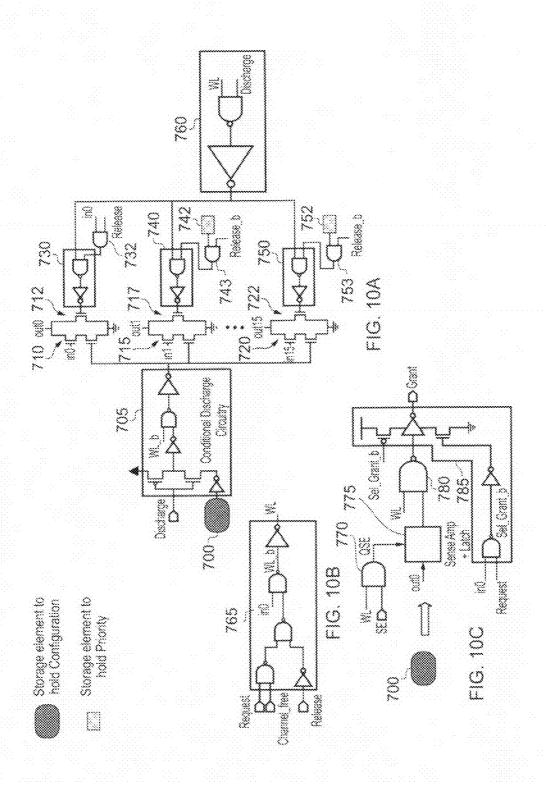

In one embodiment, each data output path provides n bit lines, and each configuration storage circuitry is associated with one of said n bit lines via which the routing value is programmed into the configuration storage circuitry, such that for up to n crossbar cells associated with the same data 35 output path, the configuration storage circuitry of those crossbar cells have a different associated bit line of said n bit lines. Within each crossbar cell the arbitration circuitry and the priority storage circuitry is associated with the n-1 bit lines other than the one bit line associated with the configuration 40 storage circuitry of that crossbar cell, with the priority storage circuitry identifying which of those n-1 bit lines should have their voltages modified by the arbitration circuitry in order to apply said adaptive priority scheme.

In one particular embodiment, the priority storage circuitry 45 may be formed of n-1 priority storage elements, one for each of the n-1 bit lines associated with the priority storage circuitry. The priority storage elements can take a variety of forms, but in one embodiment are formed of SRAM cells.

In one such embodiment, in said arbitration mode of operation, after the arbitration circuitry of any crossbar cells associated with the same data output path that receive an asserted transmission request has selectively modified the voltage on the n bit lines in order to apply said adaptive priority scheme, each configuration storage circuitry of a crossbar cell receiv- 55 a logic 1 value or a logic 0 value dependent on their form. ing an asserted transmission request is configured to sample the voltage on its associated bit line in order to program said routing value.

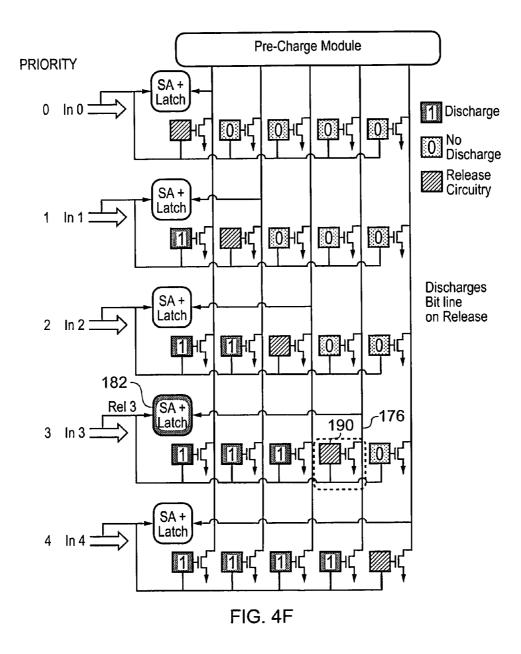

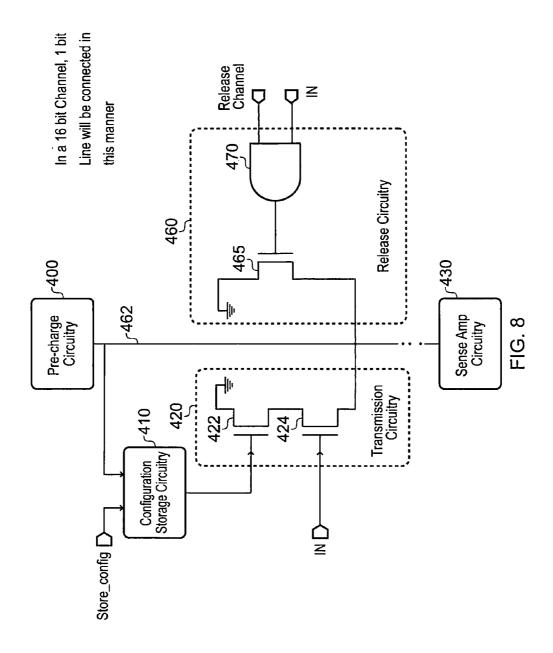

In one embodiment, each crossbar cell further comprises release circuitry coupled to the one bit line associated with the 60 configuration storage circuitry of that crossbar cell, on receipt of an asserted release request the channel release circuitry causing the voltage on that one bit line to be modified to a level that causes said second value to be stored as said routing value in the configuration storage circuitry of that crossbar 65 cell, thereby causing the crossbar cell to release the associated data output path to allow re-allocation of that data output path.

This provides a simple and effective mechanism for allowing a source circuit to release a particular data output path when it has finished transmitting data, thereby allowing another source circuit to subsequently seek to acquire that data output

In one embodiment, the priority storage circuitry in those crossbar cells associated with the released data output path is responsive to the asserted release request to self update the priority data stored therein in dependence on the voltage of at least one of the plurality of bit lines. Hence, in such embodiments, the asserted release request provides a convenient event to trigger the performance of the self update process, and ensures that the self update process is performed between each application of the adaptive priority scheme by the arbitration circuitry.

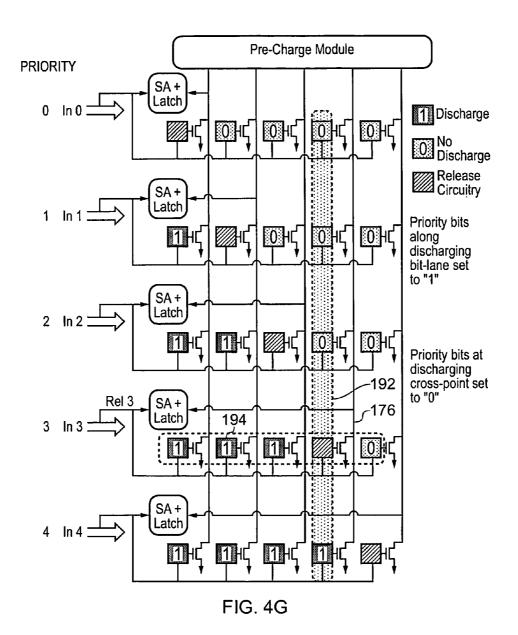

In one embodiment, each priority storage circuitry comprises a plurality of priority storage elements, each priority storage element being associated with one of said plurality of bit lines, and within each priority storage circuitry the current value of the plurality of priority storage elements indicating. for the associated data output path, a relative priority level for the source circuit coupled to the crossbar cell containing that priority storage circuitry.

In one such embodiment where the adaptive priority scheme is a least recently granted (LRG) priority scheme, then within the priority storage circuitry of those crossbar cells associated with the released data output path, those priority storage elements that are associated with the bit line whose voltage is modified by the release circuitry are set to a first value, whereby the relative priority level of each source circuit other than the source circuit releasing the data output path is either increased or maintained. Further, for the crossbar cell containing the release circuitry that received the asserted release request, the priority storage circuitry has its priority storage elements cleared to a second value, whereby the source circuitry releasing the data output path is assigned a relative priority lower than the other source circuits. This provides a particularly efficient mechanism for implementing the LRG scheme, with the relative priority levels of the source circuits being independently updated for each data output path as that data output path is released.

In one embodiment, at an initialization point, the priority storage circuitry of each crossbar cell are initialized to predetermined values to provide initial relative priority levels for the plurality of source circuits in respect of each of the plurality of data output paths.

In one embodiment, the initial relative priority levels can be specified independently for each data output path. Further, in one embodiment, each priority storage circuitry is responsive to a reset signal asserted at the initialization point in order to set itself to a predetermined value. In one particular embodiment the individual priority storage elements of each priority storage circuitry can take one of two forms, so that on application of the reset signal, their value is updated to either

In one particular embodiment, each of the bit lines are precharged to a first voltage level, and on receipt of said asserted release request, the release circuitry discharges the voltage on the one bit line associated with the configuration storage circuitry of that crossbar cell. Further, each configuration storage circuitry comprises a sense-amp enabled latch which, in the presence of an asserted release request to the associated release circuitry, senses the voltage on its associated bit line following the discharge operation performed by the release circuitry in order to update the routing value to said second value, thereby releasing the associated data output path. Hence, in such embodiments, to release a channel at

a crossbar cell, the bit line that is sensed by the associated sense-amp enabled latch is discharged and subsequently sampled

In one embodiment, each data input path provides n word lines, and the release requests for up to n crossbar cells associated with the same data input path are input to the crossbar circuitry via the n word lines of that same data input path. Further, each release circuitry is associated with one of said n word lines, such that for up to n crossbar cells associated with the same data input path, the release circuitry of those crossbar cells have a different associated word line of said n word lines via which the release request is received. Hence, in such embodiments, the release requests can, be issued in an efficient manner through re-use of the word lines of the data input paths.

In one particular embodiment, the release requests are issued in said arbitration mode of operation, and a control signal is issued by the plurality of source circuits in the arbitration mode of operation to identify if the n word lines of the associated data input path are carrying release requests or 20 transmission requests. Hence, in such embodiments the control signal can be used to qualify whether the information routed over the word lines identifies release requests or transmission requests, and hence whether the arbitration circuitry or the release circuitry needs to be activated. In one particular 25 embodiment, the control signal actually takes the form of two separate signal lines, one being a request\_channel signal and the other being a release\_channel signal, only one of these two signals being allowed to be set at any point in time. In one embodiment these two signals are provided on a per row 30 basis, and hence within any particular row the crossbar cells will either be processing release requests or transmission requests at any point in time. In some implementations it would be possible to provide a finer granularity of control signals, so that some crossbar cells in a row could be process- 35 ing release requests whilst others are processing transmission requests.

Since the configuration storage circuits of different cross-bar cells in the same data output path are associated with different bit lines, and the arbitration circuits of those cross-bar cells in that data output path receiving an asserted transmission request selectively modify the voltage on the n bit lines, it is possible to apply the adaptive priority scheme by ensuring that at the point the configuration storage circuit of each crossbar cell receiving an asserted transmission request samples the voltage on its associated bit line following the arbitration process, only one of the bit lines will be at a value that would cause the associated configuration storage circuit to store said first value as the routing value, thereby allowing only a single source circuit to be granted access to a data 50 output path at any point in time.

The manner in which the arbitration circuits selectively modify the voltage on the n bit lines can be varied dependent on implementation. However, in one embodiment, each of the bit lines are precharged to a first voltage level and then during 55 the arbitration mode of operation the arbitration circuitry of any crossbar cells associated with the same data output path that receive an asserted transmission request selectively discharge the voltage on the n bit lines in order to apply said adaptive priority scheme. Hence, in such embodiments, the 60 bit lines are conditionally discharged in order to apply the adaptive priority scheme, thereby resolving any conflicts during the arbitration mode of operation.

There are a number of ways in which the transmission request can be asserted from the source circuits to the crossbar 65 cells. However, in one embodiment, each data input path provides n word lines, and in the arbitration mode of opera-

10

tion the transmission requests for up to n crossbar cells associated with the same data input path are input to the crossbar circuitry via the n word lines of that same data input path. Hence, in such embodiments, the data input paths are themselves re-used in the arbitration mode of operation for the provision of asserted transmission requests.

In one particular embodiment, each configuration storage circuitry is associated with one of said n word lines, such that for up to n crossbar cells associated with the same data input path, the configuration storage circuitry of those crossbar cells have a different associated word line of said n word lines via which the transmission request is received.

In such embodiments where the n word lines of the data input paths and the n bit lines of the data output paths are re-used during the arbitration mode of operation, it can be seen that conflict detection and resolution can be performed in a single stage, thereby yielding significant performance benefits when compared with the conventional prior art approach where collision detection and resolution is done hierarchically in multiple stages.

In particular, it will be seen that for crossbar circuitry containing a matrix of up to n×n crossbar cells, conflict detection and resolution can be performed in a single stage.

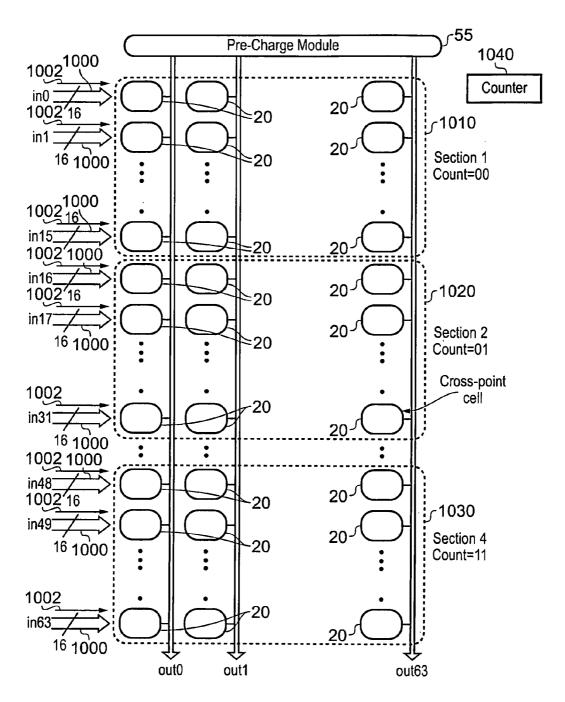

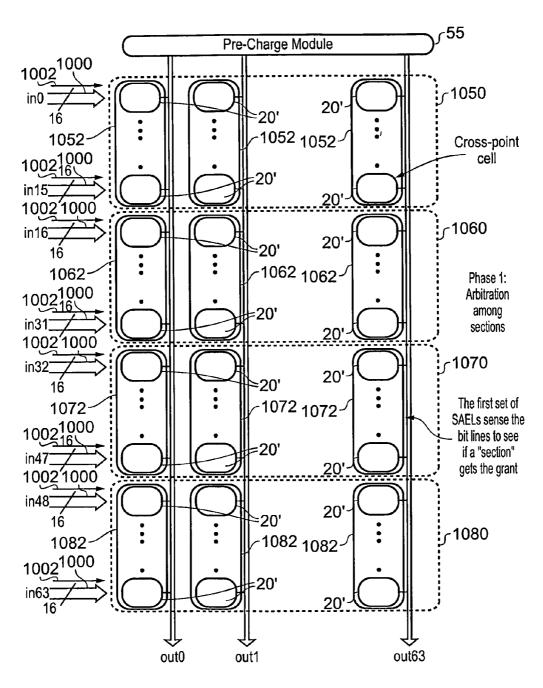

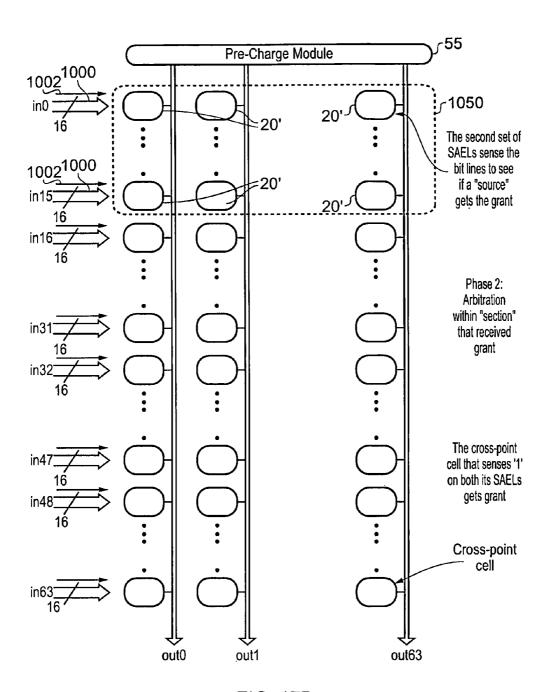

However, the techniques of embodiments of the present invention can also be used with crossbar circuits having a larger matrix of crossbar cells. In particular, in one embodiment, a matrix of mn×mn crossbar cells are provided; wherein m is an integer of 2 or more, the matrix is divided into a plurality of sections, and a series of arbitration operations are used to apply the adaptive priority scheme to cause the configuration storage circuitry of only one crossbar cell associated with said same data output path to have its routing value programmed to said first value, thereby resolving conflict between multiple asserted transmission requests according to said adaptive priority scheme. For each arbitration operation in the series, one or more of the sections in said plurality of sections are subjected to that arbitration operation.

In one particular embodiment, each arbitration operation operates on a single section, such that after said series of arbitration operations have been performed all of said plurality of sections have been subjected to said arbitration operation. Hence, by way of example, for a 64×64 crossbar circuit with 16-bit data input paths and data output paths, the crossbar circuitry can be divided into four sections, with the arbitration operation being performed in sequence on each of those sections. In one embodiment a counter can be incremented every cycle to select which section to serve during arbitration in that cycle (in the above example a two bit counter would suffice). Such an implementation still maintains the benefits of minimal wiring and logic overhead, but the arbitration latency for a given request can vary dependent on the section with which that request is associated (in the above example the latency can vary from one to four cycles). The self update of the priority data will then take place after all sections have been processed.

In an alternative embodiment, in a first arbitration operation of the series, all of the plurality of sections are subjected to the first arbitration operation in order to identify one of the sections in said plurality that contains the configuration storage circuitry whose routing value is to be programmed to said first value. Then, in a second arbitration operation of the series, said one of the sections identified by the first arbitration operation is subjected to the second arbitration operation to identify the configuration storage circuitry within that section whose routing value is to be programmed to said first value. In accordance with such embodiments, the crossbar is

again divided into sections, but arbitration is then performed hierarchically in two steps, first among the sections, and then among all requests in a given section. The same group of bit lines can be used for both arbitration steps. The self update of the priority data will then take place after both steps of the 5 arbitration have taken place.

In one embodiment, each crossbar cell is provided with two configuration storage circuits, the first being used to detect if the associated section contains the highest priority asserted transmission request, and the second being used in the subsequent arbitration step to detect if the highest priority asserted transmission request is associated with that particular crossbar cell.

By way of example, in a 64×64 crossbar with 16-bit data input paths and data output paths, the crossbar could again be 15 divided into four sections. If section 0 has the highest priority and at least one source associated with that section asserts a transmission request, then in the first stage of arbitration the first configuration storage circuits in each crossbar cell in that section will have a routing value programmed to the first 20 value, whilst those in the other sections will have their routing values programmed to the second value (in both cases the programming occurring as a result of the voltages on the bit lines associated with each first configuration storage circuit). In the next cycle, only asserted transmission requests in 25 respect of section 0 are considered, with the bit lines again being used for arbitration, and with the second configuration storage circuits now sensing the associated bit lines. In the event that both configuration storage circuits at a particular crossbar cell have their routing value set to the first value, this 30 indicates that the associated asserted transmission request has prevailed, and in the data transmission mode of operation that crossbar cell will connect its input to its output.

Such an implementation will have a fixed two cycle arbitration latency at the expense of some additional logic, but no 35 additional interconnect. With 16 bit lines in a data output path, it is possible to arbitrate between up to 16 sections, with each section being able to receive up to 16 asserted transmission requests. Hence, the arbitration latency can be retained at two cycles for a crossbar up to a 256×256 crossbar.

In one embodiment, when a crossbar cell has its routing value programmed to the first value during the arbitration mode of operation, a grant signal is asserted to the associated source circuit to confirm that the transmission request that it asserted has been granted. In one embodiment, a source circuit can only send a single request at a time, and in such an embodiment there will typically be only a single grant signal issued per row. However, in an alternative embodiment, a source circuit may be able to send multiple requests at a time, and in such embodiments multiple grant signals per row can 50 be provided, with one grant signal being associated with each data output path.

The transmission circuitry can operate in a variety of ways. However, in one embodiment, each data output path associated with a crossbar cell in the transmission mode of operation is precharged to a first logic level prior to data transfer, the transmission circuitry of each crossbar cell comprising: first and second switches connected in series between the data output path and a second logic level; in the transmission mode of operation the first switch being open or closed dependent on the routing value stored in the associated configuration storage circuitry, and the second switch being open or closed dependent on the data input over the data input path. In one particular embodiment, the first logic level is the supply voltage level Vdd and the second logic level is ground. Hence, by such an arrangement, the data on the input data path does not directly drive the data on the output data path, and instead the

12

data on the output data path either remains at the first logic level, or is discharged towards the second logic level in the event that both the first and second switches are closed.

By such an arrangement of transmission circuitry, the transmission circuitry does not need to be altered irrespective of the size of the crossbar circuitry and hence the length of the data output path, and further the drive circuitry providing the input data over the input data path also does not need resizing as the crossbar circuitry is increased in size. Hence, if the crossbar circuitry is increased in size, the circuitry of each crossbar cell does not need to be changed and instead only the number of crossbar cells needs to increase. Thus, by using such a design, the delay of the crossbar circuitry grows linearly with size, making such a design of crossbar circuitry useable with very large crossbars (for example with 128×128 or 256×256 inputs/outputs). In addition, the design is very regular and the delay across all routes through the crossbar circuitry is uniform.

In one embodiment, each said data input path comprises n word lines for carrying an n-bit input data value during the transmission mode of operation, and each said data output path comprises n bit lines for carrying an n-bit data value during said transmission mode of operation, at least the second switch being replicated for each bit line. Accordingly, the design of the transmission circuitry can readily accommodate various sizes of data input paths and data output paths, without any significant increase in the complexity of the crossbar circuitry.

In one embodiment, in the transmission mode of operation, a bit line of the data output path is pulled to the second logic level if the routing value is said first value and the input data bit on the corresponding word line is at said first logic level. Hence, if the routing value stored in the configuration storage circuitry indicates that the data input path should be coupled to the data output path, and the data on the data input path is at a logic one level, then the data output path will be discharged towards the second logic level.

In one embodiment each crossbar cell further comprises conditional discharge circuitry for turning off the first switch irrespective of the routing value whilst the associated data output path is being precharged to the first logic level, and for allowing the first switch to be controlled by the routing value following the precharging of the associated data output path to the first logic level. Accordingly, such conditional discharge circuitry isolates the bit lines of the data output path from the inputs whilst they are being precharged, thereby reducing the power consumption of the precharge operation. Also, by such an arrangement, the data input paths can be driven simultaneously with the precharge operation, due to the conditional discharge circuitry isolating the data output paths from the inputs at that time, thereby enabling an increased speed of operation.

Furthermore, by using the arrangement of transmission circuitry described above, it should be noted that all bit lines of the data output path are precharged to the first logic level, and then either stay at the first logic level or transition to the second logic level dependent on the input value on the associated word line of the data input path and the routing value. As a result, no situation arises where the voltages on two adjacent bit lines are moving in opposite directions, thereby reducing capacitive coupling effects and thereby improving speed of operation.

In embodiments where the data output path is precharged prior to data transfer, and then selectively discharged dependent on the routing value and the data input value, power consumption of the crossbar circuitry can be reduced through the use of sense amplifier circuitry. In particular, in one

embodiment, the crossbar circuitry further comprises sense amplifier circuitry to detect, during the transmission mode of operation, the data output on the bit lines of the data output path, thereby allowing detection of a transition towards the second logic level before the voltage on a bit line of the data output path has reached the second logic level. Since the detection of the transition occurs before a bit line of the data output path has reached the second logic level, the power required to precharge the bit lines of the data output path back to the first logic level is significantly reduced.

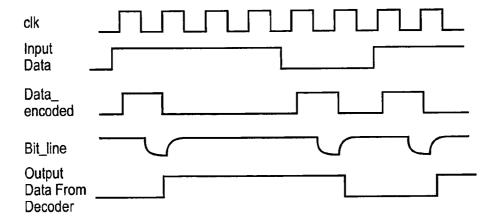

In embodiments where such precharging of the data output paths occurs, then further power savings can be obtained by suitable encoding of the input data prior to provision to the crossbar circuitry. In particular, in one embodiment, the crossbar circuitry further comprises: encode circuitry between each of said plurality of source circuits and said plurality of data input paths; decode circuitry between each of said plurality of data output paths and said plurality of destination circuits; the encode circuitry applying an encoding operation to encode input data provided by each source circuit 20 into an encoded format that reduces the number of times the data output paths need to be pulled to the second logic level following their precharge to the first logic level, when compared to the number of times the data output paths would need to be pulled to the second logic level if the original input data 25 were passed through the crossbar circuitry; the decode circuitry applying a corresponding decoding operation to identify the original input data provided by the source circuit from the encoded data output over the data output path.

In one particular embodiment, the encoding operation 30 ensures that the encoded format produced from the input data is only a logic one value when the input data changes, and accordingly the data output path is only discharged when the input changes. The decode circuitry then recreates the original input data from the encoded data output over the data 35 output path.

Due to the regular design of the crossbar circuitry of embodiments of the present invention, and the manner in which the transmission circuits of each crossbar cell operate, the plurality of source circuits are connectable to either end of 40 the plurality of data input paths, thereby significantly improving flexibility when designing the layout of the apparatus in which the crossbar circuitry and source circuits are provided. Similarly, the plurality of destination circuits are connectable to either end of the plurality of data output paths.

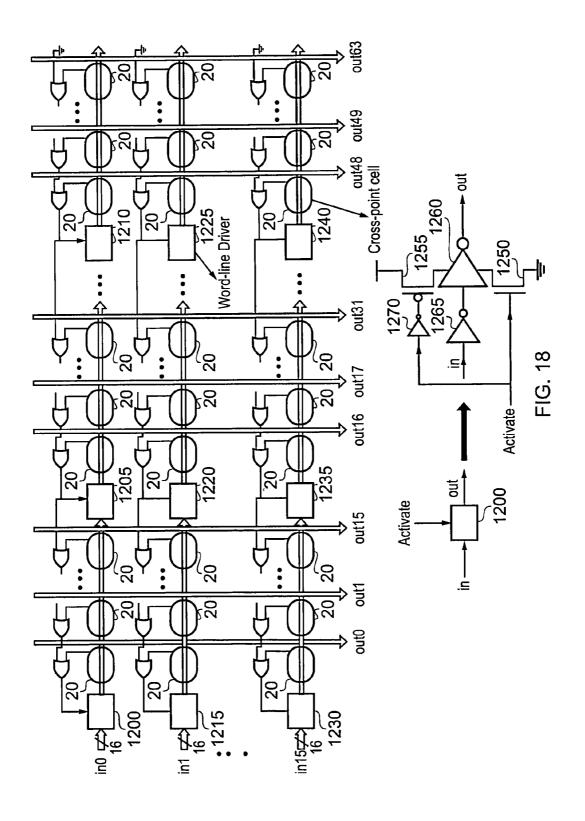

In one embodiment, a sequence of word line drivers may be used to propagate data input values along the data input paths to the various crossbar cells connected to those data input paths. In a single request embodiment, where multi-casting is not supported, and accordingly each source will only request 50 access to a single output path at a time, significant power may be consumed in propagating the data along the entirety of the data input path in situations where it is not needed. In one embodiment this power consumption is alleviated through the provision of a partially activated network arrangement. In 55 particular, in one embodiment, each data input path consists of multiple input path portions separated by word line drivers, and each word line driver is activated in dependence on the routing values stored in the configuration storage circuitry of crossbar cells provided along the associated data input path 60 but further from the source circuit than that word line driver. As a result, each word line driver is only activated if the configuration storage circuitry of at least one crossbar cell provided along the associated data input path but further from the source circuit than that word line driver has a routing value 65 set to said first value. Such an approach can yield significant power savings.

14

The crossbar circuitry of embodiments of the present invention may be utilised in a variety of systems. However, according to a second aspect of the present invention, a data processing apparatus is provided comprising: a plurality of memory devices for storing data values; a plurality of processors for performing data processing operations in parallel on multiple of the data values stored in said plurality of memory devices; and crossbar circuitry in accordance with the first aspect of the present invention for routing the data value from any of said plurality of memory devices to any of said plurality of processors.

The crossbar circuitry of embodiments of the present invention provides a particularly simple, scalable and power efficient mechanism for routing data values from any of the memory devices to any of the processors.

Viewed from a third aspect, the present invention provides crossbar circuitry for interconnecting a plurality of source means and a plurality of destination means such that data input to the crossbar circuitry from any of said plurality of source means can be output to any of said plurality of destination means, the crossbar circuitry comprising: a plurality of data input path means passing through said crossbar circuitry, each data input path means for connecting to one of said plurality of source means and providing a plurality of word line means; a plurality of data output path means passing through said crossbar circuitry transverse to the plurality of data input path means, each data output path means for connecting to one of said plurality of destination means and providing a plurality of bit line means; a crossbar cell means associated with each intersection between one of said data input path means and one of said data output path means, each crossbar cell means comprising: configuration storage means programmable in an arbitration mode of operation for storing a routing value in dependence on a voltage on at least one of said plurality of bit line means, the routing value being programmed to a first value to indicate that data input along the word line means of the data input path means to the associated intersection is to be output on the bit line means of the data output path means at the associated intersection, and the routing value being programmed to a second value to indicate that data input along the word line means of the data input path means to the associated intersection is not to be output on the bit line means of the data output path means at the associated intersection; transmission means, responsive to the routing value having said first value in a transmission mode of operation, for detecting the data input along the word line means of the data input path means and to output an indication of that data on the bit line means of the data output path means at the associated intersection; arbitration means for operating in said arbitration mode of operation in dependence on a transmission request received by the crossbar cell means from the source means connected to the data input path means of the associated intersection, if the transmission request is asserted to indicate that said source means wishes to route data from the data input path means to the data output path means at the associated intersection, the arbitration means for operating in combination with the arbitration means of other crossbar cell means associated with the same data output path means to selectively modify the voltage on the plurality of bit line means in order to apply an adaptive priority scheme, such that in the presence of multiple asserted transmission requests for said same data output path means, the configuration storage means of only one crossbar cell means associated with said same data output path means has its routing value programmed to said first value, thereby resolving conflict between said multiple asserted transmission requests according to said adaptive priority scheme; and priority storage

means for storing priority data identifying which of the plurality of bit line means are to have their voltage modified by the associated arbitration means in order to apply the adaptive priority scheme; the priority storage means for self updating the priority data stored therein in dependence on the voltage of at least one of the plurality of bit line means, between each application of the adaptive priority scheme by the arbitration means

Viewed from a fourth aspect, the present invention pro-

vides a method of operating crossbar circuitry to interconnect a plurality of source circuits and a plurality of destination circuits such that data input to the crossbar circuitry from any of said plurality of source circuits can be output to any of said plurality of destination circuits, the crossbar circuitry having a plurality of data input paths passing through said crossbar circuitry, each data input path being connectable to one of said plurality of source circuits and providing a plurality of word lines, and a plurality of data output paths passing through said crossbar circuitry transverse to the plurality of 20 data input paths, each data output path being connectable to one of said plurality of destination circuits and providing a plurality of bit lines, the method comprising the steps of: employing a crossbar cell in association with each intersection between one of said data input paths and one of said data 25 output paths; programming a routing value in each crossbar cell in an arbitration mode of operation, the routing value being programmed in dependence on a voltage on at least one of said plurality of bit lines, the routing value being programmed to a first value to indicate that data input along the word lines of the data input path to the associated intersection is to be output on the bit lines of the data output path at the associated intersection, and the routing value being programmed to a second value to indicate that data input along the word lines of the data input path to the associated intersection is not to be output on the bit lines of the data output path at the associated intersection; in a transmission mode of operation, causing the crossbar cell to be responsive to the routing value having said first value to detect the data input 40 along the word lines of the data input path and to output an indication of that data on the bit lines of the data output path at the associated intersection; in said arbitration mode of operation, causing arbitration circuitry in the crossbar cell to operate in dependence on a transmission request received by 45 the crossbar cell from the source circuit connected to the data input path of the associated intersection, if the transmission request is asserted to indicate that said source circuit wishes to route data from the data input path to the data output path at the associated intersection, the arbitration circuitry operating in combination with the arbitration circuitry of other crossbar cells associated with the same data output path to selectively modify the voltage on the plurality of bit lines in order to apply an adaptive priority scheme, such that in the presence of multiple asserted transmission requests for said same data output path, the configuration storage circuitry of only one crossbar cell associated with said same data output path has its routing value programmed to said first value, thereby resolving conflict between said multiple asserted transmission requests according to said adaptive priority scheme; storing, in priority storage circuitry within the crossbar cell, priority data identifying which of the plurality of bit lines are to have their voltage modified by the associated arbitration circuitry in order to apply the adaptive priority scheme; and 65 arranging the priority storage circuitry, between each application of the adaptive priority scheme by the arbitration cir16

cuitry, to self update the priority data stored therein in dependence on the voltage of at least one of the plurality of bit lines.

## BRIEF DESCRIPTION OF THE DRAWINGS

The present invention will be described further, by way of example only, with reference to embodiments thereof as illustrated in the accompanying drawings, in which:

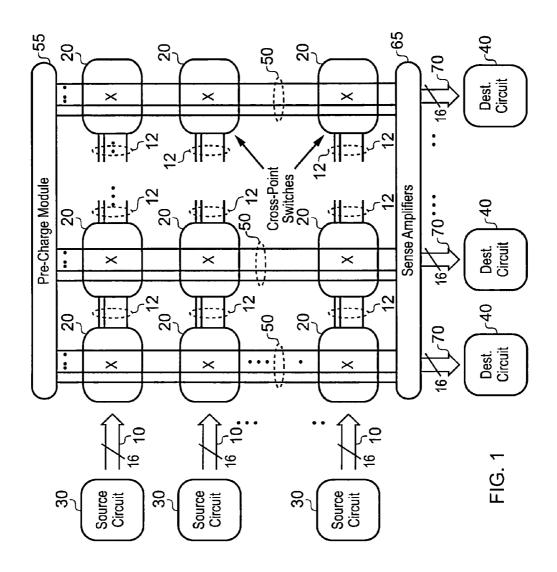

FIG. 1 is a block diagram of crossbar circuitry in accordance with one embodiment;

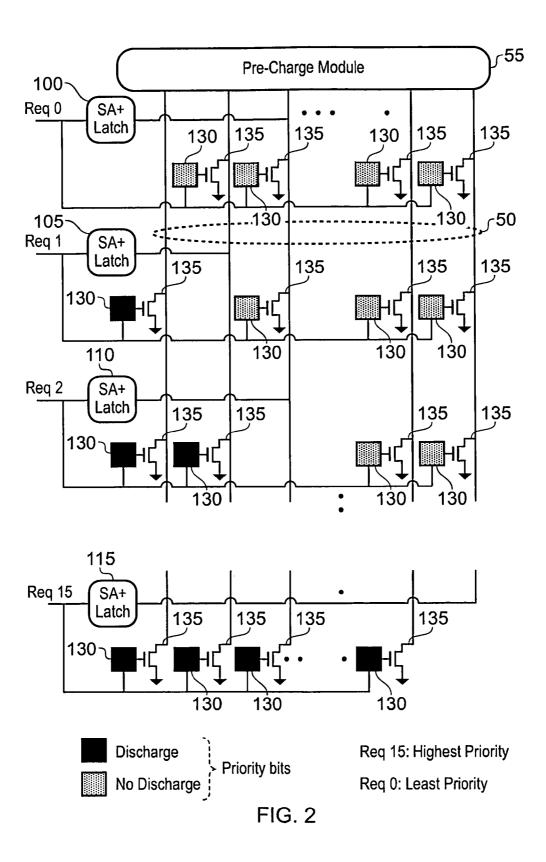

FIG. 2 illustrates how priority storage circuitry provided in association with each crossbar cell may be used in one embodiment;

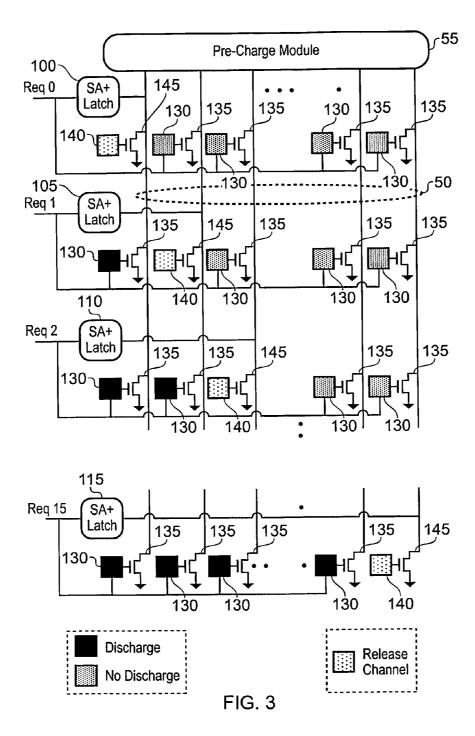

FIG. 3 illustrates how release circuitry may be used in one embodiment to enable a crossbar cell to release a particular data output path (also referred to herein as a channel);

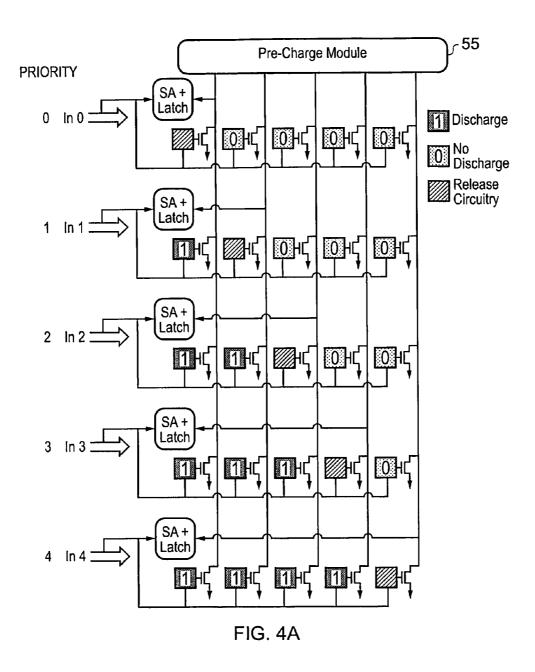

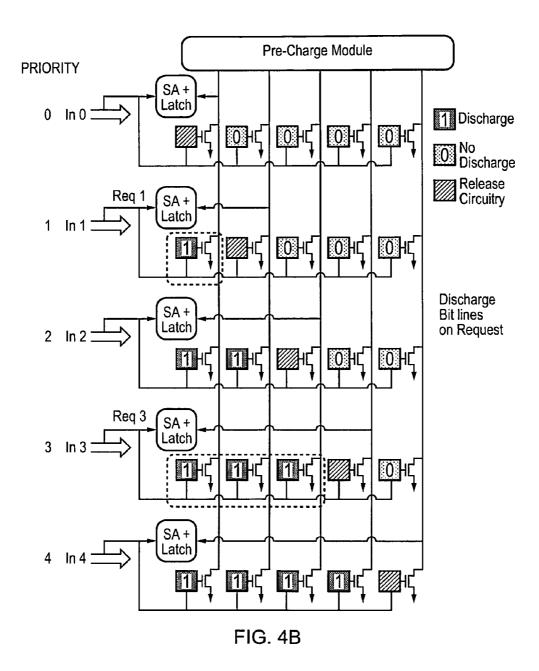

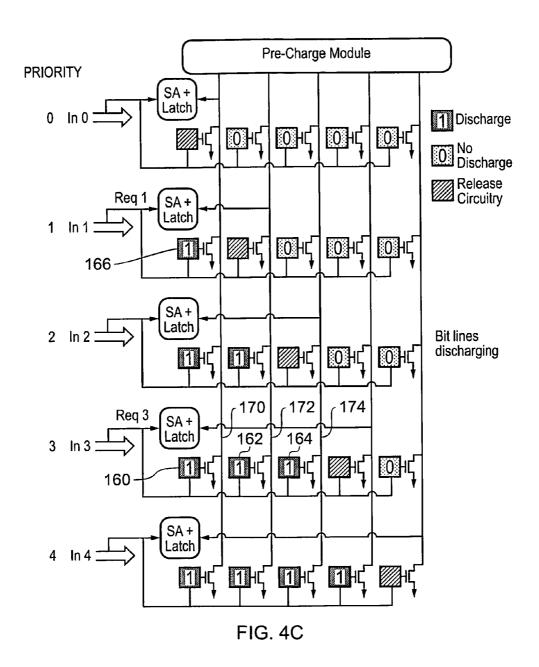

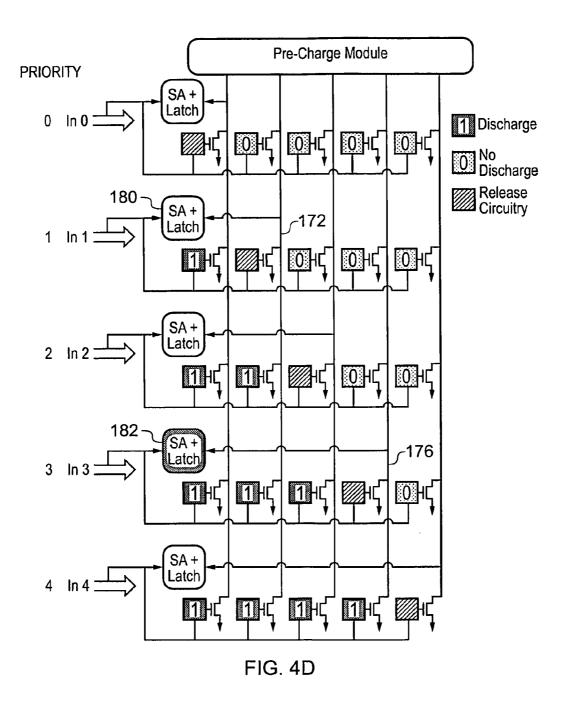

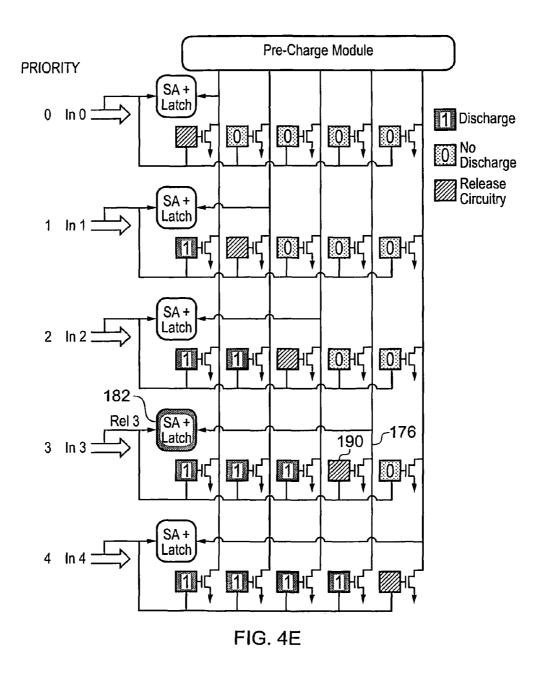

FIGS. 4A to 4H illustrate how the priority storage circuitry may be updated to support a LRG priority scheme in accordance with one embodiment;

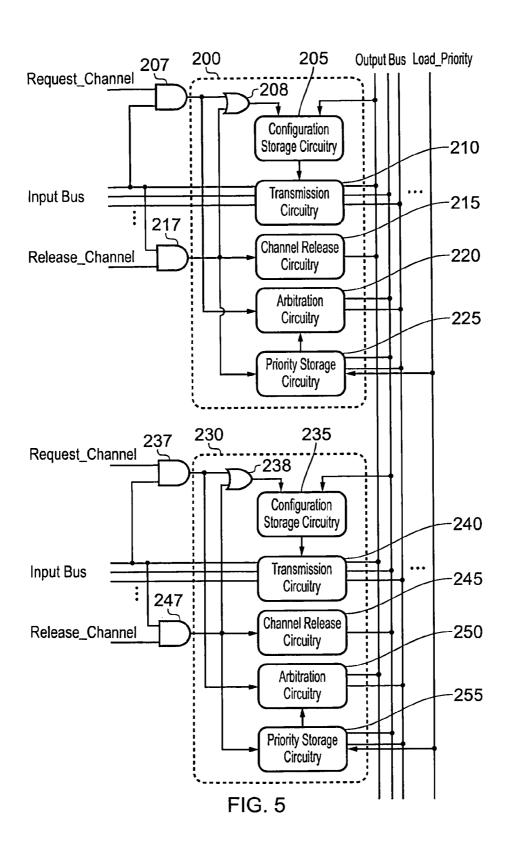

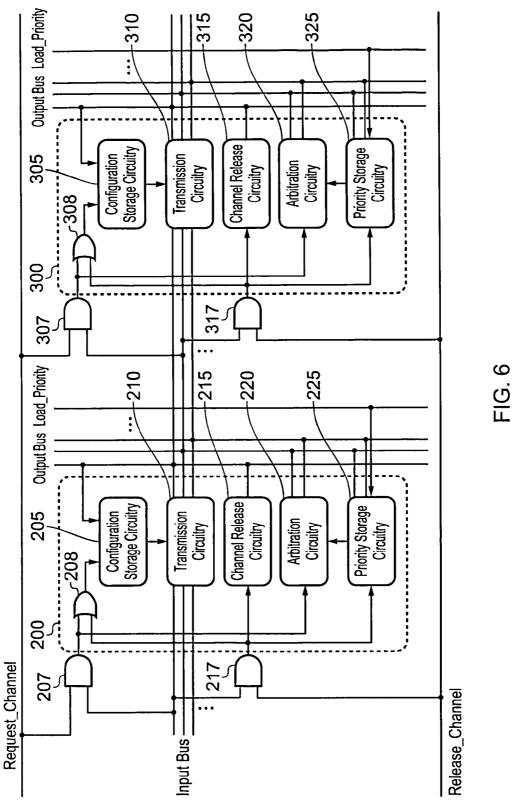

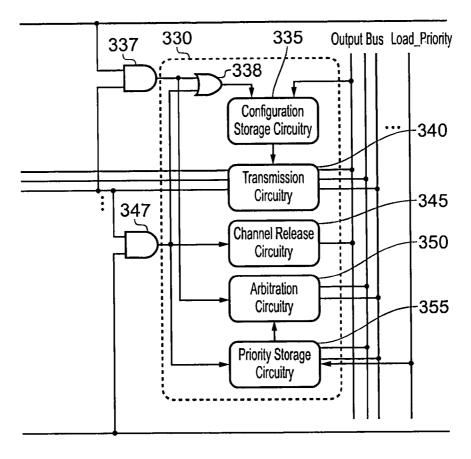

FIG. 5 illustrates the circuitry provided within each crossbar cell for a number of crossbar cells in a column;

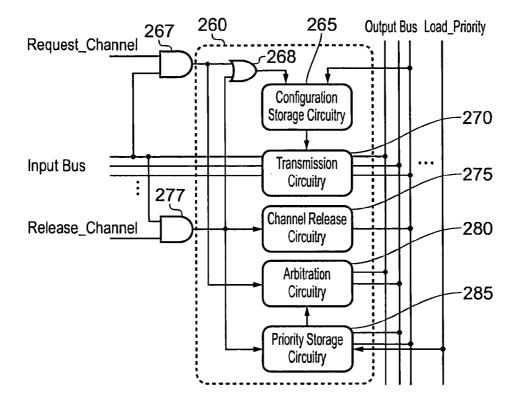

FIG. 6 illustrates the circuitry provided within each crossbar cell for a number of crossbar cells in a row;

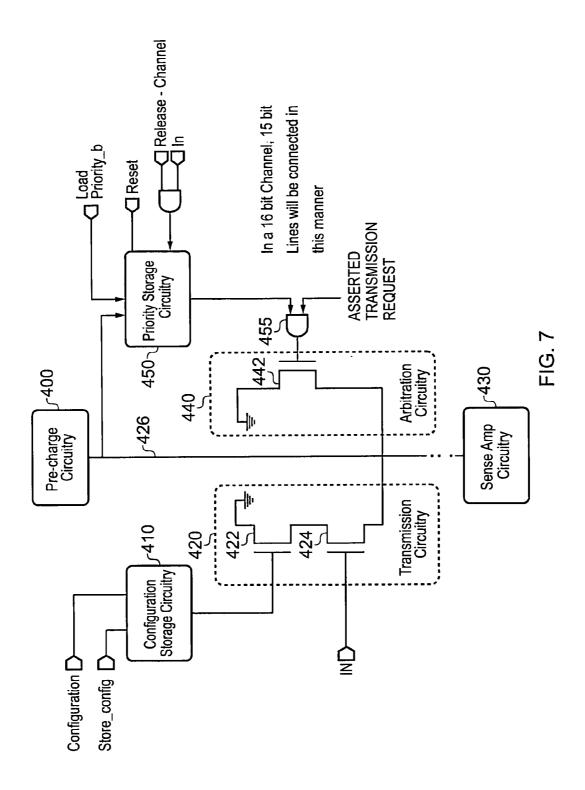

FIG. 7 illustrates in more detail the transmission circuitry, arbitration circuitry and priority storage circuitry that may be provided within each crossbar cell in accordance with one embodiment:

FIG. 8 illustrates in more detail the transmission circuitry and release circuitry that may be provided within each crossbar cell in accordance with one embodiment;

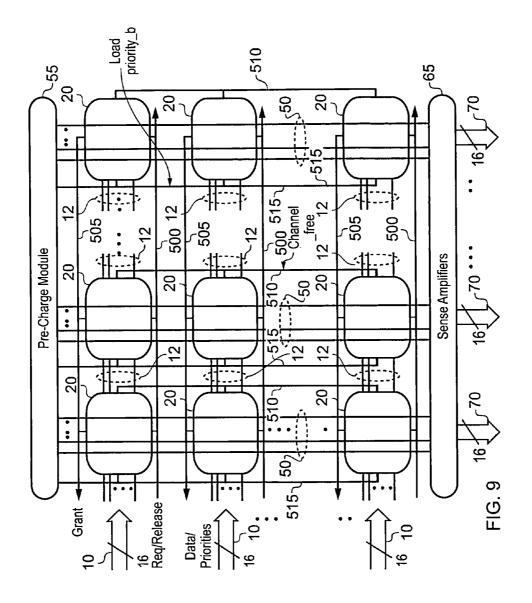

FIG. 9 schematically illustrates a packet switching crossbar implementation in accordance with one embodiment;

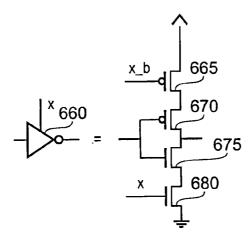

FIGS. **10**A to **10**D illustrate in more detail components provided within each crossbar cell of the crossbar circuit in accordance with one embodiment:

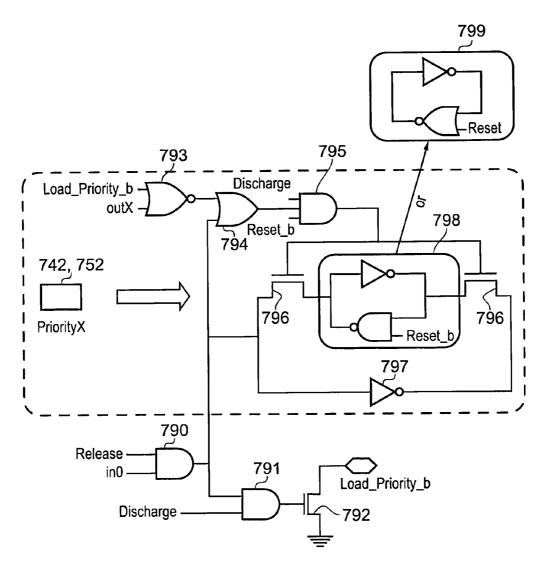

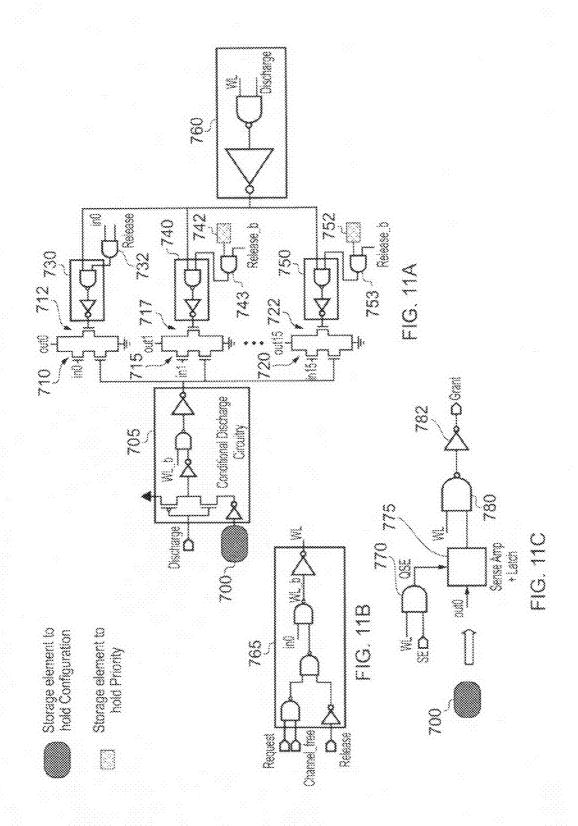

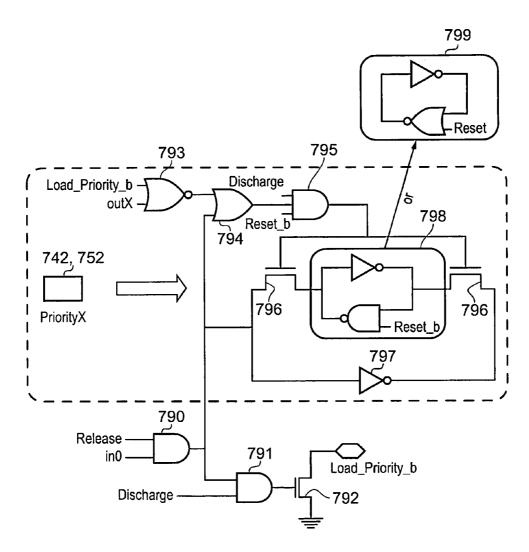

FIGS. 11A to 11D illustrate in more detail the components provided within each crossbar cell of the crossbar circuit in accordance with an alternative embodiment;

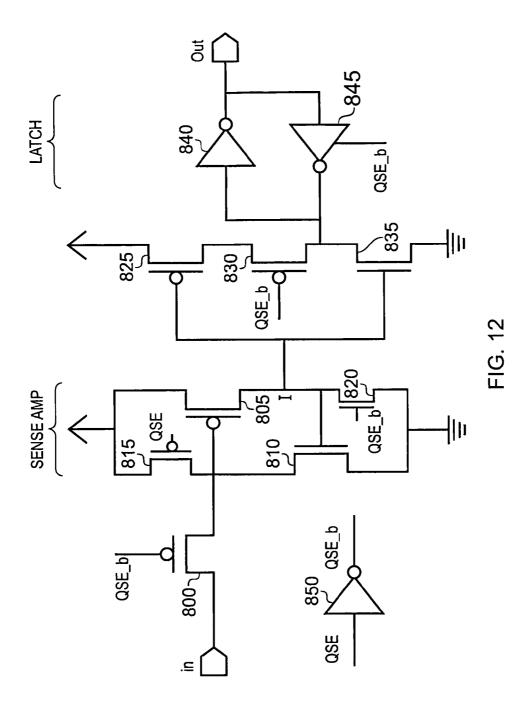

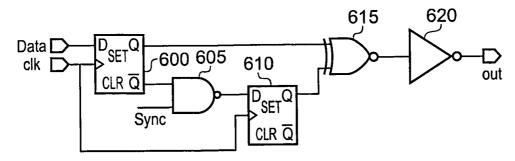

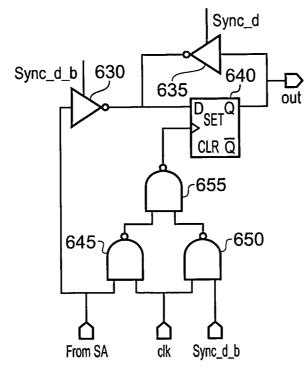

FIG. 12 illustrates in more detail the arrangement of the configuration storage element provided within each crossbar cell in accordance with one embodiment;

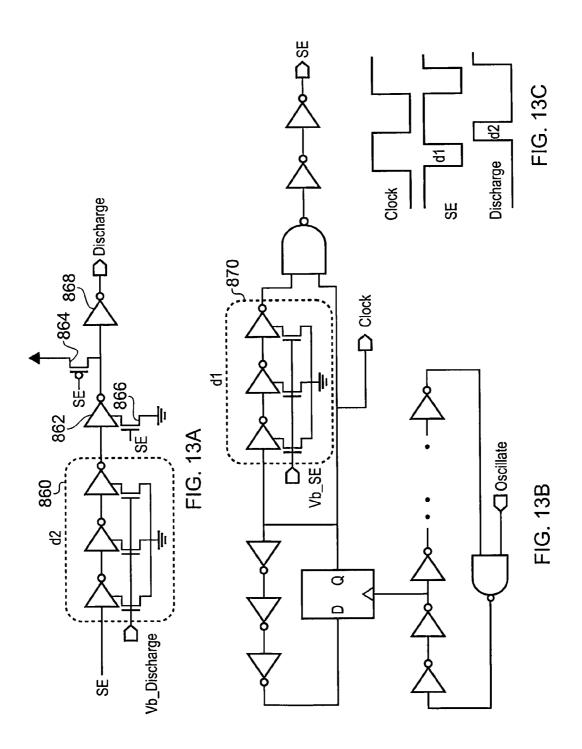

FIGS. **13**A to **13**C illustrate the configuration of a pulse generator for generating discharge and sense enable (SE) signals in accordance with one embodiment;

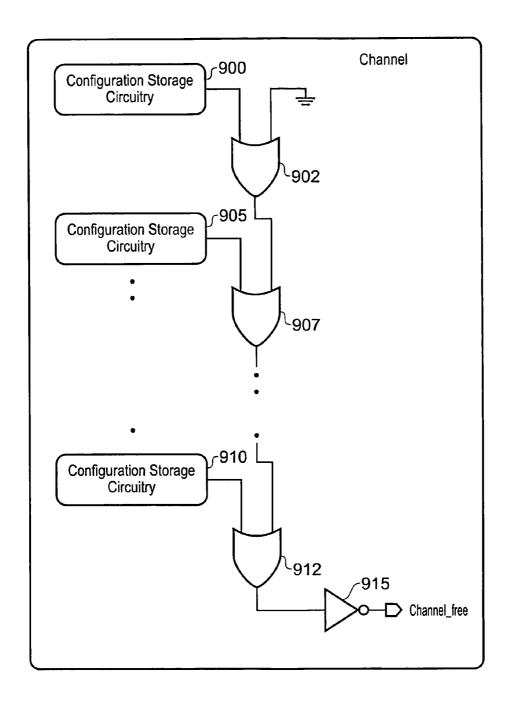

FIG. 14 illustrates how a channel\_free signal is generated in accordance with one embodiment;

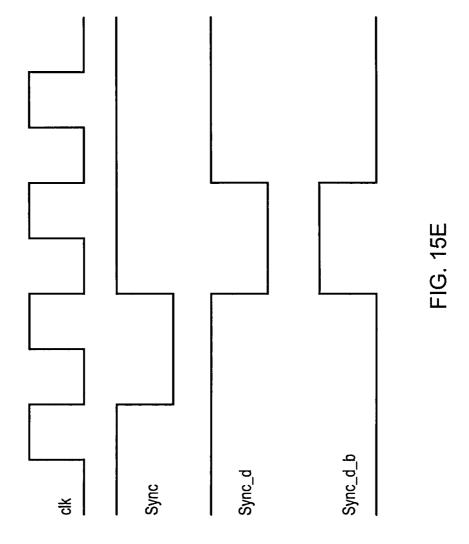

FIGS. **15**A to **15**E illustrate encoding and decoding circuitry that may be used in one embodiment to encode the input data prior to input into the crossbar circuitry, and to decode the output data from the crossbar circuitry, in order to reduce power consumption within the crossbar circuitry;

FIG. 16 illustrates how crossbar circuitry with narrow data input paths and data output paths may be arranged to operate in accordance with one embodiment;

FIGS. 17A and 17B illustrate how crossbar circuitry with narrow data input paths and data output paths may be arranged to operate in accordance with an alternative embodiment; and

FIG. **18** illustrates how crossbar circuitry may be used in a partially activated configuration in accordance with one embodiment.

## DESCRIPTION OF EMBODIMENTS

FIG. 1 illustrates a top-level diagram of a proposed switching fabric, comprising a crossbar circuitry in accordance with one embodiment and a plurality of source circuits and desti-

nation circuits connected thereto. The crossbar circuitry includes a plurality of data input paths 12 running in a first direction through the crossbar circuitry, and a plurality of data output paths 50 running in a second direction transverse to the first direction. In the embodiment of FIG. 1, both of these paths are formed by multi-bit buses, and in particular each data input path comprises a plurality of word lines and each data output path comprises a plurality of bit lines.

At the intersection between each data input path and data output path, a crossbar cell 20 is provided, which is used to selectively route data received on the associated data input path out on the associated data output path. Each crossbar cell includes a configuration storage element for storing the on/off status of each crossbar cell, such that if the crossbar cell is in the on state, then it will route input data received on the data input path to the data output path, and if the cell is in the off state, the input data will merely be passed through the cell without being routed onto the associated data output path.

Each data input path 12 is coupled to an associated source 20 circuit 30 from which input data 10 may be received, and each data output path 50 is coupled to an associated destination circuit 40 arranged to receive the output data 70 provided on that data output path.

In the embodiment shown, the bit lines of each data output 25 path 50 are precharged using a pre-charge module 55, and then the bit lines are selectively discharged dependent on the data input from one of the source circuits to a crossbar cell connecting that source circuit's data to the data output path. This selective discharge of the bit lines is detected by the 30 sense amplifier circuitry 65, in order to produce the output data 70.

Whilst data is routed through the crossbar circuitry in the above described manner when the crossbar is in a transmission mode of operation, the crossbar circuitry will not always 35 be in the transmission mode of operation. In particular, the crossbar circuitry has an arbitration mode of operation during which it detects and resolves any conflicts between transmission requests issued by the various source circuits 30. In particular, multiple requests for the same destination circuit 40 in a switching fabric is termed a collision, and with increasing numbers of sources and destinations, collisions become more frequent. As will be discussed in more detail later, each crossbar cell 20 includes arbitration circuitry which, in the arbitration mode of operation, operates in combination with arbitra- 45 tion circuitry of other crossbar cells, re-using the bit lines of the data output paths to detect the presence of multiple asserted transmission requests and, in the event of such multiple asserted transmission requests, to implement an adaptive priority scheme to resolve those conflicts. The proposed 50 approach provides a fast, low-power and highly scalable solution to detect and resolve such collisions.

Each crossbar cell includes priority storage circuitry for storing priority data referenced by the arbitration circuitry when implementing the adaptive priority scheme, the priority storage circuitry being configured to re-use the bit lines to self update the priority data stored therein between each application of the adaptive priority scheme by the arbitration circuitry.

Whilst in FIG. 1 the source circuits are shown to the left 60 hand side of the crossbar and the destination circuits are shown at the bottom of the crossbar, the source circuits can be provided at either side of the crossbar circuitry, and similarly the destination circuits can be provided at either end of the data output paths. Hence, it will be appreciated that the crossbar circuitry of embodiments of the present invention offers the flexibility of placing sources at either horizontal ends and

18

destinations at either vertical ends. This simplifies design floor planning by reducing routing congestion.

FIG. 2 illustrates how the bit lines of the data output paths may be re-used to detect and resolve conflicts during the arbitration mode of operation. In this example, there are 16 source circuits connected to the crossbar circuitry, that may issue transmission requests 0 to 15. For any particular data output path 50, each source circuit will be associated with a crossbar cell 20 which incorporates within it configuration storage circuitry in the form of a sense amp and latch. Hence, source 0 is associated with the crossbar cell containing the sense amp and latch 100, source 1 is associated with the crossbar cell containing the sense amp and latch 105, source 2 is associated with the crossbar cell containing the sense amp and latch 110, and so for the remainder of the source circuits, such that source circuit 15 is associated with the crossbar cell containing the sense amp and latch 115.

In the arbitration mode of operation, the precharge module 55 precharges all of the bit lines of each data output path 50, whereafter those bit lines are selectively discharged dependent on the asserted transmission requests and in accordance with an adaptive priority scheme. In this example, each data output path 50 comprises 16 bit lines, and it can be seen that each of the sense amp and latch circuits are associated with a different one of those bit lines. Following the precharge of the bit lines, the transmission requests asserted by the various source circuits are evaluated, an asserted transmission request in this embodiment taking a logic one value.

As shown in FIG. 2, the priority storage circuitry of each crossbar cell comprises a series of priority storage elements 130, one for each bit line other than the bit line to which the sense amp and latch of that crossbar cell is connected. In particular, as shown in FIG. 2, each crossbar cell includes a sequence of transistors 135 associated with each of the bit lines other than the bit line connected to the sense amp and latch circuitry of that crossbar cell. In the presence of an asserted transmission request, priority storage elements 130 are then used to provide a value to the gate of those transistors 135, in dependence on a value programmed into those priority storage elements.